US009786213B2

## (12) United States Patent

## Nakanishi et al.

## (54) DISPLAY DEVICE WITH BASIC CONTROL MODE AND LOW FREQUENCY CONTROL MODE

- (71) Applicant: PANASONIC LIQUID CRYSTAL DISPLAY CO., LTD., Hyogo (JP)

- Inventors: Hideyuki Nakanishi, Hyogo (JP);

Junichi Maruyama, Hyogo (JP);

Toshikazu Koudo, Hyogo (JP)

- (73) Assignee: PANASONIC LIQUID CRYSTAL DISPLAY CO., LTD., Hyogo (JP)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 15/130,614

- (22) Filed: Apr. 15, 2016

## (65) **Prior Publication Data**

US 2016/0232831 A1 Aug. 11, 2016

## **Related U.S. Application Data**

(63) Continuation of application No. PCT/JP2014/000932, filed on Feb. 21, 2014.

## (30) Foreign Application Priority Data

Oct. 16, 2013 (JP) ..... 2013-215339

- (51) Int. Cl. *G09G 3/36* (2006.01) *G09G 3/20* (2006.01) (Continued)

- (Continued) (58) Field of Classification Search

## (10) Patent No.: US 9,786,213 B2

## (45) **Date of Patent:** Oct. 10, 2017

(56) **References Cited**

## U.S. PATENT DOCUMENTS

| 8,013,822 | B2 * | 9/2011 | Nose | <br>G09G 3/3629 |

|-----------|------|--------|------|-----------------|

|           |      |        |      | 345/87          |

2003/0052852 A1 3/2003 Oohira (Continued)

## FOREIGN PATENT DOCUMENTS

| JP | H05-188885 A  | 7/1993  |

|----|---------------|---------|

| JP | 2003-091266 A | 3/2003  |

| JP | 2003-280578 A | 10/2003 |

| JP | 2006-064964 A | 3/2006  |

## OTHER PUBLICATIONS

International Search Report issued in corresponding International Patent Application No. PCT/JP2014/000932, mailed on May 27, 2014, with English translation.

Primary Examiner — Roy Rabindranath

(74) Attorney, Agent, or Firm — McDermott Will & Emery LLP

## (57) ABSTRACT

A display device including a display portion, a source driver, a gate driver and a controller, wherein the controller is configured to control the source driver and the gate driver based on a control mode for displaying the frame image on the display portion, in a basic control mode, the controller is configured to display a frame image on the display portion by causing the gate driver to progressively scan gate signal lines, in a low frequency control mode, the controller is configured to determine whether a regional signal is on in a specific region corresponding to specific gate signal lines, when it is determined that the regional signal is off, the controller is configured to display a sub-frame image on the display portion by causing the gate driver to perform interlaced scanning of the gate signal lines every K lines in the first frame frequency F1.

## 10 Claims, 30 Drawing Sheets

| (51) | Int. Cl.    |

|------|-------------|

|      | G02F 1/1368 |

|      | anna = 100  |

| G02F 1/1368 | (2006.01) |

|-------------|-----------|

| G09G 5/00   | (2006.01) |

| G09G 5/395  | (2006.01) |

|             |           |

(52) U.S. Cl. CPC ...... G09G 3/3614 (2013.01); G09G 3/3648 (2013.01); G09G 3/3677 (2013.01); G09G *3/3688* (2013.01); *G09G 5/001* (2013.01); G09G 5/395 (2013.01); G09G 2300/0426 (2013.01); *G09G* 2310/027 (2013.01); *G09G* 2310/0224 (2013.01); *G09G* 2310/0227 (2013.01); G09G 2310/08 (2013.01); G09G 2320/103 (2013.01); G09G 2330/021 (2013.01); G09G 2340/0435 (2013.01); G09G 2360/18 (2013.01)

#### **References** Cited (56)

| U.S. 1           | PATENT  | DOCUMENTS          |

|------------------|---------|--------------------|

| 2006/0044251 A1* | 3/2006  | Kato G09G 3/3611   |

|                  |         | 345/98             |

| 2007/0070010 A1* | 3/2007  | Oohira G09G 3/3648 |

|                  | - /     | 345/89             |

| 2010/0066728 A1* | 3/2010  | Oohira G09G 3/3648 |

|                  |         | 345/214            |

| 2014/0168281 A1* | 6/2014  | Ahn G09G 3/3648    |

|                  |         | 345/690            |

| 2014/0362073 A1* | 12/2014 | Huang G09G 3/3674  |

|                  |         | 345/213            |

| 2015/0062100 A1* | 3/2015  | Tanaka G09G 3/3648 |

|                  |         | 345/204            |

| 2015/0187308 A1* | 7/2015  |                    |

|                  |         | 345/209            |

|                  |         |                    |

\* cited by examiner

U.S. Patent

Sheet 6 of 30

|   |            | COMBINATION OF DATA<br>ENABLE SIGNALS (20Hz) |       |      |        |  |  |  |  |  |  |

|---|------------|----------------------------------------------|-------|------|--------|--|--|--|--|--|--|

|   | SG7        | SG7D1                                        | SG7D2 | SG70 | SG23   |  |  |  |  |  |  |

| 1 | High       | Low                                          | Low   | High | SG21   |  |  |  |  |  |  |

| 2 | don't care | High                                         | Low   | High | SG21D1 |  |  |  |  |  |  |

| 3 | don't care | don't care                                   | High  | High | SG21D2 |  |  |  |  |  |  |

| 4 |            | SG210                                        |       |      |        |  |  |  |  |  |  |

High: ENABLED, Low: DISABLED, don't care: NO REQUIREMENT

| CONTRO        |       | MD1 | (60H; | <u>z)</u> |                   |                                         |                   | M                                       | )2 (201           | Hz)               |      |                         |              | M    | D1 (60I | Hz)  | <b>3</b> 84- |

|---------------|-------|-----|-------|-----------|-------------------|-----------------------------------------|-------------------|-----------------------------------------|-------------------|-------------------|------|-------------------------|--------------|------|---------|------|--------------|

| Modi<br>Frame |       | FR1 | FR2   | FR3       | SF4               | SF5                                     | SF6               | SF7                                     | SF8               | SF9               | SF10 | SF11                    | SF12         | FR13 | FR14    | FR15 |              |

| IMAGE         |       | IM1 | IM2   | 1M3       | IM3+<br>A4+<br>B4 | IM3+<br>A5+<br>B5                       | IM3+<br>A6+<br>B6 | IM3+<br>A7+<br>B7                       | 1M3+<br>A8+<br>B8 | IM3+<br>A9+<br>B9 | +    | IM3+<br>A11<br>+<br>B11 | +            | IM13 | IM14    | IM15 |              |

| G             | 1     |     | +     | ~~~       | +                 |                                         |                   |                                         |                   |                   | +    |                         |              |      | +       |      | <b>≜</b>     |

| G             | 2 [   |     | +     |           |                   |                                         |                   |                                         | +                 |                   |      | -                       |              |      | +       |      | 20Hz         |

| G             | 3 [   |     | +     |           |                   |                                         | ÷                 |                                         |                   |                   |      |                         | +            |      | +       |      | ZUHZ         |

| G             | 4 [   |     | +     |           | ÷                 | 000000000000000000000000000000000000000 |                   |                                         |                   | 00000000000       |      |                         | 000000000000 |      |         |      | ¥            |

| G             | 5     |     | +     |           | +                 |                                         |                   |                                         | +                 |                   | +    |                         |              |      | +       |      | 🗘 40Hz       |

| G             | 6     |     | +     |           | +                 |                                         | +                 |                                         | +                 |                   | +    |                         | +            |      | +       |      | <b>A</b>     |

| G             | 7     |     | +     |           | +                 |                                         | +                 |                                         | +                 | ~~                | +    |                         | +            | ~~~  | +       |      | 60Hz         |

| G             | 8     |     | +     |           | +                 |                                         | +                 |                                         | +                 |                   | +    |                         | +            | ~~~  | +       |      |              |

| G             | 9     |     | +     |           |                   |                                         | +                 |                                         | +                 |                   | +    |                         | +            |      | +       |      | ¥            |

| G             | 10    |     | +     |           | +                 |                                         |                   |                                         | +                 |                   | +    |                         |              |      | +       |      | 🗘 40Hz       |

| G             | . j., |     | +     |           |                   |                                         |                   |                                         | +                 |                   |      |                         |              |      | +       |      | <b>Å</b>     |

| G             | 12    |     | +-    |           |                   |                                         | +                 | 000000000000000000000000000000000000000 |                   |                   |      |                         |              |      | +       |      | 20Hz         |

| G             | 13    |     | +     | _         | +                 |                                         |                   |                                         |                   |                   | +    |                         |              | _    | +       |      |              |

| G             | 14    |     | +     |           |                   |                                         |                   |                                         | +                 |                   |      |                         |              |      | +       |      | ¥            |

| G             | 15    |     | +     |           | +                 |                                         | +                 |                                         |                   |                   | +    |                         | +            |      | +       |      | 🗘 40Hz       |

| G             | 16    |     | +     |           | +                 |                                         | +                 |                                         | +                 |                   | +    |                         | +            |      | +       |      | A I          |

| G             | 17    |     | +     |           | +                 |                                         | +                 |                                         | +                 |                   | +    |                         | +            |      | +       |      | 60Hz         |

| G             | 18    |     | +     |           | +                 |                                         | +                 |                                         | +                 |                   | +    |                         | +            |      | +       |      | ¥            |

| G             | 19    |     | +     |           | +                 |                                         |                   |                                         | +                 |                   | +    |                         | ļ            |      | +       |      | 🗘 40Hz       |

| G2            | 20    |     | +     |           |                   |                                         |                   |                                         | +-                |                   |      |                         |              |      | -+-     |      | 🗘 20Hz       |

U.S. Patent

| CONTROL<br>MODE | М   | D1 (60H | z)  | MD2 (20Hz) |                                         |            |            |                   |                   |                   |                                         |      | MD1 (60Hz) |      |  |

|-----------------|-----|---------|-----|------------|-----------------------------------------|------------|------------|-------------------|-------------------|-------------------|-----------------------------------------|------|------------|------|--|

| FRAME           | FR1 | FR2     | FR3 | SF4        | SF5                                     | SF6        | SF7        | SF8               | SF9               | SF10              |                                         | SF12 | FR13       | FR14 |  |

| IMAGE           | IM1 | IM2     | IM3 | IM3        | IM3                                     | IM3+<br>A1 | IM3+<br>A1 | 1M3+<br>A1+<br>A2 | 1M3+<br>A1+<br>A2 | IM3+<br>A1+<br>A2 | IM3+<br>A1+<br>A2                       | IM12 | IM13       | ]M14 |  |

| <b>G</b> 1      | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          |      |  |

| G2              | +   |         | +   |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          |      |  |

| G3              | +   |         | +   |            |                                         |            |            |                   | +                 |                   |                                         |      | +          | —    |  |

| G4              | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          | —    |  |

| G5              | +   |         | +   |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          |      |  |

| G6              | +   |         |     |            |                                         |            |            |                   | +                 |                   |                                         |      | +          |      |  |

| G7              | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          |      |  |

| G8              | +   |         | +   |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          |      |  |

| G9              | +   |         | +   |            |                                         |            |            |                   | +                 |                   |                                         |      | +          |      |  |

| G10             | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          |      |  |

| G11             | +   |         | -†- |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          |      |  |

| G12             | +   |         | +   |            |                                         |            |            |                   | +                 |                   |                                         |      | +          |      |  |

| G13             | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          |      |  |

| G14             | +   |         | +   |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          |      |  |

| G15             | +   |         |     |            |                                         |            |            |                   | +                 |                   | 000000000000000000000000000000000000000 |      | -+-        |      |  |

| G16             | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          |      |  |

| G17             | +   |         | +-  |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          | —    |  |

| G18             | +   |         | -+- |            | 000000000000000000000000000000000000000 |            |            |                   | +                 |                   |                                         |      | +          |      |  |

| G19             | +   |         | +   |            |                                         |            | +          |                   |                   |                   |                                         |      | +          |      |  |

| G20             | +   |         | +   |            | +                                       |            |            |                   |                   |                   | +                                       |      | +          |      |  |

Sheet 28 of 30

5

## DISPLAY DEVICE WITH BASIC CONTROL MODE AND LOW FREQUENCY CONTROL MODE

## CROSS-REFERENCE TO RELATED APPLICATION

This application is bypass continuation of international patent application PCT/JP14/000932, filed: Feb. 21, 2014 designating the United States of America, the entire disclo-<sup>10</sup> sure of which is incorporated herein by reference. Priority is claimed based on Japanese patent applications JP 2013-215339, filed: Oct. 16, 2013. The entire disclosures of this Japanese patent application are incorporated herein by reference in its entirety.

## TECHNICAL FIELD

This disclosure is related with a display device including  $_{20}$  a display portion configured to display a frame image.

### BACKGROUND

A liquid crystal display device is one example of display 25 devices that are used as high-definition color monitors for computers and other information devices, and as television receivers. A liquid crystal display device fundamentally includes a display portion in which liquid crystals are sandwiched between two substrates at least one of which is 30 made of transparent glass or the like. In addition, a liquid crystal display device includes a driver for selectively applying voltages to pixel electrodes formed on the substrate of the display portion. Pixels of the respective pixel electrodes are controlled based on the voltage applied by the driver. 35

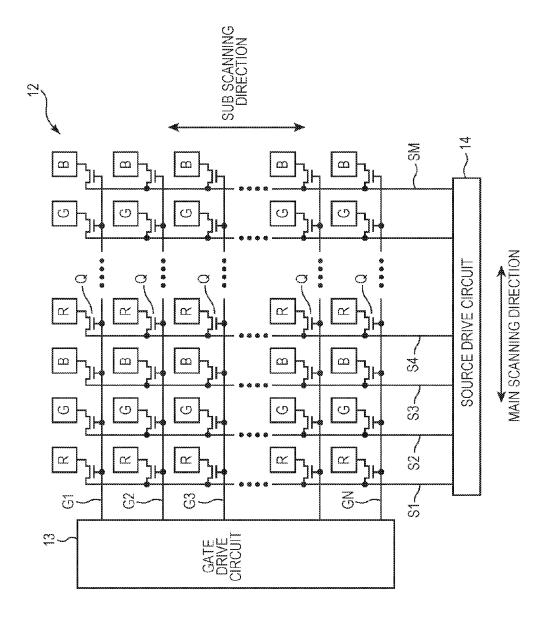

The display portion generally includes gate signal lines, source signal lines, and pixel electrodes. The gate signal lines, for example, respectively extend in a horizontal direction (main scanning direction), and are aligned in a vertical direction (sub scanning direction). The source signal lines, 40 for example, respectively extend in the vertical direction (sub scanning direction), and are aligned in the horizontal direction (main scanning direction). Thin film transistors (TFTs) and the pixel electrodes are disposed in a matrix at intersection points of the gate signal lines and the source 45 signal lines. A gate driver outputs voltages (gate signals) to the gate signal lines for turning the TFTs on and off. A source driver outputs voltages (source signals) based on an input image signal to the pixel electrodes via the source signal lines to thereby control transmittance of liquid crystals 50 provided corresponding to the pixel electrodes to values according to the source signals.

A display device smoothly displays images on a display portion by successively switching frame images to be displayed on the display portion, for example, based on image 55 signals input from outside. A framefrequency, a frequency of switching a frame image is generally 60 Hz. A display device is conventionally known to detect whether an input image signal is a signal representing still picture or moving picture, and switch the framefrequency depending on a 60 result of detection, for example, described in a prior art (See Japanese Unexamined Patent Application Publication No. JP 2003-280578). This prior art discloses a display device which detects whether an image signal is a still picture or a moving picture, and switches to lower the framefrequency 65 when it detects a still picture. It can decrease power consumption when the display device displays an image.

The display device according to the prior art, however, does not lower the frame frequency, in a case that even if an input image signal represents a still picture in a part of an image, it represents a moving picture in the other part of an image. Therefore, there is a problem in that it does not reduce power consumption enough.

### SUMMARY

The present disclosure has been made in view of above, and an object of this application is to provide a display device which can reduce power consumption.

In one general aspect, the instant application describes a display device including a display portion including source signal lines, gate signal lines, and pixel electrodes, each pixel electrode being connected to one of the source signal lines and one of the gate signal lines. The display portion is configured to display a frame image in a frame frequency for every vertical synchronizing signal. The frame image is represented by image signals corresponding to the pixel electrodes. The display device includes source driver being configured to apply voltages to the pixel electrodes corresponding to the image signals via the source signal lines, a gate driver configured to scan the gate signal lines by outputting a gate signal to each of the gate signal lines, and a controller configured to control the source driver and the gate driver based on a control mode for displaying the frame image on the display portion. The control mode includes a basic control mode and a low frequency control mode. In the basic control mode, the frame frequency is determined to be a first frame frequency F1, and in the low frequency control mode, the frame frequency is determined to be a second frame frequency F2 (F2 $\leq$ F1). The controller is configured to control the gate driver such that a horizontal scanning period (H) is constant regardless of the control mode being the basic control mode or the low frequency control mode. In the basic control mode, the controller is configured to display the frame image on the display portion by causing the gate driver to progressively scan the gate signal lines. In the low frequency control mode, the controller is configured to determine whether a regional signal is on in a specific region corresponding to specific gate signal lines in a frame image. When it is determined that the regional signal is off, the controller is configured to display a sub-frame image on the display portion by causing the gate driver to perform interlaced scanning of the gate signal lines every K lines in the first frame frequency F1. The K is an integer expressed by F1/F2, and the controller is configured to display the frame image constituted by K sub-frame images on the display portion by repeating display of the sub-frame image for K times. When it is determined that the regional signal is on, the controller is configured to cause the gate driver to progressively scan the specific gate signal lines every time the sub-frame image is displayed.

According to one aspect of this disclosure, even in the low frequency control mode, the controller is configured to cause the gate driver to progressively scan in the specific region of the frame image every time the sub-frame image is displayed. Thereby, quality of image display in the specific region of the frame image is the same as that in the basic control mode. And, in the low frequency mode, in a region other than the specific region, where the regional signal is off, the gate signal lines are performed interlaced scanning of every K lines in the first frame frequency F1. Therefore, it can achieve a lot of reduction of power consumption.

## BRIEF DESCRIPTION OF DRAWINGS

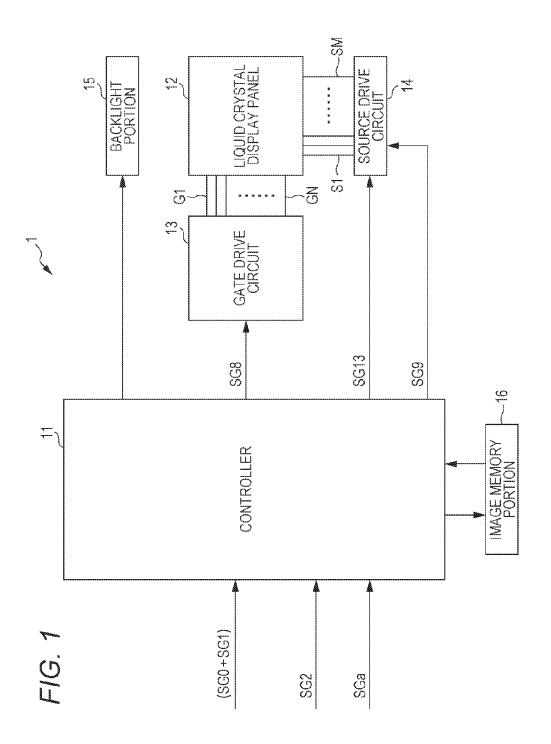

FIG. **1** is a block diagram showing a configuration of a display device according to a first embodiment;

30

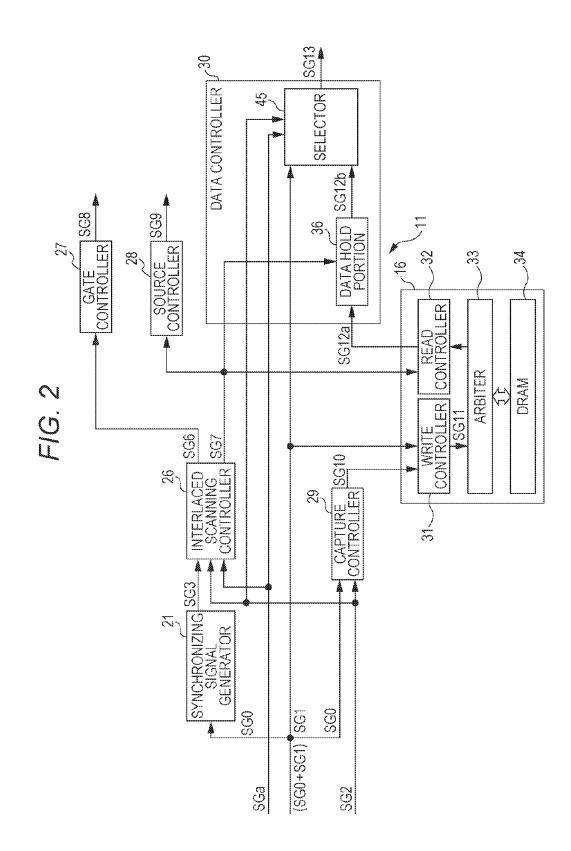

FIG. **2** is a block diagram showing a configuration of a controller and an image memory portion shown in FIG. **1**;

FIG. **3** is a circuit diagram showing a state of connection of signal lines in a liquid crystal display panel shown in FIG. **1**:

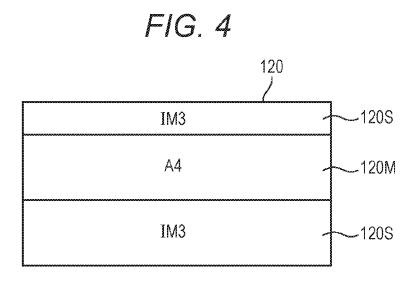

FIG. **4** is a configuration schematically showing a mixing image of a moving picture region and a still picture region displayed in a display portion of the liquid crystal display panel shown in FIG. **1**;

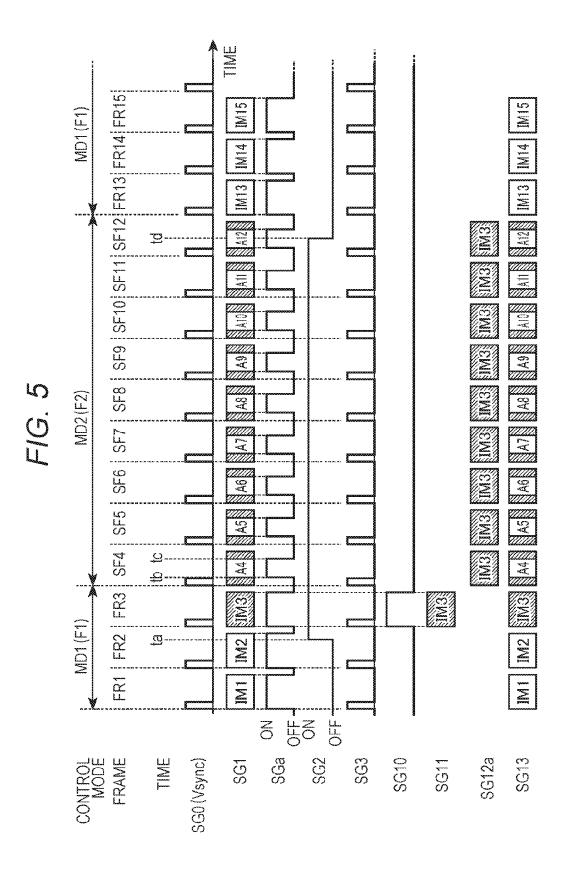

FIG. **5** is a timing chart schematically showing main 10 signals shown in FIG. **2** in a case in which the control mode shifts from a basic control mode to a low frequency control mode, and in the low frequency control mode, a part of a still picture is shifted to a moving picture;

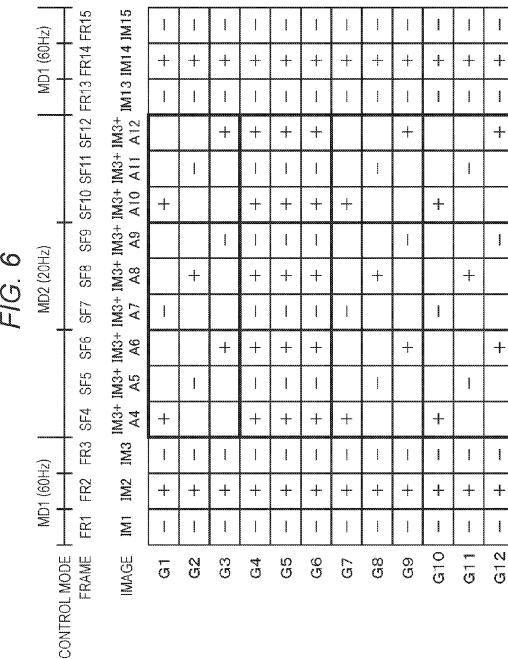

FIG. **6** is a diagram schematically showing polarities of 15 voltages applied to one of the source signal lines in performing an operation shown in FIG. **5** of the control mode shifting from the basic control mode to the low frequency control mode and returning to the basic control mode from the low frequency control mode; 20

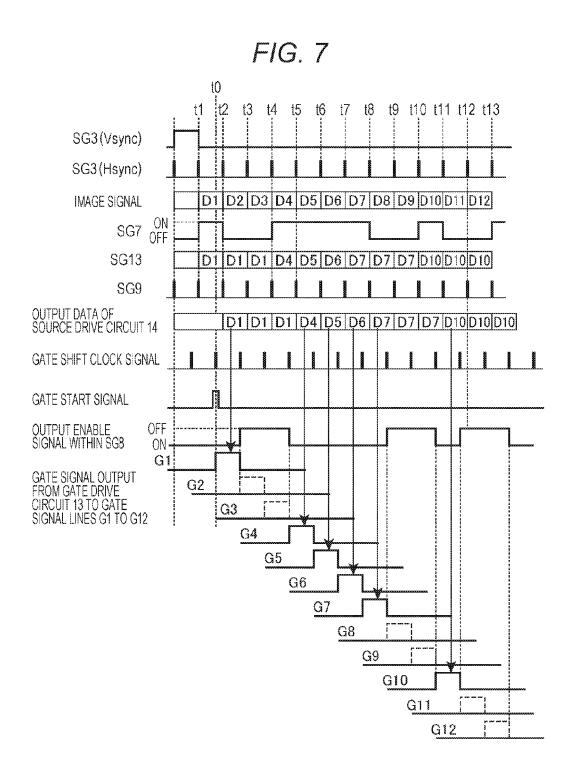

FIG. **7** is a timing chart schematically showing operations of a gate drive circuit and a source drive circuit in a sub-frame in FIG. **5** in which the control mode is the low frequency control mode;

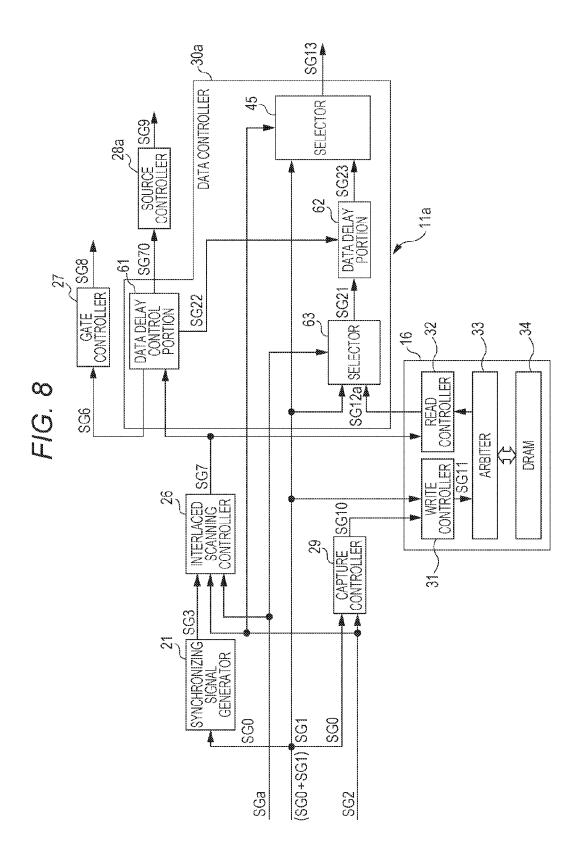

FIG.  $\hat{\mathbf{8}}$  is a block diagram showing a configuration of a 25 controller and an image memory portion of a display device according to a second embodiment.

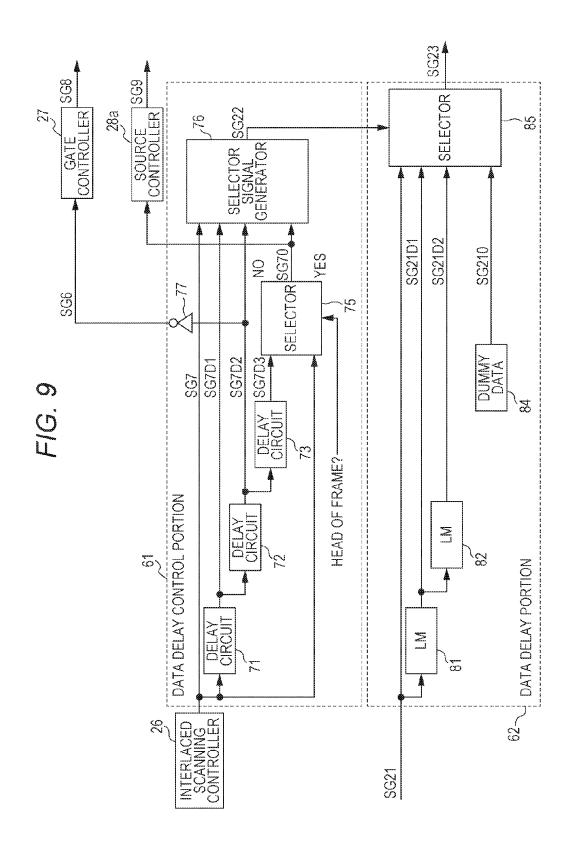

FIG. **9** is a block diagram showing a configuration of a data delay control portion and a data delay portion shown in FIG. **8**;

FIG. **10** is a truth table of a selector in a data delay portion shown in FIG. **9**;

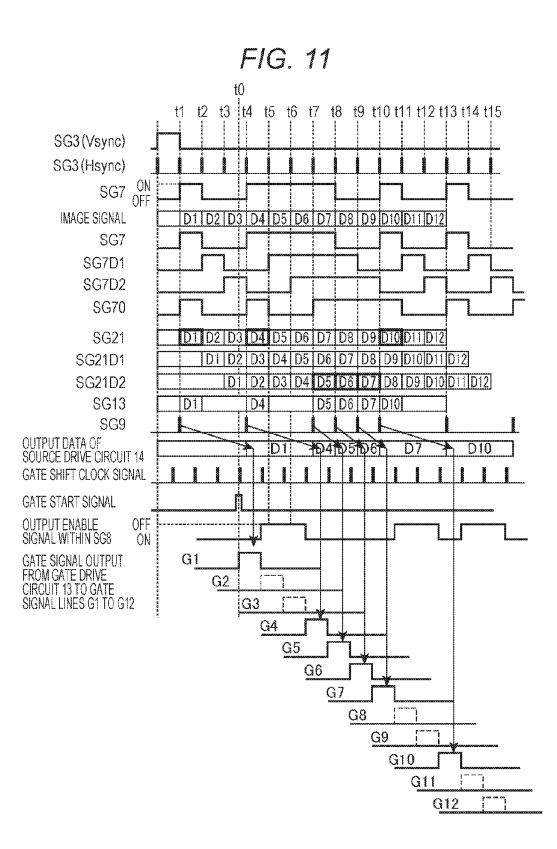

FIG. **11** is a timing chart schematically showing operations of a gate drive circuit and a source drive circuit according to the second embodiment

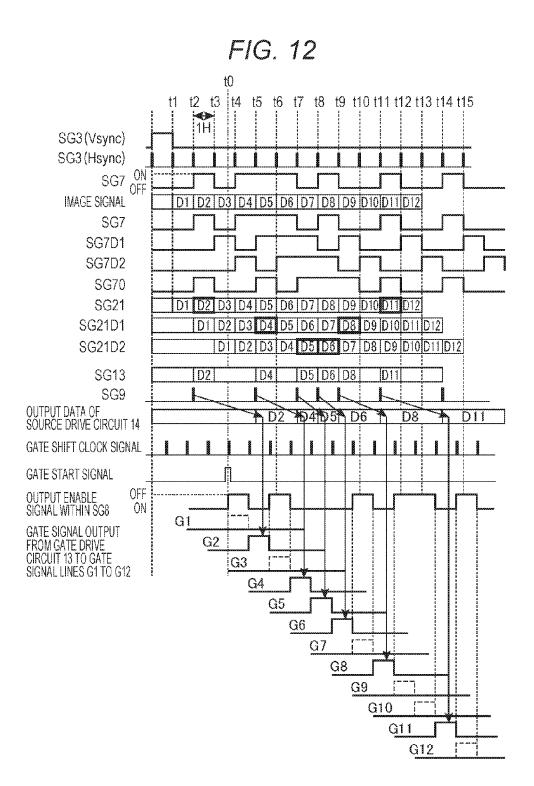

FIG. **12** is a timing chart schematically showing operations of the gate drive circuit and the source drive circuit according to the second embodiment;

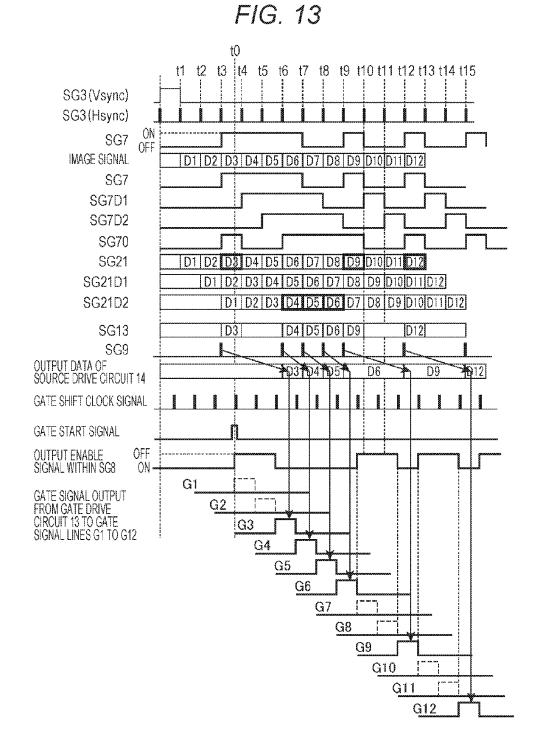

FIG. **13** is a timing chart schematically showing operations of the gate drive circuit and the source drive circuit 40 according to the second embodiment;

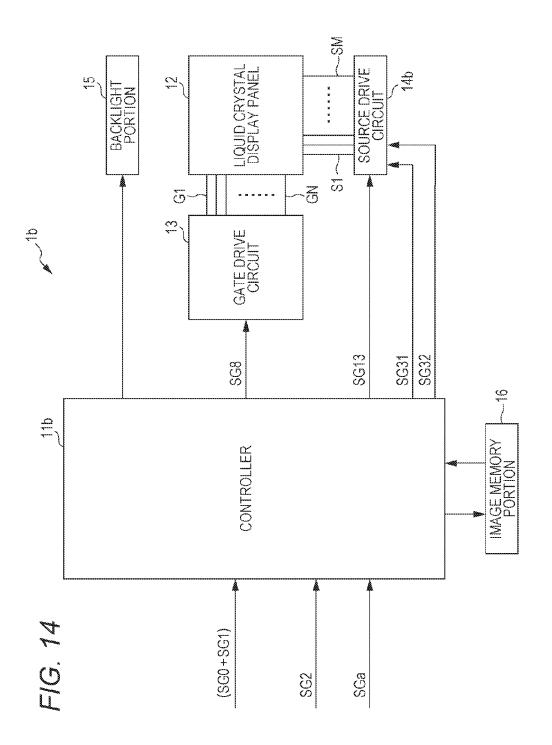

FIG. **14** is a block diagram showing a configuration of a display device according to a third embodiment;

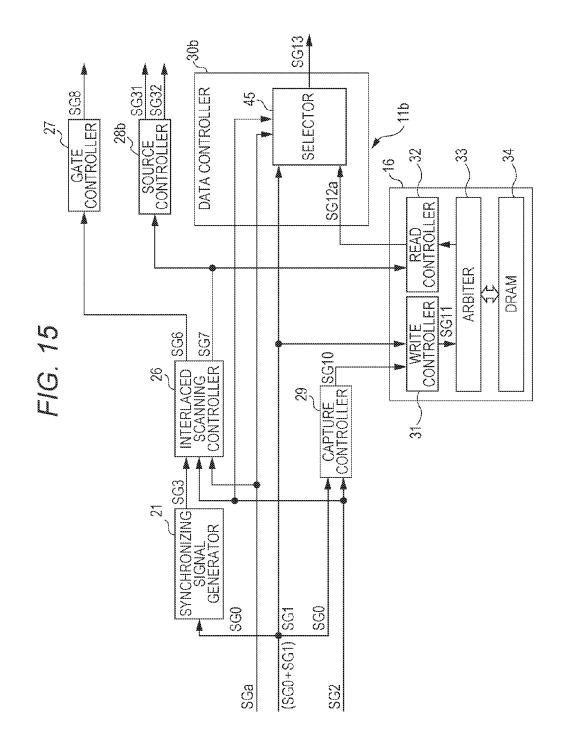

FIG. **15** is a block diagram showing a configuration of a controller and an image memory portion of the display 45 device shown in FIG. **15** according to the third embodiment;

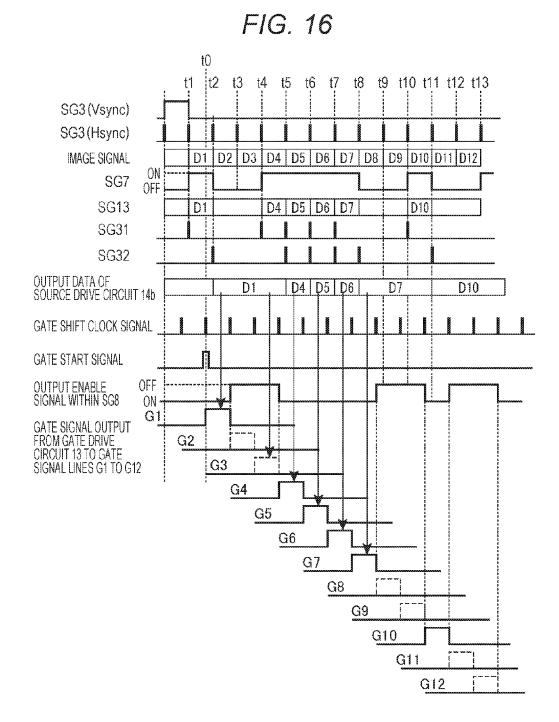

FIG. **16** is a timing chart schematically showing operations of a gate drive circuit and a source drive circuit according to the third embodiment;

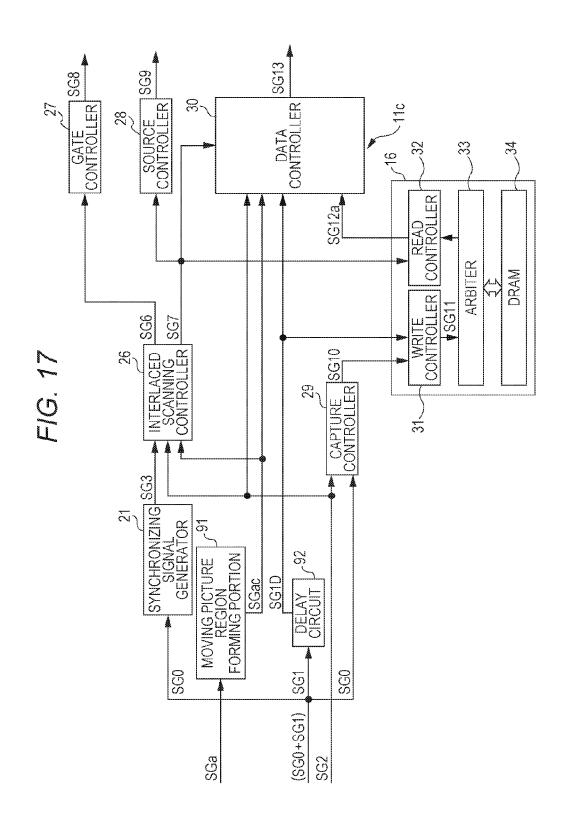

FIG. **17** is a block diagram showing a configuration of a <sup>50</sup> controller and an image memory portion of a display device according to a fourth embodiment;

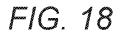

FIG. **18** is a configuration schematically showing a mixing image of a still picture region and two moving picture regions displayed in the display portion of the liquid crystal 55 display panel shown in FIG. **1**;

FIG. **19** is a configuration schematically showing on and off of an input voltage input to one source signal line when an image shown in FIG. **18** is displayed;

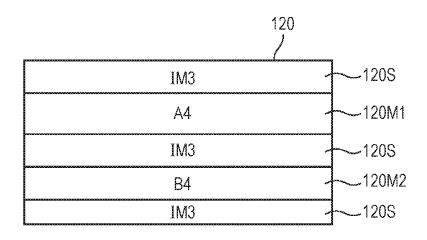

FIG. **20** is a timing chart schematically showing main 60 signals shown in FIG. **17**;

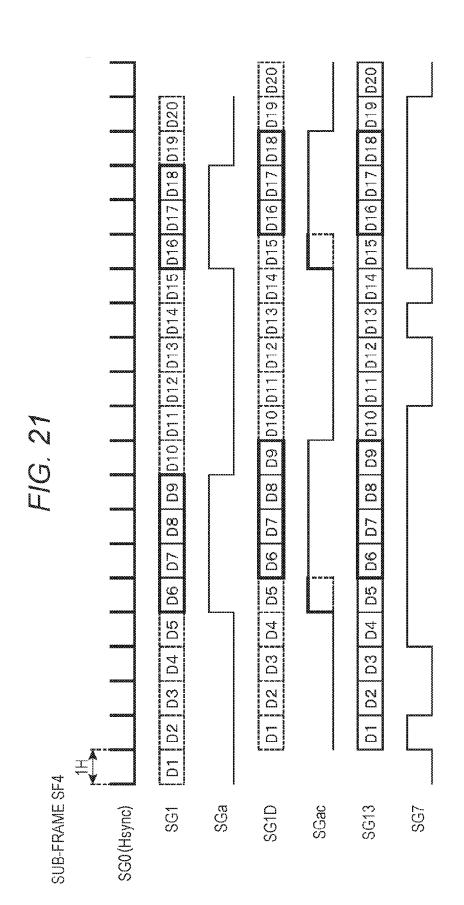

FIG. 21 is a timing chart schematically showing main signals shown in FIG. 17;

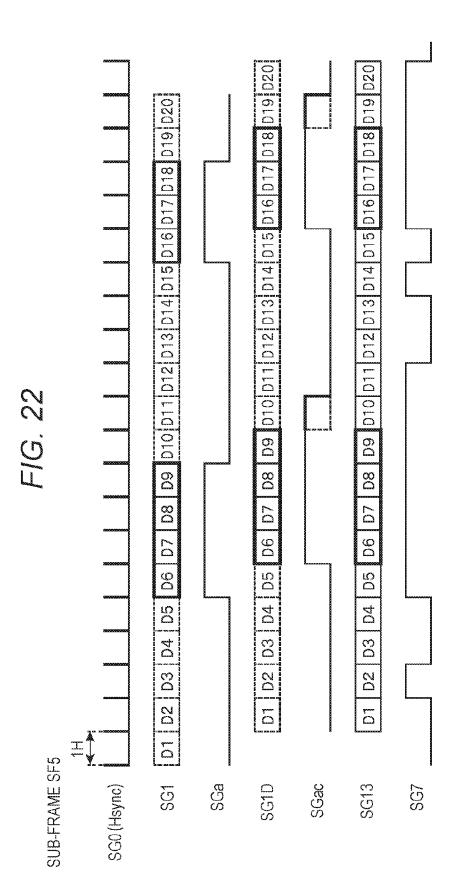

FIG. 22 is a timing chart schematically showing main signals shown in FIG. 17; 65

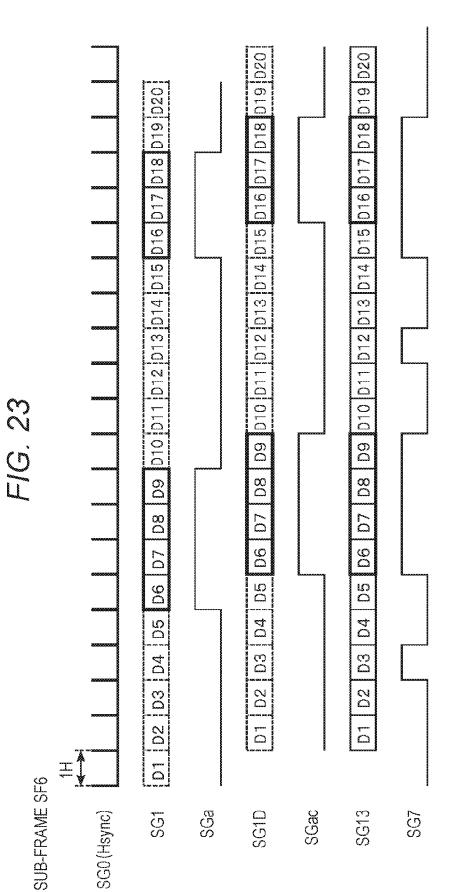

FIG. 23 is a timing chart schematically showing main signals shown in FIG. 17;

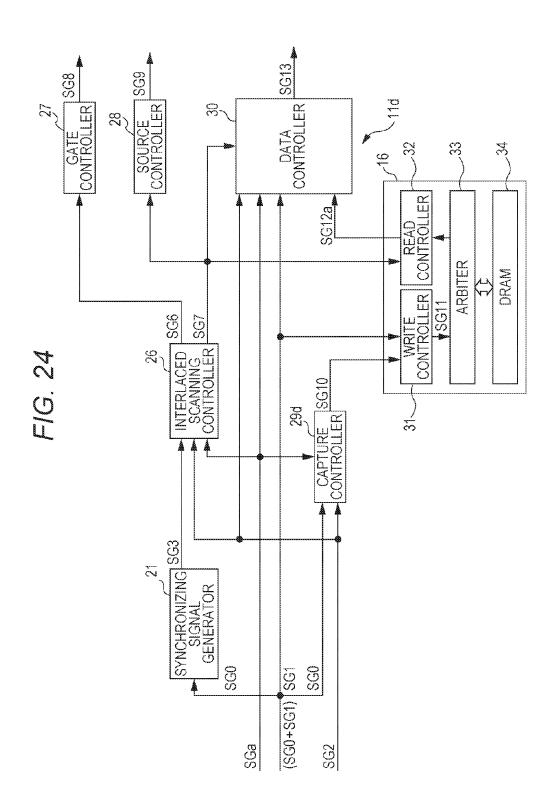

FIG. **24** is a block diagram showing a configuration of a controller and an image memory portion of a display device according to a fifth embodiment;

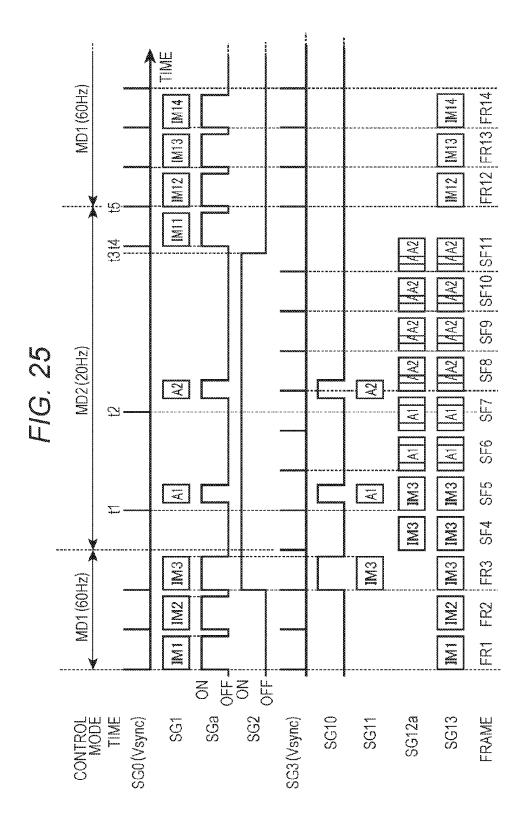

FIG. **25** is a timing chart schematically showing main signals shown in FIG. **24** in a case in which after the control mode shifts from a basic control mode to a low frequency control mode, a part of a region of a still picture is updated to a different still picture, and then another part of the region of the still picture is updated to a different still picture in the low frequency control mode;

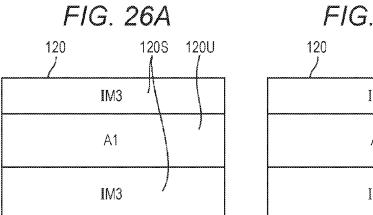

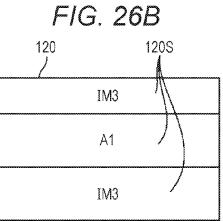

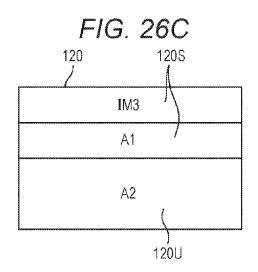

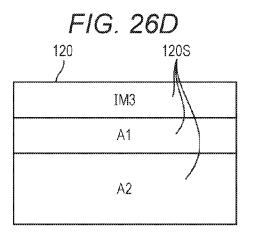

FIGS. **26** A~D are configurations schematically showing states of image in the display portion of the liquid crystal display panel in cases of operations shown in FIG. **25**;

FIG. **27** is a diagram schematically showing polarities of voltages applied to one of the source signal lines in performing the operation shown in FIG. **25**;

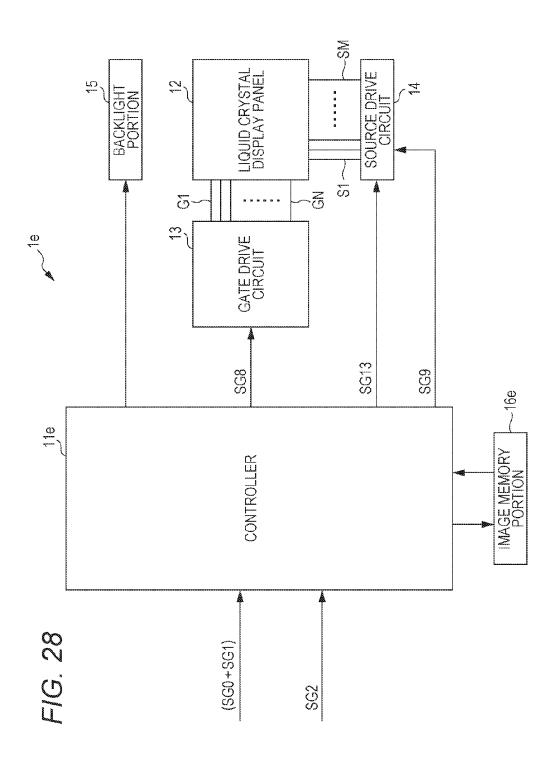

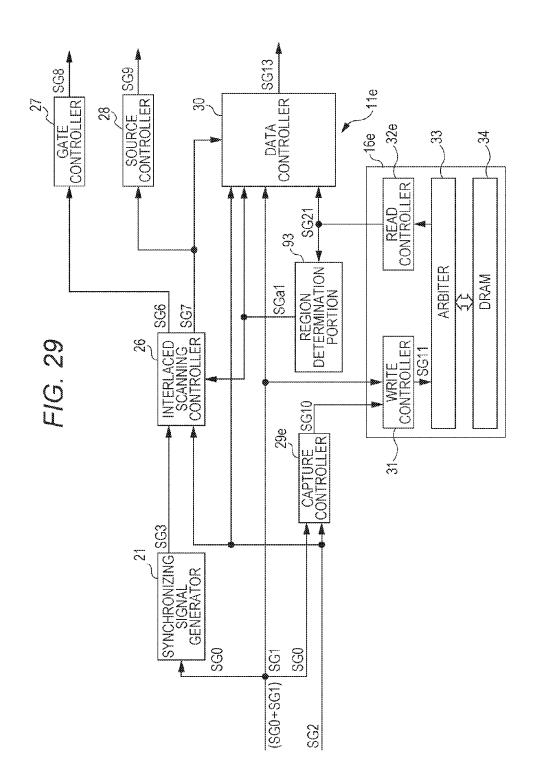

FIG. **28** is a block diagram showing a configuration of a display device according to a sixth embodiment;

FIG. **29** is a block diagram showing a configuration of a <sup>20</sup> display device according to the sixth embodiment shown in FIG. **28**;

FIG. **30** is a configuration schematically showing a mixing image of an image region in which a gap in gray scales is small and another image region in which a gap in gray scale is large displayed in a display portion of the liquid crystal display panel shown in FIG. **28**.

## DETAILED DESCRIPTION

Exemplary display devices are described below with reference to the drawings. In the following numerals. Redundant explanation is omitted as appropriate to clarify the description. Configurations, arrangements and shapes shown in the drawings and description relating to the drawings aim to make principles of the embodiments easily understood. Therefore, the principles of the present embodiments are not limited thereto.

## First Embodiment

FIG. 1 is a block diagram showing a configuration of a display device according to the first embodiment. FIG. 2 is a block diagram showing a configuration of a controller and an image memory portion shown in FIG. 1. FIG. 3 is a circuit diagram showing a state of connection of signal lines in a liquid crystal display panel shown in FIG. 1. FIG. 4 is a configuration schematically showing a mixing image of a moving picture region and a still picture region displayed in a display portion of the liquid crystal display panel shown in FIG. 1.

Referring to FIG. 1, a display device 1 includes a controller 11, a liquid crystal display panel 12, a gate drive circuit 13, a source drive circuit 14, a backlight portion 15, and an image memory portion 16. The controller 11 includes, as shown in FIG. 2, a synchronizing signal generator 21, an interlaced scanning controller 26, a gate controller 27, a source controller 28, a capture controller 29, and a data controller 30. The data controller 30 includes a selector 45 and a data hold portion 36. The image memory portion 16 includes a write controller 31, a read controller 32, an arbiter 33, and a dynamic random access memory (DRAM) 34.

The liquid crystal display panel **12** includes, as shown in FIG. **3**, source signal lines S**1**, S**2**, ..., SM, gate signal lines G**1**, G**2**, ..., GN, thin film transistors Q, pixel electrodes R, G, and B (i. e., the pixel electrode R corresponding to a red sub-pixel, the pixel electrode G corresponding to a green

sub-pixel, and the pixel electrode B corresponding to a blue sub-pixel). The source signal lines S1, S2, ..., SM extend along a vertical direction (sub scanning direction), and are aligned in a horizontal direction (main scanning direction). The gate signal lines G1, G2, ..., GN extend along the 5 horizontal direction (main scanning direction), and are aligned in the vertical direction (sub scanning direction). The thin film transistors Q and the pixel electrodes R, G, and B are disposed in a matrix at intersections between the source signal lines S1, S2, ..., SM and the gate signal lines 10 G1, G2, ..., GN.

The backlight portion **15** includes a light source, and is configured to illuminate the liquid crystal display panel **12** from the back side of the liquid crystal display panel **12**. The backlight portion **15** may employ a lighting method of either 15 of an edge lighting type and a direct lighting type.

To the controller 11, an input signal including a synchronizing signal SG0 and an image signal SG1, a standby mode signal SG2 and a regional signal SGa are input from outside. The synchronizing signal SG0 includes a vertical synchro- 20 nizing signal Vsync and a horizontal synchronizing signal Hsync. The image signal SG1 represents a frame image. The image signal SG1 includes image signals respectively corresponding to the pixel electrodes R, G, and B of the liquid crystal display panel 12. The standby mode signal SG2 is 25 turned on when the frame image represented by the image signal SG1 that has been input is switched from a moving picture to a still picture. When the standby mode signal SG2 is turned on, then, an input of the image signal SG1 representing the still picture is stopped. This helps reduction 30 of power consumption. Further, the standby mode signal SG2 is turned off when the frame image represented by the image signal SG1 that has been input is switched from a still picture to a moving picture.

The regional signal SGa is turned on, while the image 35 signal SG1 representing a moving picture is input. And the regional signal SGa is turned on corresponding to a region representing a moving picture in an image signal SG1, when the image signal SG1 which represents a moving picture mixed with a still picture is input while the standby mode 40 signal SG2 is turned on.

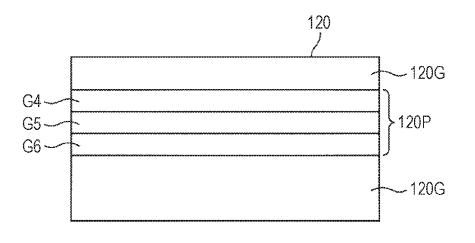

FIG. 4 shows a mixing image of a moving picture region 120M displaying a moving picture A4 and a still picture region 120S displaying a still picture IM3 in a display portion 120 of the liquid crystal display panel 12. In the FIG. 45 4, the regional signal SGa is turned on corresponding to a region in which a moving picture A4 is displayed in a moving picture region 120M within the display portion 120 of the liquid crystal display panel 12. In this manner, when the standby mode signal SG2 is turned on, and then a still 50 picture and a moving picture are mixed, the image signal SG1 which represents only the moving picture is input, and the image signal SG1 which represents the still picture is not input. This helps reduction of power consumption.

The controller **11** controls the source drive circuit **14** to 55 apply a voltage, in a column inversion drive mode, to the pixel electrodes R, G, and B, which are disposed in a matrix, of the liquid crystal display panel **12**. The column inversion drive mode is a drive mode in which voltages of the same polarity are applied to pixel electrodes connected to the 60 same source signal line in each frame, polarities of voltages applied to pixel electrodes connected to adjacent ones of source signal lines are inverted, and polarities of the voltages applied to pixel electrodes are inverted for each frame.

The controller 11 controls the gate drive circuit 13 and the 65 source drive circuit 14 according to a control mode. The controller 11 includes a basic control mode and a low

6

frequency control mode as the control mode. The controller **11** normally takes the basic control mode as the control mode. The controller **11** causes the control mode to shift from the basic control mode to the low frequency control mode when the standby mode signal SG**2** is turned on. When the standby mode signal SG**2** is turned off, the controller **11** causes the control mode to return to the basic control mode from the low frequency control mode.

In the basic control mode, as a result of completion of application of the voltage to the gate signal lines G1, G2, ..., GN from the top to the bottom (that is, the gate signal lines G1, G2, ..., GN are progressively scanned) by the gate drive circuit 13 and the source drive circuit 14, image data corresponding to the image signal SG1 is written once into pixels (liquid crystals) of all of pixel electrodes R, G, and B. Writing of the image data to all of the pixels generates an image for one frame. The liquid crystal display panel 12 is a holding-type display portion that holds the written image data for one frame period until the image data is next written. The liquid crystal display panel 12 may employ an IPS (In Plane Switching) method, a VA (Vertical Alignment) method, or any other methods.

In the basic control mode, the controller 11 repeats image generation for one frame at a frame frequency F1. In the first embodiment, F1=60 Hz. This allows a moving picture displayed on the liquid crystal display panel 12 to be visually recognized by a viewer. When the standby mode signal SG2 is turned on, the controller 11 stores an image signal representing a frame image at this time in the DRAM 34 of the image memory portion 16, and causes the control mode to shift from the basic control mode to the low frequency control mode.

In the low frequency control mode, the controller **11** repeats image generation for one frame at a frame frequency F2 using the image signal stored in the DRAM **34**. In the first embodiment, F2=20 Hz. In the low frequency control mode, the controller **11** displays an image for one frame on the liquid crystal display panel **12** by performing interlaced scanning of the gate signal lines by every three gate signal lines (that is, thinning the gate signal lines to be scanned), generating a sub-frame image at the same frequency as the frame frequency F1, and repeating an operation of displaying the generated sub-frame image on the liquid crystal display panel **12** three times. This allows a still picture displayed on the liquid crystal display panel **12** to be visually recognized by the viewer.

The controller **11** does not perform interlaced scanning of gate signal lines, but progressively scans the gate signal lines in a region in which a moving picture is displayed, that is a region where the regional signal SGa is turned on, in a case when a part of a still picture is switched to a moving picture in the low frequency control mode. It can prevent image qualities of a moving picture from deteriorating.

The controller **11** controls light-on and light-off of the backlight portion **15**. The controller **11** repeats light-on and light-off of the backlight portion **15** at the same frequency as the frame frequency F1 regardless of the frame frequency.

In FIG. 2, when the synchronizing signal SG0 and the image signal SG1 are input, the synchronizing signal generator 21 generates the input synchronizing signal SG0 as a synchronizing signal SG3 for display an image. When the synchronizing signal SG0 and the image signal SG1 are not input, the synchronizing signal generator 21 generates the synchronizing signal SG3 for displaying an image. The synchronizing signal SG3 to the interlaced scanning controller 26. The synchronizing signal SG3 includes the ver-

tical synchronizing signal Vsync and the horizontal synchronizing signal Hsync, as the synchronizing signal SG0 does.

While the standby mode signal SG2 is turned off, that is, during the basic control mode, the interlaced scanning controller 26 generates an output enable signal SG6 and a 5 data enable signal SG7 to scan the gate signal lines G1~GN in order at the frame frequency F1 of 60 Hz in synchronization with the synchronizing signal SG3. Further, during the low frequency control mode in which the standby mode signal SG25 is turned on, the interlaced scanning controller 10 26 generates the output enable signal SG6 and a data enable signal SG7 to perform interlaced scanning of the gate signal lines G1~GN at the frame frequency F2 of 20 Hz.

The interlaced scanning controller **26** generates the output enable signal SG**6** and the data enable signal SG**7** to perform 15 interlaced scanning of gate signal lines G**1**-GN in a region corresponding to a still picture, that is a region where the standby mode signal SG**2** is turned on and the regional signal SGa is turned off. And the interlaced scanning controller **26** generates the output enable signal SG**6** and the 20 data enable signal SG**7** to progressively scan the gate signal lines G**1**-GN in a region corresponding to a moving picture, that is a region where the standby mode signal SG**2** is turned on and the regional signal SGa is turned on.

The interlaced scanning controller **26** outputs the gener- <sup>25</sup> ated output enable signal SG**6** to the gate controller **27**. The interlaced scanning controller **26** outputs the generated data enable signal SG**7** to the source controller **28**, the read controller **32** and data hold portion **36**.

The capture controller **29** generates a range signal SG10 30 when the standby mode signal SG2 is turned on. The range signal SG10 represents a range of data stored in the DRAM **34** of the image memory portion **16** out of the image signal SG1. The capture controller **29** outputs the generated range signal SG10 to the write controller **31** of the image memory 35 portion **16**.

The write controller **31** generates a write address, and makes a write request to the arbiter **33** for the range of the range signal SG**10** out of the image signal SG**11**. The write controller **31** outputs an image signal SG**11** of the write 40 request to the arbiter **33**. The read controller **32** generates a read address, and makes a read request to the arbiter **33**. The arbiter **33** coordinates and arbitrates the write request and the read request, and writes data to the DRAM **34** and reads data written in the DRAM **34**.

The read controller 32 outputs an image signal SG12 that has been read by the arbiter 33 to the data hold portion 36. Further, when the data enable signal SG7 is turned off, the read controller 32 holds a read address of DRAM34. As a result, the image signal SG12*a* output from the read controller 32 includes only the thinned data, when the data enable signal SG7 is turned on.

The data hold portion **36** possesses a memory of a capacity in which single line data out of the gate signal lines (that is, an image signal of source signal lines S1~SM) can 55 be stored. The data hold portion **36** stores image signal SG12*a* output from the read controller **32** in the memory. The data hold portion **36** outputs the image signal SG12*a* written in the memory to the selector **45** as image signals **12***b* every one horizontal scanning period (1H). 60

When the data enable signal SG7 is turned off, the data hold portion **36** holds a read address. As a result, the image signal SG12b at a time when data enable signal SG7 is turned off is the same as data when the data enable signal SG7 is turned on immediately before.

When the standby mode signal SG2 is turned off, the selector 45 outputs an input of the image signal SG1 to the

8

source drive circuit 14 as the image signal SG13. And when the standby mode signal SG2 is turned on and the regional signal SGa is turned on, the selector 45 outputs an input image signal SG1 to the source drive circuit 14 as the image signal SG13. And when the standby mode signal SG2 is turned on and the regional signal SGa is turned off, the selector 45 outputs an image signal SG12b output from the data hold portion 36 to the source drive circuit 14 as the image signal SG13.

The gate controller **27** generates a gate drive signal SG**8**. The gate controller **27** outputs the generated gate drive signal SG**8** to the gate drive circuit **13**. The gate drive signal SG**8** includes a gate start signal, a gate shift clock signal, and an output enable signal.

The gate controller **27** outputs a gate start signal after predetermined delay time from rising of the vertical synchronizing signal Vsync. The gate drive circuit **13** starts outputting a gate signal to the gate signal line **G1** in synchronization with the gate start signal. The gate controller **27** outputs a gate shift clock signal with the same period as the horizontal synchronizing signal Hsync. The gate drive circuit **13** switches the gate signal line to which the gate signal is output every time the gate shift clock signal is input.

The gate controller 27 outputs a signal obtained by delaying the output enable signal SG6 input from the interlaced scanning controller 26 by a predetermined time as an output enable signal. In the first embodiment, according to aftermentioned FIG. 7 shown, the output enable signal in the gate drive signal SG8 enables output of the gate signal from the gate drive circuit 13 at a low level, and masks output of the gate signal from the gate drive circuit 13 at a high level.

In the basic control mode, the gate drive circuit 13 applies a scan voltage (gate signal) progressively to the gate signal lines G1, G2, ..., GN in the sub scanning direction based on the gate drive signal SG8, and sequentially turns thin film transistors Q of the corresponding gate signal lines G1, G2, ..., GN on.

In the low frequency control mode, the gate drive circuit **13** repeats interlaced scanning of applying a scan voltage (gate signal) to the gate signal lines G**1**, G**2**, ..., GN every three gate signal lines based on the gate drive signal SG**8** in this embodiment, and sequentially turns the thin film transistors Q of the corresponding gate signal lines G**1**, G**2**, ..., GN on.

In the low frequency control mode, when the regional signal SGa is input, the gate drive circuit 13 turns the thin film transistors Q of the corresponding gate signal lines G1, G2, ..., GN on based on the gate drive signal SG8. Here, the gate drive circuit 13 repeats interlaced scanning of applying a scan voltage (gate signal) to the gate signal lines G1, G2, ..., GN every three gate signal lines in a region corresponding to a still picture. The gate drive circuit 13 applies a scan voltage (gate signal) progressively to the gate signal lines G1, G2, ..., GN in a region corresponding to moving picture.

The source controller **28** generates a latch timing signal SG**9** based on the data enable signal SG**7** from the interlaced scanning controller **26**. The source controller **28** outputs the generated latch timing signal SG**9** to the source drive circuit **14**.

The latch timing signal SG9 is for controlling operational timing of the source drive circuit 14. The latch timing signal SG9 is output in synchronization with the horizontal synchronizing signal Hsync. The latch timing signal SG9 indicates a leading head of the data input to the source drive

65

circuit 14. Specifically, the image signal SG13 is input to the source drive circuit 14 in synchronization with the latch timing signal SG9.

Further, the source drive circuit 14 outputs a voltage based on the image signal SG13 that has been input, to the source 5 signal lines in synchronization with the latch timing signal SG9. Specifically, the source drive circuit 14 outputs the voltage based on the image signal SG13 that has been input in synchronization with the latch timing signal SG9, to the source signal lines in synchronization with the latch timing 10 signal SG9 that comes next.

In this manner, when one latch timing signal SG9 is input to the source drive circuit 14, in synchronization with the input, the image signal SG13 is input to the source drive circuit 14, and the source drive circuit 14 outputs, to the 15 source signal lines, the voltage based on the image signal SG13 that has been input in synchronization with the previous latch timing signal SG9.

The source drive circuit 14 outputs a voltage (source signal) based on the input image signal SG13 to the source 20 signal lines S1, S2, ..., SM. This allows a voltage (source signal) based on the image signal SG13 to be applied to the pixels (liquid crystals) of the pixel electrodes R, G, and B corresponding to the gate signal lines G1, G2, ..., GN selected by the gate drive circuit 13 (that is, the pixel 25 electrodes whose thin film transistors Q are turned on), and thus transmittance of the pixels (liquid crystals) of pixel electrodes R, G, and B is controlled. In this embodiment, the liquid crystal display panel 12 corresponds to one example of the display portion, the gate drive circuit 13 corresponds 30 to one example of the gate driver, the source drive circuit 14 corresponds to one example of the source driver, the DRAM 34 corresponds to one example of an image storage, the moving picture region 120M corresponds to one example of the specific region, the still picture region 120S corresponds 35 to one example of the interlaced region.

FIG. 5 is a timing chart schematically showing main signals shown in FIG. 2 in a case in which the control mode shifts from a basic control mode to a low frequency control mode, and in the low frequency control mode, a part of a still 40 picture is shifted to a moving picture. An operation of the display device 1 according to the first embodiment will be described with reference to FIGS. 1 to 5.

Referring to FIG. 5, in frames FR1 and FR2, the image signal SG1 representing images IM1 and IM2 is input from 45 outside every frame in synchronization with the synchronizing signal SG0 (the vertical synchronizing signal Vsvnc). During this time, as described above, the synchronizing signal SG0 input from outside is output as the synchronizing signal SG3 from the synchronizing signal generator 21. In 50 this first embodiment, as images IM1 and IM2 are moving pictures, the standby mode signal SG2 is turned off. Therefore, the selector 45 outputs image signal SG1 representing images IM1 and IM2 as the image signals 13 to the source drive circuit 14.

When the standby mode signal SG2 is turned on at time to in the course of the frame FR2, the capture controller 29 generates the range signal SG10 corresponding to image signal SG1 representing the image IM3 in synchronization with the synchronizing signal SG0 that comes next. As a 60 result, the image signal SG11 representing the image IM3 is output from the write controller 31 by way of the arbiter 33 and stored in the DRAM 34.

In frames FR1 to FR3, because input images IM1 to IM3 are moving pictures, regional signal SGa is turned on during 65 an input of the image signal SG1. In addition, in frame FR3, the standby mode signal SG2 is turned on. Therefore, the

image IM3 which is input is a still picture from in and after the frame F3. However, in a step of the frame FR3, the image IM3 is a moving picture for the image IM2. As described later, after the frame FR3, a sub-frame appears. Specifically, one frame image is displayed with three sub-frames SF4 to SF6, three sub-frames SF7 to SF9 and three sub-frames SF10 to SF12.

In the sub-frame SF4 that comes next, the moving picture A4 shown in FIG. 4, that is image signal SG1 only representing the moving picture A4 displayed in a part of the display portion 120 in the liquid crystal display panel 12. And the regional signal SGa is turned on, while image signal SG1 representing the moving picture A4 is input during the time th to tc.

Therefore, in the sub-frame SF4, until the time th when the standby mode signal SG2 is turned on and the regional signal SGa is turned off, the selector 45 outputs the image signal SG12b output from the data hold portion 36 as the image signal SG13 to the source drive circuit 14. And, in the sub-frame SF4, from time tb to time tc when the standby mode signal SG2 is turned on and the regional signal SGa is turned on, the selector 45 outputs the image signal SG12binput from outside as the image signal SG13 to the source drive circuit 14. Further, in the sub-frame SF4, after time tc when an input of the image signal SG1 representing the moving picture A4 ends, and the standby mode signal SG2 is turned on and the regional signal SGa is turned off, the selector 45 outputs the image signal SG12b output from data hold portion 36 as the image signal SG13 to the source drive circuit 14.

In the sub-frames SF5 to SF12, the display device 1 operates in the same way as the sub-frame SF4. As a result, in the sub-frames SF 5 to SF12, mixing images of moving pictures A5 to A12 and a still picture IM3 are displayed in the liquid crystal display panel 12, respectively.

Further, at time td in the course of the sub-frame SF12, the standby mode signal SG2 is turned off. As a result, in the sub-frames SF 13 to SF 15, the selector 45 outputs the image signal SG1 representing frame images IM13 to IM15 which are moving pictures input from outside as the image signal SG13 to the source drive circuit 14

In addition, in the sub-frames SF4 to SF12, because image signal SG1 representing moving pictures A4 to A12 is continuously input from outside, the synchronizing signal SG0 is continuously input from outside. Therefore, in the sub-frames SF4 to SF12, the synchronizing signal generator 21 outputs the synchronizing signal SG0 from outside as the synchronizing signal SG3.

In the frames FR1 to FR3, the control mode is the basic control mode MD1. The frame frequency F1 is expressed by F1=60 Hz in this first embodiment. In the frames FR4 to FR12, the control mode is the low frequency control mode MD2. The frame frequency F2 is expressed by F2=20 Hz in this first embodiment. The frame frequency F2 is less than the frame frequency F1. In the frames FR13 to FR15, the control mode is the basic control mode MD1. The frame frequency F1 is expressed by F1=60 Hz in this first embodiment.

FIG. 6 is a diagram schematically showing polarities of voltages applied to one of the source signal lines (in this embodiment, e. g., the source signal line S1) in performing the operation shown in FIG. 5 of the control mode shifting from the basic control mode to the low frequency control mode and returning to the basic control mode from the low frequency control mode. In FIG. 6, similarly to FIG. 5, the frames FR1 to FR3, the sub-frames SF4 to SF12, and the frames FR13 to FR15 are shown, similarly to FIG. 5.

Further, in FIG. 6, the number N of the gate signal lines is expressed by N=12. A scanning to the gate signal lines in a case of an operation in FIG. 5 will be described with reference to FIGS. 4 to 6.

As described with reference to FIG. 5, in the frames FR1 5 to FR3 in FIG. 6, the control mode is the basic control mode MD1, and the frame frequency F1 for image display is expressed by F1=60 Hz. As shown in FIG. 6, pixel electrodes are driven in the column inversion drive mode taking the polarity of a voltage applied to the source signal line S1 in the frame FR1 as "-", the polarity of a voltage applied to the source signal line S1 in the frame FR2 as "+", and the polarity of a voltage applied to the source signal line S1 in the frame FR3 as "-"

As described with reference to FIG. 5, in the frame FR4, 15 the control mode is switched from the basic control mode MD1 to the low frequency control mode MD2. In the sub-frames SF4 to SF12, the control mode is the low frequency control mode MD2. In the low frequency control mode MD2, the frame frequency F2 is expressed by F2=20  $_{20}$ Hz. In the low frequency control mode MD2, scanned gate signal lines are thinned in a part of gate signal lines. This leads to reduction of power consumption.

Here, among gate signal lines G1 to G12 in FIG. 6, gate signal lines G1 to G3 correspond to the still picture region 25 120S shown in a upper part of FIG. 4, gate signal lines G4 to G6 correspond to the moving picture region 120M shown in FIG. 4 and gate signal lines G7 to G12 correspond to the still picture region 120S shown in a bottom part of FIG. 4.

Thus, in the sub-frames SF4 to SF12, the gate signal lines 30 G4 to G6 are not subjected to interlaced scanning, but are progressively scanned. In this manner, moving pictures A4 to A12 which partially consist of frame images are displayed in the gate signal lines G4 to G6 (the moving picture region 120M in FIG. 4) at the frame frequency of 60 Hz. It can 35 prevent image quality of moving pictures A4 to A12 from deteriorating.

On the other hand, the gate signal lines G1 to G3 and G7 to G12 are subjected to interlaced scanning every three gate signal lines at the frame frequency of 60 Hz, the interlaced 40 time t3 that comes next, a voltage corresponding to the scanning is repeated three times, and thus all of the gate signal lines G1 to G3 and G7 to G12 are scanned. In other words, three sub-frame images are respectively displayed in the three sub-frames SF4 to SF6 at 60 Hz. With this, the image IM3 which is one frame of a still image is displayed. 45 Similarly to sub-frames SF7 to SF9 and sub-frames SF10 to SF12, three sub-frame images are respectively displayed at 60 Hz, and then a still picture of the image IM3 which is a part of frame image is displayed. Thus, the frame images IM3, A4 and so on are displayed in the liquid crystal display 50 panel 12 at the frame frequency of 20 Hz.

Then, as described with reference to FIG. 5, the control mode returns to the basic control mode MD1 in the frame FR13, and a voltage is applied to the source signal line S1 at the frame frequency of F1, F1=60 Hz in the frames FR13 55 to FR15.

FIG. 7 is a timing chart schematically showing operations of the gate drive circuit and the source drive circuit in the sub-frame SF7 in FIG. 6 in which the control mode is the low frequency control mode MD2. Similarly to FIG. 6, in 60 FIG. 7, the number N of the gate signal lines is expressed by N=12, which comprises of gate signal lines G1 to G12. With reference to FIG. 2, FIG. 6, and FIG. 7, a description will be given of operations of the gate drive circuit 13 and the source drive circuit 14 in the sub-frame SF7 in FIG. 6 in 65 which the control mode is the low frequency control mode MD2.

In FIG. 7, first, the vertical synchronizing signal Vsync is output and the horizontal synchronizing signal Hsync is output in synchronization with rising of the vertical synchronizing signal Vsync. In synchronization with the latch timing signal SG9 at time t1 after the vertical synchronizing signal Vsync is output, the image signal SG13 corresponding to the gate signal line G1 is input to the source drive circuit 14 from the selector 45. A voltage based on the image signal SG13, that is, a voltage corresponding to the gate signal line G1 is output from the source drive circuit 14 in synchronization with the latch timing signal SG9 at time t2 that comes next.

On the other hand, at time t0 between time t1 and time t2, a gate start signal is output. Specifically, the gate controller 27 outputs the gate start signal after delay time of a time period (1+Tg)\*H (0≤Tg<1) from the rising of the vertical synchronizing signal Vsync. The delay time is the same as that in the basic control mode MD1. In other words, in the basic control mode MD 1, the gate controller 27 also outputs the gate start signal after the delay time of the time period (1+Tg)\*H from the rising of the vertical synchronizing signal Vsync.

At time t0, the output enable signal in the gate drive signal SG8 is turned on. Accordingly, a gate signal corresponding to the gate signal line G1 is output in synchronization with the gate start signal. Therefore, while the gate signal is output to the gate signal line G1, a voltage corresponding to the image signal D1 corresponding to the gate signal line G1 is output from the source drive circuit 14. Thus, a voltage corresponding to the image signal D1 is input to pixel electrodes.

Further, an image signal SG13 is input to the source drive circuit 14 from the selector 45 in synchronization with the latch timing signal SG9 at time t2. At time t2, the data enable signal SG7 is turned off. Therefore, this image signal SG13 is an image signal D1 when the data enable signal SG7 is turned on immediately before, that is, an image signal D1 corresponding to gate signal lines G1

In synchronization with the latch timing signal SG9 at image signal D1 that has been input in synchronization with the latch timing signal SG9 at time t2 is output to the source signal lines from the source drive circuit 14. However, as the output enable signal in the gate drive signal SG8 is turned off, a gate signal is not output to the gate signal line G2 from the gate drive circuit 13. Therefore, a voltage corresponding to the image signal that has been output to the source signal lines from the source drive circuit 14 is not applied to pixel electrodes.

Further, an image signal SG13 inputs to the source drive circuit 14 from the selector 45 in synchronization with the latch timing signal SG9 at time t3. At time t3, the data enable signal SG7 is turned off. Therefore, this image signal SG13 is an image signal D1 when the data enable signal SG7 is turned on immediately before, that is, an image signal D1 corresponding to gate signal lines G1

In synchronization with the latch timing signal SG9 at time t4 that comes next, a voltage corresponding to the image signal D1 that has been input in synchronization with the latch timing signal SG9 at time t3 is output to the source signal lines from the source drive circuit 14. However, as the output enable signal in the gate drive signal SG8 is turned off, a gate signal is not output to the gate signal line G3 from the gate drive circuit 13. Therefore, a voltage corresponding to the image signal that has been output to the source signal lines from the source drive circuit 14 is not applied to pixel electrodes.

Further, an image signal SG13 is input to the source drive circuit 14 from the selector 45 in synchronization with the latch timing signal SG9 at time t4. At time t4, the data enable signal SG7 is turned on. Therefore, this image signal SG13 is an image signal D4 corresponding to next gate signal lines 5 G4. As described with FIGS. 5 and 6, the standby mode signal SG2 is turned on and the regional signal SGa is turned on. Therefore, this image signal D4 is an image signal SG1 which had been input from outside.

In synchronization with the latch timing signal SG9 at 10 time t5 that comes next, a voltage corresponding to the image signal D4 that has been input in synchronization with the latch timing signal SG9 at time t4 is output to the source signal lines from the source drive circuit 14. At the time, the output enable signal in the gate drive signal SG8 is turned 15 on. Therefore, a voltage corresponding to the image signal D4 that is output to the source signal lines from the source drive circuit 14 is applied to pixel electrodes.

Further, an image signal SG13 is input to the source drive circuit 14 from the selector 45 in synchronization with the 20 latch timing signal SG9 at time t5. At time t5, the data enable signal SG7 is turned on. Therefore, this image signal SG13 is an image signal D5 corresponding to next gate signal lines G5. As described with FIGS. 5 and 6, the standby mode signal SG2 is turned on and the regional signal SGa is turned on. Therefore, this image signal D5 is an image signal SG1 input from outside.

In the latch timing signal SG9 at times t6 and t7 that come next, the data enable signal SG7 is continuously turned on. Thus, similarly to time t5, image signals D6 and D7 corre- 30 sponding to gate signal lines G6 and G7 are output to the source drive circuit 14 as the image signal SG13, respectively.

In the latch timing signal SG9 at times t6 and t7, the data enable signal SG7 in the gate drive signal SG8 is continu- 35 ously turned on. Thus, similarly to time t5, voltages corresponding to the image signals D5 and D6 are applied to pixel electrodes.

In synchronization with the latch timing signal SG9 at time t8 that comes next, a voltage corresponding to the 40 image signal D7 that has been input in synchronization with the latch timing signal SG9 at time t7 is output to the source signal lines from the source drive circuit 14. At the time, the output enable signal in the gate drive signal SG8 is turned on. Therefore, a voltage corresponding to the image signal 45 D7 that is output to the source signal lines from the source drive circuit 14 is applied to pixel electrodes.

Further, an image signal SG13 is input to the source drive circuit 14 from the selector 45 in synchronization with the latch timing signal SG9 at time t8. At time t8, the data enable 50 signal SG7 is turned off. Therefore, this image signal SG13 is an image signal D7 when the data enable signal SG7 is turned on immediately before, that is, an image signal D7 corresponding to gate signal lines G7.

time t9 that comes next, a voltage corresponding to the image signal D7 that has been input in synchronization with the latch timing signal SG9 at time t8 is output to the source signal lines from the source drive circuit 14. However, the output enable signal in the gate drive signal SG8 is turned 60 off. Thus, a gate signal is not output to the gate signal line G2 from the gate drive circuit 13. Therefore, a voltage corresponding to the image signal D7 that has been output to the source signal lines from the source drive circuit 14 is not applied to pixel electrodes. 65

Further, an image signal SG13 is input to the source drive circuit 14 from the selector 45 in synchronization with the latch timing signal SG9 at time t9. At time t9, the data enable signal SG7 is turned off. Therefore, this image signal SG13 is an image signal D7 when the data enable signal SG7 is turned on immediately before, that is, an image signal D7 corresponding to gate signal lines G7.

In synchronization with the latch timing signal SG9 at time t9 that comes next, a voltage corresponding to the image signal D7 that has been input in synchronization with the latch timing signal SG9 at time t9 is output to the source signal lines from the source drive circuit 14. However, the output enable signal in the gate drive signal SG8 is turned off. Thus, a gate signal is not output to the gate signal line G2 from the gate drive circuit 13. Therefore, a voltage corresponding to the image signal D7 that has been output to the source signal lines from the source drive circuit 14 is not applied to pixel electrodes.

Further, an image signal SG13 is input to the source drive circuit 14 from the selector 45 in synchronization with the latch timing signal SG9 at time t10. At time t10, the data enable signal SG7 is turned on. Therefore, this image signal SG13 is an image signal D10 corresponding to next gate signal line SG10. As described with FIGS. 5 and 6, the standby mode signal SG2 is turned on and the regional signal SGa is turned on. Therefore, this image signal D10 is an image signal SG12b output from the data hold portion 36.

At times t11 to t13 which come next, the same operation is performed similarly to times t8 to t10. In FIG. 10, gate signals are not output to the gate signal lines G2, G3, and G10, and so they are indicated by broken lines.

Here, in the sub-frame SF4 of the low frequency control mode MD2 shown in FIG. 7, a description will be given of a relation between an interval of scanning of the gate signal lines by the gate drive circuit 13 and a voltage output from the source drive circuit 14.

In the low frequency control mode MD2 shown in FIG. 7, the gate drive circuit 13 first scans the first gate signal line G1, and then the fourth gate signal line G4, for example. In this case, the data controller 30 causes the source drive circuit 14 to output a voltage corresponding to the first gate signal line G1 output from the source drive circuit 14 in response to the scanning of the first gate signal line G1 continuously for a period 3H. Specifically, for two horizontal scanning period 2H corresponding to the gate signal lines G2 and G3 that are not scanned, a voltage corresponding to the image signal D7 output corresponding to the gate signal line G1 is continuously output.

Further, the gate drive circuit 13 scans, for example, the fourth gate signal line G4, and then the fifth gate signal line G5. In this case, the data controller 30 causes the source drive circuit 14 to output a voltage corresponding to the image signal D4 output from the source drive circuit 14 in response to the scanning of the fourth gate signal line G4 continuously for one horizontal scanning period 1H.

Further, the gate drive circuit 13 scans, for example, the In synchronization with the latch timing signal SG9 at 55 fifth gate signal line G5, and then the sixth gate signal line G6. In this case, the data controller 30 causes the source drive circuit 14 to output a voltage corresponding to the image signal D5 output from the source drive circuit 14 in response to the scanning of the fifth gate signal line G5 continuously for one horizontal scanning period 1H. This also applies to a case of the next seventh gate signal line G7

> Further, the gate drive circuit 13 scans, for example, the seventh gate signal line G7, and then the tenth gate signal line G10. In this case, the data controller 30 causes the source drive circuit 14 to output a voltage corresponding to the image signal D5 output from the source drive circuit 14 in response to the scanning of the seventh gate signal line G7

continuously for three horizontal scanning period 3H. Specifically, for the horizontal scanning period 2H corresponding to the gate signal lines G7 and G8 that are not scanned, a voltage corresponding to the image signal D7 output corresponding to the gate signal line G7 is continuously <sup>5</sup> output.

In this manner, in the low frequency control mode MD2, in a case in which the gate drive circuit **13** first scans a U-th gate signal line out of the N gate signal lines (U is an integer that is not less than 1 and less than N), and then a (U+V)-th<sup>10</sup> gate signal line (V is an integer that is not less than 1 and not greater than K), the data controller **30** causes the source drive circuit **14** to output a voltage output from the source drive circuit **14** in response to scanning of the U-th gate signal line for a period V\*H (V times of the horizontal scanning period 1H).

As described above, in the first embodiment, after the control mode is switched from the basic control mode MD1 to the low frequency control mode MD2, the image signal 20 SG1 representing a moving picture which is displayed in a part of the display portion **120** of the liquid crystal display panel **12** is input, and then a mixing image of the moving picture and the still picture is displayed in the display portion **120**. At the time, the gate signal lines corresponding to the <sup>25</sup> region of the moving picture are progressively scanned at the frequency of 60 Hz. As a result, according to the first embodiment, it is possible to prevent image qualities of moving pictures from excessively deteriorating.

Further, in this first embodiment, image signal SG1 rep-<sup>30</sup> resenting a still picture is stored in the DRAM **34**, and then the image signal SG1 is read from the DRAM **34** and is displayed in the liquid crystal display panel **12**. Therefore, it is possible to prevent power consumption from increasing.

Further, in this first embodiment, at timings at which gate <sup>35</sup> signals are output to the gate signal lines G2, G3, G8, G9, G11, and G11, the source drive circuit 14 outputs a voltage which had been output immediately before, that is, the voltage based on image signal D1, D7 and D10 corresponding to the gate signal lines G1, G7, and G10. As a result, as <sup>40</sup> compared to a case where the source drive circuit 14 outputs different voltages, wasteful discharge and charge may not occur in the source drive circuit 14. Therefore, it is possible to prevent power consumption from increasing.

Further, in the first embodiment, a voltage is output from 45 the source drive circuit **14** every time the latch timing signal SG9 is output. However, at timing at which gate signals are output to the gate signal lines G2, G3, G8, G9, G11 and G12, the output enable signal in the gate drive signal SG8 is turned off, and gate signals are not output from the gate drive <sup>50</sup> circuit **13** to the gate signal lines G2, G3, G8, G9, G11 and G12. Therefore, it is possible to preferably perform mixing operation of interlaced scanning and progressive scanning of the gate signal lines G1 to G12 with a configuration in which the latch timing signal SG9 is output every time the hori- <sup>55</sup> zontal synchronizing signal Hsync is output.

#### Second Embodiment

FIG. **8** is a block diagram showing a configuration of a 60 controller and an image memory portion of a display device according to a second embodiment. FIG. **9** is a block diagram showing a configuration of a data controller shown in FIG. **8**. FIG. **10** is a truth table of a selector in a data delay portion shown in FIG. **9**. In the second embodiment, similar 65 components as in the first embodiment are denoted by similar reference numerals.

The configuration of the display device according to the second embodiment is substantially the same as the display device 1 according to the first embodiment shown in FIG. 1. The display device according to the second embodiment includes a controller 11a in place of the controller 11 according to the first embodiment. In the second embodiment, similarly to the first embodiment, a frame frequency F1 in the basic control mode is expressed by F1=60 Hz, and a frame frequency F2 in the low frequency control mode is expressed by F2=20 Hz. Therefore, similarly to the first embodiment, in the second embodiment, K=F1/F2=3. Hereinafter, the second embodiment will be described focusing on differences from the first embodiment.

Referring to FIG. 8, the controller 11a includes the synchronizing signal generator 21, the interlaced scanning controller 26, the gate controller 27, a source controller 28*a*, the capture controller 29, and a data controller 30*a*. The data controller 30*a* includes a selector 45, a data delay control portion 61, a data delay portion 62 and the selector 63.

Referring to FIG. 9, the data delay controller 61 includes delay circuits 71 to 73, a selector 75, a selection signal generator 76, and an inverter 77. The data delay portion 62 includes line memories (LMs) 81 and 82, a dummy data generator 84, and a selector 85.

The interlaced scanning controller **26** outputs the generated data enable signal SG7 to the delay circuit **71**, the selector **75**, and the selection signal generator **76** of the data delay controller **61**. The delay circuit **71** delays the data enable signal SG7 by one horizontal scanning period (1H), and outputs a delayed data enable signal SG7D1 to the delay circuit **72**.

The delay circuit **72** delays the data enable signal SG7D2 further by 1H, and outputs a delayed data enable signal SG7D2 to the delay circuit **73** and the selection signal generator **76**. Further, the delay circuit **72** outputs the data enable signal SG7D2 to the gate controller **27** via the inverter **77**. The delay circuit **73** delays the data enable signal SG7D2 further by 1H, and outputs a delayed data enable signal SG7D3 to the selector **75**.

The selector **75** outputs the data enable signal SG**7** as the data enable signal SG**7** to the selection signal generator **76** at the head of a frame, that is, immediately after the vertical synchronizing signal Vsync. If not at the head of the frame, the selector **75** outputs the data enable signal SG**70** as the data enable signal SG**70** to the selection signal generator **76**. The selector **75** also outputs the data enable signal SG**70** to the source controller **28***a*.

The source controller 28a outputs the latch timing signal SG9 to the source drive circuit 14 in synchronization with the horizontal synchronizing signal Hsync when the data enable signal SG70 is turned on. The source controller 28a does not output the latch timing signal SG9 to the source drive circuit 14 when the data enable signal SG70 is turned off. In this manner, unlike the source controller 28a of the first embodiment, an interval at which the latch timing signal SG9 is econd embodiment is not a constant one-horizontal scanning period (1H).

The selection signal generator **76** outputs, as a selection signal SG**22** to the selector **85**, information indicating whether each of the data enable signals SG**7**, SG**7D1** to SG**7D2**, and SG**70** that are input is enabled or disabled.

The read controller 32 outputs an image signal SG12*a* that has been read to the selector 63. The selector 63 outputs the image signal SG1 which had been input from outside as an image signal SG21 to a line memory 81 of the data delay portion 62 and the selector 85 while the regional signal SGa is turned on. Further, the selector **63** outputs the image signal SG1 which had been input from the read controller **32** as an image signal SG**21** to the line memory **81** of data delay portion **62** and the selector **85** while the regional signal SGa is turned off.