# (12) United States Patent Beck et al.

## (54) GROUND FAULT CIRCUIT INTERRUPTER AND METHOD

(71) Applicant: SEMICONDUCTOR COMPONENTS

INDUSTRIES, LLC, Phoenix, AZ

(US)

Inventors: Riley D. Beck, Eagle Mountain, UT

(US); Kent D. Layton, Lehi, UT (US)

Assignee: SEMICONDUCTOR COMPONENTS

INDUSTRIES, LLC, Phoenix, AZ

Subject to any disclaimer, the term of this (\*) Notice:

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

Appl. No.: 15/132,775

(22)Filed: Apr. 19, 2016

(65)**Prior Publication Data**

> US 2016/0233837 A1 Aug. 11, 2016

#### Related U.S. Application Data

- (60) Division of application No. 13/829,366, filed on Mar. 14, 2013, now Pat. No. 9,331,469, which is a (Continued)

- (51) **Int. Cl.** G01R 31/14 (2006.01)H03F 1/30 (2006.01)(Continued)

- (52) U.S. Cl. CPC ...... H03F 1/303 (2013.01); G01R 27/18 (2013.01); G01R 31/025 (2013.01); (Continued)

# US 9,680,421 B2

(45) **Date of Patent:** Jun. 13, 2017

#### (58)Field of Classification Search

(10) Patent No.:

CPC ...... G01R 31/025; H02H 1/0092; H03F 2203/45288; H03F 2203/45

(Continued)

#### (56)References Cited

#### U.S. PATENT DOCUMENTS

2/1974 Sircom 3,794,884 A 3,879,639 A 4/1975 Sircom (Continued)

## OTHER PUBLICATIONS

Kugelstadt, Thomas. "Auto-zero amplifiers ease the design of high-precision circuits."  $2^{nd}$  quarter, 2005, Analog Applications Journal, Texas Instruments Incorporated.\* (Continued)

Primary Examiner — Patrick Assouad Assistant Examiner — Sean Curtis

(74) Attorney, Agent, or Firm — Rennie William Dover

#### ABSTRACT

A method and circuit for dynamically correcting offsets associated with an AC power system. In an embodiment, a first offset current generated in response to a ground to neutral fault stimulus is decreased and a second offset current generated in response to a differential fault stimulus is decreased. In another embodiment, the circuit includes an offset correction circuit that has one of a chopper circuit or an auto-zeroing circuit. An amplifier is connected to the offset correction circuit and an output connected to the offset correction circuit. A signal generator is switchably coupled to a first input of the offset correction circuit and a bias generator is switchably coupled to the first input of the offset correction circuit.

#### 15 Claims, 13 Drawing Sheets

| Related U.S. Application Data |                                                                                                    |            |                                            | 7,323,934                                                               |                                                                 |              | Huang                                    |  |

|-------------------------------|----------------------------------------------------------------------------------------------------|------------|--------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|--------------|------------------------------------------|--|

|                               | continuation-in-part of application No. 12/572,870, filed on Oct. 2, 2009, now Pat. No. 8,390,297. |            |                                            | 7,336,457                                                               |                                                                 |              | Liscinsky, III                           |  |

|                               |                                                                                                    |            |                                            | 7,684,162                                                               |                                                                 |              | Musat et al.<br>Lewinski et al.          |  |

|                               | med on Oct.                                                                                        | 2, 2009,   | now Pat. No. 8,390,297.                    | 8,018,235                                                               |                                                                 |              |                                          |  |

|                               |                                                                                                    |            |                                            | 8,054,593<br>8,085,516                                                  | D1                                                              |              | Reid et al.                              |  |

| (51)                          | Int. Cl.                                                                                           |            |                                            |                                                                         |                                                                 |              | Armstrong                                |  |

|                               | H02H 3/16                                                                                          |            | (2006.01)                                  | 8,217,644<br>8,390,297                                                  |                                                                 |              | Younsi et al.<br>Beck                    |  |

|                               | G01R 27/18                                                                                         |            | (2006.01)                                  | 8,390,297                                                               | DZ.                                                             | 3/2013       |                                          |  |

|                               | H02H 3/33                                                                                          |            | (2006.01)                                  | 0.096.400                                                               | Da                                                              | 7/2015       | 324/509                                  |  |

|                               |                                                                                                    |            | ,                                          | 9,086,400<br>9,124,094                                                  |                                                                 |              | Minch et al.                             |  |

|                               | G01R 31/02                                                                                         |            | (2006.01)                                  |                                                                         |                                                                 |              | Beck                                     |  |

|                               | H03F 3/45                                                                                          |            | (2006.01)                                  | 9,276,393<br>9,329,216                                                  |                                                                 |              | Ostrovsky H02H 1/0015<br>Beck G01R 27/18 |  |

|                               | H02H 1/00                                                                                          |            | (2006.01)                                  | 9,329,210                                                               |                                                                 |              | Beck                                     |  |

|                               | H02H 1/04                                                                                          |            | (2006.01)                                  | 9,331,469                                                               |                                                                 |              | Beck H01H 83/02<br>Beck H02H 3/162       |  |

|                               | U.S. Cl.                                                                                           |            | (2000.01)                                  | 9,411,003                                                               |                                                                 |              | Danesh                                   |  |

|                               |                                                                                                    | 77.007     | T 2/1/2 (2012 01) TT02TT 2/22              | 9,478,969                                                               |                                                                 |              | Beck                                     |  |

|                               |                                                                                                    |            | <i>I 3/162</i> (2013.01); <i>H02H 3/33</i> | 2003/0156367                                                            |                                                                 |              | Macbeth                                  |  |

|                               | (2                                                                                                 | 2013.01);  | ; <i>H03F 3/45</i> (2013.01); <i>H02H</i>  | 2005/0083616                                                            |                                                                 |              | Reid et al.                              |  |

|                               | 1/                                                                                                 | 0092 (20   | 13.01); <i>H02H 1/04</i> (2013.01);        | 2006/0125622                                                            |                                                                 |              | Baldwin et al.                           |  |

|                               |                                                                                                    | ,          | 2203/45152 (2013.01); H03F                 | 2008/0022153                                                            |                                                                 |              | Wang et al.                              |  |

|                               | 22/                                                                                                |            | (2013.01); <i>H03F 2203/45288</i>          | 2008/0106269                                                            |                                                                 |              | Lewinski et al.                          |  |

|                               | 220                                                                                                | 13/43220   |                                            | 2010/0290164                                                            |                                                                 | 11/2010      |                                          |  |

|                               |                                                                                                    |            | (2013.01)                                  | 2011/0080177                                                            |                                                                 |              | Beck G01R 27/18                          |  |

| (58)                          | Field of Clas                                                                                      | sificatio  | n Search                                   |                                                                         |                                                                 |              | 324/509                                  |  |

|                               | USPC                                                                                               |            |                                            | 2011/0216452                                                            | A1                                                              | 9/2011       | Haines et al.                            |  |

|                               | See application                                                                                    | on file fo | r complete search history.                 | 2011/0221600                                                            |                                                                 |              | Kinsel et al.                            |  |

|                               | ore apparent                                                                                       |            | r compress source morely.                  | 2013/0128396                                                            |                                                                 | 5/2013       | Danesh G01R 19/00                        |  |

| (56)                          |                                                                                                    | Deferen    | ces Cited                                  |                                                                         |                                                                 |              | 361/45                                   |  |

| (30)                          |                                                                                                    | Keleren    | ces Cheu                                   | 2013/0214800                                                            | A1*                                                             | 8/2013       | Beck G01R 27/18                          |  |

|                               | II S II                                                                                            | DATENIT    | DOCUMENTS                                  |                                                                         |                                                                 |              | 324/691                                  |  |

|                               | 0.5.                                                                                               | ALLINI     | DOCUMENTS                                  | 2013/0215537                                                            | A1*                                                             | 8/2013       | Beck H02H 3/162                          |  |

| 4                             | ,001,646 A                                                                                         | 1/1077     | Howell                                     |                                                                         |                                                                 |              | 361/42                                   |  |

|                               | ,001,040 A<br>,012,668 A                                                                           |            | Wittlinger                                 | 2013/0229734                                                            | A1*                                                             | 9/2013       | Beck H02H 3/162                          |  |

|                               | ,012,008 A<br>,021,729 A                                                                           |            | Hudson, Jr.                                |                                                                         |                                                                 |              | 361/42                                   |  |

|                               | .150.411 A                                                                                         |            | Howell                                     | 2014/0092503                                                            | A1*                                                             | 4/2014       | Ostrovsky H02H 1/0015                    |  |

|                               | ,378,579 A                                                                                         |            | Hudson, Jr.                                |                                                                         |                                                                 |              | 361/45                                   |  |

|                               | ,206,600 A                                                                                         |            | Moehlmann                                  | 2014/0210484                                                            | A1*                                                             | 7/2014       | Beck H02H 3/044                          |  |

|                               | ,459,630 A                                                                                         |            | MacKenzie et al.                           |                                                                         |                                                                 |              | 324/509                                  |  |

|                               | ,508,607 A                                                                                         |            | Gibson                                     | 2014/0268435                                                            | A1*                                                             | 9/2014       | Beck H02H 3/283                          |  |

|                               | ,515,001 A                                                                                         | 5/1996     | Vranish                                    |                                                                         |                                                                 |              | 361/42                                   |  |

| 5                             | ,600,524 A                                                                                         | 2/1997     | Neiger et al.                              | 2016/0006234                                                            | A1*                                                             | 1/2016       | Ostrovsky H02H 1/0015                    |  |

| 5                             | ,715,125 A                                                                                         | 2/1998     | Neiger et al.                              |                                                                         |                                                                 |              | 361/86                                   |  |

| 5                             | ,808,574 A                                                                                         | 9/1998     | Johnson et al.                             | 2016/0233837                                                            | A1*                                                             | 8/2016       | Beck H02H 3/162                          |  |

|                               | ,111,733 A                                                                                         |            | Neiger et al.                              | 2016/0238644                                                            | A1*                                                             |              | Beck G01R 27/18                          |  |

|                               | ,259,996 B1                                                                                        |            | Haun et al.                                |                                                                         |                                                                 |              |                                          |  |

|                               | 6,421,214 B1 7/2002 Packard et al.                                                                 |            |                                            |                                                                         | OTI                                                             | TED DIE      | DI ICATIONE                              |  |

|                               | 6,426,632 B1 7/2002 Clunn                                                                          |            |                                            |                                                                         | OH                                                              | HEK PU.      | BLICATIONS                               |  |

|                               | ,618,648 B1                                                                                        |            | Shirota et al.                             |                                                                         |                                                                 |              |                                          |  |

|                               | 6,674,289 B2 1/2004 Macbeth                                                                        |            |                                            |                                                                         | McEachern, Alexander, A floating-window algorithm for detecting |              |                                          |  |

|                               | 6,807,035 B1 10/2004 Baldwin et al.<br>6,807,036 B2 10/2004 Baldwin                                |            | certain power lin                          | certain power line faults that disrupt sensitive electronic loads, IEEE |                                                                 |              |                                          |  |

|                               | ,807,036 B2                                                                                        |            |                                            | Trans. on Inst. a                                                       | and Me                                                          | eas., vol. 3 | 39, No. 1, Feb. 1990, pp. 112-115.       |  |

|                               | ,873,158 B2                                                                                        |            | Macbeth                                    |                                                                         |                                                                 |              | signal processing algorithm for          |  |

|                               | ,946,828 B1<br>,980,005 B2                                                                         | 9/2005     | Finlay, Sr. et al.                         |                                                                         |                                                                 |              | distribution feeders, IEEE Trans.        |  |

|                               | ,980,005 B2<br>,079,365 B2                                                                         |            | Brown et al.                               |                                                                         |                                                                 |              | 1, Jan. 1989, pp. 132-140.               |  |

|                               | ,079,365 B2<br>,154,718 B1                                                                         |            | Finlay, Sr.                                |                                                                         | -5, .0                                                          | ., 1.01      | ,, FF. 102 1.00                          |  |

|                               | ,253,629 B1                                                                                        |            | Richards et al.                            | * cited by exa                                                          | miner                                                           | ,            |                                          |  |

| ,                             | ,233,023 11                                                                                        | 0/200/     | rachards et al.                            | ched by exa                                                             | mincl                                                           |              |                                          |  |

<sup>\*</sup> cited by examiner

Fig. 2

## GROUND FAULT CIRCUIT INTERRUPTER AND METHOD

The present patent application is a divisional application of prior U.S. patent application Ser. No. 13/829,366, filed on Mar. 14, 2013, by Riley D. Beck et al., titled "Ground Fault Circuit Interrupter and Method," which is a continuationin-part application of prior U.S. patent application Ser. No. 12/572,870, filed on Oct. 2, 2009, now U.S. Pat. No. 8,390,297 issued Mar. 5, 2013 by Riley D. Beck et al., titled "Ground Fault Circuit Interrupter and Method," which applications are hereby incorporated by reference in their entirety, and priority thereto for common subject matter is hereby claimed.

#### BACKGROUND

The present invention relates, in general, to measurement systems and, more particularly, to the measurement systems 20 for electrical signals.

Circuits for measuring or calculating electrical signals such as current, voltage, and power and circuits for measuring or calculating electrical parameters such as impedance, admittance, phase relationships are used in a variety of 25 applications including impedance measurements, load detection and calibration, security systems, smart grids, sensor interfaces, automotive systems, self-test systems, etc. For example, circuits used for determining the impedance of so that the current flowing through the resistor can be used to determine the current flowing through the load. Drawbacks with this technique are the reduction of the input voltage range, the consumption of large areas of semiconductor material to manufacture the circuits, frequency limi- 35 tations of the circuit elements, and the need for highly accurate circuit elements.

In some applications it may be desirable to detect a ground fault condition. One technique for detecting this condition is to establish resonance in an inductor-resistor- 40 capacitor network when it is exposed to a ground-to-neutral condition. Resonance may be established by delivering a pulse to a positive feedback system that includes an operational amplifier. Alternatively, a steady state stimulus can be delivered to the circuit, which is then monitored for signifi- 45 cant changes in the waveform profile. Drawbacks with these techniques are that they are prone to temperature and manufacturing shifts which reduce the accuracy of detec-

Accordingly, it would be advantageous to have a circuit 50 and method for determining electrical signals and electrical parameters of a circuit element. It would be of further advantage for the circuit and method to be cost efficient to implement.

## BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will be better understood from a reading of the following detailed description, taken in conjunction with the accompanying drawing figures, in which 60 like reference characters designate like elements and in which:

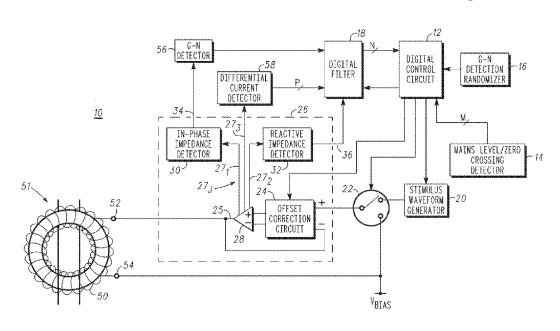

FIG. 1 is a block diagram of a measurement circuit in accordance with an embodiment of the present invention;

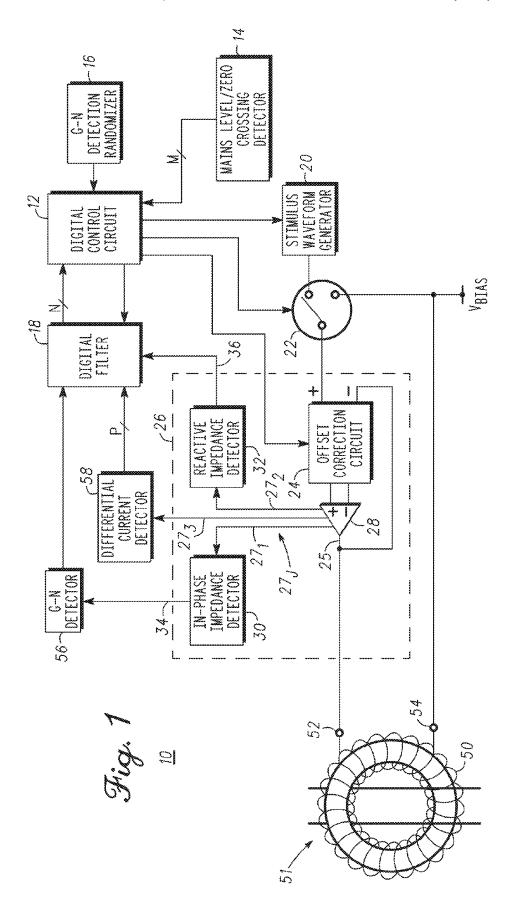

FIG. 2 is a block diagram of a portion of a measurement 65 circuit in accordance with an embodiment of the present invention;

2

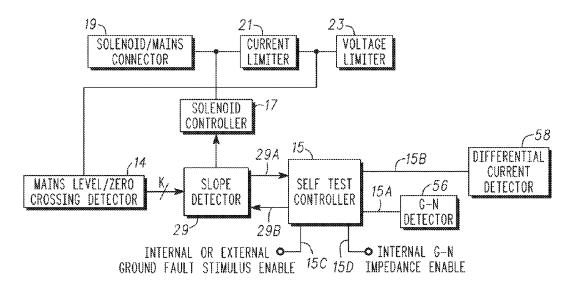

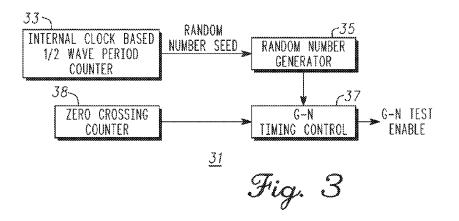

FIG. 3 is a block diagram of a circuit module for randomizing the timing of the ground-to-neutral measurements in accordance with embodiments of the present invention;

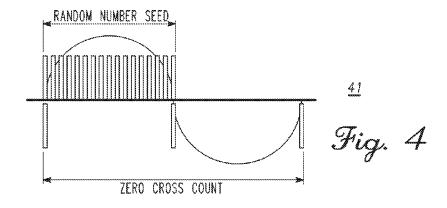

FIG. 4 is a waveform for randomizing the timing of the ground-to-neutral measurements in accordance with embodiments of the present invention;

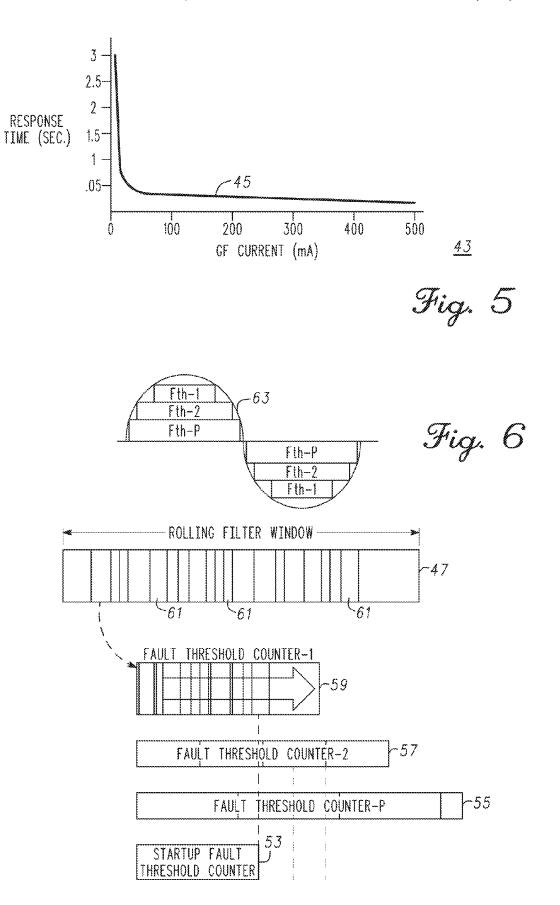

FIG. 5 is a timing diagram for a portion of the circuit module of FIG. 1;

FIG. 6 illustrates a threshold diagram for a portion of the circuit module of FIG. 1;

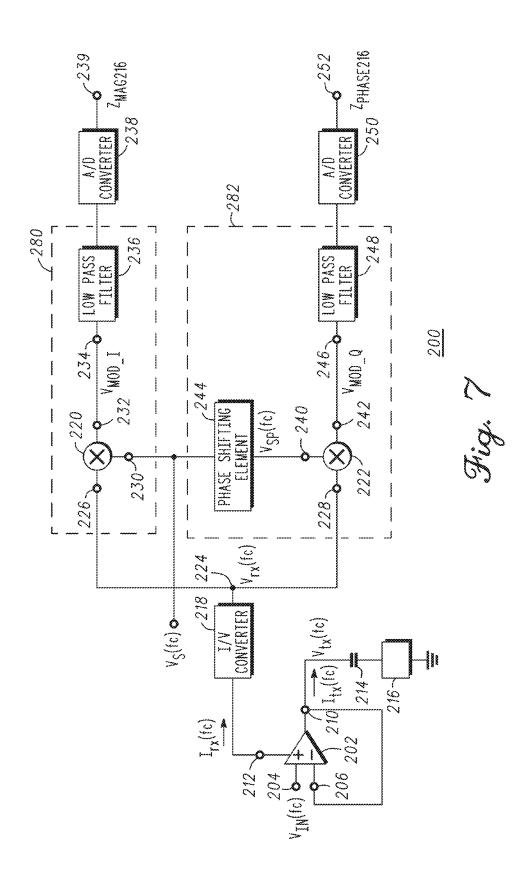

FIG. 7 is a schematic diagram of a measurement circuit in accordance with another embodiment of the present inven-

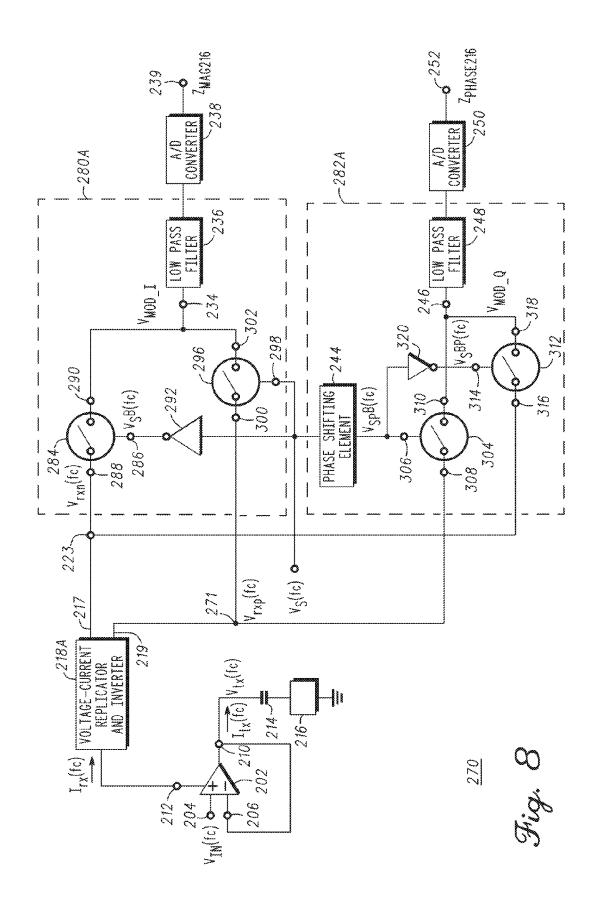

FIG. 8 is a schematic diagram of a measurement circuit in 15 accordance with another embodiment of the present invention;

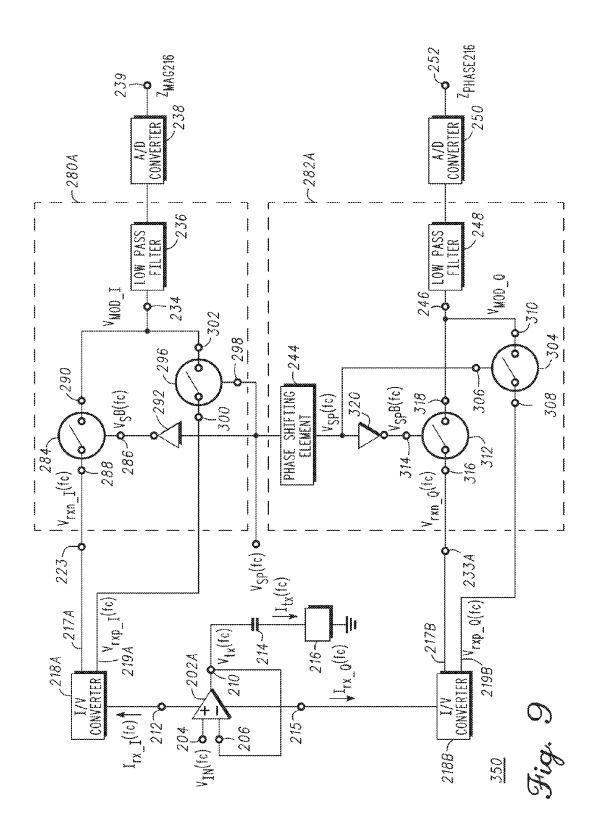

FIG. 9 is a schematic diagram of a measurement circuit in accordance with another embodiment of the present inven-

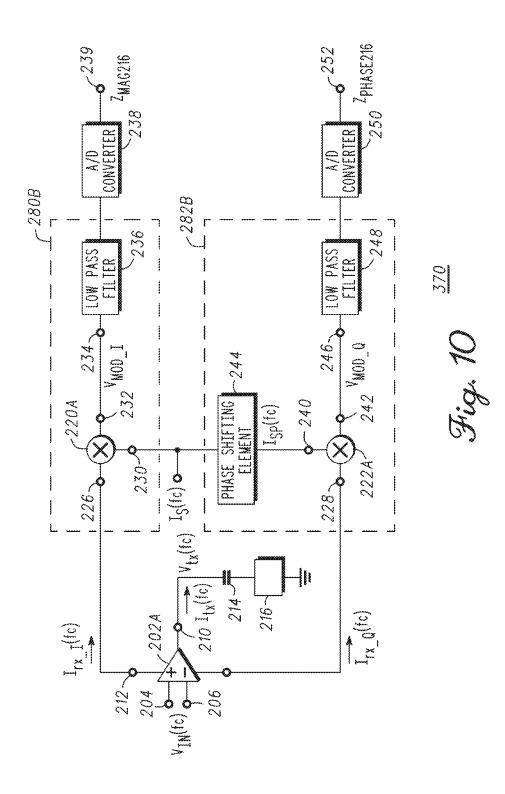

FIG. 10 is a schematic diagram of a measurement circuit in accordance with another embodiment of the present invention;

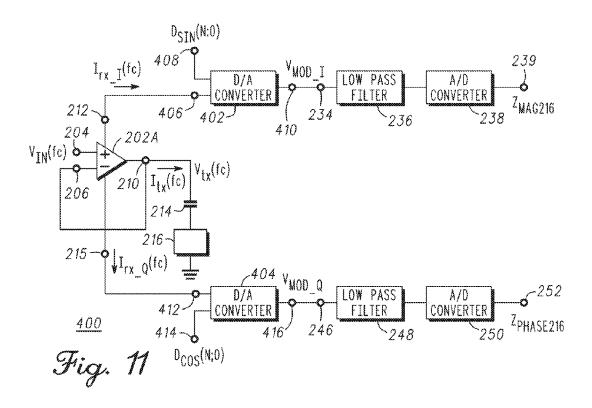

FIG. 11 is a schematic diagram of a measurement circuit in accordance with another embodiment of the present invention;

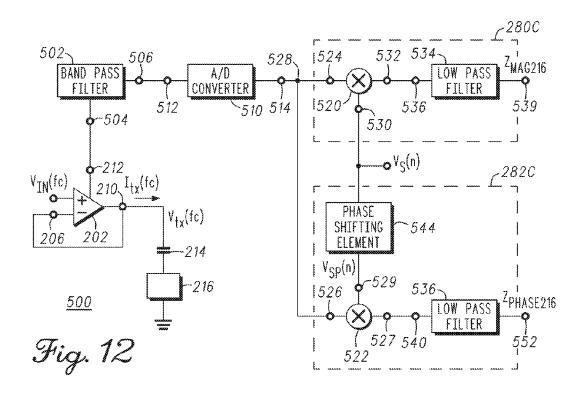

FIG. 12 is a schematic diagram of a measurement circuit in accordance with another embodiment of the present invention:

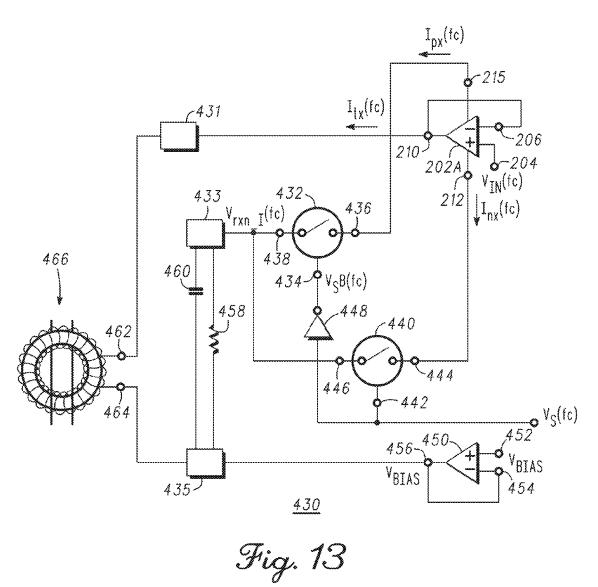

FIG. 13 is a schematic diagram of a measurement circuit a system may include a resistor placed in series with a load 30 in accordance with another embodiment of the present invention:

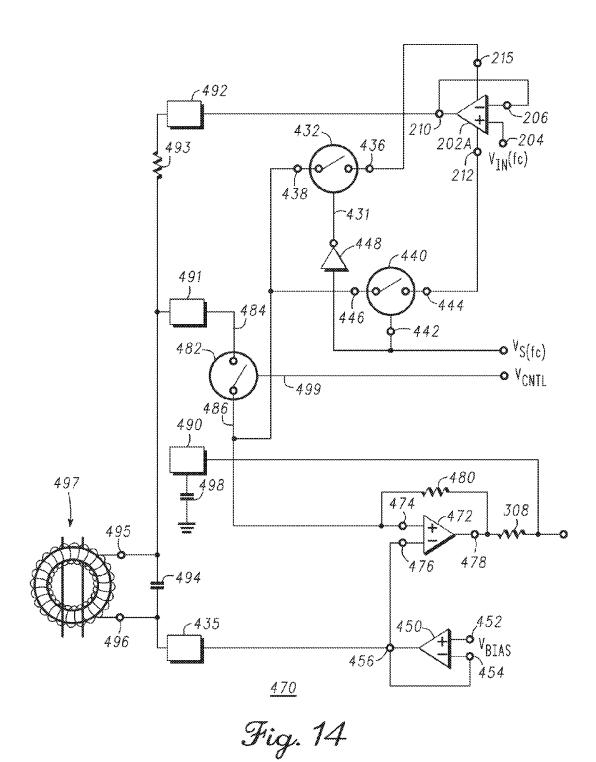

> FIG. 14 is a schematic diagram of a measurement circuit in accordance with another embodiment of the present

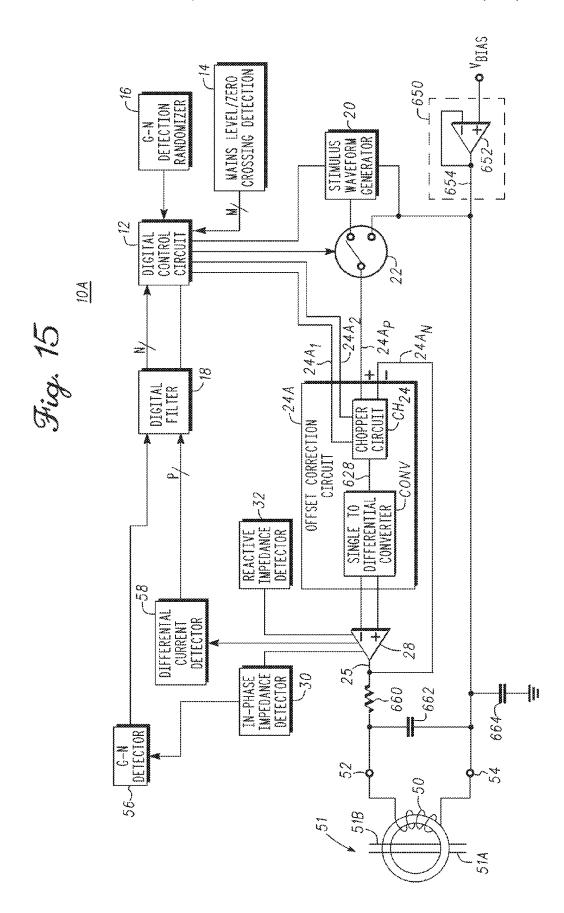

FIG. 15 is a schematic diagram of an offset correction circuit in accordance with another embodiment of the present invention:

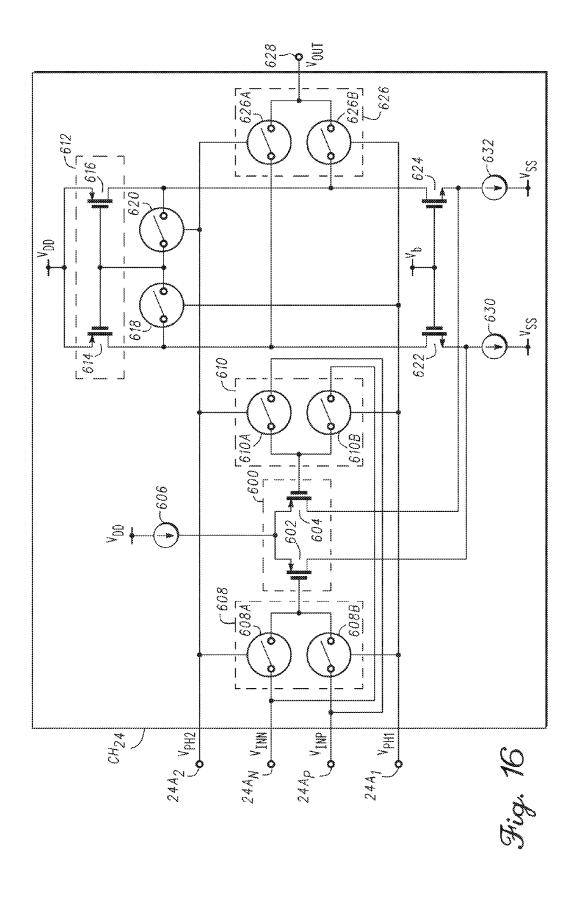

FIG. 16 is a schematic diagram of a chopper module in accordance with an embodiment of the present invention;

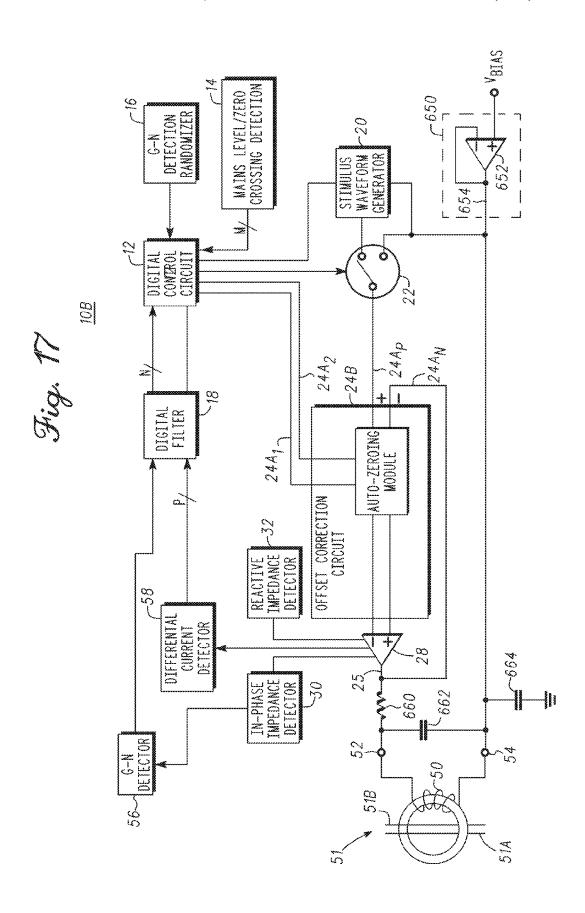

FIG. 17 is a schematic diagram of an offset correction circuit in accordance with another embodiment of the present invention.

For simplicity and clarity of illustration, elements in the figures are not necessarily to scale, and the same reference characters in different figures denote the same elements. Additionally, descriptions and details of well-known steps and elements are omitted for simplicity of the description. As used herein current carrying electrode means an element of a device that carries current through the device such as a source or a drain of an MOS transistor or an emitter or a collector of a bipolar transistor or a cathode or an anode of a diode, and a control electrode means an element of the device that controls current flow through the device such as 55 a gate of an MOS transistor or a base of a bipolar transistor. Although the devices are explained herein as certain n-channel or p-channel devices, or certain n-type or p-type doped regions, a person of ordinary skill in the art will appreciate that complementary devices are also possible in accordance with embodiments of the present invention. It will be appreciated by those skilled in the art that the words during, while, and when as used herein are not exact terms that mean an action takes place instantly upon an initiating action but that there may be some small but reasonable delay, such as a propagation delay, between the reaction that is initiated by the initial action and the initial action. The use of the words approximately, about, or substantially means that a value of

an element has a parameter that is expected to be very close to a stated value or position. However, as is well known in the art there are always minor variances that prevent the values or positions from being exactly as stated. It is well established in the art that variances of up to about ten per cent (10%) (and up to twenty per cent (20%) for semiconductor doping concentrations) are regarded as reasonable variances from the ideal goal of exactly as described.

3

It should be noted that a logic zero voltage level  $(V_I)$  is also referred to as a logic low voltage or logic low voltage level and that the voltage level of a logic zero voltage is a function of the power supply voltage and the type of logic family. For example, in a Complementary Metal Oxide Semiconductor (CMOS) logic family a logic zero voltage may be thirty percent of the power supply voltage level. In a five volt Transistor-Transistor Logic (TTL) system a logic zero voltage level may be about 0.8 volts, whereas for a five volt CMOS system, the logic zero voltage level may be about 1.5 volts. A logic one voltage level  $(V_H)$  is also 20 referred to as a logic high voltage level, a logic high voltage, or a logic one voltage and, like the logic zero voltage level, the logic high voltage level also may be a function of the power supply and the type of logic family. For example, in a CMOS system a logic one voltage may be about seventy 25 percent of the power supply voltage level. In a five volt TTL system a logic one voltage may be about 2.4 volts, whereas for a five volt CMOS system, the logic one voltage may be about 3.5 volts.

#### DETAILED DESCRIPTION

Generally, the present invention provides a Ground Fault Circuit Interrupter having various elements including an impedance measurement circuit. In accordance with embodiments of the present invention, an Operational Transconductance Amplifier (OTA) generates a plurality of output signals. For example, the OTA may generate a plurality of output currents where second, third, fourth, etc. 40 currents are copies of a first current. Alternatively, the OTA may generate a plurality of output voltages where each output voltage of the plurality of output voltages is proportional to an output current of the OTA. When the OTA generates a plurality of output currents, they may be input to 45 corresponding mixers as currents or they may be converted to output voltages which are input to corresponding mixers. A modulator may be used to modulate at least one of the current or voltage signals from the OTA by an in-phase signal resulting in a modulated signal that is filtered by a low 50 pass filter to pass the baseband voltage of the mixed signal. Preferably, the in-phase signal is in phase with the input signal to the OTA. The output signal of the low pass filter is digitized by an analog-to-digital converter to determine multiple real impedance levels or by a comparator to deter- 55 mine a specific real impedance. In addition, a modulator may be used to modulate at least one of the current or voltage signals from the OTA by a phase shifted signal resulting in a modulated signal that is filtered by a low pass filter, where the modulated signal indicates the reactive 60 impedance of the load. The reactive component is digitized by an analog-to-digital converter or a comparator. Preferably, the phase shifted signal is shifted by ninety degrees from the signal at the input terminal of the OTA.

In accordance with alternative embodiments, the circuit 65 can be configured to measure just the in-phase impedance or just the quadrature impedance. In addition, a single modu-

4

lator may be used to measure the in-phase impedance and the quadrature impedance by performing the measurements at different times.

In addition, embodiments of the present invention are suitable for use with GFCI circuits associated with single wound single current transformer circuits thereby forming a single wound single current transformer based impedance measurement circuit. An advantage of using single wound single current transformer circuits is that they are less expensive to implement.

FIGS. 1, 2, and 3 are block diagrams of a Ground Fault Circuit Interrupter (GFCI) module 10 in accordance with an embodiment of the present invention. For the sake of clarity, FIGS. 1, 2, and 3 are described together. GFCI module 10 is comprised of a digital control circuit 12 coupled for receiving input signals from a mains level/zero crossing detector circuit 14, a ground-to-neutral (G-N) detection randomizer 16, and a digital filter 18. The signals received from digital filter 18 may be transmitted over a bus connection having N interconnects, where N is an integer and the signals received from mains level detector circuit 14 may be transmitted over a bus connection having M interconnects, where M is an integer. Integers N and M may be the same as each other or they may be different from each other. Digital control circuit 12 is coupled for transmitting signals to digital filter 18, to a stimulus waveform generator 20, to a switch 22, and to an offset correction circuit 24. Although filter 18 is described as a digital filter, this is not a limitation of the present invention. Filter 18 may be an analog filter.

In accordance with an embodiment, mains level/zero crossing detector circuit 14 is connected to a slope detector 29 through a bus connection having K interconnects, where K is an integer. Slope detector 29 is connected to a self test controller 15 through connections 29A and 29B, where a slope detect fault signal (SD\_FAULT) is transmitted to self test controller 15 through connection 29A and a slope detect enable signal (SD\_EN) is received from self test controller 15 through connection 29B. Slope detector 29 is connected to a solenoid controller 17, which is connected to a solenoid or the mains through a solenoid/mains connector 19. The connection between slope detector 29 and solenoid controller 17 transmits a solenoid enable signal (SOL EN) to solenoid controller 17. Self test controller 15 is connected to G-N detector 56 through an output terminal 15A and to differential current detector 58 through an output terminal 15B. In addition, self test controller 15 has an output terminal 15C through which an internal or external ground fault stimulus enable signal is transmitted and an output terminal 15D through which an internal G-N impedance enable signal is transmitted. Alternatively, slope detector 29 may be omitted in which case mains level/zero crossing detector circuit 14 is connected to self test controller 15 through the bus connection having the K interconnects. In this embodiment, self test controller 15 is connected to solenoid controller 17. Mains level/zero crossing detector 14 is connected to solenoid/mains connector 19 through a current limiter 21 and to a voltage limiter 23.

The input terminal of mains/line level detector circuit 14 is connected to the power mains or line level of the circuit being monitored by GFCI module 10. It may be connected through a protection structure such as, for example, current limiter 21 shown in FIG. 2. By way of example, current limiter 21 is a resistor. Mains level detector circuit 14 communicates the mains level to digital control circuit 12 and is capable of indicating when the mains level is crossing neutral during a polarity transition or it can indicate when other levels are being used. During a self test, mains level

detector circuit 14 can indicate when it is safe for digital control circuit 12 to activate an external device such as, for example, a Silicon Controlled Rectifier (SCR) to test a GFCI solenoid. In addition, mains level detector circuit 14 can be used to determine if the external device is working properly by monitoring the effect of tripping the external device on the mains voltage level. For example, digital control circuit 12 may activate an external transistor or SCR to pull current through an external solenoid. As current is pulled through the transistor or the SCR, the mains voltage decreases or 10 droops at a different rate from that of steady state operation, i.e., there is a change in the slope of mains voltage. The rate at which the mains voltage decreases can be measured by mains level detector circuit 14 to determine if the external device is working properly. Introducing a small change in 15 the slope increases the window after a zero crossing during which the circuit can be tested and indicates when the SCR can be activated. Thus, level detector circuit 14 generates an operating condition signal in accordance with the rate at which the mains voltage level decreases that indicates if the 20 circuit is working properly or if it is safe for digital control circuit 12 to activate an external device.

Ground-to-neutral detection randomizer 16 is used to determine when GFCI module 10 should check for a ground-to-neutral fault. If multiple GFCI modules 10 are 25 used on the same mains circuit, one GFCI module 10 may corrupt another GFCI module 10 if they operate the groundto-neutral measurements at the same time. Therefore, it is advantageous to randomize the timing of the ground-toneutral measurements. G-N detection randomizer 16 ran- 30 domizes the timing between ground-to-neutral measurements to minimize the likelihood of corrupting them. FIG. 3 is a block diagram of a circuit module 31 for randomizing the timing of the ground-to-neutral measurements. An internal clock based half-wave period counter 33 is connected for 35 transmitting a random number seed to a random number generator 35, which is connected for transmitting the random number generation signal to a G-N timing control circuit 37. In addition, G-N timing control circuit 37 is connected for receiving a zero-crossing count signal from a 40 zero-crossing counter 38 and generates a G-N test enable signal. G-N timing control circuit 37 may be a sub-module within G-N detection randomizer 16. The randomization may be based on the number of oscillations of a clock in a given period of the mains cycle as illustrated in FIG. 4. What 45 is shown in FIG. 4 is a plot 41 illustrating the mains cycle having three zero crossings and a random number seed based on a counter that counts during a half period of the mains cycle.

Offset correction circuit 24 is used to minimize the 50 effective offset of an Operational Transconductance Amplifier (OTA) 28. If a DC blocking capacitor is not used in series with current transformer 51, an offset voltage in OTA 28 will produce a DC current through current transformer 51. The DC current will affect the accuracy of the differential 55 current measurements by differential current detector circuit 58. Offset correction detector 24 removes the offset of OTA 28 and preserves the accuracy of the differential current measurements. Another reason this is advantageous is that it allows current transformer 51 to be implemented with fewer 60 windings.

GFCI module 10 further includes a circuit element parameter measurement network 26 that is comprised of offset correction circuit 24, operational transconductance amplifier (OTA) 28, an in-phase impedance detector 30, and a reactive 65 impedance detector 32. By way of example circuit element parameter measurement network 26 is an impedance mea-

6

surement network, i.e., the circuit element parameter measured by network 26 is impedance. An inverting input terminal of offset correction circuit 24 is commonly connected to an output terminal 25 of OTA 28 and to a terminal 52 of the primary windings 50 of a current transformer 51 and a non-inverting input terminal of offset correction circuit 24 is connected to a terminal of switch 22. Output terminals of offset correction circuit 24 are connected to corresponding input terminals of OTA 28. More particularly, an output terminal of offset correction circuit 24 is connected to the inverting input terminal of OTA 28 and another output terminal of offset correction circuit 24 is connected to a non-inverting input terminal of OTA 28. A control terminal of switch 22 is coupled for receiving a control signal from digital control circuit 12 and another terminal of switch 22 is coupled for receiving a bias voltage  $V_{BL\!AS}$  and to a terminal 54 of primary windings 50.

An output terminal 34 of in-phase impedance detector 30 is connected to a ground-neutral (G-N) detector 56 and an output terminal 36 of reactive impedance detector 32 is connected to digital filter 18. Output terminals 34 and 36 serve as output terminals of circuit element parameter measurement network 26. An output terminal 27<sub>J</sub> of OTA 28 is connected to an input terminal of differential current detector 58 and an output terminal of differential current detector 58 may be connected to an input terminal of digital filter 18 over a bus connection having P interconnects, where P is an integer. It should be noted that reference character "J" represents an integer and has been appended to reference character 27 to indicate that one or more output terminals, e.g., output terminals 27<sub>1</sub>, 27<sub>2</sub>, 27<sub>3</sub>, etc., may extend from OTA 28. In embodiments in which the electrical signal that is output from OTA 28 is current, it is preferable that each of in-phase impedance detector 30, reactive impedance detector 32, and differential current detector 58 be connected to its own output terminal from OTA 28. For example, when the output signal of OTA 28 is a current, an output terminal 27, is connected to in-phase impedance detector 30, an output terminal 27<sub>2</sub> is connected to reactive impedance detector 32, and an output terminal 27<sub>3</sub> is connected to differential current detector 58.

GFCI module 10 includes sub-modules that are capable of performing an impedance measurement, including a ground-to-neutral resistance measurement and a current transformer reactive impedance measurement, i.e., a self test; a differential current measurement level detection; an OTA offset correction; a ground-to-neutral level detection; a mains/line voltage level detection; stimulus generation; ground-to-neutral detection randomization; digital fault filtering; or the

In accordance with embodiments in which impedance is being measured, waveform stimulus generator 20 creates an electrical signal or waveform that is transmitted to the non-inverting input terminal of offset correction circuit 24 through switch 22. It should be noted that waveform stimulus generator 20 may generate a waveform having a single frequency or a plurality of waveforms having different frequencies from each other. By way of example, to determine whether a true fault has occurred waveform stimulus generator 20 may generate three waveforms each having a different frequency. GFCI 10 includes a voting algorithm to determine when a fault occurs. More particularly, GFCI 10 determines that a fault has occurred based on a majority of the waveform frequencies, e.g., if a fault condition is detected using two out of three of the waveforms, then GFCI 10 indicates the occurrence of a fault. This type of algorithm

protects against false trips that may occur if there is a perfectly aligned noise signal on the system.

Offset correction circuit 24 transmits the electrical signal to the non-inverting input terminal of OTA 28. Because OTA 28 is configured as a follower, the electrical signal at its 5 output terminal 25 follows the electrical signal at its noninverting input terminal. Thus, the electrical signal appearing at the non-inverting input terminal of OTA 28 is transmitted to output terminal 25 and to input terminal 52 of current transformer 51. Input terminal 54 of current trans- 10 former 51 is coupled for receiving a bias voltage  $V_{BIAS}$ . OTA 28 creates an electrical signal that is proportional to the electrical signal that appears at output terminal 25 and transmits the proportional electrical signal from output terminals 27, to in-phase impedance detector 30, quadrature or 15 reactive impedance detector 32, and differential current detector 58. It should be noted that the reference character "J" has been appended to reference character 27 to indicate that one or more output terminals may extend from OTA 28 and provide copies of the current that appears at output 20 terminal 25. As discussed above, when the electrical signal that is output from OTA 28 is current, it is preferable to have output terminals 27<sub>1</sub>, 27<sub>2</sub>, and 27<sub>3</sub> extending from OTA 28 to in-phase impedance detector 30, reactive impedance detector 32, and differential current detector 58, respec- 25 tively. Alternatively, output terminals 27<sub>1</sub>, 27<sub>2</sub>, and 27<sub>3</sub> may be replaced by a single output terminal that is connected to a switch (not shown) that switches the current from the single output terminal between in-phase impedance detector **30**, reactive impedance detector **32**, and differential current 30 detector 58.

In-phase impedance detector 30 detects the real component or portion of the impedance of the current transformer load for current transformer 51 and transmits a current or voltage signal to G-N detector 56 that is proportional to this 35 component or portion of the impedance of current transformer 51. G-N detector 56 determines whether the impedance should cause a fault. Reactive or quadrature impedance detector 32 detects the reactive component or portion of the impedance of the current transformer load for current trans- 40 former 51 and transmits a current or voltage signal to digital filter 18 that is proportional to this component or a portion of the impedance of current transformer 51. Digital filter 18 determines whether the reactive component is within an acceptable range. For example, a reactive impedance that is 45 too low may indicate that the current transformer is not properly connected to network 26.

In accordance with an embodiment, differential current measurement may be accomplished by operating switch 22 such that the non-inverting input terminal of offset correc- 50 tion circuit 24 is connected to bias voltage  $V_{\it BIAS}$ . The electrical signal at output terminal 25 is driven to voltage  $V_{\it BIAS}$  by the feedback configuration of OTA 28. In this configuration input terminals 52 and 54 of current transformer 51 are driven to the voltage level  $V_{BIAS}$ . Any differ- 55 ential current through the secondary windings of current transformer 51 will induce a current through the primary windings of current transformer 51. The induced current is supplied to output terminal 25 to maintain the voltage at output terminal 25 at the voltage  $V_{BIAS}$ . OTA 28 creates or 60 generates a copy of the induced current that is proportional to the induced current at output terminal 27<sub>3</sub>, which is transmitted to the input terminal of differential current detector 58. Differential current detector 58 generates an output current that is transmitted to digital filter 18, which 65 determines whether a differential current fault has occurred based on the differential current levels, and the amount of

8

time that the current levels exist. The filter timing of digital filter 18 may be adjusted dynamically based on the conditions of circuit 10. For example, on initial startup it may be advantageous to minimize the filter timing to quickly catch a wiring fault. However, during normal operation it may be advantageous to increase the filter timing to minimize the effects of noise on the mains line. FIGS. 5 and 6 illustrate the timing of digital filter 18 in accordance with an embodiment of the present invention. FIG. 5 is a timing diagram 43 showing a plot 45 of the relationship between a differential fault current and the time allowed for GFCI module 10 to respond to the fault by opening up the electrical contacts. FIG. 6 illustrates rolling windows for each piecewise linear segment of the differential current that is monitored. More particularly, digital filter 18 is capable of monitoring several states in which GFCI module 10 may be operating. Each state is associated with a different threshold level for identification of a ground fault. During the startup state or phase, a startup fault threshold counter that may be a sub-module within digital filter 18 is programmed to have a startup fault threshold count. During steady state or a steady state phase of operation, digital filter 18 may have a fault threshold counter programmed to have a steady state fault threshold count that is different and preferably higher than the startup fault threshold count during the startup state or phase. It should be noted that the fault threshold counters may be timers such that when a fault exceeds fault threshold for a predetermined period of time, a wiring fault has occurred. The number of states is not limited to being a startup state and steady state. For instance, GFCI module 10 may be operating in a state or phase that is determined by environmental or external conditions. By way of example, GFCI module 10 may be operating in a non-ideal environmental condition such as a brownout condition, i.e., an insufficient power supply voltage, or during a negative half wave, or module 10 may be operating in a condition in which it is undesirable to maintain power to a portion of the circuitry, e.g., the analog portion of the circuitry. Thus, the portion of the circuitry may be powered down. When the brownout condition is over or the portion of the circuitry that was powered down is powered back up, a portion of the output signal from digital filter 18 may be lost. Accordingly, it may be desirable to begin GFCI module 10 so that digital filter 18 is in the startup state, i.e., programmed to have the startup fault threshold count, or digital filter 18 may be programmed to have a fault threshold count that is lower than the startup fault threshold count, lower than the steady state fault threshold count, between the startup fault threshold count and the steady state fault threshold count, or greater than the steady state fault threshold count to meet a specified set of timing requirements. Accordingly, there can be one state, two states, three states, four states, or more states. In addition, the steady state may be comprised of one or more states depending on the circuit configurations and external conditions.

Although the fault threshold counts have been described as being as comprising a fixed number of counts to trigger a fault, this is not a limitation of the present invention. Alternatively, the fault threshold can be based on a ratio-metric value. For example, the fault threshold may be a ratio of the count of the over-threshold counter to the count of the half wave period counter or the count of the over-threshold counter to the frequency of the mains. An advantage of using a ratio-metric approach is that it provides immunity to AC source variation.

FIG. 6 illustrates a rolling time window 47 over which a linear segment of plot 45 is monitored for a differential fault

current. By way of example, digital filter 18 has four fault threshold counters 53, 55, 57, and 59. However, this is not a limitation of the present invention. There may be P fault threshold counters, where P is an integer. Fault threshold counter **53** is a startup threshold counter. A fault creates fault pulses 61 in rolling time window 47 that have different magnitudes, different pulse widths, and different pulse thresholds. The pulses have different widths for each value of a fault impedance. FIG. 6 also illustrates a fault current waveform 63 with fault threshold count or timing levels Fth-1, Fth-2, ..., Fth-P. When a minimum threshold of fault time or fault count has been reached, GFCI module 10 indicates that a fault has occurred, i.e., if fault time or count exceeds the fault threshold for a first period of time or number of counts, a wiring fault has occurred. Digital filter 15 18 monitors GFCI module 10 for a predetermined minimum period of time and if no fault pulse is detected then GFCI module 10 continues in the normal mode of operation. If a fault pulse is detected, GFCI module 10 measures the duration and intensity of the pulse and generates an oper- 20 ating condition signal in accordance with the rate at which the mains level voltage decreases.

Although the electrical signal generated by OTA 28 and transmitted to differential current detector 58 has been described as a current, this is not a limitation of the present 25 invention. Alternatively, the electrical signal transmitted from OTA 28 may be a voltage that is proportional to the induced current.

FIGS. **7-14** illustrate embodiments of circuit element parameter measurement networks that are included in GFCI 30 module **10**. The circuit element parameter measurement networks of FIGS. **7-14** measure impedances. However, it should be understood this is not a limitation of the present invention. When GFCI module **10** measures impedance and is coupled to a single wound single current transformer, it is 35 referred to as a single wound single current transformer impedance measurement circuit.

FIG. 7 is a block diagram of a circuit element parameter measurement network 200 in accordance with an embodiment of the present invention. What is shown in FIG. 7 is an 40 Operational Transconductance Amplifier (OTA) 202 having a non-inverting input terminal 204, an inverting input terminal 206, and output terminals 210 and 212. It should be noted that OTA 202 is analogous to OTA 28 shown and described with reference to FIG. 1. Non-inverting input 45 terminal 204 is coupled for receiving an electrical signal  $V_{ro}$  (fc) having a frequency fc and inverting input terminal 206 is connected to output terminal 210. Preferably, electrical input signal  $V_{IN}(fc)$  is a voltage signal. More preferably, electrical signal  $V_{IN}(fc)$  is a periodic voltage signal 50 such as, for example, a sine wave. It should be noted that electrical signal  $V_{IN}(fc)$  may be a DC signal, i.e., frequency fc equals zero. Output terminal 210 of OTA 202 is coupled to a load 216 through a capacitor 214. By way of example, load 216 is a load impedance that has a circuit element 55 parameter having a real component and a reactive component. For example, when load 216 is an impedance, the impedance has a magnitude and a phase. It should be noted capacitor 214 is an optional circuit element that may be omitted.

Output terminal 212 of OTA 202 is coupled to modulators 220 and 222 through a current to voltage (I/V) converter 218. An input terminal 226 of modulator 220 and an input terminal 228 of modulator 222 are connected to an output terminal of I/V converter 218 to form a node 224. By way of example, I/V converter 218 may be a resistor through which current  $I_{rx}(fc)$  flows generating a voltage  $V_{rx}(fc)$ .

10

Modulator 220 also has an input terminal 230 coupled for receiving a modulation signal  $V_s(fc)$  and an output terminal 232 that is connected to an input terminal 234 of a Low Pass Filter (LPF) 236. Modulation signal  $V_s(fc)$  may be a periodic signal such as, for example, a sine wave, a square wave, a saw tooth wave, etc. It should be noted that modulation signal  $V_s(fc)$  is the same type of signal as input signal  $V_{IN}(fc)$  and has the same frequency as input signal  $V_{IN}(fc)$ . Preferably, modulation signal  $V_s(fc)$  is a sine wave. An Analog-to-Digital Converter (ADC) 238 is connected to an output terminal of LPF 236. An output signal  $Z_{MAG216}$  appears at an output terminal 239 of ADC 238. Modulator 220 and LPF 236 form an in-phase or real impedance detector 280.

Modulator 222 has an input terminal 240 coupled for receiving a modulation signal V<sub>SP</sub>(fc) through a phase shifting element 244, and an output terminal 242 coupled to an input terminal 246 of an LPF 248. Phase shifting element **244** shifts the phase of modulation signal  $V_s(fc)$  to produce a phase shifted modulation signal  $V_{SP}(fc)$  that has the same frequency and amplitude as modulation signal V<sub>s</sub>(fc), but a different phase. For example, signals  $V_S(fc)$  and  $V_{SP}(fc)$ may have a phase difference of ninety degrees, e.g., signal  $V_{S\!P}(fc)$  is ninety degrees out of phase from signal  $V_{S\!C}(fc)$ . An ADC 250 is connected to an output terminal of LPF 248. An output signal  $Z_{PHASE216}$  appears at an output terminal 252 of ADC 250. Modulator 222 and LPF 248 form a quadrature impedance detector 282. Quadrature impedance detector 282 is also referred to as an imaginary impedance detector or a reactive impedance detector.

In operation, input voltage  $V_{IN}(fc)$  is applied at input terminal 204 of OTA 202. In response to input voltage  $V_{IN}(fc)$ , OTA 202 generates a current  $I_{Ix}(fc)$  that flows from output terminal 210 through capacitor 214 and into load 216 thereby generating a voltage  $V_{Ix}(fc)$  at output terminal 210. Because output terminal 210 is connected to input terminal 206, voltage  $V_{Ix}(fc)$  appears at input terminal 206. Thus, OTA 202 buffers input signal  $V_{IN}(fc)$  to load 216. In addition, OTA 202 generates a copy of current  $I_{Ix}(fc)$  and conducts this current through output terminal 212. The copy of current  $I_{Ix}(fc)$  is labeled current  $I_{Ix}(fc)$  and is referred to as a copy current or a copied current. Current  $I_{Ix}(fc)$  is transmitted to I/V converter 218, which generates a voltage  $V_{Ix}(fc)$  at node 224.

In response to voltages  $V_{rx}(fc)$  and  $V_s(fc)$ , modulator 220 generates an output voltage  $V_{MOD\_I}$  at output terminal 232. Output voltage  $V_{MOD\_I}$  is equivalent to the magnitude or the real portion of current  $I_{tx}(fc)$  shifted down to the baseband, i.e., shifted down to DC. LPF 236 filters output voltage  $V_{MOD\_I}$  to remove any high frequency noise and ADC 238 digitizes the filtered output voltage  $V_{MOD\_I}$  to form a digital code  $Z_{MAG216}$  that represents the magnitude of the impedance of load 216, i.e., the digitized signal represents the magnitude of the in-phase component of the impedance of load 216

In response to voltages  $V_{rx}(fc)$  and  $V_{SP}(fc)$ , modulator 222 generates an output voltage  $V_{MOD\_Q}$  at output terminal 242. LPF 248 filters output voltage  $V_{MOD\_Q}$  to remove any high frequency noise and ADC 250 digitizes the filtered output voltage  $V_{MOD\_Q}$  to form a digital code  $Z_{PHASE216}$  that represents the phase of the impedance of load 216, i.e., the digitized signal represents the quadrature component of the impedance of load 216.

FIG. 8 is a schematic diagram of a circuit element parameter measurement network 270 in accordance with another embodiment of the present invention. Network 270 includes OTA 202, capacitor 214, load 216, LPF's 236 and

248, and ADC's 238 and 250 which have been described above with reference to FIG. 2. In addition, network 270 includes a voltage/current replicator and inverter block 218A which has an output terminal 217 commonly connected to input terminal 288 of switch 284 and to input 5 terminal 316 of switch 312 to form a node 223 and an output terminal 219 commonly connected to terminal 300 of switch 296 and to terminal 308 of switch 304 to form a node 271. Network 270 further includes a switch 284 which has a control terminal 286, a terminal 288 connected to node 223, and a terminal 290 connected to input terminal 234 of LPF 236. Control terminal 286 is coupled for receiving modulation signal V<sub>s</sub>B(fc) through an inverter 292, i.e., an input terminal of inverter 292 is coupled for receiving modulation signal V<sub>s</sub>(fc) and an output terminal of inverter 292 is connected to control terminal 286 of switch 284 for transmitting inverted modulation signal V<sub>S</sub>B(fc). Node 271 is coupled to input terminal 234 of LPF 236 through a switch 296, which has a control terminal 298 and terminals 300 and **302**. Control terminal **298** is coupled for receiving modula- 20 tion signal V<sub>s</sub>(fc), terminal 300 is connected to node 271, and terminal 302 is connected to input terminal 234 of LPF

In addition, node 271 is coupled to input terminal 246 of LPF 248 through a switch 304, which has a control terminal 25 306 and terminals 308 and 310. More specifically, control terminal 306 is coupled for receiving modulation signal  $V_{SP}(fc)$ , terminal 308 is connected to node 271, and terminal 310 is connected to input terminal 246 of LPF 248. Switch 312 has a control terminal 314 coupled for receiving modulation signal  $V_{SP}(fc)$  from an inverter 320, a terminal 316 commonly connected to terminal 288 of switch 284, and to terminal 217 of current-to-voltage converter 218A, and a terminal 318 commonly connected to input terminal 246 of LPF 248 and to terminal 310 of switch 304.

In operation, input signal  $V_{IN}(fc)$  is received at input terminal 204 of OTA 202. In response to input signal  $V_{IN}(fc)$ , OTA 202 generates a current  $I_{Ix}(fc)$  that flows from output terminal 210 through capacitor 214 and into load 216 thereby generating a voltage  $V_{cx}(fc)$  at output terminal 210. 40 Because output terminal 210 is connected to input terminal 206, voltage V(fc) appears at input terminal 206. Thus, OTA 202 buffers input signal  $V_{IN}(fc)$  to load 216. In addition, OTA 202 generates a copy of current  $I_{tx}(fc)$  and conducts this current through output terminal 212. The copy of current  $I_{Ix}(fc)$  is labeled current  $I_{Ix}(fc)$  and is referred to as a copy current or a copied current. Current  $I_{Ix}(fc)$  is transmitted to I/V converter 218A and is converted to a voltage  $V_{rxp}(fc)$  which appears at node 271 and a voltage  $V_{rxp}(fc)$  that appears at node 223.

It should be noted that modulation signal V<sub>s</sub>(fc) controls switches 284 and 296 and modulation signal  $V_{SP}(fc)$  controls switches 304 and 312. When modulation signal V<sub>s</sub>(fc) is at a logic high voltage level switch 284 is closed and switch **296** is open and when modulation signal  $V_s(fc)$  is at 55 a logic low voltage level switch 284 is open and switch 296 is closed. When modulation signal  $V_{SP}(fc)$  is at a logic high voltage level switch 304 is closed and switch 312 is open and when modulation signal  $V_{SP}(fc)$  is at a logic low voltage level switch 304 is open and switch 312 is closed. Thus, 60 switches 284 and 296 are opened and closed to multiply signals  $V_{rxn}(fc)$  and  $V_sB(fc)$  with each other and to multiply signals  $V_{rxp}(fc)$  and  $V_s(fc)$  with each other. The multiplication of these signals forms product signals that are combined to form voltage signal  $V_{MOD\_I}$  at input terminal 234 of LPF 236. Output voltage  $V_{MOD\_i}$  is equivalent to the magnitude or the real portion of current I<sub>tx</sub>(fc) shifted down to the

12

baseband, i.e., shifted down to DC. Because signals  $V_{rxn}(fc)$  and  $V_{rxp}(fc)$  are fully differential signals, the DC component of input signal  $V_{IN}(fc)$  is removed, thereby increasing the noise immunity of network 270. LPF 236 filters output voltage  $V_{MOD_J}$  to remove any high frequency noise and ADC 238 digitizes filtered output voltage  $V_{MOD_J}$  to form a digital code  $Z_{MAG216}$  that represents the magnitude of the impedance of load 216, i.e., the digitized signal represents the magnitude of the in-phase component of the impedance of load 216. Switches 284 and 296, inverter 292, and LPF 236 form an in-phase or real impedance detector 280A.

Similarly, switches 304 and 312 are opened and closed to multiply signals  $V_{rxp}(fc)$  and  $V_{SP}B(fc)$  with each other and to multiply signals  $V_{rxp}(fc)$  and  $V_{SP}B(fc)$  with each other. The multiplication of these signals forms product signals that are combined to form voltage signal  $V_{MOD\_Q}$  at input terminal 246 of LPF 248. LPF 248 filters output voltage  $V_{MOD\_Q}$  to remove any high frequency noise and ADC 250 digitizes filtered output voltage  $V_{MOD\_Q}$  to form a digital code  $Z_{PHASE216}$  that represents the phase of the impedance of load 216, i.e., the digitized signal represents the quadrature component of the impedance of load 216. Switches 304 and 312, inverter 320, phase shifting element 244, and LPF 248 form a quadrature impedance detector 282A. Quadrature impedance detector or a reactive impedance detector.

FIG. 9 is a schematic diagram of a circuit element parameter measurement network 350 in accordance with another embodiment of the present invention. What is shown in FIG. 9 is OTA 202A coupled to load 216 through capacitor 214. OTA 202A is similar to OTA 202 but has three output terminals 210, 212, and 215 rather than the two output terminals 210 and 212 of OTA 202. Because OTA 202A has three output terminals, reference character "A" has been appended to reference character "202" to distinguish between OTA 202 of FIG. 2 and the operational transconductance amplifier of FIG. 8. Similar to network 270 described with reference to FIG. 7, output 210 of OTA 202A is coupled to load 216 through capacitor 214. Network 350 includes node 223 coupled to input terminal 234 of LPF 236 through a switch 284 and to an output terminal 217A of current-to-voltage converter 218A. More particularly, switch 284 has a control terminal 286, a terminal 288 connected to node 223, and a terminal 290 connected to input terminal 234 of LPF 236. Control terminal 286 is coupled for receiving modulation signal V<sub>S</sub>B(fc) from an inverter 292, i.e., an input terminal of inverter 292 is coupled for receiving modulation signal V<sub>S</sub>(fc) and an output terminal of inverter 292 is connected to control terminal 286 of switch 284 for transmitting an inverter modulation signal V<sub>S</sub>B(fc). Input terminal 234 of LPF 236 is coupled to output terminal 219A of current-to-voltage converter 218A through a switch 296, which has a control terminal 298 and terminals 300 and 302. Control terminal 298 is coupled for receiving modulation signal V<sub>S</sub>(fc), terminal 300 is connected to output terminal 219A of current-to-voltage converter 218A, and terminal 302 is commonly connected to input terminal 234 of LPF 236 and to terminal 290 of switch 284.

Output terminal 215 of OTA 202A is coupled to LPF 248 through a switch 312 and a current-to-voltage converter 218B. More particularly, output terminal 215 is connected to an input terminal of current-to-voltage converter 218B and an output terminal 217B of current-to-voltage converter 218B is connected to terminal 316 to form a node 223A. An output terminal 219B of current-to-voltage converter 218B is connected to a terminal 308 of switch 304. Switch 304 also has a control terminal 306 coupled for receiving modu-

lation signal  $V_{SP}(fc)$  and a terminal 310 commonly connected to input terminal 246 of LPF 248 and to a terminal 318 of switch 312. Output terminal 217B is coupled to input terminal 246 of LPF 248 and to terminal 310 of switch 304 through switch 312. More particularly, switch 312 has a control terminal 314, a terminal 316 connected to output terminal 217B, and a terminal 318 commonly connected to input terminal 246 of LPF 248 and to terminal 310 of switch 304. Control terminal 314 is coupled for receiving modulation signal  $V_{SP}B(fc)$  from inverter 320, i.e., an input terminal of inverter 320 is coupled for receiving modulation signal  $V_{SP}B(fc)$  and an output terminal of inverter 320 is connected to terminal 314 of switch 312 for transmitting inverted modulation signal  $V_{SP}B(fc)$ .

In operation, input voltage  $V_{IN}(fc)$  is applied at input 15 terminal 204 of OTA 202A. In response to input voltage  $V_{IN}(fc)$ , OTA **202**A generates a current  $I_{cx}(fc)$  that flows from output terminal 210 through capacitor 214 and into load 216 thereby generating a voltage  $V_{tx}(fc)$  at output terminal 210. Because output terminal 210 is connected to 20 input terminal 206, voltage  $V_{rx}(fc)$  appears at input terminal **206**. Thus, OTA **202**A buffers input signal  $V_{IN}(fc)$  to load **216.** In addition, OTA **202** generates copies  $I_{rx}$  (fc) and  $I_{rx}$  O(fc) of current  $I_{tx}$ (fc) and conducts the currents  $I_{rx}$  I(fc) and  $I_{rx}$ <sub>Q</sub>(fc) through output terminals 212 and 215, respec- 25 tively. The copies of current  $I_{tx}(fc)$  are labeled  $I_{rx}$  (fc) and  $I_{rx}$  O(fc) and each current is referred to as a copy current or a copied current. Current I<sub>rx</sub> (fc) is transmitted to currentto-voltage converter 218A which generates a voltage signal  $V_{rxp\_I}(fc)$  at node **223**. Current  $I_{rx\_Q}(fc)$  is transmitted to current-to-voltage converter 218B which generates a voltage

signal  $V_{rxp\_Q}(fc)$  at node 223A. It should be noted that modulation signal  $V_S(fc)$  controls switches 284 and 296 and modulation signal  $V_{SP}(fc)$  controls switches 304 and 312. When modulation signal  $V_s(fc)$  35 is at a logic high voltage level switch 284 is closed and switch **296** is open and when modulation signal  $V_s(fc)$  is at a logic low voltage level switch 284 is open and switch 296 is closed. When modulation signal  $V_{\ensuremath{\mathit{SP}}}(fc)$  is at a logic high voltage level switch 304 is closed and switch 312 is open 40 and when modulation signal  $V_{SP}(fc)$  is at a logic low voltage level switch 304 is open and switch 312 is closed. Thus, switches 284 and 296 are opened and closed to multiply signals  $V_{rxp\_I}(fc)$  and inverted signal  $V_SB(fc)$  with each other and to multiply signal  $V_{rxp}$  (fc) and  $V_s$ (fc) with each 45 other. The multiplication of these signals forms product signals that are combined to form voltage signal  $\mathbf{V}_{MOD\_I}$  at input terminal 234 of LPF 236. Output voltage  $V_{MOD\_I}$  is equivalent to the magnitude or the real portion of current I<sub>tx</sub>(fc) shifted down to the baseband, i.e., shifted down to 50 DC. Because signals  $V_{rxn\_I}(fc)$  and  $V_{rxp\_I}(fc)$  are fully differential signals, the DC component of input signal  $V_{IN}$ (fc) is removed, thereby increasing the noise immunity of network 350. LPF 236 filters output voltage  $V_{\textit{MOD}\_\textit{I}}$  to remove any high frequency noise and ADC 238 digitizes 55 filtered output voltage  $V_{MOD\_I}$  to form a digital code  $Z_{MAG216}$  at output terminal 239 that represents the magnitude of the impedance for load 216, i.e., the digitized signal represents the magnitude of the in-phase component of the impedance of load 216.

Similarly, switches **304** and **312** are opened and closed to multiply signals  $V_{rxp}$  Q(fc) and inverted signal  $V_{SP}$ B(fc) with each other and to multiply signal  $V_{rxp}$  Q(fc) and  $V_{SP}$ (fc) with each other. The multiplication of these signals forms product signals that are combined to form voltage signal  $V_{MOD\_Q}$  at input terminal **246** of LPF **248**. LPF **248** filters output voltage  $V_{MOD\_Q}$  to remove any high frequency

14

noise and ADC **250** digitizes filtered output voltage  $V_{MOD\_Q}$  to form a digital code  $Z_{PHASE216}$  at output terminal **252** that represents the phase of the impedance for load **216**, i.e., the digitized signal represents the quadrature component of the impedance of load **216**.

FIG. 10 is a schematic diagram of a circuit element parameter measurement network 370 in accordance with another embodiment of the present invention. Network 370 is similar to network 200 except that OTA 202 is replaced with OTA 202A and current-to-voltage converter 218 is absent from network 370. In addition, modulators 220 and 222 are replaced with modulators 220A and 222A which are configured to receive current rather than a voltage. The operation of network 370 is similar to that of network 200 except that mixers 220A and 222A mix currents rather than voltages. Modulator 220A and LPF 236 form an in-phase or real impedance detector 280B. Modulator 222A and LPF 248 form a quadrature impedance detector 282B. Quadrature impedance detector 282B is also referred to as an imaginary impedance detector or a reactive impedance detector

FIG. 11 is a schematic diagram of a circuit element parameter measurement network 400 in accordance with another embodiment of the present invention. What is shown in FIG. 11 is OTA 202A coupled to load 216 through capacitor 214. The configuration of network 400 is similar to that of network 350 except that switches 284 and 296 and inverter 292 are replaced by a Digital-to-Analog Converter (DAC) 402 and switches 304 and 312 and inverter 320 are replaced by a DAC 404. More particularly, DAC 402 has an input terminal 406 connected to output terminal 212 of OTA 202A, an input terminal 408 coupled for receiving an input signal D<sub>SIN</sub>[N:0], and an output terminal 410 connected to input terminal 234 of LPF 236. DAC 404 has an input terminal 412 connected to output terminal 215 of OTA 202A, an input terminal 414 coupled for receiving an input signal  $D_{COS}[N:0]$  and an output terminal 416 connected to input terminal 246 of LPF 248. Signals  $D_{SIN}[N:0]$  and D<sub>COS</sub>[N:0] are also referred to as digital codes.

In operation, input voltage  $V_{IN}(fc)$  is applied at input terminal 204 of OTA 202A. In response to input voltage  $V_{IN}(fc)$ , OTA 202A generates a current  $I_{cx}(fc)$  that flows from output terminal 210 through capacitor 214 and into load 216 thereby generating a voltage  $V_{tx}(fc)$  at output terminal 210. Because output terminal 210 is connected to input terminal 206, voltage  $V_{\mbox{\tiny LX}}(\mbox{fc})$  appears at input terminal **206**. Thus, OTA **202**A buffers input signal  $V_{IN}(fc)$  to load 216. In addition, OTA 202 generates copies  $I_{rx\_I}(fc)$  and  $I_{rx}$  O(fc) of current  $I_{tx}$ (fc) and conducts the currents  $I_{rx}$  (fc) and  $I_{rx}$  (fc) through output terminals 212 and 215, respectively. The copies of current  $I_{tx}(fc)$  are labeled  $I_{rx}$  (fc) and  $I_{rx\_Q}(fc)$  and each current is referred to as a copy current or a copied current. Current  $I_{rx_n}$  (fc) is transmitted to DAC 402 which modulates current  $\bar{I}_{rx_n}$  (fc) by digital input code  $D_{SIN}[N:0]$  and generates a voltage  $V_{MOD\_I}$  that appears at output terminal 410. LPF 236 filters output voltage  $V_{MOD\ I}$ to remove any high frequency noise and ADC 238 digitizes filtered output voltage  $V_{MOD\ I}$  to form a digital code  $Z_{MAG216}$  at output terminal  $23\overline{9}$  that represents the magni-60 tude of the impedance of load 216, i.e., the digitized signal represents the magnitude of the in-phase component of the impedance of load 216.

Current  $I_{rx\_Q}$ (fc) is transmitted to DAC **404** which modulates current  $\overline{I}_{rx\_Q}$ (fc) by digital input code  $D_{COS}[N:0]$  and generates a voltage  $V_{MOD\_Q}$  that appears at output terminal **416**. LPF **248** filters output voltage  $V_{MOD\_Q}$  to remove any high frequency noise and ADC **250** digitizes filtered output

voltage  $V_{MOD\_Q}$  to form a digital code  $Z_{PHASE216}$  at output terminal 252 that represents the phase of the impedance of load 216, i.e., the digitized signal represents the quadrature component of the impedance of load 216.