US009666477B2

## (12) United States Patent

## Ohashi et al.

## (54) METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE

- (71) Applicant: HITACHI KOKUSAI ELECTRIC INC., Tokyo (JP)

- Inventors: Naofumi Ohashi, Toyama (JP); Satoshi (72)Takano, Toyama (JP)

- Assignee: HITACHI KOKUSAI ELECTRIC (73)INC., Tokyo (JP)

- Subject to any disclaimer, the term of this (\*) Notice: patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 15/067,790

- Filed: Mar. 11, 2016 (22)

#### (65)**Prior Publication Data**

US 2016/0293480 A1 Oct. 6, 2016

#### (30)**Foreign Application Priority Data**

Mar. 30, 2015 (JP) ..... 2015-068999

- (51) Int. Cl. H01L 21/66 (2006.01)H01L 21/768 (2006.01)

- (52) U.S. Cl. CPC .. H01L 21/76816 (2013.01); H01L 21/76819 (2013.01); H01L 21/76843 (2013.01); H01L 21/76864 (2013.01); H01L 21/76879 (2013.01); H01L 22/12 (2013.01)

- (58) Field of Classification Search CPC ...... H01L 21/76819; H01L 21/7684; H01L 22/12; H01L 27/76843

See application file for complete search history.

#### US 9,666,477 B2 (10) Patent No.:

#### (45) Date of Patent: May 30, 2017

#### (56)**References** Cited

## U.S. PATENT DOCUMENTS

| 5,893,050    | Α      | 4/1999  | Park et al.            |

|--------------|--------|---------|------------------------|

| 6,033,921    | Α      | 3/2000  | Dawson et al.          |

| 8,420,528    | B2     | 4/2013  | Noguchi                |

| 9,401,293    | B2     | 7/2016  | Kobata et al.          |

| 2007/0232063 | A1 $*$ | 10/2007 | Frohberg H01L 21/76801 |

|              |        |         | 438/672                |

2008/0169571 A1 7/2008 Izumi

## FOREIGN PATENT DOCUMENTS

| JP | 02-262331 A       | 10/1990 |

|----|-------------------|---------|

| JP | 07-066291 A       | 3/1995  |

| JP | 09-143722 A       | 6/1997  |

| JP | 2010-108953 A     | 5/2010  |

| JP | 2012-138442 A     | 7/2012  |

| KR | 10-2008-0067977 A | 7/2008  |

## OTHER PUBLICATIONS

Korean Office Action issued on Jan. 1, 2017 in the Korean Application No. 10-2016-0029523.

\* cited by examiner

Primary Examiner — Amar Movva

(74) Attorney, Agent, or Firm-Volpe and Koenig, P.C.

#### ABSTRACT (57)

A method of manufacturing a semiconductor device includes forming a first insulating film as a portion of a laminated insulating film on a substrate in which a plurality of circuit configurations is formed; polishing the first insulating film; measuring a film thickness distribution of the first insulating film; and forming a second insulating film as a portion of the laminated insulating film on the polished first insulating film at a film thickness distribution differing from the film thickness distribution of the first insulating film to correct a film thickness of the laminated insulating film.

## 18 Claims, 29 Drawing Sheets

# FIG. 1

Radial position on substrate [mm]

Radial position on substrate [mm]

FIG. 12

FIG. 26

|                       |                |      | Mass flow | controller |      |

|-----------------------|----------------|------|-----------|------------|------|

|                       |                | 241b | 242b      | 251b       | 252b |

| First insulating film | Distribution A | a101 | α102      | α103       | α104 |

| distribution          | Distribution B | β101 | β102      | β103       | β104 |

|                       |                |      |      |      | Mass flow controller | controller |      |      |      |

|-----------------------|----------------|------|------|------|----------------------|------------|------|------|------|

|                       | <u>[</u>       | 241b | 243c | 242b | 244c                 | 251b       | 253c | 252b | 254c |

| First insulating film | Distribution A | α201 | α202 | α203 | α204                 | α205       | α206 | α207 | α208 |

| distribution          | Distribution B | β201 | β202 | β203 | β204                 | β205       | β206 | ß207 | β208 |

FIG. 27

|                       |                |      | Mass flow | Aass flow controller |      | He   | Heater |

|-----------------------|----------------|------|-----------|----------------------|------|------|--------|

|                       | 1              | 241b | 242b      | 251b                 | 252b | 213a | 213b   |

| First insulating film | Distribution A | α301 | α302      | α303                 | α304 | α305 | α306   |

| distribution          | Distribution B | β301 | β302      | β303                 | β304 | β305 | β306   |

FIG. 28

|                       |                |      |      |      | Mass flow ( | w controller | <b>.</b> |      |      | He   | -leater |

|-----------------------|----------------|------|------|------|-------------|--------------|----------|------|------|------|---------|

|                       | <u>I</u>       | 241b | 243c | 242b | 244c        | 251b         | 253c     | 252b | 254c | 213a | 213b    |

| First insulating film | Distribution A | α401 | α402 | α403 | α404        | α405         | α406     | α407 | α408 | α409 | α410    |

| distribution          | Distribution B | β401 | β402 | β403 | β404        | β405         | β406     | β407 | β408 | β409 | ₿410    |

FIG. 29

15

65

## METHOD OF MANUFACTURING SEMICONDUCTOR DEVICE

## CROSS-REFERENCE TO RELATED APPLICATION

This application is based upon and claims the benefit of priority from Japanese Patent Application No. 2015-068999, filed on Mar. 30, 2015, the entire contents of which are incorporated herein by reference.

## TECHNICAL FIELD

The present disclosure relates to a method of manufacturing a semiconductor device, a substrate processing system, and a substrate processing apparatus.

## BACKGROUND

Recently, semiconductor devices tend to be highly integrated. In line with the tendency of high integration of semiconductor devices, pattern sizes have been remarkably miniaturized. The patterns are formed through a hard mask or resist forming process, a lithography process, an etching 25 process and the like. When forming the patterns, a variation in the characteristics of the semiconductor devices should be prevented.

However, a variation in a distance between circuits to be formed on a substrate may occur due to processing prob-<sup>30</sup> lems. In particular, such a variation may significantly affect the characteristics of semiconductor devices with miniaturized patterns.

## SUMMARY

The present disclosure provides some embodiments of a technique capable of suppressing a variation in characteristics of a semiconductor device.

According to one embodiment of the present disclosure, <sup>40</sup> there is provided a technique including: forming a first insulating film as a portion of a laminated insulating film on a substrate in which a plurality of circuit configurations is formed; polishing the first insulating film; measuring a film 45 thickness distribution of the first insulating film; and forming a second insulating film as a portion of the laminated insulating film at a film thickness distribution differing from the film thickness distribution of the first insulating film at a film thickness distribution differing from the film thickness distribution of the first insulating film to correct a film thickness 50 of the laminated insulating film.

## BRIEF DESCRIPTION OF THE DRAWINGS

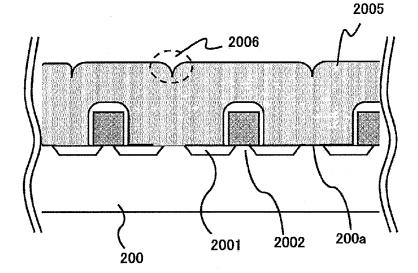

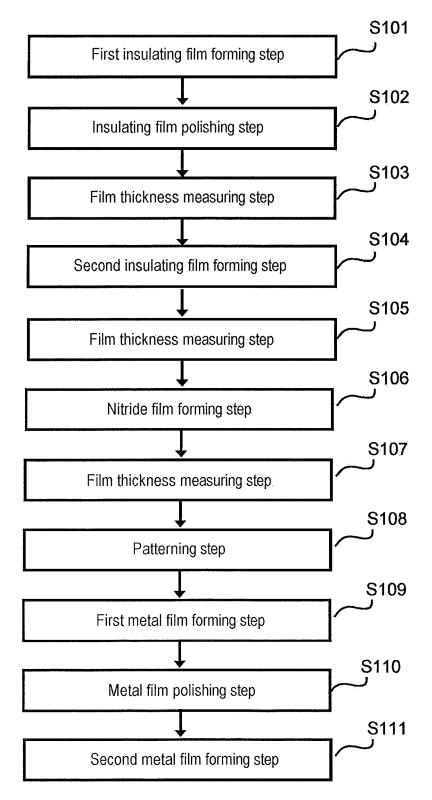

FIG. 1 is an explanatory view illustrating a manufacturing 55 flow of a semiconductor device according to an embodiment.

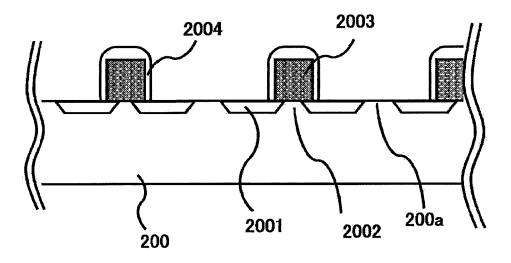

FIG. **2** is an explanatory view of a wafer according to an embodiment.

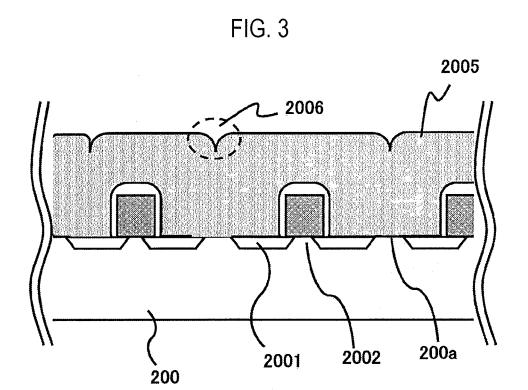

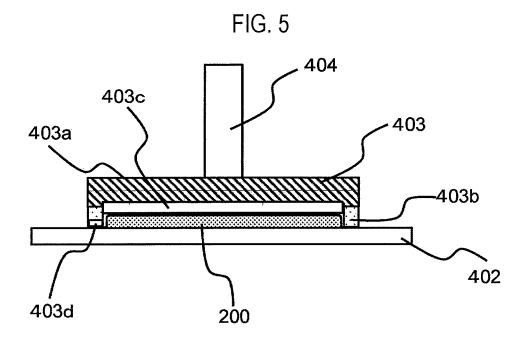

FIG. **3** is an explanatory view illustrating a processing 60 state of a wafer according to an embodiment.

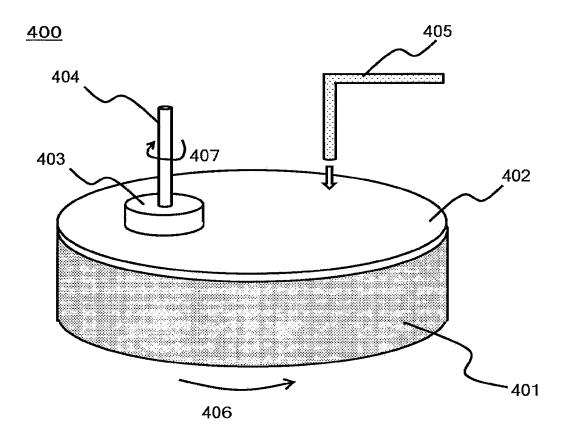

FIG. **4** is an explanatory view illustrating a polishing apparatus according to an embodiment.

FIG. **5** is an explanatory view illustrating a polishing apparatus according to an embodiment.

FIG. **6** is an explanatory view illustrating a processing state of a wafer according to an embodiment.

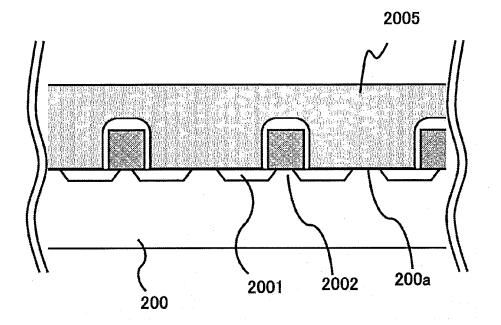

FIG. 7 is an explanatory view illustrating a thickness distribution of an insulating film after a polishing step according to an embodiment.

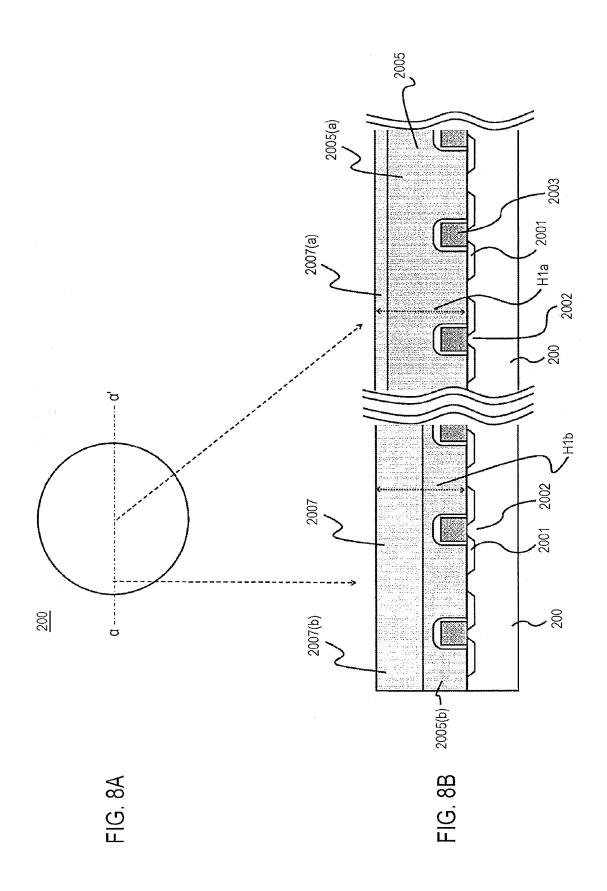

FIGS. **8**A and **8**B are explanatory views illustrating a processing state of a wafer according to an embodiment.

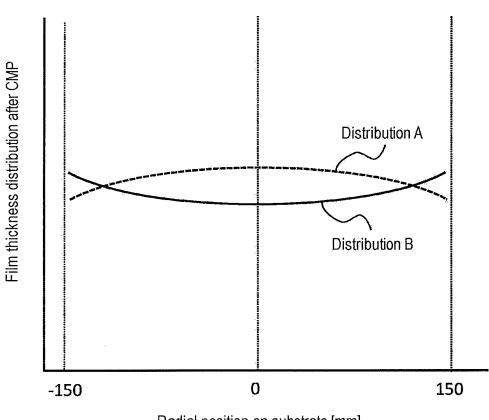

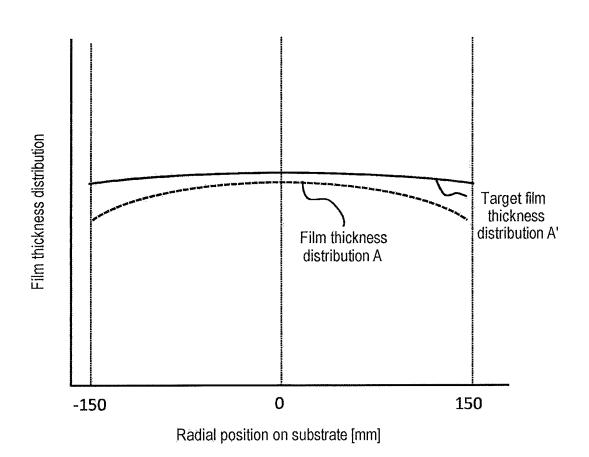

FIG. **9** is an explanatory view illustrating a thickness distribution of an insulating film according to an embodiment.

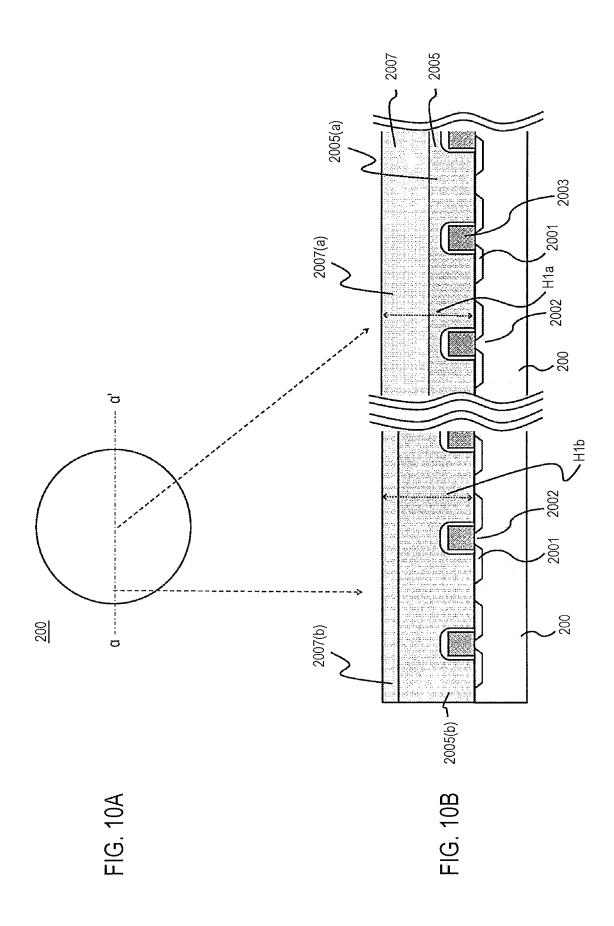

FIGS. **10**A and **10**B are explanatory views illustrating a processing state of a wafer according to an embodiment.

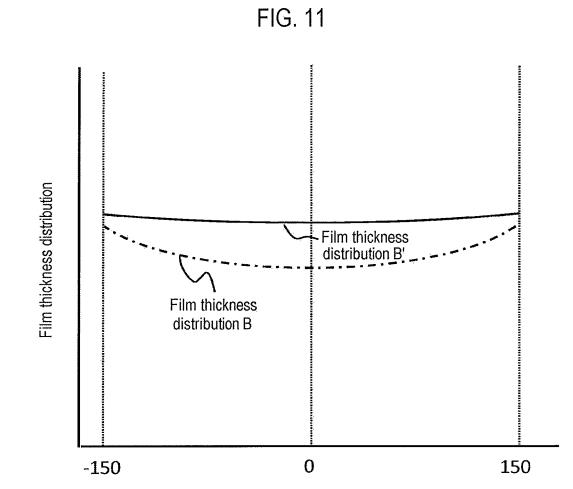

FIG. **11** is an explanatory view illustrating a thickness distribution of an insulating film according to an embodiment.

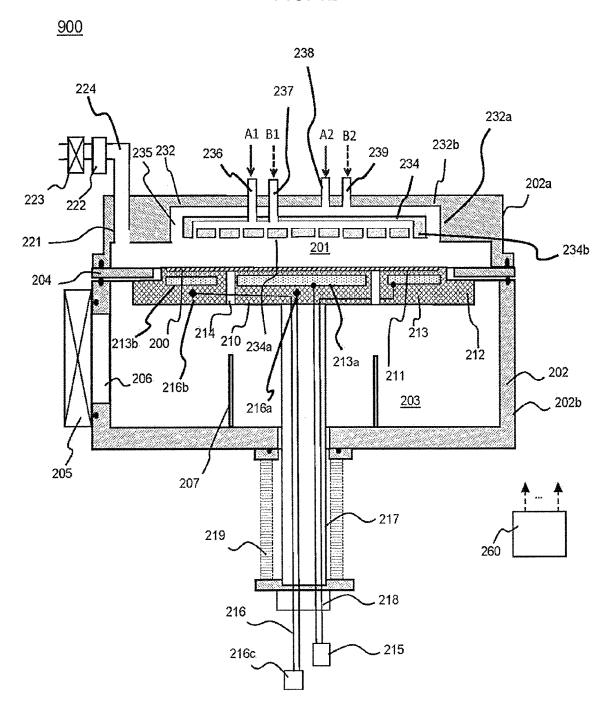

FIG. **12** is an explanatory view illustrating a substrate processing apparatus according to an embodiment.

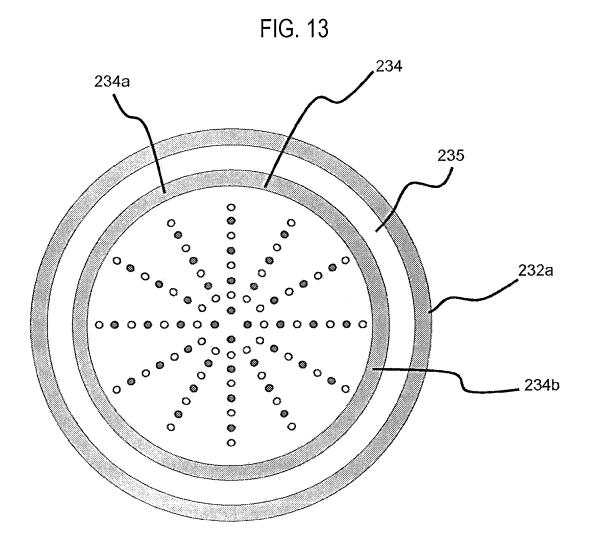

FIG. **13** is an explanatory view illustrating a shower head of a substrate processing apparatus according to an embodiment.

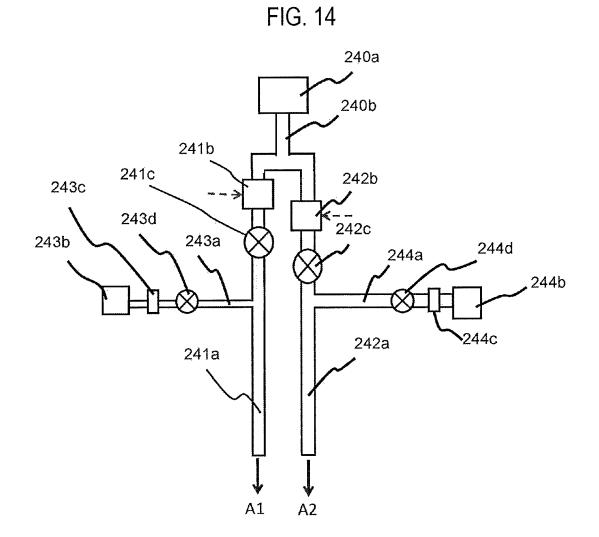

FIG. **14** is an explanatory view illustrating a gas supply system of a substrate processing apparatus according to an embodiment.

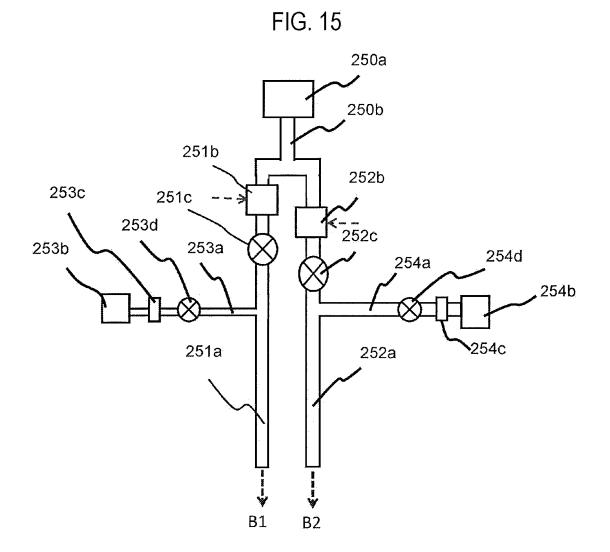

FIG. **15** is an explanatory view illustrating a gas supply system of a substrate processing apparatus according to an embodiment.

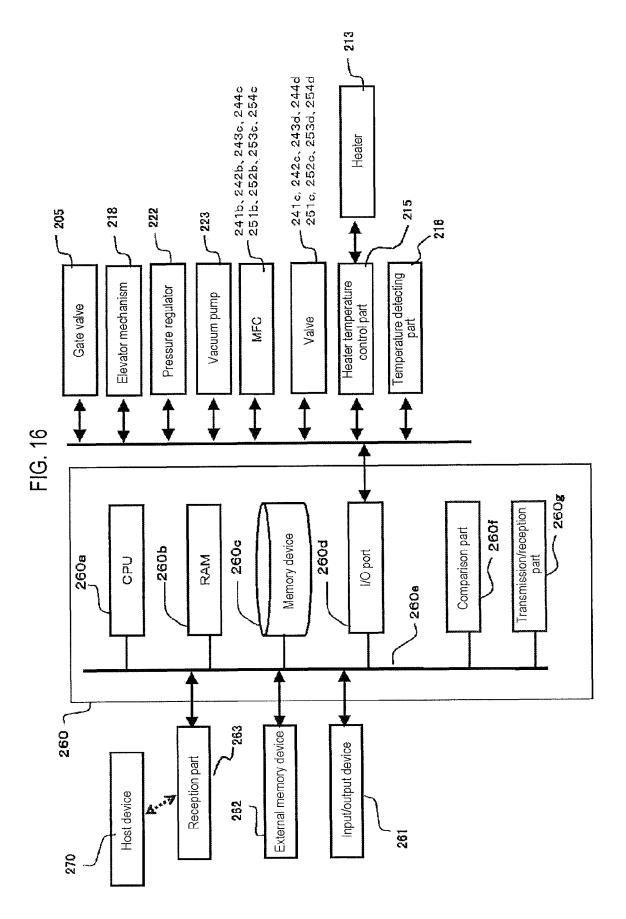

FIG. **16** is a schematic configuration view of a controller according to an embodiment.

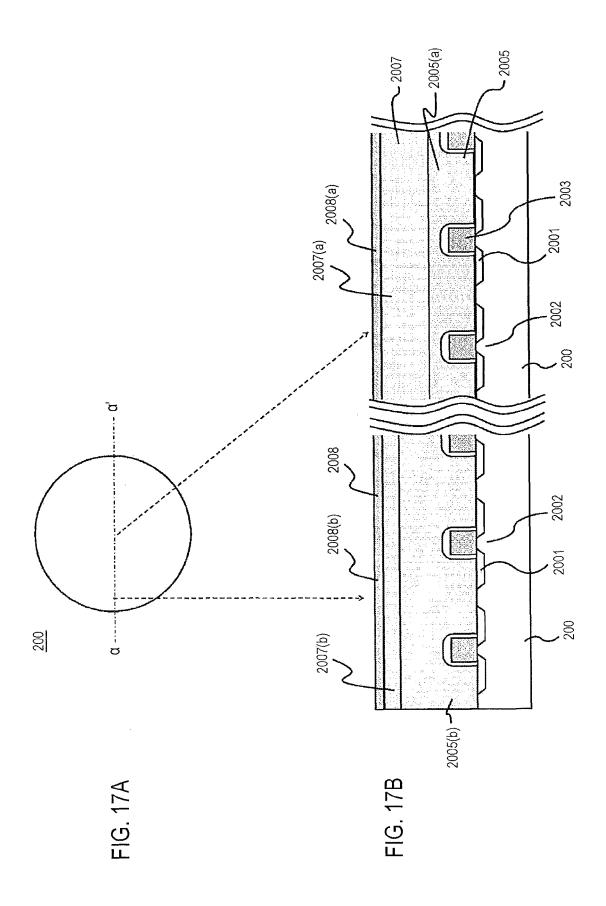

FIGS. **17**A and **17**B are explanatory views illustrating a processing state of a wafer according to an embodiment.

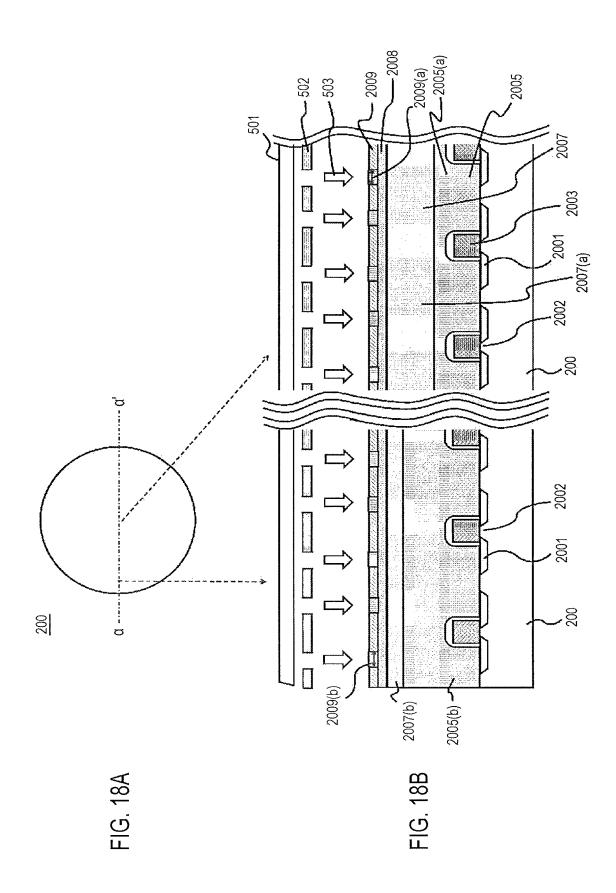

FIGS. **18**A and **18**B are explanatory views illustrating a processing state of a wafer according to an embodiment.

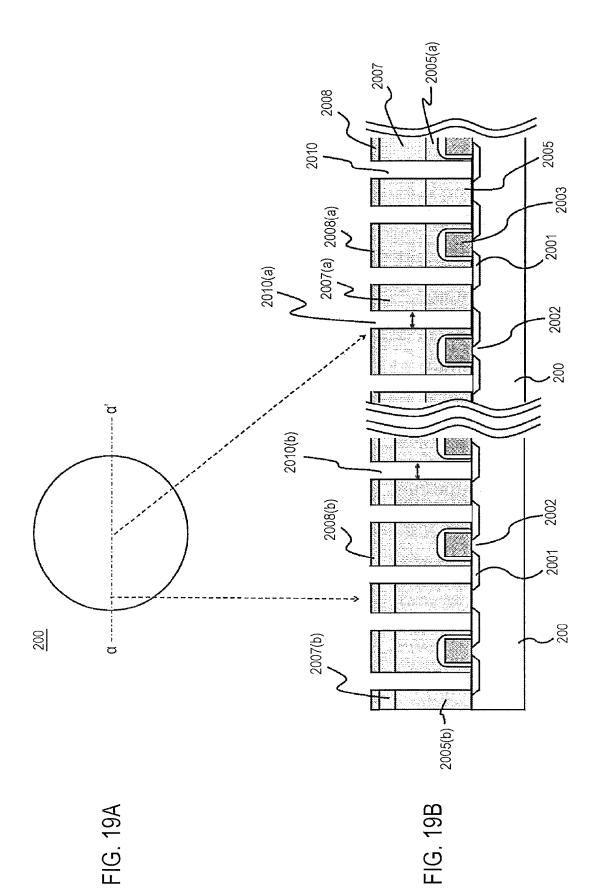

FIGS. **19**A and **19**B are explanatory views illustrating a processing state of a wafer according to an embodiment.

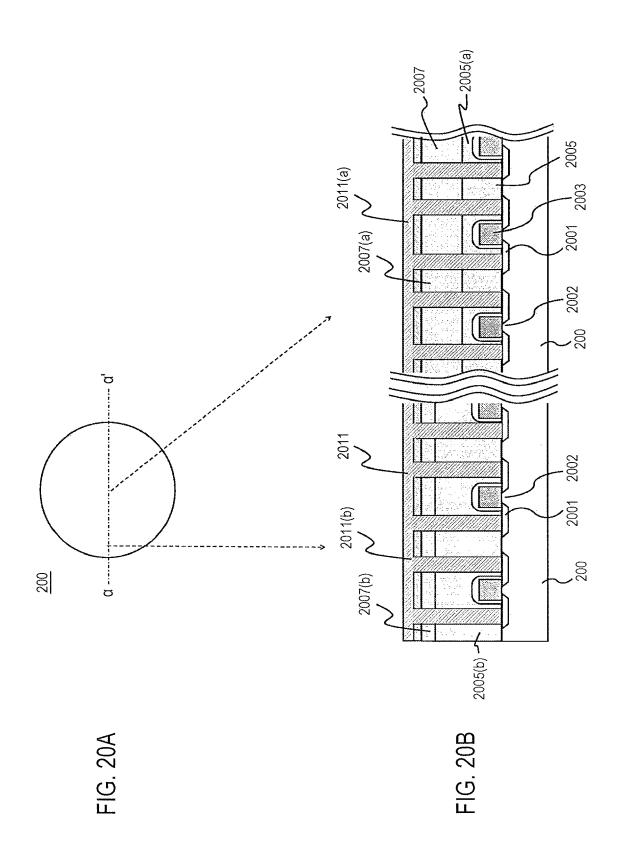

FIGS. **20**A and **20**B are explanatory views illustrating a processing state of a wafer according to an embodiment.

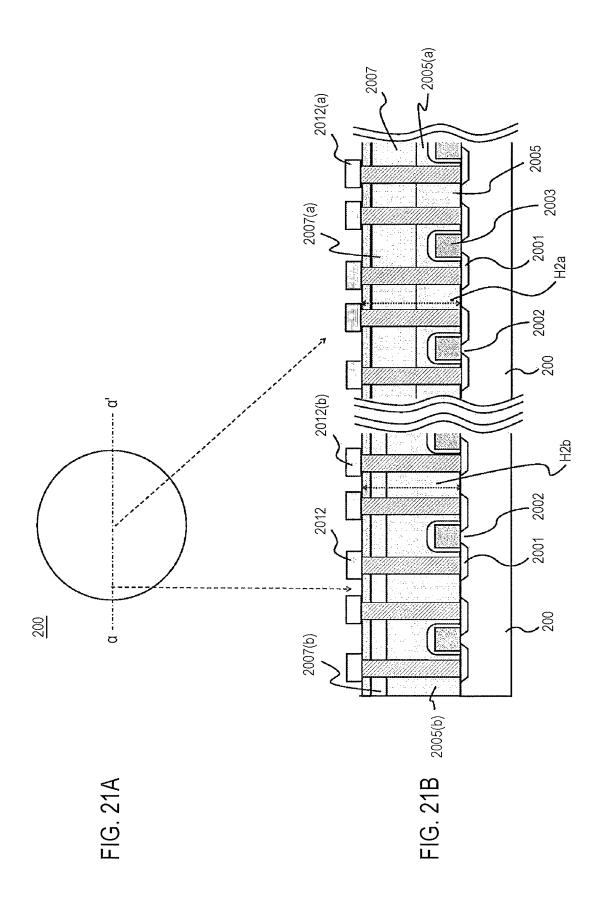

FIGS. **21**A and **21**B are explanatory views illustrating a  $_{40}$  processing state of a wafer according to an embodiment.

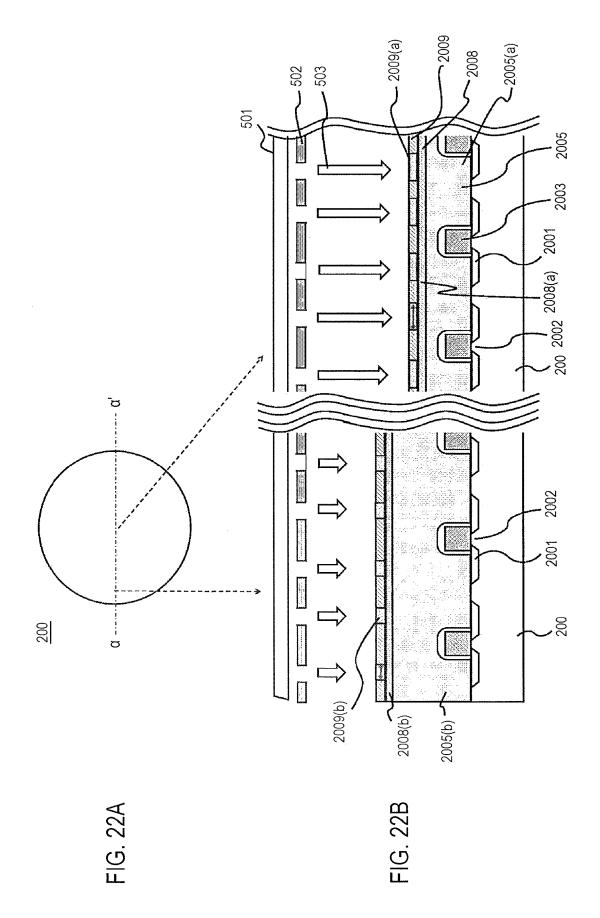

FIGS. **22**A and **22**B are explanatory views illustrating a processing state of a wafer according to a comparative example.

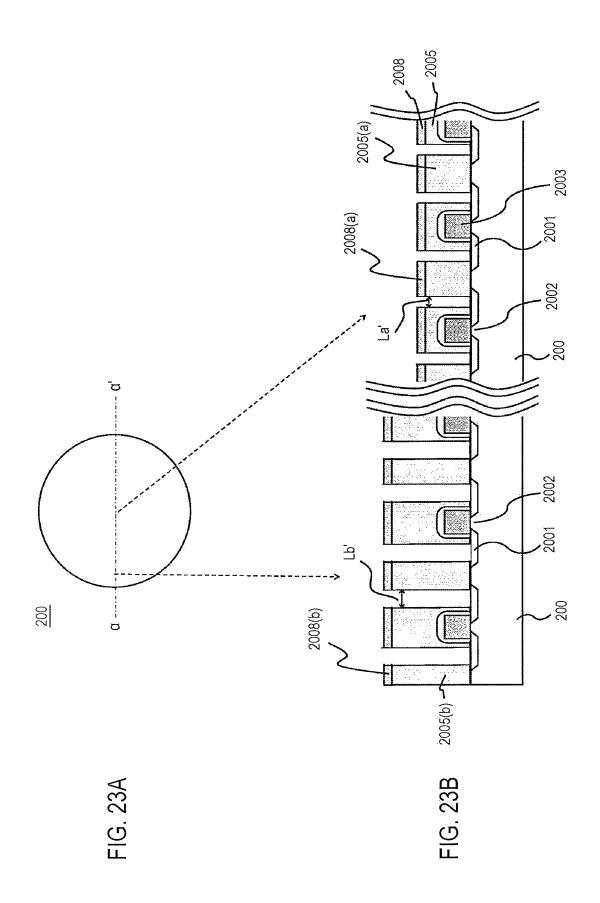

FIGS. **23**A and **23**B are explanatory views illustrating a processing state of a wafer according to a comparative example.

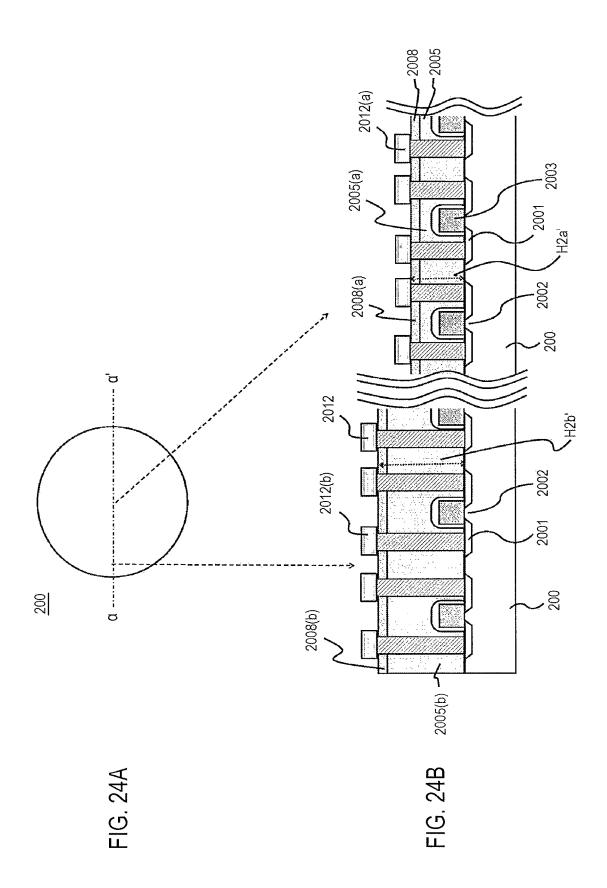

FIGS. **24**A and **24**B are explanatory views illustrating a processing state of a wafer according to a comparative example.

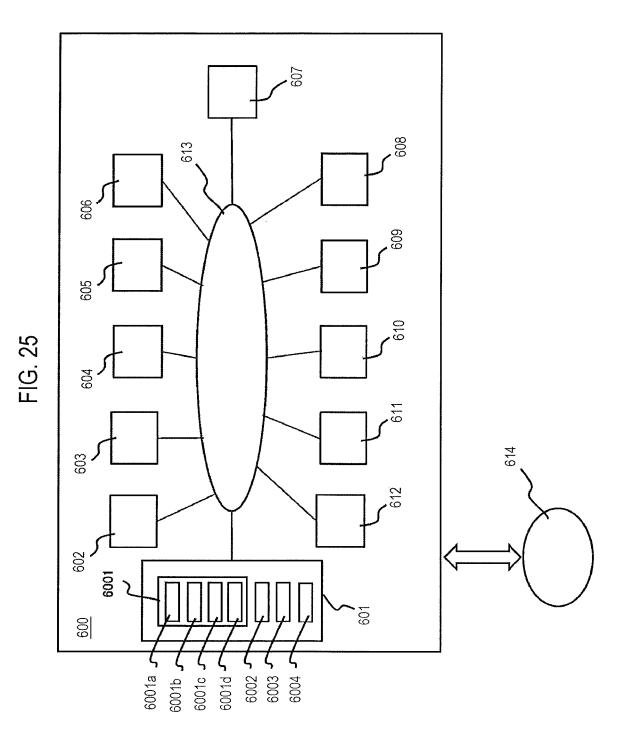

FIG. **25** is an explanatory view illustrating a system according to an embodiment.

FIG. **26** is a table illustrating a relationship between distributions of a first insulating film and control values of individual mass flow controllers.

FIG. **27** is a table illustrating a relationship between distributions of a first insulating film and control values of individual mass flow controllers.

FIG. **28** is a table illustrating a relationship between distributions of a first insulating film, control values of individual mass flow controllers and control values of individual heaters.

FIG. **29** is a table illustrating a relationship between distributions of a first insulating film, control values of individual mass flow controllers and control values of individual heaters.

## DETAILED DESCRIPTION

Embodiments of the present disclosure will now be described.

One of processes of manufacturing a semiconductor <sup>5</sup> device will be described with reference to FIG. **1**. (First Insulating Film Forming Step **S101**)

With regard to a first insulating film forming step S101, a wafer 200 will be described with reference to FIGS. 2 and 3. FIG. 2 illustrates a state before an insulating film is formed.

Source/drain regions 2001, each of which is configured by a source or a drain, are formed in the wafer 200. Channel regions 2002 are formed between the source/drain regions 2001. On a surface 200*a* of the wafer 200, gate electrodes 2003 are formed above the respective channel regions 2002. Outer walls 2004 serving to suppress a current flow from sidewalls of the gate electrodes 2003 are formed around the gate electrodes 2003. The source/drain regions 2001 and the gate electrodes 2003 are used as a part of a circuit configuration of a semiconductor device.

Subsequently, the first insulating film forming step S101 will be described with reference to FIG. **3**. If the wafer **200** is loaded into a substrate processing apparatus (first-insu-25 lating-film forming apparatus) which forms a first insulating film, a silicon-containing gas and an oxygen-containing gas are supplied into a process chamber of the substrate processing apparatus. The gases thus supplied react within the process chamber to form a first interlayer insulating film **30 2005** (simply referred to as an insulating film **2005**) which insulates circuits or electrodes adjoining each other. The insulating film **2005** is formed of, e.g., a silicon oxide film (SiO<sub>2</sub> film). The silicon-containing gas may be, e.g., a TEOS (tetraethyl orthosilicate, Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub>) gas. The oxygen-con-35 taining gas may be, e.g., an oxygen gas (O<sub>2</sub>).

If the insulating film **2005** is formed after a desired time is elapsed, the wafer **200** is unloaded from the substrate processing apparatus (first-insulating-film forming apparatus). The insulating film **2005** is used as an interlayer 40 insulating film.

The insulating film **2005** formed by the first-insulatingfilm forming apparatus will now be described with reference to FIG. **3**. As already described, a plurality of gate electrodes **2003** having a convex shape is formed in the wafer **200**. In 45 the case where a film is formed on the wafer **200** of this state, the heights from the substrate surface **200***a* to the upper end of the insulating film **2005** are not aligned with each other. Thus, the heights from the substrate surface **200***a* to the upper end of the insulating film **2005** vary in the plane of the 50 wafer **200**. For example, the height of the insulating film formed between the gate electrodes **2003** becomes smaller than the height of the insulating film formed on the gate electrodes **2003**. Consequently, dents **2006** are formed. The wafer **200** is unloaded from the process chamber after the 55 insulating film **2005** is formed.

However, in view of the relationship between a patterning step S108 and either or both of a first metal film forming step S110 and a second metal film forming step S111 which will be described later, there is required a state in which the dents 60 2006 do not exist. Thus, in order to eliminate the dents 2006, the insulating film 2005 is polished in the next polishing step S102.

(Insulating Film Polishing Step S102)

Next, an insulating film polishing step S102 of polishing 65 the insulating film 2005 will be described. The polishing step is also referred to as a CMP (Chemical Mechanical

Polishing) step. The wafer **200** unloaded from the firstinsulating-film forming apparatus is loaded into a polishing apparatus **400**.

Details of the polishing step will be described below. After unloaded from the first-insulating-film forming apparatus, the wafer **200** is loaded into the polishing apparatus **400** illustrated in FIG. **4**.

In FIG. 4, reference numeral 401 denotes a polishing disc and reference numeral 402 denotes an abrasive cloth which polishes the wafer 200. The polishing disc 401 is connected to a rotation mechanism (not shown). When polishing the wafer 200, the polishing disc 401 rotates in a direction of an arrow 406.

Reference numeral **403** denotes a polishing head. A shaft **404** is connected to an upper surface of the polishing head **403**. The shaft **404** is connected to a rotation mechanism and a vertical drive mechanism (not shown). While polishing the wafer **200**, the shaft **404** rotates in a direction of an arrow **407**.

Reference numeral **405** denotes a supply pipe configured to supply slurry (abrasive). While the wafer **200** is being polished, the slurry is supplied from the supply pipe **405** to the abrasive cloth **402**.

Subsequently, details of the polishing head 403 and a peripheral structure thereof will be described with reference to FIG. 5. FIG. 5 is a cross-sectional view illustrating the polishing head 403 and a peripheral structure thereof. The polishing head 403 includes a top ring 403a, a retainer ring 403b and an elastic mat 403c. While the wafer 200 is being polished, the outer side of the wafer 200 is surrounded by the retainer ring 403b and the wafer 200 is pushed against the abrasive cloth 402 by the elastic mat 403c. Grooves 403d are formed in the retainer ring 403b to allow the slurry to pass through the grooves 403d from an outer side of the retainer ring to an inner side thereof. The grooves 403d are formed in a plural number along a circumferential direction in conformity with the shape of the retainer ring 403b. Used slurry is replaced by unused fresh slurry through the grooves 403d.

Subsequently, an operation at this step will be described. When the wafer 200 is loaded into the polishing head 403, the slurry is supplied from the supply pipe 405 and the polishing disc 401 and the polishing head 403 are rotated. The slurry flows into the retainer ring 403*b* to polish a surface of the wafer 200. Through this polishing, as illustrated in FIG. 6, the heights of the insulating film 2005 can be aligned with each other. After the wafer 200 is polished for a predetermined period of time, the wafer 200 is unloaded from the polishing apparatus 400. The term "height" used herein refers to a height from the wafer surface 200*a* to the upper end of the insulating film 2005, namely to the surface of the insulating film 2005.

It has been found that even if the wafer **200** is polished by the CMP apparatus **400** to align the heights of the insulating film **2005**, the heights of the insulating film may not be aligned in the plane of the wafer **200** as illustrated in FIG. 7. For example, it has been found that there may appear distribution A in which a film thickness of a peripheral surface of the wafer **200** is smaller than a film thickness of a central surface thereof or distribution B in which a film thickness of a central surface of the wafer **200** is smaller than a film thickness of a peripheral surface thereof.

When there is a bias in the film thickness distribution, a problem is posed in that a variation in a width of a pattern is generated at a patterning step which will be described later. Similarly, a problem is posed in that a variation in a height from the wafer surface 200a to a metal film surface

is generated at a first metal film forming step which will be described later. Due to these problems, a variation in the characteristics of a metal film is generated, which may result in a reduction of yield rate.

According to the results of extensive researches on this 5 problem conducted by the inventors, it has been found that distribution A and distribution B have their own causes. The causes will be described hereinafter.

The cause of distribution A resides in a supply method of slurry with respect to the wafer 200. As set forth above, the 10 slurry supplied to the abrasive cloth 402 is supplied from the periphery of the wafer 200 through the retainer ring 403b. Thus, the slurry used to polish the peripheral surface of the wafer 200 flows toward the central surface of the wafer 200, while fresh slurry flows onto the peripheral surface of the 15 wafer 200. Since the fresh slurry has high polishing efficiency, the peripheral surface of the wafer 200 is polished more heavily than the central surface of the wafer 200. It has been found from the foregoing that the film thickness of the insulating film 2005 has distribution A. 20

The cause of distribution B resides in the wear of the retainer ring 403b. When a large amount of wafers 200 are polished by the polishing apparatus 400, a front end of the retainer ring 403b pressed against the abrasive cloth 402 is worn and the grooves 403d or the surface of the retainer ring 25 403b making contact with the abrasive cloth 402 is deformed. For this reason, slurry to be supplied may not be supplied to an inner circumference of the retainer ring 403b. In this case, the slurry is not supplied to the peripheral surface of the wafer 200. Therefore, the central surface of 30 the wafer 200 is polished while the peripheral surface thereof is not polished. Thus, it has been found that the film thickness of the insulating film 2005 has distribution B.

Accordingly, in the present embodiment, as will be described later, a step of polishing the insulating film 2005 35 on the wafer 200 by the polishing apparatus 400 and subsequently aligning the heights of a laminated insulating film in the substrate plane is performed. The term "laminated insulating film" used herein refers to a film obtained by overlapping a below-described insulating film 2007 with the 40 insulating film 2005. In other words, the laminated insulating film includes the insulating film 2005 as a portion thereof and includes the insulating film 2007 as another portion thereof.

As a specific method for aligning the heights, a film 45 thickness distribution of the insulating film 2005 is measured at a film thickness measuring step S103 after the polishing step S102, and a second insulating film forming step S104 is executed according to the measurement data. By doing so, a variation in a width of a pattern is suppressed 50 at a patterning step which will be described later. Similarly, a variation in a height from the wafer surface 200a to a surface of a metal film is suppressed at a first metal film forming step which will be described later. (Film Thickness Measuring Step S103) 55

Subsequently, the film thickness measuring step S103 will be described. At the film thickness measuring step S103, the film thickness of the insulating film 2005 which has been subjected to the polishing is measured using a measuring apparatus. Since a general measuring apparatus can be used 60 loaded into the substrate processing apparatus 900 as a as the measuring apparatus, a detailed description thereof will be omitted. The term "film thickness" used herein refers to, for example, a height from the wafer surface 200a to the surface of the insulating film 2005.

After the polishing step S102, the wafer 200 is loaded into 65 the measuring apparatus. The measuring apparatus measures a film thickness (height) distribution of the insulating film

2005 by measuring film thicknesses of at least some points of the central surface and the peripheral surface of the wafer **200** that may be easily affected by the polishing apparatus 400. The measurement data are transmitted to a belowdescribed substrate processing apparatus 900 via a host device. After the measurement, the wafer 200 is unloaded from the measuring apparatus.

(Second Insulating Film Forming Step S104)

Subsequently, a second insulating film forming step will be described. The second insulating film is identical in component and composition with the first insulating film 2005. At this step, as illustrated in FIGS. 8A and 8B or FIGS. 10A and 10B, a second interlayer insulating film 2007 (also referred to as an insulating film 2007 or a correction film) is formed on the first insulating film 2005 which has been subjected to the polishing. In the subject specification, a film obtained by overlapping the first insulating film 2005 and the second insulating film 2007 with each other is referred to as a laminated insulating film.

The second interlayer insulating film **2007** is formed so as to correct the film thickness distribution of the first interlayer insulating film 2005 which has been subjected to the polishing. More preferably, the insulating film 2007 is formed to align the surface heights of the insulating film 2007. The term "height" used herein refers to a surface height of the insulating film 2007, namely a distance from the wafer surface 200a to the surface of the insulating film 2007.

Hereinafter, this step will be described with reference to FIGS. 8A to 16. FIGS. 8A and 8B are views illustrating the insulating film 2007 formed at this step when the first insulating film 2005 has distribution A. FIG. 9 is an explanatory view illustrating film thickness distribution A and corrected film thickness distribution A'. FIGS. 10A and 10B are views illustrating the insulating film 2007 formed at this step when the first insulating film 2005 has distribution B. FIG. 11 is an explanatory view illustrating film thickness distribution B and corrected film thickness distribution B'. FIGS. 12 to 16 are views illustrating a substrate processing apparatus for realizing this step.

FIG. 8A is a top view illustrating the wafer 200 available after the insulating film 2007 is formed. FIG. 8B is a view illustrating the center and outer periphery of the wafer 200 excerpted from a cross-section taken along line  $\alpha$ - $\alpha$ ' in FIG. 8A in the case of film thickness distribution A.

FIG. 10A is a top view illustrating the wafer 200 available after the insulating film 2007 is formed. FIG. 10B is a view illustrating the center and outer periphery of the wafer 200 excerpted from a cross-section taken along line  $\alpha$ - $\alpha$ ' in FIG. 10A in the case of film thickness distribution B.

In the subject specification, the first insulating film existing on the central surface of the wafer 200 will be referred to as an insulating film 2005*a* and the second insulating film existing on the central surface of the wafer 200 will be referred to as an insulating film 2007a. The first insulating film existing on the peripheral surface of the wafer 200 will be referred to as an insulating film 2005b and the second insulating film existing on the peripheral surface of the wafer 200 will be referred to as an insulating film 2007b.

The wafer 200 unloaded from the measuring apparatus is second-insulating-film forming apparatus illustrated in FIG. 12

The substrate processing apparatus 900 controls the film thickness of the insulating film 2007 in the substrate plane based on the data measured at the film thickness measuring step S103. For example, if the data received from the host device are data indicative of distribution A, the substrate processing apparatus 900 controls the film thickness such that the thickness of the insulating film 2007*b* on the peripheral surface of the wafer 200 becomes larger and such that the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*b* on 5 the peripheral surface of the wafer 200. Furthermore, if the data received from the host device are data indicative of distribution B, the substrate processing apparatus 900 controls the film thickness such that the thickness of the insulating film 2007*a* on the central surface of the wafer 200 becomes larger and such that the insulating film 2007*b* on the peripheral surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200 becomes thinner than the insulating film 2007*a* on the central surface of the wafer 200.

More preferably, the thickness of the second insulating 15 film 2007 is controlled such that the height of the laminated insulating film obtained by overlapping the first insulating film 2005 and the second insulating film 2007 with each other falls within a predetermined range in the wafer plane. In other words, the heights are aligned by controlling the 20 film thickness distribution of the second insulating film 2007 such that the height distribution of the second insulating film 2007 in the substrate plane falls within a predetermined range. That is to say, as illustrated in FIGS. 8A, 8B, 10A and 10B, the height H1a from the wafer surface 200a to the 25 upper end of the second insulating film 2007*a* on the central surface of the wafer 200 and the height H1b from the wafer surface 200a to the upper end of the second insulating film 2007b on the peripheral surface of the wafer 200 can be made equal to each other.

Next, the substrate processing apparatus 900 capable of controlling the film thickness of each of the insulating films 2007a and 2007b will be described in detail.

The substrate processing apparatus **900** according to the present embodiment will be described. As illustrated in FIG. 35 **12**, the substrate processing apparatus **900** is configured as a single-substrate-type substrate processing apparatus.

As shown in FIG. 12, the substrate processing apparatus 900 includes a process vessel 202. The process vessel 202 is configured as, e.g., a flat airtight vessel having a circular 40 horizontal cross-section. Furthermore, the process vessel 202 is made of a metallic material such as, e.g., aluminum (Al) or stainless steel (SUS), or quartz. A process space (process chamber) 201, in which the wafer 200 such as a silicon wafer as a substrate is processed, and a transfer space 45 203 are formed in the process vessel 202. The process vessel 202 is configured by an upper vessel 202*a* and a lower vessel 202b. A partition plate 204 is installed between the upper vessel 202a and the lower vessel 202b. A space, which is surrounded by the upper vessel 202a and is provided above 50 the partition plate 204, is referred to as the process space (also, referred to as a process chamber) 201. A space, which is surrounded by the lower vessel 202b and is provided below the partition plate 204, is referred to as the transfer space 203.

A substrate loading/unloading port **206** adjacent to a gate valve **205** is formed on a side surface of the lower vessel **202***b*. The wafer **200** moves into and out of a transfer chamber (not shown) through the substrate loading/unloading port **206**. A plurality of lift pins **207** is installed in a 60 bottom portion of the lower vessel **202***b*.

A substrate support part 210 configured to support the wafer 200 is installed in the process chamber 201. The substrate support part 210 includes a substrate mounting surface 211 on which the wafer 200 is mounted, and a 65 substrate mounting stand 212 having the substrate mounting surface 211 on a surface thereof. Preferably, a heater 213 as

a heating part is installed. By installing the heating part, it is possible to heat the substrate and to improve the quality of a film formed on the substrate. Through-holes **214** through which the lift pins **207** pass may be formed in the substrate mounting stand **212** in such positions corresponding to the lift pins **207**, respectively.

The substrate mounting stand 212 is supported by a shaft 217. The shaft 217 passes through a bottom portion of the process vessel 202. Furthermore, the shaft 217 is connected to an elevator mechanism 218 outside the process vessel 202. By operating the elevator mechanism 218 to move the shaft 217 and the substrate mounting stand 212 up and down, the wafer 200 mounted on the substrate mounting surface 211 can be moved up and down. Further, the periphery of the lower end of the shaft 217 is covered with a bellows 219 so that the inside of the process vessel 202 is kept airtight.

When transferring the wafer 200, the substrate mounting stand 212 is moved down such that the substrate mounting surface 211 is located in a position of the substrate loading/ unloading port 206 (or a wafer transfer position). When processing the wafer 200, as shown in FIG. 12, the substrate mounting stand 212 is moved up until the wafer 200 reaches a processing position (or a wafer processing position) within the process chamber 201.

Specifically, when the substrate mounting stand **212** is moved down to the wafer transfer position, the upper end portions of the lift pins **207** protrude from an upper surface of the substrate mounting surface **211** so that the lift pins **207** support the wafer **200** from below. Further, when the substrate mounting stand **212** is moved up to the wafer processing position, the lift pins **207** are retracted from the upper surface of the substrate mounting surface **211** so that the substrate mounting surface **211** supports the wafer **200** from below. In addition, the lift pins **207** are preferably made of a material such as, e.g., quartz, alumina or the like, because the lift pins **207** make direct contact with the wafer **200**. Moreover, an elevator mechanism may be installed in the lift pins **207** such that the substrate mounting stand **212** and the lift pins **207** are moved relatively to each other.

The heater **213** has a configuration capable of individually heat-controlling the central surface which is the center of the wafer **200** and the peripheral surface which is the outer periphery of the wafer **200**. For example, the heater **213** includes a central zone heater **213***a* installed at the center of the substrate mounting surface **211** and fox med in an annular shape when viewed from above and an outer zone heater **213***b* formed in an annular shape and installed in the periphery of the central zone heater **213***a*. The central zone heater **213***a* heats the central surface of the wafer **200**. The outer zone heater **213***b* heats the peripheral surface of the wafer **200**.

Each of the central zone heater 213a and the outer zone heater 213b is connected to a heater temperature control part 55 215 via a heater power supply line. The heater temperature control part 215 controls the temperatures of the central surface and the peripheral surface of the wafer 200 by controlling the power supply to each heater.

A temperature measuring instrument 216a and a temperature measuring instrument 216b for measuring a temperature of the wafer 200 are embedded in the substrate mounting stand 212. The temperature measuring instrument 216a is installed in a central portion of the substrate mounting stand 212 so as to measure a temperature in the vicinity of the central zone heater 213a. The temperature measuring instrument 216b is installed on a peripheral surface of the substrate mounting stand 212 so as to measure a temperature in the vicinity of the outer zone heater 213b. The temperature measuring instrument 216a and the temperature information reception part 216c. The temperatures measured by the respective temperature information reception part 216c. The temperature information reception part 216c transmits the received temperature information to a controller 260 which will be described later. The controller 260 controls a heater temperature based on the received temperature information received from a host device. Further, the temperature measuring instrument 216a, the temperature measuring instrument 216a and the temperature information reception part 216c is collectively called a temperature detecting part 216.

(Exhaust System)

An exhaust port **221** is formed on an upper surface of an inner wall of the process chamber **201** (the upper vessel **202***a*) so as to exhaust an atmosphere of the process chamber **201**. An exhaust pipe **224** as a first exhaust pipe is connected 20 to the exhaust port **221**. A pressure regulator **222** such as an auto pressure controller (APC) for controlling the internal pressure of the process chamber **201** to a predetermined pressure and a vacuum pump **223** are serially connected to the exhaust pipe **224** in the named order. A first exhaust part 25 (exhaust line) is mainly configured by the exhaust port **221**, the exhaust pipe **224** and the pressure regulator **222**. In addition, the vacuum pump **223** may be included in the first exhaust part.

(Buffer Chamber)

A buffer chamber 232 is installed above the process chamber 201. The buffer chamber 232 is defined by a sidewall 232*a* and a ceiling 232*b*. The buffer chamber 232 includes a shower head 234. A gas supply path 235 is defined between an inner wall 232*a* of the buffer chamber 232 and 35 the shower head 234. That is to say, the gas supply path 235 is installed to surround a sidewall 234*b* of the shower head 234.

A dispersion plate 234a is installed in the wall that separates the shower head 234 and the process chamber 201. 40 The dispersion plate 234a has, for example, a disc shape. When viewed from the side of the process chamber 201, the gas supply path 235 is positioned between the shower head sidewall 234b and the sidewall 232a and is installed around the dispersion plate 234a in a horizontal direction as illus- 45 trated in FIG. 13.

A gas introduction pipe 236 and a gas introduction pipe 237 extend through the ceiling 232*b* of the buffer chamber 232. Furthermore, a gas introduction pipe 238 and a gas introduction pipe 239 are connected to the ceiling 232*b* of 50 the buffer chamber 232. The gas introduction pipe 236 and the gas introduction pipe 237 are connected to the shower head 234. The gas introduction pipe 236 and the gas introduction pipe 238 are connected to a first gas supply system which will be described later. The gas introduction 55 pipe 237 and the gas introduction pipe 239 are connected to a second gas supply system which will be described later.

The gas introduced from the gas supply pipe **236** and the gas supply pipe **237** is supplied into the process chamber **201** via the shower head **234**. The gas introduced from the gas 60 supply pipe **238** and the gas supply pipe **239** is supplied into the process chamber **201** via the gas supply path **235**.

The gas supplied from the shower head **234** is supplied to the center of the wafer **200**. The gas supplied from the gas supply path **235** is supplied to the edge of the wafer **200**. The 65 peripheral surface (edge) of the wafer refers to a periphery with respect to the center of the wafer described above. The

shower head **234** is made of a material such as, e.g., quartz, alumina, stainless steel, aluminum or the like.

With this configuration, the shower head 234 is installed in a position where the shower head 234 faces the central surface of the wafer 200 mounted on the substrate mounting surface 211. Thus, the gas supplied from the shower head 234 can be supplied to the central surface of the wafer 200. Furthermore, the gas supply path 235 is installed in a position where the gas supply path 235 faces the peripheral surface of the wafer 200. Thus, the gas supplied from the gas supply path 235 can be supplied to the peripheral surface of the wafer 200.

(Gas Supply System)

(First Gas Supply system)

Next, a first gas supply system will be described with reference to FIG. 14. A1 indicated in FIG. 14 is connected to A1 indicated in FIG. 12. A2 indicated in FIG. 14 is connected to A2 indicated in FIG. 12. That is to say, a gas supply pipe 241a is connected to the gas introduction pipe 236. A gas supply pipe 242a is connected to the gas introduction pipe 238.

A junction pipe **240***b*, a mass flow controller **241***b* and a valve **241***c* are installed in the gas supply pipe **241***a* in the named order from the upstream side. A flow rate of a gas that passes through the gas supply pipe **241***a* is controlled by the mass flow controller **241***b* and the valve **241***c*. A gas source **240***a* of a first process gas is installed at the upstream side of the junction pipe **240***b*. The first process gas is a silicon-containing gas. For example, disilane (Si<sub>2</sub>H<sub>6</sub>) is used as the first process gas.

Preferably, a first inert gas supply pipe 243a for supplying an inert gas is connected to the downstream side of the valve 241c. An inert gas source 243b, a mass flow controller 243cand a valve 243d are installed in the inert gas supply pipe 243a in the named order from the upstream side. As the inert gas, for example, a helium (He) gas is used. The inert gas is added to the gas flowing through the gas supply pipe 241aand is used as a dilution gas. A concentration or a flow rate of the process gas supplied through the gas introduction pipe 236 and the shower head 234 may be more optimally tuned by controlling the mass flow controller 243c and the valve 243d.

A junction pipe 240b, a mass flow controller 242b and a valve 242c are installed in the gas supply pipe 242a connected to the gas introduction pipe 238, in the named order from the upstream side. A flow rate of a gas that passes through the gas supply pipe 242a is controlled by the mass flow controller 242b and the valve 242c. The gas source 240a of the first process gas is installed at the upstream side of the junction pipe 240b.

Preferably, a second inert gas supply pipe 244a for supplying an inert gas is connected to the downstream side of the valve 242c. An inert gas source 244b, a mass flow controller 244c and a valve 244d are installed in the inert gas supply pipe 244a in the named order from the upstream side. As the inert gas, for example, a helium (He) gas is used. The inert gas is added to the gas flowing through the gas supply pipe 242a and is used as a dilution gas. A concentration or a flow rate of the gas flowing through the gas introduction pipe 238 and the gas supply path 235 may be more optimally tuned by controlling the mass flow controller 244c and the valve 244d.

The gas supply pipe 241a, the mass flow controller 241b, the valve 241c, the gas supply pipe 242a, the mass flow controller 242b, the valve 242c and the junction pipe 240b are collectively referred to as a first gas supply system.

Furthermore, the gas source 240a, the gas introduction pipe 236 and the gas introduction pipe 238 may be included in the first gas supply system.

The first inert gas supply pipe 243a, the mass flow controller 243*c*, the valve 243*d*, the second inert gas supply pipe 244a, the mass flow controller 244c and the valve 244d are collectively referred to as a first inert gas supply system. Furthermore, the inert gas source 243b and the inert gas source 244b may be included in the first inert gas supply system. Moreover, the first inert gas supply system may be 10 included in the first gas supply system.

In the present embodiment, the gas supply pipe 241a is referred to as a first gas supply pipe and the gas supply pipe **242***a* is referred to as a second gas supply pipe.

Furthermore, the mass flow controller 241b alone or the 15 combination of the mass flow controller 241b and the valve 241c is referred to as a first process gas flow rate control part. Moreover, the mass flow controller 242b alone or the combination of the mass flow controller 242b and the valve 242c is referred to as a second process gas flow rate control 20 part.

Furthermore, the mass flow controller 243c alone or the combination of the mass flow controller 243c and the valve **243***d* is referred to as a first inert gas flow rate control part. Moreover, the mass flow controller 244c alone or the com- 25 bination of the mass flow controller 244c and the valve 244d is referred to as a second inert gas flow rate control part. (Second Gas Supply System)

Next, a second gas supply system will be described with reference to FIG. 15. B1 indicated in FIG. 15 is connected 30 to B1 indicated in FIG. 12. B2 indicated in FIG. 15 is connected to B2 indicated in FIG. 12. That is to say, a gas supply pipe 251a is connected to the gas introduction pipe 237. A gas supply pipe 252a is connected to the gas introduction pipe 239.

A junction pipe 250b, a mass flow controller 251b and a valve 251c are installed in the gas supply pipe 251a in the named order from the upstream side. A flow rate of a gas that passes through the gas supply pipe 251a is controlled by the mass flow controller 251b and the value 251c. A gas source 40 250a of a second process gas is installed at the upstream side of the junction pipe 250b. The second process gas is an oxygen-containing gas. For example, an oxygen gas  $(O_2)$  is used as the second process gas.

Preferably, a third inert gas supply pipe 253a for supply- 45 ing an inert gas is installed at the downstream side of the valve 251c. An inert gas source 253b, a mass flow controller 253c and a valve 253d are installed in the inert gas supply pipe 253*a* in the named order from the upstream side. As the inert gas, for example, a helium (He) gas is used. The inert 50 gas is used as a dilution gas that dilutes the gas flowing through the gas supply pipe 251a. A concentration or a flow rate of the gas supplied through the gas introduction pipe 237 and the shower head 234 may be more optimally tuned by controlling the mass flow controller 253c and the valve 55 troller 260 that controls the operations of the respective parts 253d.

A junction pipe 250b, a mass flow controller 252b and a valve 252c are installed in the gas supply pipe 252a in the named order from the upstream side. A flow rate of a gas that passes through the gas supply pipe 252a is controlled by the 60 mass flow controller 252b and the value 252c. The gas source 250a of the second process gas is installed at the upstream side of the junction pipe 250b. The second process gas is an oxygen-containing gas. For example, an oxygen gas  $(O_2)$  is used as the second process gas. 65

Preferably, a fourth inert gas supply pipe 254a for supplying an inert gas is installed at the downstream side of the valve 252c. An inert gas source 254b, a mass flow controller 254c and a valve 254d are installed in the inert gas supply pipe 254*a* in the named order from the upstream side. As the inert gas, for example, a helium (He) gas is used. The inert gas is used as a dilution gas that dilutes the gas flowing through the gas supply pipe 252a. A concentration or a flow rate of the gas flowing through the gas introduction pipe 239 and the gas supply path 235 may be more optimally tuned by controlling the mass flow controller 254c and the valve 254d.

The gas supply pipe 251*a*, the mass flow controller 251*b*, the value 251c, the gas supply pipe 252a, the mass flow controller 252*b*, the valve 252c and the junction pipe 250bare collectively referred to as a second gas supply system. Furthermore, the gas source 250a, the gas introduction pipe 237 and the gas introduction pipe 239 may be included in the second gas supply system.

The third inert gas supply pipe 253a, the mass flow controller 253c, the valve  $\overline{253d}$ , the fourth inert gas supply pipe 254a, the mass flow controller 254c and the value 254dare collectively referred to as a second inert gas supply system. Furthermore, the inert gas source 253b and the inert gas source 254b may be included in the second inert gas supply system. Moreover, the second inert gas supply system may be included in the second gas supply system. In addition, the first gas supply system and the second gas supply system are collectively referred to as a gas supply system.

In the present embodiment, the gas supply pipe 251a is referred to as a third gas supply pipe and the gas supply pipe 252*a* is referred to as a fourth gas supply pipe.

Furthermore, the mass flow controller 251b alone or the combination of the mass flow controller 251b and the valve **251***c* is referred to as a third process gas flow rate control part. Moreover, the mass flow controller 252b alone or the combination of the mass flow controller **252***b* and the valve 252c is referred to as a fourth process gas flow rate control part.

Furthermore, the mass flow controller 253c alone or the combination of the mass flow controller 253c and the valve 253d is referred to as a third inert gas flow rate control part. Moreover, the mass flow controller 254c alone or the combination of the mass flow controller 254c and the value 254dis referred to as a fourth inert gas flow rate control part.

As described above, the mass flow controller and the valve are installed in each of the first gas supply system and the second gas supply system. It is therefore possible to individually control the amounts of gases. Furthermore, the mass flow controller and the valve are installed in each of the first inert gas supply system and the second inert gas supply system. It is therefore possible to individually control the concentrations of gases.

(Control Part)

The substrate processing apparatus 900 includes a conof the substrate processing apparatus 900.

An outline of the controller 260 is illustrated in FIG. 16. The controller **260** serving as a control part (control means) is configured as a computer including a central processing unit (CPU) 260a, a random access memory (RAM) 260b, a memory device 260c, an I/O port 260d, a comparison part 260f and a transmission/reception part 260g. The RAM 260b, the memory device 260c and the I/O port 260d are configured to exchange data with the CPU 260a via an internal bus 260e according to an instruction of the transmission/reception part 260g. An input/output device 261 configured as, e.g., a touch panel or the like, and an external

memory device 262 are connectable to the controller 260. In addition, there is installed a reception part 263 electrically connected to a host device 270 via a network. The reception part 263 may receive information of other devices from the host device.

The memory device 260c is configured by, for example, a flash memory, a hard disk drive (HDD), or the like. A control program for controlling the operations of the substrate processing apparatus, a program recipe in which a sequence, condition, or the like for a substrate processing 10 described later is written, a table to be described later, and the like are readably stored in the memory device 260c. In addition, the process recipe is a combination of sequences which causes the controller 260 to execute each sequence in a substrate processing process described later in order to 15 obtain a predetermined result. The process recipe functions as a program. Hereinafter, the program recipe, the control program, and the like will be generally and simply referred to as a program. Furthermore, the term "program" used herein may be intended to include the program recipe alone, 20 the control program alone, or a combination of the program recipe and the control program. Moreover, the RAM 260b is configured as a memory area (work area) in which a program, data, or the like read by the CPU 260a is temporarily held.

The I/O port **260***d* is connected to the gate valve **205**, the elevator mechanism **218**, the heater **213**, the pressure regulator **222**, the vacuum pump **223** and the like. In addition, the I/O port **260***d* may be connected to the MFCs **241***b*, **242***b*, **243***c*, **244***c*, **251***b*, **252***b*, **253***c* and **254***c*, the valves **241***c*, 30 **242***c*, **243***d*, **244***d*, **251***c*, **252***d*, **253***d* and **254***d*, and the like.

The CPU **260***a* is configured to read the control program from the memory device **260***c* and to execute the control program. Furthermore, the CPU **260***a* is configured to read the process recipe from the memory device **260***c* according 35 to an operation command inputted from the input/output device **261**, or the like. In addition, the CPU **260***a* is configured to control the opening/closing operation of the gate valve **205**, the elevating operation of the elevator mechanism **218**, the operation of supplying electric power to 40 the heater **213**, the pressure regulating operation performed by the pressure regulator **222**, the on/off control of the vacuum pump **223**, the flow rate adjusting operations of the mass flow controllers, the operations of the valves, and the like, according to the contents of the read process recipe. 45

In addition, the controller 260 is not limited to being configured as a dedicated computer and may be configured as a general-purpose computer. For example, the controller 260 according to the present embodiment may be configured by preparing the external memory device 262 (e.g., a mag- 50 netic tape, a magnetic disc such as a flexible disc or a hard disc, an optical disc such as a compact disc (CD) or a digital versatile disc (DVD), a magneto-optical (MO) disc, or a semiconductor memory such as a universal serial bus (USB) memory or a memory card) which stores the program 55 described above, and installing the program on the generalpurpose computer using the external memory device 262. Furthermore, a means for supplying the program to the computer is not limited to the case of supplying the program through the external memory device 262. For example, the 60 program may be supplied using a communication means such as the Internet or a dedicated line without going through the external memory device 262. Moreover, the memory device 260c or the external memory device 262 is configured as a non-transitory computer-readable recording 65 medium. Hereinafter, these will be generally and simply referred to as a recording medium. Additionally, the term

"recording medium" used herein may be intended to include the memory device 260c alone, the external memory device 262 alone, or both the memory device 260c and the external memory device 262.

Subsequently, descriptions will be made on a table. The memory device **260***c* includes a table illustrated in FIG. **26**. The table illustrates a relationship between first insulating film distributions and control values  $\alpha$ **11** to  $\alpha$ **14** and  $\beta$ **12** to  $\beta$ **14** of the respective mass flow controllers. When the reception part **263** receives first insulating film distribution information, the CPU **260***a* reads the table from the memory part **260***b*. The comparison part **260***f* compares the read table and the received information. Data  $\alpha$ **11**,  $\alpha$ **12**,  $\alpha$ **13** and  $\alpha$ **14** calculated as a result of comparison are transmitted, as control values, to the respective mass flow controllers.

Next, a method of forming a film using the substrate processing apparatus 900 will be described. After the film thickness measuring step S103, the measured wafer 200 is loaded into the substrate processing apparatus 900. In the following descriptions, the operations of respective parts that constitute the substrate processing apparatus 900 are controlled by the controller 260.

(Substrate Loading Step)

After the thickness of the first insulating film 2005 is measured at the film thickness measuring step S103, the wafer 200 is loaded into the substrate processing apparatus 900. Specifically, the substrate support part 210 is moved down by the elevator mechanism 218 such that the lift pins 207 protrude from the through-holes 214 toward the upper surface side of the substrate support part 210. Furthermore, after the internal pressure of the process chamber 201 is regulated to a predetermined pressure, the gate valve 205 is opened and the wafer 200 is mounted onto the lift pins 207 from the gate valve 205. After the wafer 200 is mounted onto the lift pins 207, the substrate support part 210 is moved up to a predetermined position by the elevator mechanism 218 so that the wafer 200 is transferred from the lift pins 207 to the substrate support part 210.

(Pressure Reducing and Temperature Increasing Step)

Thereafter, the interior of the process chamber 201 is evacuated through the exhaust pipe 224 such that the internal pressure of the process chamber 201 reaches a predetermined pressure (vacuum degree). At this time, the opening degree of the APC valve as the pressure regulator 222 is feedback-controlled based on the pressure value measured by a pressure sensor. Furthermore, the amount of electric current supplied to the heater 213 is feedback-controlled based on the temperature value detected by the temperature detecting part 216, such that the internal temperature of the process chamber 201 reaches a predetermined temperature. Specifically, the substrate support part 210 is preheated by the heater 213. After a temperature change in the wafer 200 or the substrate support part 210 disappears, the wafer 200 and the substrate support part 210 are left alone for a predetermined period of time. During this period, when moisture remains in the process chamber 201 or degassing occurs from a member, it may be removed by vacuumexhausting or purging through the supply of an inert gas. By doing so, a preparation preceding a film forming process is completed. When evacuating the interior of the process chamber 201 to a predetermined pressure, the interior of the process chamber 201 may be first evacuated up to a reachable vacuum degree.

After the wafer 200 is mounted on the substrate support part 210 and the atmosphere within the process chamber 201 is stabilized, the mass flow controller 241*b*, the mass flow controller 251*b* and the mass

flow controller **252***b* are actuated and the opening degrees of the valve **241***c*, the valve **242***c*, the valve **251***c* and the valve **252***c* are also adjusted. At this time, the mass flow controller **243***c*, the mass flow controller **244***c*, the mass flow controller **253***c* and the mass flow controller **254***c* may be actuated and <sup>5</sup> the opening degrees of the valve **243***d*, the valve **244***d*, the valve **253***d* and the valve **254***d* may be adjusted.

(Gas Supply Step)

At a gas supply step, gases are supplied into the process chamber **201** from the first gas supply system and the second gas supply system.

When supplying the gases, an amount (or a concentration) of a process gas supplied to the central surface of the wafer **200** and an amount (or a concentration) of a process gas 15 supplied to the peripheral surface of the wafer **200** are respectively controlled by controlling the mass flow controllers and the valves of the first gas supply system and the second gas supply system according to the film thickness distribution data of the insulating film **2005** received from 20 the host device **270**. More preferably, the in-plane temperature gradient of the wafer **200** is controlled by controlling the central zone heater **213***a* and the outer zone heater **213***b* according to the measurement data received from the host device **270**.

The gases supplied into the process chamber 201 are decomposed within the process chamber 201 to form the second insulating film 2007 on the first insulating film 2005 which has been subjected to the polishing.

After a predetermined period of time is elapsed, the 30 respective valves are closed to stop the supply of gases.

At this time, the temperature of the heater **213** is set at a temperature which does not adversely affect the alreadyformed configurations such as the gate electrodes **2003** and the like. For example, the temperature of the heater **213** is set 35 such that the temperature of the wafer **200** falls within a range of 200 to 500 degrees C., specifically 300 to 450 degrees C. As the inert gas, in addition to the He gas, any gas may be used as long as it does not adversely affect the film. For example, a rare gas such as Ar, N<sub>2</sub>, Ne, Xe or the like 40 may be used.

(Substrate Unloading Step)

After the film forming step is finished, the substrate support part 210 is moved down by the elevator mechanism 218 such that the lift pins 207 protrude from the through-45 holes 214 to the upper surface side of the substrate support part 210. Furthermore, after the internal pressure of the process chamber 201 is regulated to a predetermined pressure, the gate valve 205 is opened and the wafer 200 is transferred from above the lift pins 207 to the outside of the 50 gate valve 205.

Subsequently, a method of controlling the thickness of the second interlayer insulating film using this apparatus will be described. As described above, after the polishing step S102 is completed, the first poly-Si film 2005 has different film 55 thicknesses in the central surface and the peripheral surface of the wafer 200. At the measuring step S103, the film thickness distribution is measured. The measurement result is stored in the RAM 260*b* through the host device 270. The stored data are compared with a table stored in the memory 60 device 260*c* and the apparatus is controlled based on the corresponding control value.

Subsequently, a case where the data received from the host device and stored in the RAM **260***b* have distribution A will be described. The case of distribution A refers to a case 65 where the insulating film **2005***a* is thicker than the insulating film **2005***b* as illustrated in FIG. **7**.

In the case of distribution A, at this step, control is executed so that the insulating film 2007b formed on the peripheral surface of the wafer 200 becomes thick and so that the thickness of the insulating film **2007***a* formed on the central surface of the wafer 200 becomes smaller than the thickness of the insulating film 2007b. Specifically, when supplying the gas, control is executed so that the siliconcontaining gas supplied to the peripheral surface of the wafer 200 becomes larger in amount than the siliconcontaining gas supplied to the central surface of the wafer 200. By doing so, the height of the insulating film in the semiconductor device, namely the thickness of the laminated insulating film obtained by overlapping the insulating film 2007 with the insulating film 2005, can be corrected like target film thickness distribution A' illustrated in FIG. 9. That is to say, the thickness of the laminated insulating film can be corrected like film thickness distribution A'.

Specifically, a table illustrated in FIG. 26 is first read from the memory device 260c. The comparison part 260f com-20 pares the read data with the received film thickness distribution, thereby selecting the control values of the respective mass flow controllers. In this regard, a control value  $\alpha 101$  is selected with respect to the mass flow controller 241b. A control value  $\alpha 102$  is selected with respect to the mass flow 25 controller 242b. A control value  $\alpha 103$  is selected with respect to the mass flow controller 251b. A control value  $\alpha 104$  is selected with respect to the mass flow controller 252b. Thereafter, the transmission/reception part 260g transmits the control values to the respective mass flow control-30 lers via the I/O port 260d. The respective mass flow controllers are adjusted at the received control values so as to control the flow rates of gases.

In the first gas supply system, the mass flow controller **241***b* is controlled based on the received control value so as to control the amount of the silicon-containing gas supplied from the shower head **234** into the process chamber **201**. Furthermore, the mass flow controller **242***b* is controlled so as to supply the silicon-containing gas from the gas supply path **235** into the process chamber **201**. An exposure amount of the silicon-containing gas per unit area in a processing plane of the wafer **200** is controlled such that an exposure amount of the gas supplied from the gas supplied from the shower head. The term "exposure amount" used herein refers to an exposure amount of a main component of a process gas. In the present embodiment, the process gas is a silicon-containing gas and the main component is silicon.

Furthermore, in the second gas supply system, the mass flow controller 251b is controlled based on the received control value and the opening degree of the valve 251c is controlled to control the amount of the oxygen-containing gas supplied from the shower head 234. The amount of the oxygen-containing gas in the gas supply pipe 251a is set at an amount corresponding to the amount of the siliconcontaining gas in the gas supply pipe 241a. Moreover, the mass flow controller 252b is controlled and the opening degree of the valve 252c is controlled to supply the oxygencontaining gas in the gas supply path 235. The amount of the oxygen-containing gas in the gas supply pipe 252a is set at an amount corresponding to the amount of the siliconcontaining gas in the gas supply pipe 242a.

At this time, an exposure amount of the silicon-containing gas per unit area in a processing plane of the wafer **200** is controlled such that an exposure amount of the gas supplied from the gas supply path **235** becomes larger than an exposure amount of the gas supplied from the shower head **234**. The term "exposure amount" used herein refers to an exposure amount of a main component of a process gas. In the present embodiment, the process gas is a silicon-containing gas and the main component is silicon.

The silicon-containing gas and the oxygen-containing gas supplied through the shower head 234 are supplied onto the insulating film 2005a formed on the central surface of the wafer 200. The gases thus supplied form the insulating film 2007a on the insulating film 2005a as illustrated in FIGS. **8**A and **8**B.

The silicon-containing gas and the oxygen-containing gas <sup>10</sup> supplied through the gas supply path **235** are supplied onto the insulating film **2005***b* formed on the peripheral surface of the wafer **200**. The gases thus supplied form the insulating film **2007***b* on the insulating film **2005***b* as illustrated in <sup>15</sup> FIGS. **8**A and **8**B.

As described above, the exposure amount of the siliconcontaining gas per unit area in the processing plane of the wafer **200** is larger on the insulating film **2005***b* than on the insulating film **2005***a*. It is therefore possible to make the  $_{20}$ thickness of the insulating film **2007***b* larger than the thickness of the insulating film **2007***a*.

At this time, the thickness of the insulating film 2007 is controlled such that as illustrated in FIGS. 8A and 8B, a thickness H1b of the insulating film **2005**b and the insulating 25 film 2007b overlapped with each other becomes substantially equal to a thickness H1a of the insulating film 2005aand the insulating film 2007a overlapped with each other. More preferably, the thickness of the insulating film 2007 is controlled such that a difference between the distance from 30 the substrate surface 200a to the upper end of the insulating film 2007b and the distance from the substrate surface 200a to the upper end of the insulating film 2007a falls within a predetermined range. Even more preferably, the film thickness distribution of the second insulating film 2007 is 35 controlled such that the distribution of the heights of the insulating film 2007 (the upper end of the second interlayer insulating film) in the plane of the substrate falls within a predetermined range.

As an alternative method, the supply amounts of the 40 silicon-containing gas supplied through the gas supply pipe 241a and the gas supply pipe 242a may be made equal to each other and, instead, the concentrations of the siliconcontaining gas supplied through the gas supply pipe 241a and the gas supply pipe 242a may be controlled. When 45 controlling the concentrations of the silicon-containing gas, the concentrations of the silicon-containing gas passing through the gas supply pipe 241a and the gas supply pipe 242a are controlled by controlling the first inert gas supply system. In the case of distribution A, the concentration of the 50 silicon-containing gas passing through the gas supply pipe 241a is reduced and the concentration of the silicon-containing gas passing through the gas supply pipe 242a is made higher than the concentration of the silicon-containing gas passing through the gas supply pipe 241a. 55

Specifically, upon receiving film thickness distribution A, a table illustrated in FIG. 27 is read in place of the table illustrated in FIG. 26. The comparison part 260*f* compares the read table illustrated in FIG. 27 with the received film thickness distribution, thereby selecting control values  $\alpha$ 201 <sup>60</sup> to  $\alpha$ 208 of the mass flow controller 241*b*, the mass flow controller 243*c*, the mass flow controller 242*b*, the mass flow controller 244*c*, the mass flow controller 251*c*, the mass flow controller 253*c*, the mass flow controller 252*b* and the mass flow controller 254*c*. Thereafter, the transmission/ 65 reception part 260*g* transmits the control values to the respective mass flow controllers via the I/O port 260*d*. The

respective mass flow controllers are adjusted at the received control values so as to control the flow rates of gases.

By doing so, it is possible to more accurately control the exposure amount of the silicon-containing gas per unit area in the processing plane of the wafer **200** such that the gas amount supplied from the gas supply path **235** becomes larger than the gas amount supplied from the shower head **234**. By virtue of this control, the thickness of the insulating film **2007***b* can be reliably made larger than the thickness of the insulating film **2007***a*.

More preferably, the supply amounts of the silicon-containing gas supplied through the gas supply pipe 241a and the gas supply pipe 242a may be made different and the concentrations thereof may be made different. By virtue of this control, it is possible to supply the silicon-containing gas at a greater difference in the exposure amount of the silicon-containing gas per unit area. That is to say, it is possible to increase the film thickness difference between the insulating film 2007a and the insulating film 2007b. Accordingly, even if the height difference between the insulating film 2005a and the insulating film 2005b becomes larger at the insulating film polishing step S102, it is possible to align the heights.

Even more preferably, the central zone heater 213a and the outer zone heater 213b may be controlled in parallel with the aforementioned control of the process gas. In this case, a table illustrated in FIG. 28 is read in place of the tables illustrated in FIGS. 26 and 27. The comparison part 260f compares the read table illustrated in FIG. 28 with the received film thickness distribution, thereby selecting control values  $\alpha$ 301 to  $\alpha$ 304 of the mass flow controller 241*b*, the mass flow controller 243c, the mass flow controller 242b, the mass flow controller 244c, the mass flow controller 251c, the mass flow controller 253c, the mass flow controller 252b and the mass flow controller 254c and control values  $\alpha 305$  and  $\alpha 306$  of the heater 213a and the heater 213b. Thereafter, the transmission/reception part 260g transmits the control values to the respective mass flow controllers via the I/O port 260d. The respective mass flow controllers are adjusted at the received control values so as to control the flow rates of gases. Moreover, the transmission/reception part 260g transmits the control values to the heater temperature control part 215 via the I/O port 260d; accordingly, the heater temperature control part 215 performs a control operation so that the wafer 200 has a desired temperature distribution.

In the case of simultaneously controlling the inert gas supply system, a table illustrated in FIG. 29 is read in place of the table illustrated in FIG. 28. The comparison part 260fcompares the read table illustrated in FIG. 29 with the received film thickness distribution, thereby selecting control values  $\alpha 401$  to  $\alpha 408$  of the mass flow controller 241b, the mass flow controller 243c, the mass flow controller 242b, the mass flow controller 244c, the mass flow controller 251c, the mass flow controller 253c, the mass flow controller 252b and the mass flow controller 254c and control values  $\alpha 409$  and  $\alpha 410$  of the heater 213a and the heater 213b. Thereafter, the transmission/reception part 260g transmits the control values to the respective mass flow controllers and heaters via the I/O port 260d. The respective mass flow controllers are adjusted at the received control values so as to control the flow rates of gases. Moreover, the transmission/reception part 260g transmits the control values to the heater temperature control part 215 via the I/O port 260d; accordingly, the heater temperature control part 215 performs a control operation so that the wafer 200 has a desired temperature distribution.

10

The thickness of the film thus formed is proportional to the temperature. Therefore, in the case of distribution A, the temperature of the outer zone heater 213b is set higher than the temperature of the central zone heater 213a. This is effective in a case where the insulating film 2007 is formed 5 using a gas, e.g., a disilane gas, the temperature condition of which greatly contributes to the film formation efficiency.

If the supply amount (concentration) of the process gas and the temperature are parallel-controlled in this way, it is possible to accurately control the film thickness.

Subsequently, a case where the data stored in the RAM **260***b* have distribution B will be described. The case of distribution B refers to a case where the insulating film **2005***b* is thicker than the insulating film **2005***a* as illustrated in FIG. **7**.

In the case of distribution B, at this step, control is executed so that the insulating film 2007a formed on the central surface of the wafer 200 becomes thick and so that the thickness of the insulating film 2007b formed on the peripheral surface of the wafer 200 becomes smaller than the 20 thickness of the insulating film 2007a. Specifically, when supplying the gas, control is executed so that the siliconcontaining gas supplied to the central surface of the wafer 200 becomes larger in amount than the silicon-containing gas supplied to the peripheral surface of the wafer 200. By 25 doing so, the height of the insulating film in the semiconductor device, namely the thickness of the insulating film 2005 and the insulating film 2007 overlapped with each other, can be corrected like target film thickness distribution B' illustrated in FIG. 11. That is to say, the thickness of the 30 laminated insulating film can be corrected like film thickness distribution B'.

Specifically, a table illustrated in FIG. 26 is first read from the memory device 260*c*. The comparison part 260*f* compares the read data with the received film thickness distribution, thereby selecting the control values of the respective mass flow controllers. In this regard, a control value  $\beta$ 101 is selected with respect to the mass flow controller 241*b*. A control value  $\beta$  102 is selected with respect to the mass flow controller 242*b*. A control value  $\beta$ 103 is selected with 40 respect to the mass flow controller 251*b*. A control value  $\beta$ 104 is selected with respect to the mass flow controller 252*b*. Thereafter, the transmission/reception part 260*g* transmits the control values to the respective mass flow controllers via the I/O port 260*d*. The respective mass flow controllers are adjusted at the received control values so as to control the flow rates of gases.

In the first gas supply system, the mass flow controller **241***b* is controlled based on the received control value and the opening degree of the valve **241***c* is controlled so as to 50 control the amount of the silicon-containing gas supplied from the shower head **234** into the process chamber **201**. Furthermore, the mass flow controller **242***b* is controlled and the opening degree of the valve **242***c* is controlled so as to supply the silicon-containing gas from the gas supply path 55 **235** into the process chamber **201**. An exposure amount of the silicon-containing gas per unit area in the processing plane of the wafer **200** is controlled such that an exposure amount of the gas supplied from the shower head **234** becomes larger than an exposure amount of the gas supplied from the gas supplied 60 from the gas supply path **235**.

Furthermore, in the second gas supply system, the mass flow controller 251b is controlled based on the received control value and the opening degree of the valve 251c is controlled to control the amount of the oxygen-containing 65 gas supplied from the shower head 234. The amount of the oxygen-containing gas in the gas supply pipe 251a is set at

an amount corresponding to the amount of the siliconcontaining gas in the gas supply pipe 241a. Moreover, the mass flow controller 252b is controlled and the opening degree of the valve 252c is controlled to supply the oxygencontaining gas from the gas supply path 235. The amount of the oxygen-containing gas in the gas supply pipe 252a is set at an amount corresponding to the amount of the siliconcontaining gas in the gas supply pipe 242a.

At this time, an exposure amount of the silicon-containing gas per unit area in the processing plane of the wafer **200** is controlled such that an exposure amount of the gas supplied from the shower head **234** becomes larger than an exposure amount of the gas supplied from the gas supplied from the gas supplied from the gas supplied at **235**.

The silicon-containing gas and the oxygen-containing gas supplied through the shower head 234 are supplied onto the insulating film 2005a formed on the central surface of the wafer 200. The gases thus supplied form the insulating film 2007a on the insulating film 2005a as illustrated in FIGS. 10A and 10B.

The silicon-containing gas and the oxygen-containing gas supplied through the gas supply path **235** are supplied onto the insulating film **2005***b* formed on the peripheral surface of the wafer **200**. The gases thus supplied form the insulating film **2007***b* on the insulating film **2005***b* as illustrated in FIGS. **10**A and **10**B.

As described above, the exposure amount of the siliconcontaining gas per unit area in the processing plane of the wafer **200** is larger on the insulating film **2005***a* than on the insulating film **2005***b*. It is therefore possible to make the thickness of the insulating film **2007***a* larger than the thickness of the insulating film **2007***b*.