US009542878B2

# (12) United States Patent

# Qing et al.

#### (54) SHIFT REGISTER UNIT, DISPLAY PANEL AND DISPLAY APPARATUS

- (71) Applicants: BOE TECHNOLOGY GROUP CO., LTD., Beijing (CN); CHENGDU BOE OPTOELECTRONICS TECHNOLOGY CO., LTD., Chengdu (CN)

- (72) Inventors: Haigang Qing, Beijing (CN); Xiaojing Qi, Beijing (CN)

- (73) Assignees: BOE TECHNOLOGY GROUP CO., LTD., Beijing (CN); CHENGDU BOE OPTOELECTRONICS TECHNOLOGY CO., LTD., Chengdu (CN)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 14/771,129

- (22) PCT Filed: Mar. 6, 2015

- (86) PCT No.: PCT/CN2015/073765

§ 371 (c)(1),

(2) Date: Aug. 27, 2015

- (87) PCT Pub. No.: WO2016/065785PCT Pub. Date: May 6, 2016

#### (65) **Prior Publication Data**

US 2016/0351112 A1 Dec. 1, 2016

# (30) Foreign Application Priority Data

Oct. 29, 2014 (CN) ...... 2014 1 0594095

(51) Int. Cl.

| G11C 19/00 | (2006.01) |

|------------|-----------|

| G09G 3/20  | (2006.01) |

| G11C 19/28 | (2006.01) |

# (10) Patent No.: US 9,542,878 B2

# (45) **Date of Patent:** Jan. 10, 2017

- (58) Field of Classification Search CPC .... G09G 3/20; G09G 3/34; G09G 2300/0482; G09G 2300/0842; G09G 2300/0847; G09G 2300/0852; G09G 2300/0857; G09G 2300/0861; G09G 2300/0866; G09G 2310/08; G09G 3/3685; G09G 3/3688; G09G 3/3692; G09G 2310/0286; G09G 3/2096; G09G 2330/023; G09G 2330/028; G11C 19/28; G11C 19/00; H03K 23/54; H03K 5/15; H03K 23/00; G06F 5/01

See application file for complete search history.

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

| 2009/0146716 A1* | 6/2009 | Ide G11C 7/1072   |

|------------------|--------|-------------------|

|                  |        | 327/276           |

| 2014/0143292 A1* | 5/2014 | Yasuda G06F 7/588 |

|                  |        | 708/251           |

\* cited by examiner

Primary Examiner — Lun-Yi Lao

Assistant Examiner — Jarurat Suteerawongsa (74) Attorney, Agent, or Firm — Harness, Dickey & Pierce, P.L.C.

#### (57) ABSTRACT

A shift register unit includes a latch circuit and a transmission circuit. The latch circuit is configured to process a clock signal received by its first clock signal end and a low level signal by a NOR operation to obtain a signal and output the obtained signal when a selection signal is of a high level; during a first time period where the selection signal is of a low level, process a signal outputted by the latch circuit when the selection signal is of a high level by a NOT operation, then process the resultant signal with a feedback signal by a NOR operation to obtain a signal and output the obtained signal; output a low level signal during a time

(Continued)

2122LatchTransmissionCircuitCircuit

period where the selection signal is of a low level other than the first time period. The transmission circuit is configured to output a signal related to the clock signal received by its first clock signal end when the signal outputted by the latch circuit is of a high level; and output a corresponding signal when the signal outputted by the latch circuit is of a low level.

# 20 Claims, 19 Drawing Sheets

(52) U.S. Cl.

CPC ... G09G 2310/08 (2013.01); G09G 2330/023 (2013.01); G09G 2330/028 (2013.01)

-Prior Art-

FIG.12

FIG.20

FIG.23

FIG.25

FIG.27

FIG.28

FIG.29

FIG.31

**FIG.32**

5

20

## SHIFT REGISTER UNIT, DISPLAY PANEL AND DISPLAY APPARATUS

#### CROSS REFERENCE OF RELATED APPLICATIONS

This application is the U.S. national phase of PCT Application No. PCT/CN2015/073765 filed on Mar. 6, 2015, which claims a priority of the Chinese Patent Application No. 201410594095.4 filed on Oct. 29, 2014, the disclosures <sup>10</sup> of which are incorporated in their entirety by reference herein.

#### TECHNICAL FIELD

The present disclosure relates to a technical field of displaying, in particular to a shift register unit, a display panel and a display apparatus.

#### BACKGROUND

In a conventional Low Temperature Poly-Silicon (LTPS) shift register unit, D flip-flops consisted of inverters and transmission gates are adopted. In generally, the conventional LTPS shift register unit includes two D flip-flops. In 25 the LTPS shift unit, an output signal is latched by the D flip-flop, and shift and transmission of the signal are controlled by a clock signal.

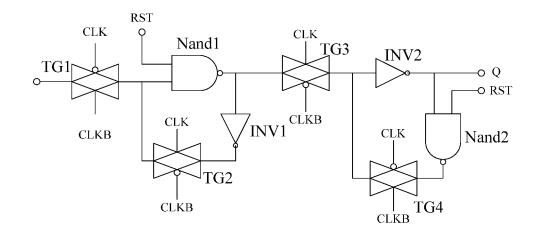

FIG. 1 illustrates a representative structure of the conventional LTPS shift register unit. As illustrated in FIG. 1, in 30 the LTPS shift register unit, a first D flip-flop is consisted of a transmission gate TG1, a NAND gate Nand1, an inverter INV1 and a transmission gate TG2, and a second D flip-flop is consisted of a transmission gate TG3, a NAND gate Nand2, an inverter INV2 and a transmission gate TG4. 35 When a clock signal CLK is of a low level and a reverse clock signal CLKB is of a high level so that the first D flip-flop is turned on, a signal outputted by a previous shift register unit enters into the first D flip-flop. At this time, the transmission gate TG3 at a front end of the second D 40 flip-flop is in an OFF state, and thus the signal outputted by the NAND gate Nand1 cannot enter into the second D flip-flop. On the other hand, when the clock signal CLK is of a high level and the reverse clock signal CLKB is of a low level so that the transmission gate TG1 in the first D flip-flop 45 is turned off, the state of the D flip-flop in a previous clock period is latched by the first D flip-flop. In other words, when the clock signal CLK is of a high level and the reverse clock signal CLKB is of a low level, the first D flip-flop latches the signal outputted by the first D flip-flop when the 50 clock signal CLK is of the low level and the reverse clock signal CLKB is of the high level. At this time, the transmission gate TG3 in the second D flip-flop is turned on, and the signal outputted by the first D flip-flop enters into the second D flip-flop which then outputs this signal. Thus, a 55 shift operation of the signal from a previous shift register unit to a next shift register unit is implemented. When the shift register unit operates, a reset signal RST is of a high level.

However, for the display apparatus, each shift register unit 60 is used only once during a time period for displaying one frame of image. For example, in the display apparatus, if there are N rows of pixels and the time period for displaying one frame of image is T seconds, then one shift register unit may be used for merely T/N seconds during the time period 65 for displaying one frame of the image. That is, during the time period for displaying one frame of image, each shift

register unit is kept in an operation state for merely T/N seconds, but in a non-operation state for T–T/N seconds. In other words, during the time period of one frame, an operation period of each shift register unit is only T/N seconds, and a non-operation period thereof is T–T/N seconds.

In the conventional shift register unit, turning on and off of all the transmission gates are controlled by the clock signal CLK and the reverse clock signal CLKB. Even during a non-operation period, the transmission gates are still turned on and off by the clock signal CLK and the reverse clock signal CLKB. Each of the transmission gates is consisted of parallel connected complementary transistors. When the transmission gates are controlled to be turned on and off by the clock signal CLK and the reverse clock signal CLKB, the clock signal CLK and the reverse clock signal CLKB is required to be inputted to gate electrodes of the transistors. In each of the transistors, the gate electrode covers a gate insulation layer, which covers a substrate. Thus, a capacitor is formed between the gate electrode and the substrate, which may be called a gate capacitor. In this manner, the gate capacitor of the transistor will be charged by the signal inputted to the gate electrode of the transistor when the signal is of a high level, and will be discharged by the signal when the signal is of a low level. As a result, during the non-operation period, such charging and discharging of the circuit may cause meaningless power consumption. A contemporary display apparatus often includes hundreds or thousands stages of shift register units, and only one stage of the shit register unit circuit is operating at a same time, meanwhile the other shift register units are in the non-operation state. At this time, both the clock signal CLK and the reverse clock signal CLKB will be inputted to the transmission gates of the transfer register units which are in the non-operation state, which may cause meaningless but large power consumption.

It can be seen from above that, due to the fact that the transmission gates in the conventional shift register units are controlled to switch between being-turned-on and being-turned-off by the two complementary and reversed clock signals during the non-operation period, the gate capacitors of the transistors in the transmission gates are charged and discharged during the non-operation period, which causes meaningless but large power consumption.

#### SUMMARY

#### (1) Technical Problems to be Solved

In embodiments of the present disclosure, it is provided a shift register unit, a display panel and a display apparatus to solve the following problem: in the conventional shift register unit, it is required two complementary and reverse clock signals to control the switching of the transmission gate between turning-on and turning-off, so that the gate capacitor of the transistor in the transmission gate is charged and discharged during the non-operation period of the shift register unit, which causes meaningless but large power consumption.

#### (2) Technical Solutions

For solving the above problem, in one aspect of the present disclosure, it is provided a shift register unit including a latch circuit and a transmission circuit; the latch circuit is configured to process a clock signal received by a first clock signal end of the shift register unit and a low level

signal by a NOR operation to obtain a signal and output the obtained signal when a selection signal is of a high level, wherein the clock signal received by the first clock signal end is of a low level when the selection signal is of a high level; during a first time period where the selection signal is 5 of a low level, process the signal outputted by the latch circuit when the selection signal is of a high level by NOT operation to obtain a signal, then process the resultant signal with a feedback signal by a NOR operation to obtain a signal, and output the obtained signal; output a low level signal during a time period where the selection signal is of a low level other than the first time period where the selection signal is of a first low level; and the transmission circuit is configured to output a signal related to the clock 15 signal received by the first clock signal end when the signal outputted by the latch circuit is of a high level; and output a corresponding signal when the signal outputted by the latch circuit is of a low level;

wherein, the feedback signal is able to make the signal 20 outputted by the latch circuit during the time period where the selection signal is of a high level and the signal outputted by the latch circuit during the first time period where the selection signal is of a low level be the same; the feedback signal is converted from being of a low level to being of a <sup>25</sup> high level, at an end time point of the first time period where the selection signal is of a low level; and the first time period where the selection signal is of a low level is a time period from a time point when the selection signal is converted from being of a low level to being of a high level to a time point when a signal outputted by a next stage shift register unit with respect to the shift register unit jumps from being of a low level to being of a high level.

In another aspect of the present disclosure, it is provided <sup>35</sup> a display panel including a plurality of stages of the shift register units according to the embodiment of the present disclosure.

In another aspect of the present disclosure, it is provided a display apparatus including the display panel according to  $_{40}$  the embodiment of the present disclosure.

#### (3) Advantageous Effects

The embodiments of the present disclosure at least imple- 45 ments the following advantageous effects: in the shift register unit, the display panel and the display apparatus according to the embodiment of the present disclosure, the latch circuit in the shift register unit is capable of processing the clock signal received by the first clock signal end and a low 50level signal by a NOR operation to obtain a signal of a high level and outputting the obtained signal when the selection signal is of a high level, and capable of maintaining a state of the latch circuit when the selection signal is of a high level during the first time period where the selection signal is of a low level. That is, the latch circuit may latch the state when the selection signal is of a high level, the state of the latch circuit may be changed by the feedback signal, and the signal outputted by the output circuit may be controlled by 60 the signal outputted by the latch circuit. As a result, a shift registering function is implemented. In other words, in this embodiment of the present disclosure, the shift register unit is controlled by the selection signal to implement the shift registering function, so that it is avoided that the transmis- 65 sion gate in the shift register unit is controlled by the two complementary and reversed clock signals to implement the

4

shift registering function. Thus, the meaningless power consumption of the shift register unit during a non-operation time period is reduced.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In order to illustrate the technical solutions of the present disclosure or the related art in a clearer manner, the drawings desired for the embodiments will be described briefly hereinafter. Obviously, the following drawings merely relate to some embodiments of the present disclosure, and based on these drawings, a person skilled in the art may obtain the other drawings without any creative effort.

FIG. **1** is a schematic diagram for a structure of a conventional shift register unit;

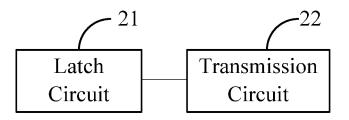

FIG. **2** is a block diagram for a structure of a shift register unit according to an embodiment of the present disclosure;

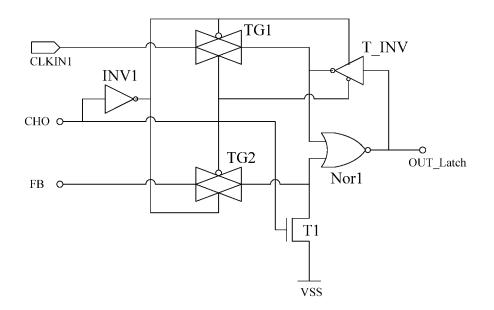

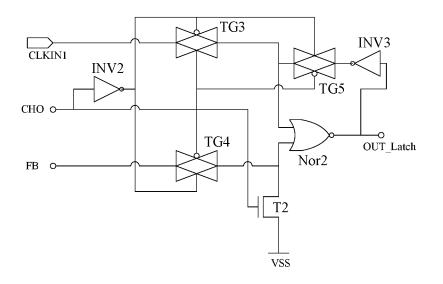

FIG. **3** is a first schematic diagram for a structure of a latch circuit in the shift register unit according to an embodiment of the present disclosure;

FIG. **4** is a second schematic diagram for the structure of the latch circuit in the shift register unit according to an embodiment of the present disclosure;

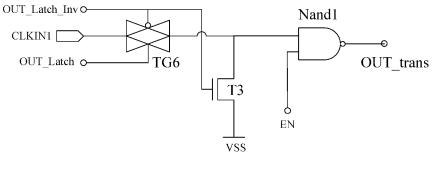

FIG. **5** is a first schematic diagram for a structure of a transmission circuit in the shift register unit according to an embodiment of the present disclosure;

FIG. **6** is a second schematic diagram for the structure of the transmission circuit in the shift register unit according to an embodiment of the present disclosure;

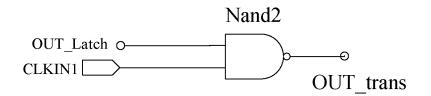

FIG. **7** is a schematic diagram for a structure of a buffer circuit in the shift register unit according to an embodiment of the present disclosure;

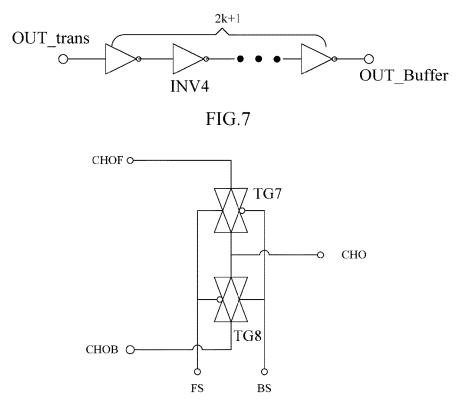

FIG. **8** is a schematic diagram for a structure of a scanning direction selecting circuit in the shift register unit according to an embodiment of the present disclosure;

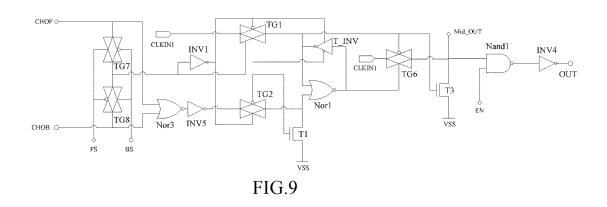

FIG. 9 is a first schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

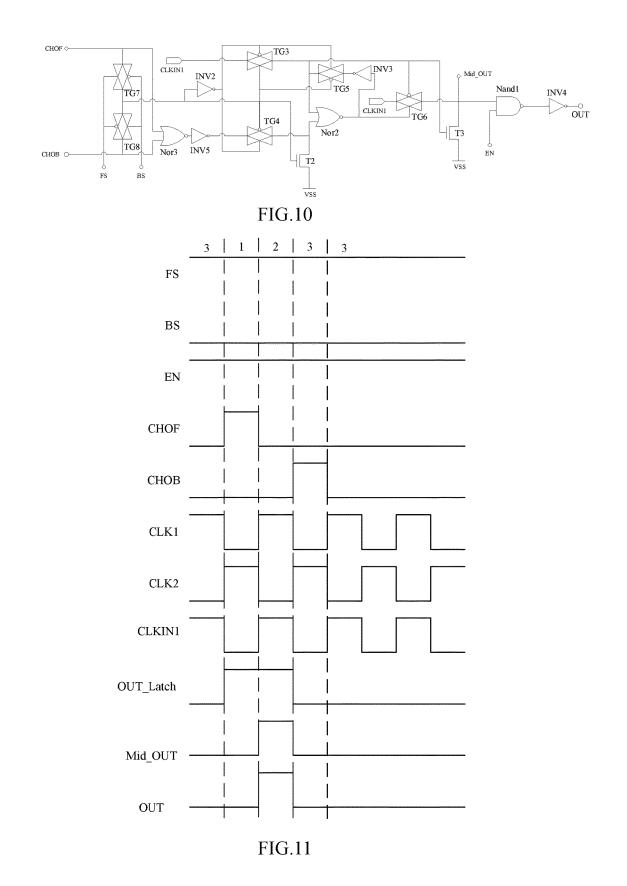

FIG. **10** is a second schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

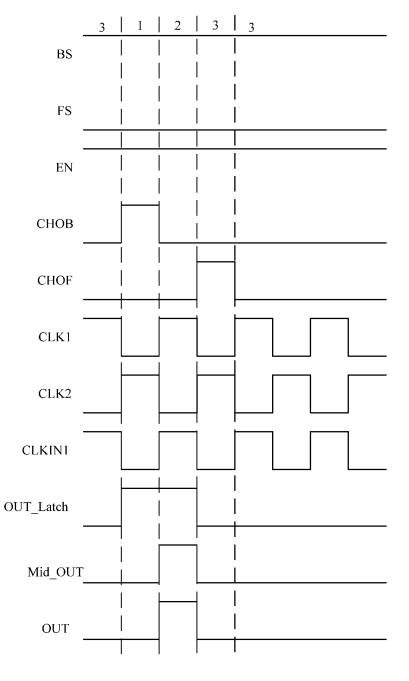

FIG. **11** illustrates a workflow diagram for a forward scanning by the shift register unit as illustrated in FIG. **9** or **10**;

FIG. **12** illustrates a workflow diagram for a backward scanning by the shift register unit as illustrated in FIG. **9** or **10**;

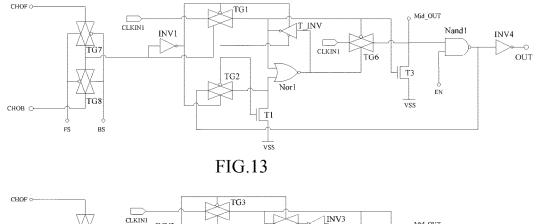

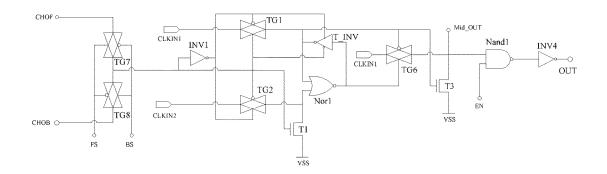

FIG. **13** is a third schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

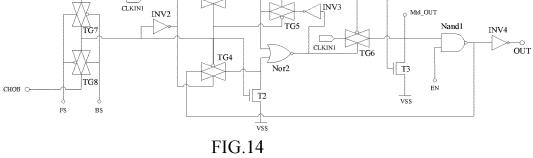

FIG. **14** is a fourth schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

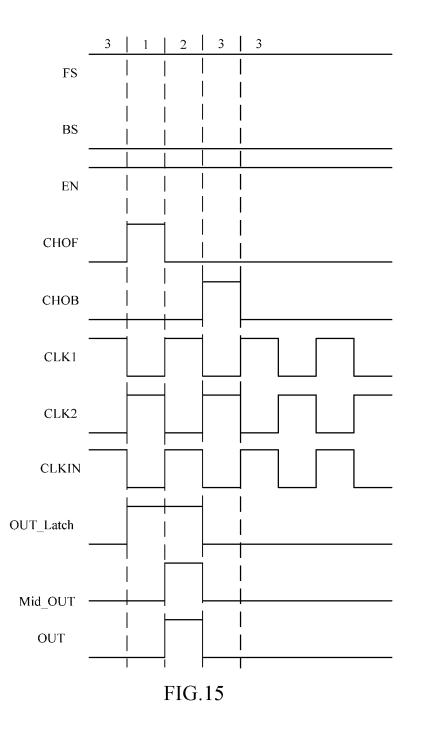

FIG. **15** illustrates a workflow diagram for a forward scanning by the shift register unit as illustrated in FIG. **13** or **14**;

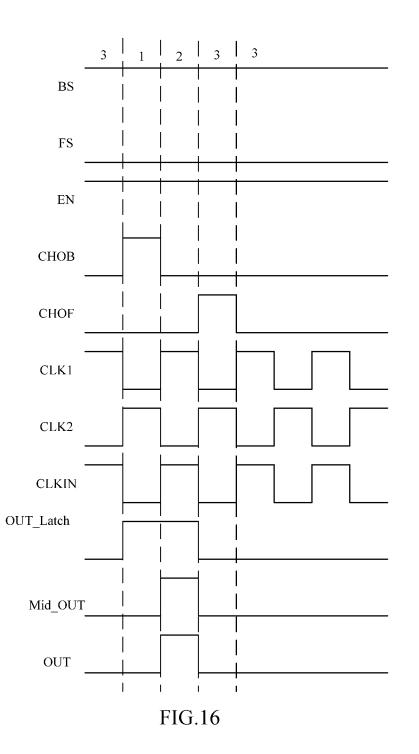

FIG. **16** illustrates a workflow diagram for a backward scanning by the shift register unit as illustrated in FIG. **13** or **14**;

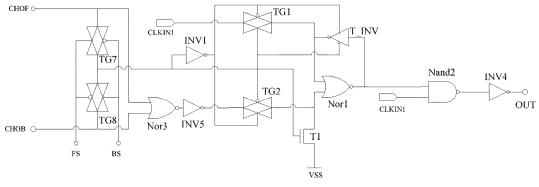

FIG. **17** is a fifth schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

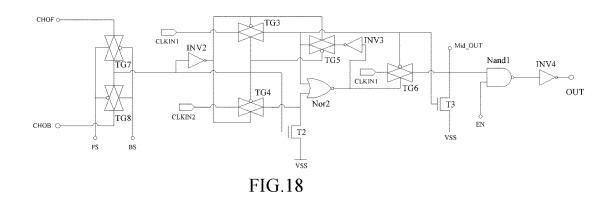

FIG. **18** is a sixth schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

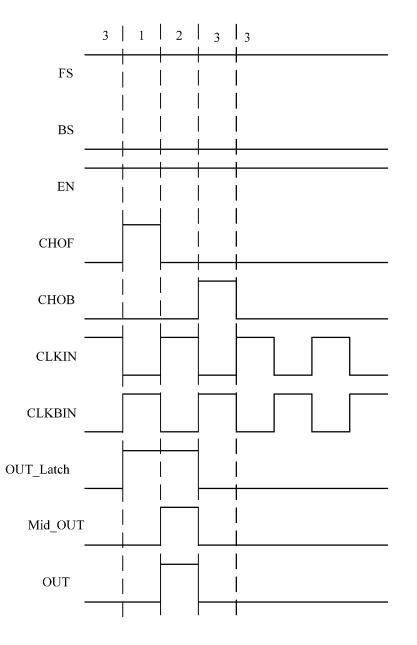

FIG. **19** illustrates a workflow diagram for a forward scanning by the shift register unit as illustrated in FIG. **17** or **18**;

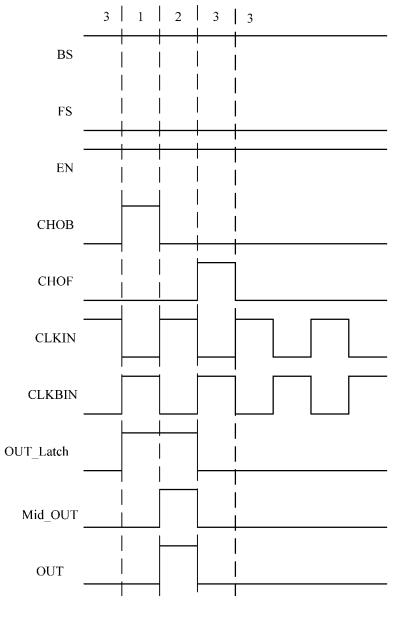

FIG. 20 illustrates a workflow diagram for a backward scanning by the shift register unit as illustrated in FIG. 17 or 5 18;

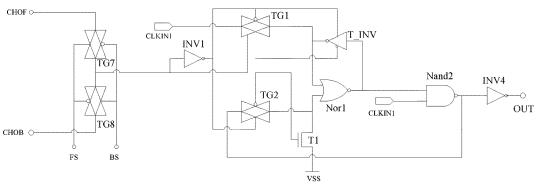

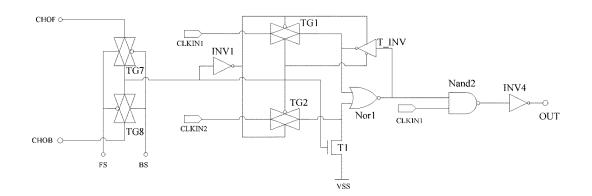

FIG. **21** is a seventh schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

FIG. **22** is an eighth schematic diagram for the structure <sup>10</sup> of the shift register unit according to an embodiment of the present disclosure;

FIG. **23** is a ninth schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

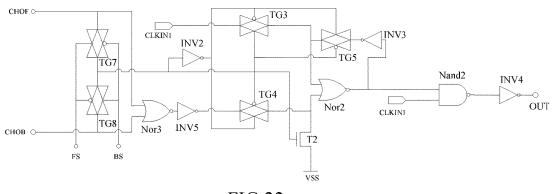

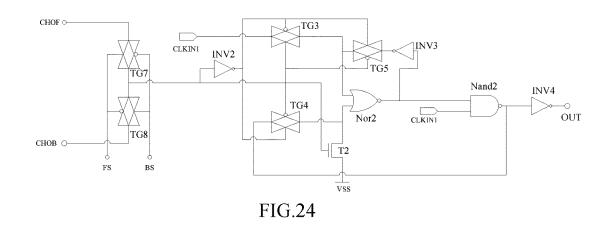

FIG. **24** is a tenth schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

FIG. **25** is a eleventh schematic diagram for the structure of the shift register unit according to an embodiment of the <sup>20</sup> present disclosure;

FIG. **26** is a twelfth schematic diagram for the structure of the shift register unit according to an embodiment of the present disclosure;

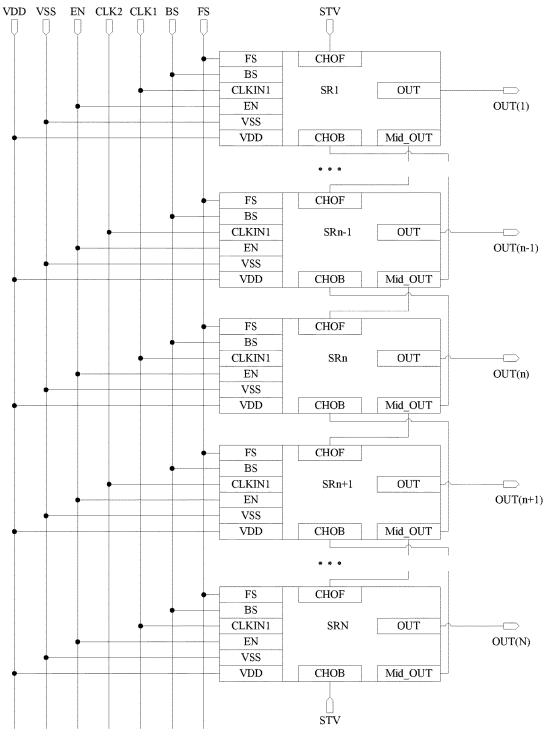

FIG. **27** is a first schematic diagram for a cascading <sup>25</sup> connection of the shift register units as illustrated in any one of FIGS. **9**, **10**, **13** and **14**:

FIG. **28** is a second schematic diagram for a cascading connection of the shift register units as illustrated in any one of FIGS. **9**, **10**, **13** and **14**;

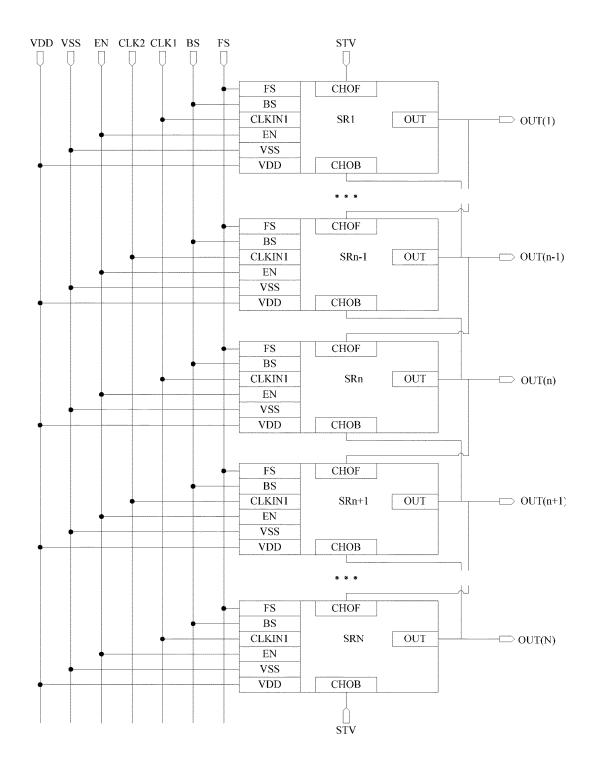

FIG. **29** is a first schematic diagram for s cascading connection of the shift register units as illustrated in FIG. **17** or **18**;

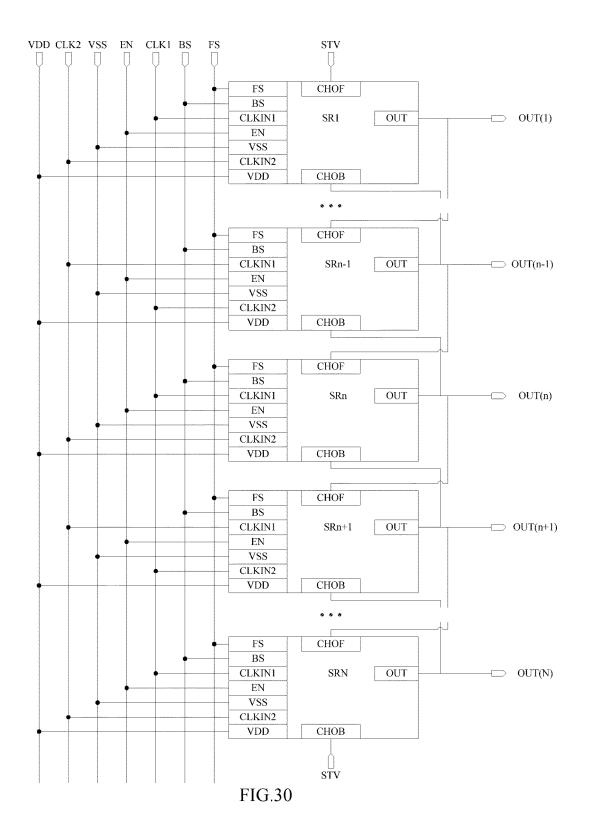

FIG. **30** is a second schematic diagram for a cascading connection of the shift register units as illustrated in FIG. **17** <sup>35</sup> or **18**;

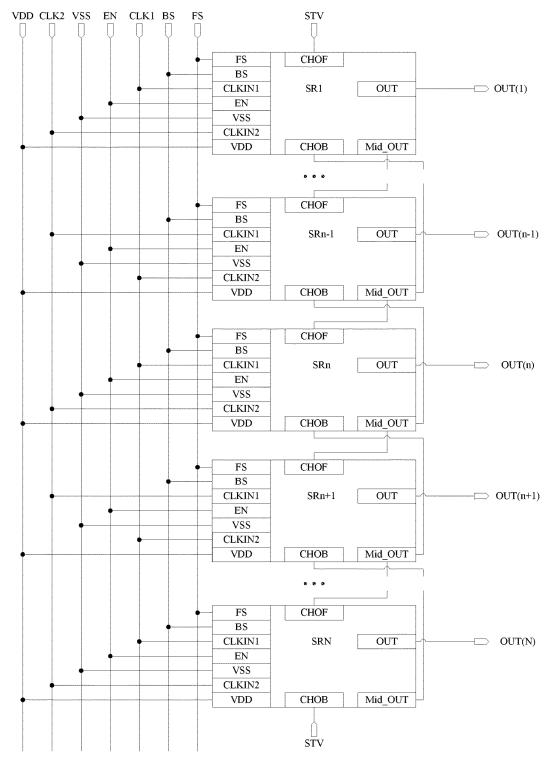

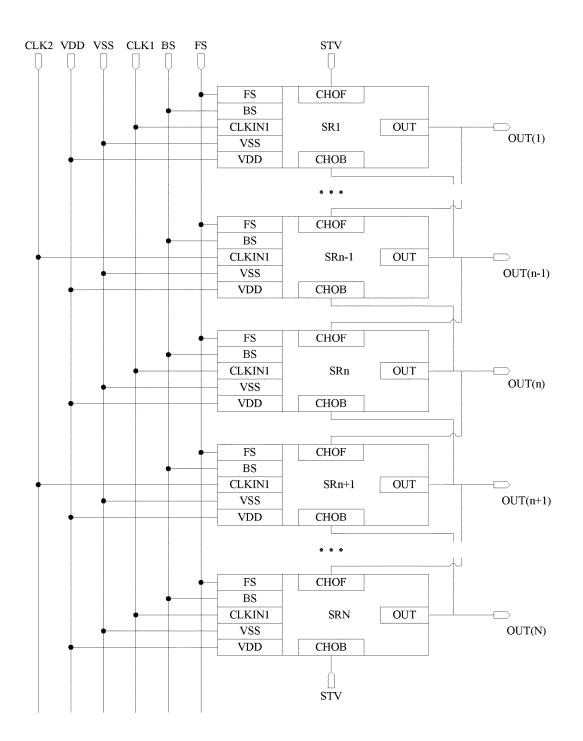

FIG. **31** is a schematic diagram for a cascading connection of the shift register units as illustrated in any one of FIGS. **21**, **22**, **23** and **24**; and

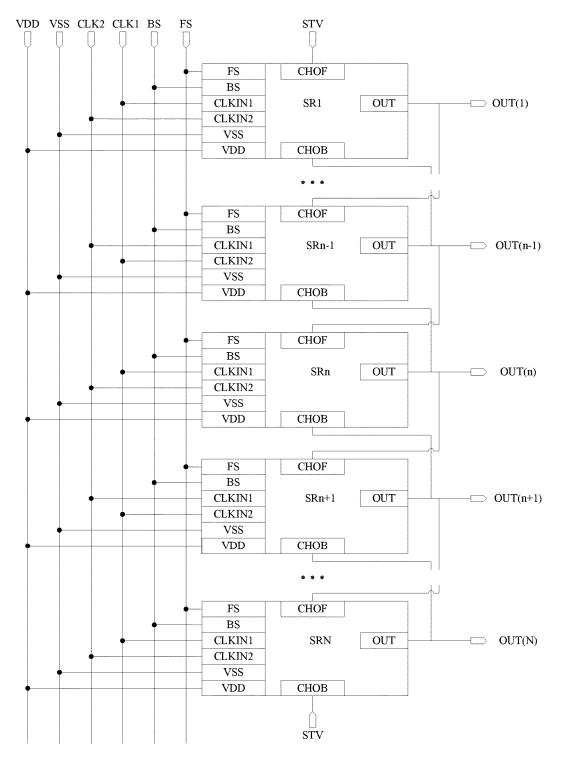

FIG. **32** is a schematic diagram for a cascading connection <sup>40</sup> of the shift register units as illustrated in FIG. **25** or **26**.

## DETAILED DESCRIPTION

The present disclosure will be described hereinafter in 45 conjunction with the drawings and embodiments. The following embodiments are for illustrative purposes only, but shall not be used to limit the scope of the present disclosure.

In order to make the objects, the technical solutions and the advantages of the present disclosure more apparent, <sup>50</sup> some technical solutions of the present disclosure will be described hereinafter in a clear and complete manner in conjunction with the drawings and embodiments. Obviously, the following embodiments are merely a part of, rather than all of, the embodiments of the present disclosure, <sup>55</sup> and based on these embodiments, a person skilled in the art may obtain the other embodiments, which also fall within the scope of the present disclosure.

Unless otherwise defined, any technical or scientific term used herein shall have the common meaning understood by 60 a person of ordinary skills. Such words as "first" and "second" used in the specification and claims are merely used to differentiate different components rather than to represent any order, number or importance. Similarly, such words as "one" or "a/an" are merely used to represent the 65 existence of at least one member, rather than to limit the number thereof. Such words as "connect" or "connected to" 6

may include electrical connection, direct or indirect, rather than to be limited to physical or mechanical connection. Such words as "on", "under", "left" and "right" are merely used to represent relative position relationship, and when an absolute position of the object is changed, the relative position relationship will be changed too.

In the shift register unit, the display panel and the display apparatus according to the embodiment of the present disclosure, the latch circuit in the shift register unit may latch the state of the circuit when a latch selection signal is of a high level, the state of the latch circuit is changed by the feedback signal, and the signal outputted by the transmission circuit is controlled by the signal outputted by the latch circuit. As a result, a shift registering function is implemented. In this manner, it is avoided that the transmission gate in the shift register unit is controlled by the two complementary and reversed clock signals to implement the shift registering function, and thus the meaningless power consumption of the shift register unit during the nonoperation time period is reduced.

In the following, embodiments of the shift register unit, the display panel and the display apparatus will be explained with figures.

General Circuit Structure

In the embodiment of the present disclosure, as illustrated in FIG. 2, the shift register unit includes a latch circuit 21 and a transmission circuit 22.

The latch circuit **21** processes a clock signal received by a first clock signal end of a shift register unit and a low level signal by a NOR operation to obtain a signal and output the obtained signal when a selection signal is of a high level. The clock signal received by the first clock signal end is of a low level when the selection signal is of a high level. Then, during a first time period where the selection signal is of a low level, the latch circuit **21** processes the signal outputted by the latch circuit **21** when the selection signal is of a high level by a NOT operation, then process the resultant signal with a feedback signal by a NOR operation to obtain a signal and output the obtained signal. Furthermore, the latch circuit **21** outputs a low level signal during a time period where the selection signal is of a low level other than the first time period where the selection signal is of a low level.

The transmission circuit 22 outputs a signal related to the clock signal received by the first clock signal end when the signal outputted by the latch circuit 21 is of a high level; and outputs a corresponding signal when the signal outputted by the latch circuit 21 is of a low level.

In particular, the feedback signal is able to make the signal outputted by the latch circuit during the time period where the selection signal is of a high level and the signal outputted by the latch circuit during the first time period where the selection signal is of a low level be the same; the feedback signal is converted from being of a low level to being of a high level, at an end time point of the first time period where the selection signal is of a low level; and the first time period where the selection signal is of a low level is a time period from a time point when the selection signal is converted from being of a low level to being of a high level to a time point when a signal outputted by a next stage shift register unit with respect to the shift register unit jumps from being of a low level to being of a high level.

Upon a forward scanning, a selection signal received by a k-th stage shift register unit may be the signal outputted by a (k-1)-th stage shift register unit. At this time, a next stage shift register unit to the k-th shift register unit is a (k+1)-th stage shift register unit. In contrast, upon a backward scanning, the selection signal received by the k-th stage shift

register unit may be a signal outputted by the (k+1)-th stage shift register unit. At this time, a next stage shift register unit to the k-th shift register unit is the (k-1)-th stage shift register unit. During a time period where the selection signal is of a high level and a first time period where the selection 5 signal is of a low level, the k-th stage shift register unit is in an operation state.

During the time period where the selection signal is of a high level, since the selection signal is of a high level and the signal received by the first clock signal end of the shift register unit is of a low level, the signal outputted by the latch circuit 21 is of a high level. Furthermore, during the first time period where the selection signal is of a low level, since the selection signal is of a low level and the signal received by the first clock signal end of the shift register unit 15 is of a high level, the signal outputted by the latch circuit 21 is still of a high level. That is, during the first time period where the selection signal is of a low level, the latch circuit 21 may latch its state when the selection signal is of a high level. Moreover, during the first time period where the 20 selection signal is of a low level, the latch circuit 21 processes a signal outputted by the latch circuit 21 when the selection signal is of a high level by a NOT operation, then process the resultant signal with a feedback signal by a NOR operation to obtain a signal, and output the obtained signal. 25 Thus, once the feedback signal is of a high level, the signal outputted by the latch circuit 21 is of a low level. That is, when the selection signal is of a low level, the signal outputted by the latch circuit may be changed by the feedback signal, and thus the shift register unit may be 30 changed from being in an operation state to be in a nonoperation state. At an end time point of the first time period where the selection signal is of a low level, the feedback signal is changed from being of a low level to being of a high level. Thus, at the end time point of the first time period 35 where the selection signal is of a low level, the signal outputted by the latch circuit is changed to be of a low level. That is, at the end time point of the first time period where the selection signal is of a low level, the shift register unit is changed from being in an operation state to be in a 40 non-operation state.

When the signal outputted by the latch circuit **21** is of a high level, the transmission circuit **22** outputs a signal related to the clock signal received by the first clock signal end of the shift register unit. In particular, the transmission 45 circuit **22** may outputs a signal, either identical to, or reverse to, the clock signal received by the first clock signal end of the shift register unit. As a result, the shift register unit implements the shift registering function. When the signal outputted by the latching circuit **21** is of a low level, the 50 transmission circuit **22** may output a corresponding signal. In particular, the output circuit **22** may output a high level signal or a low level signal, so that the shift register unit may enter the non-operation state.

That is, in this embodiment of the present disclosure, the 55 shift register unit is configured to control, through the selection signal, the latch circuit to latch, during the first time period where the selection signal is of a low level, its state when the selection signal is of a high level, and control the transmission circuit based on the state of the latch circuit, 60 so that the shift registering function may be implemented by the shift register unit. Furthermore, the state of the latch circuit may be changed based on the change of a level of the feedback signal when the selection signal is of a low level, so that the shift register unit may enter its non-operation 65 state. In this manner, it is unnecessary to adopt two complementary signals to control the transmission gate so that the

shift register unit implements the shift registering function and enters its non-operation state. As a result, the meaningless power consumption of the shift register unit during the non-operation time period is reduced.

#### First and Second Embodiments Regarding Latch Circuit

Alternatively, as illustrated in FIG. **3**, the latch circuit 10 includes a first inverter INV**1**, a ternary inverter T\_INV, a first transmission gate TG**1**, a second transmission gate TG**2**, a first NOR gate Nor**1** and a first transistor T**1**.

The first inverter INV1 receives the selection signal CHO, processes a selection signal CHO by a NOT operation to obtain a signal and outputs the obtained signal. If the selection signal CHO is of a high level, a signal outputted by the first inverter INV1 is of a low level. In contrast, if the selection signal CHO is of a low level, the signal outputted by the first inverter INV1 is of a low level, the signal outputted by the first inverter INV1 is of a high level.

A control end of the first transmission gate TG1 which is effective when inputted with a low level receives the signal outputted by the first inverter INV1, another control end of the first transmission gate TG1 which is effective when inputted with a high level receives the selection signal CHO, an input end of the first transmission gate TG1 is the first clock signal end CLKIN1 of the shift register unit, and the first transmission gate TG1 outputs the clock signal received by the input end of the first transmission gate TG1 when the first transmission gate TG1 is turned on. When the selection signal CHO is of a high level, the first transmission gate TG1 is turned on. In contrast, when the selection signal CHO is of a low level, the first transmission gate TG1 is turned off.

A control end of the second transmission gate TG2 which is effective when inputted with a low level receives the selection signal CHO, another control end of the second transmission gate TG2 which is effective when inputted with a high level receives the signal outputted by the first inverter INV1, and the second transmission gate TG2 receives a feedback signal FB, and outputs the feedback signal TB when the second transmission gate TG2 is turned on. When the selection signal CHO is of a low level, the second transmission gate TG2 is turned on. In contrast, when the selection signal CHO is of a high level, the second transmission gate TG2 is turned off.

An input end of the first NOR gate Nor1 is connected to an output end of the first transmission gate TG1 and an output end of the ternary inverter T INV respectively. another input end of the first NOR gate Nor1 is connected to an output end of the second transmission gate TG2 and a first electrode of the first transistor T1, and a signal outputted by the first NOR gate Nor1 is a signal OUT\_Latch outputted by the latch circuit. The first electrode of the first transistor T1 is a source electrode (SOURCE) or a drain electrode (DRAIN) of the first transistor T1. When the first electrode of the first transistor T1 is the source electrode, the second electrode of the first transistor T1 is the drain electrode. When the first electrode of the first transistor T1 is the drain electrode, the second electrode of the first transistor T1 is the source electrode. A person skilled in the art may understand that the present disclosure is not limited thereto.

A control end of the ternary inverter  $T_INV$  which is effective when inputted with a low level receives the selection signal CHO, another control end of the ternary inverter  $T_INV$  which is effective when inputted with a high level receives the signal outputted by the first inverter INV1, and the ternary inverter  $T_INV$  receives the signal outputted by the first NOR gate Nor1, and processes the signal outputted by the first NOR gate Nor1 by a NOT operation to obtain a signal and outputs the obtained signal when the selection signal CHO is of a low level and the signal outputted by the first inverter INV1 is of a high level. As illustrated in FIG. **3**, when the selection signal CHO is of a high level, the 5 ternary inverter T\_INV is in a high impedance state. In contrast, when the selection signal CHO is of a low level, the ternary inverter T\_INV is turned on, and then processes the received signal by a NOT operation to obtain a signal and outputs the obtained signal.

As illustrated in FIG. **3**, a gate electrode of the first transistor T1 receives the selection signal CHO, and the drain electrode of the first transistor T1 receives a low level signal VSS. A person skilled in the art may understand that, alternatively, the drain electrode of the first transistor T1 may receive the selection signal CHO, and the source electrode of the first transistor T1 may receive a low level signal Vss; the present disclosure is not limited thereto.

During a time period where the selection signal CHO is of a high level, the selection signal CHO is of a high level, the 20 signal received by the first clock signal end CLKIN1 of the shift register unit is of a low level, the feedback signal FB is of a high level, and the signal outputted by the first inverter INV1 is of a low level. Thus, the first transmission gate TG1 is turned on; the second transmission gate TG2 is 25 turned off, the first transistor T1 is turned on, and the ternary inverter T\_INV is in the high impedance state. Thus, both signals received by the first NOR gate Nor1 are each of a low level, and the signal outputted by the first NOR gate Nor1 is of a high level. 30

During a first time period where the selection signal CHO is of a low level, the selection signal CHO is of a low level, the signal received by the first clock signal end CLKIN1 of the shift register unit is of a high level, the feedback signal FB is of a low level, and the signal outputted by the first 35 inverter INV1 is of a high level. Thus, the first transmission gate TG1 is turned off, the second transmission gate TG2 is turned on, the first transistor T1 is turned off, the ternary inverter T\_INV is turned on, and the ternary inverter T\_INV processes the signal outputted by the first NOR gate Nor1 40 when the selection signal CHO is of a high level, i.e. a high level signal, by a NOT operation to obtain a signal, and outputs the obtained signal to an input end of the first NOR gate Nor1. Since the first transistor T1 is turned off and the second transmission gate TG2 is turned on, another input 45 end of the first NOR gate Nor1 receives the feedback signal FB of a low level. Therefore, during the first time period where the selection signal is of a low level, the first NOR gate Nor1 still outputs the high level signal.

During the time period where the selection signal CHO is 50 of a high level and the first time period where the selection signal CHO is of a low level, the signal outputted by the latch circuit is of a high level, the signal outputted by the transmission circuit is related to the clock signal received by the first clock signal end of the shift register unit, and the 55 shift register unit is in its operation state.

During a time period from an end of the first time period where the selection signal CHO is of a first low level to a start of the selection signal CHO being turned to be of a high level again, the selection signal CHO is kept to be of a low 60 level. Thus, the first transmission gate TG1 is turned off, the second transmission gate TG2 is turned on, the first transistor T1 is turned off, and the ternary inverter T\_INV is turned on. Once the feedback signal FB is turned to be of a high level, the first NOR gate Nor1 receives a high level signal 65 and then outputs a low level signal. Thus, the ternary inverter T\_INV outputs a high level signal. As a result, the

latch circuit keeps being in a state of outputting a low level signal, and the signal outputted by the latch circuit will not change until the selection signal CHO is turned to be of a high level again.

That is, during the time period from the end of the first time period where the selection signal CHO is of a first low level to the start of the selection signal CHO being turned to be of a high level again, once the feedback signal FB is turned to be of a high level, the latch circuit is changed from being in a state of outputting a high level signal to being in a state of outputting a low level signal; and when the latch circuit outputs a low level signal, the transmission circuit outputs a corresponding signal and the shift register unit is in its non-operation state. Furthermore, since the feedback signal FB is changed from being of a low level to being of a high level at the end of the first time period where the selection signal CHO is of a first low level, the shift register unit enters the operation state from the non-operation state at the end of the first time period where the selection signal CHO is of a first low level.

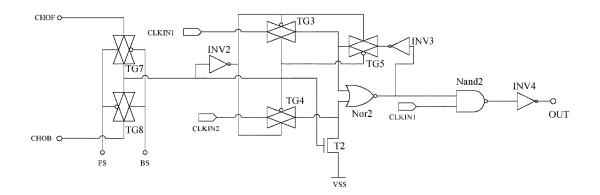

Alternatively, as an alternation of the embodiment as illustrated in FIG. **3**, as illustrated in FIG. **4**, the latch circuit includes a second inverter INV**2**, a third inverter INV**3**, a third transmission gate TG**3**, a fourth transmission gate TG**4**, a fifth transmission gate TG**5**, a second NOR gate Nor**2** and a second transistor T**2**.

The second inverter INV2 receives the selection signal CHO, and processes the selection signal CHO by a NOT operation to obtain a signal and output the obtained signal. If the selection signal CHO is of a high level, the signal outputted by the second inverter INV2 is of a low level. In contrast, if the selection signal CHO is of a low level, the signal outputted by the second inverter INV2 is of a high level, the signal outputted by the second inverter INV2 is of a high level.

A control end of the third transmission gate TG3 is which is effective when inputted with a low level receives a signal outputted by the second inverter INV2, another control end of the third transmission gate TG3 is which is effective when inputted with a high level receives the selection signal CHO, an input end of the third transmission gate TG3 is connected to the first clock signal end CLKIN1 of the shift register unit, and the third transmission gate TG3 outputs the clock signal received by the input end of the third transmission gate TG3 when the third transmission gate TG3 is turned on. When the selection signal CHO is of a high level, the third transmission gate TG3 is turned on. In contrast, when the selection signal CHO is of a low level, the third transmission gate TG3 is turned off.

A control end of the fourth transmission gate TG4 which is effective when inputted with a low level receives the selection signal CHO, another control end of the fourth transmission gate TG4 which is effective when inputted with a high level receives the signal outputted by the second inverter INV2, and the fourth transmission gate TG4 receives the feedback signal FB, and outputs the feedback signal FB when the fourth transmission gate TG4 is turned on. When the selection signal CHO is of a low level, the fourth transmission gate TG4 is turned on. In contrast, when the selection signal CHO is of a high level, the fourth transmission gate TG4 is turned off.

An input end of the second NOR gate Nor2 is connected to an output end of the third transmission gate TG3 and an output end of the fifth transmission gate TG5 respectively, another input end of the second NOR gate Nor2 is connected to an output end of the fourth transmission gate TG4 and a first electrode of the second transistor T2, and a signal outputted by the second NOR gate Nor2 is the signal

OUT\_Latch outputted by the latch circuit. The first electrode of the second transistor T2 is a source electrode or a drain electrode of the second transistor T2. When the first electrode of the second transistor T2 is the source electrode, the second electrode of the second transistor T2 is the drain 5 electrode. When the first electrode of the second transistor T2 is the drain electrode, the second electrode of the second transistor T2 is the source electrode. A person skilled in the art may understand that the present disclosure is not limited thereto. 10

The third inverter INV3 receives the signal outputted by the second NOR gate Nor2, and processes the signal outputted by the second NOR gate Nor2 by a NOT operation to obtain a signal and output the obtained signal. When the second NOR gate Nor2 outputs a high level signal, the third 15 inverter INV3 outputs a low level signal. In contrast, when the second NOR gate Nor2 outputs a low level signal, the third inverter INV3 outputs a high level signal.

A control end of the fifth transmission gate TG5 which is effective when inputted with a low level receives the selection signal CHO, another control end of the fifth transmission gate TG5 which is effective when inputted with a high level receives the signal outputted by the second inverter INV2, and the fifth transmission gate TG5 receives the signal outputted by the third inverter INV3, and outputs the 25 signal outputted by the third inverter INV3 when the selection signal CHO is of a low level. When the selection signal CHO is of a low level, the fifth transmission gate TG5 is turned on. In contrast, when the selection signal CHO is of a high level, the fifth transmission gate TG5 is turned off. 30

As illustrated in FIG. **4**, a gate electrode of the second transistor **T2** receives the selection signal CHO, and the drain electrode of the second transistor **T2** receives a low level signal VSS. A person skilled in the art may understand that, alternatively, the drain electrode of the second transistor **T2** may receive the selection signal CHO, and the source electrode of the second transistor **T2** may receive a low level signal Vss; the present disclosure is not limited thereto. being in the state of output in a state of output is a low level output a corresponding s in its non-operation state. Third and Fourth signal Vss; the present disclosure is not limited thereto.

During a time period where the selection signal CHO is of a high level, the selection signal CHO is of a high level, the 40 clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a low level, the feedback signal FB is of a high level, and the signal outputted by the second inverter INV2 is of a low level. As a result, the third transmission gate TG3 is turned on, the fourth transmission 45 gate TG4 is turned off, the fifth transmission gate TG5 is turned off, and the second transistor T2 is turned on. Thus, both signals received by the second NOR gate Nor2 are each of a low level, and the signal outputted by the second NOR gate Nor2 is of a high level. 50

During a first time period where the selection signal CHO is of a low level, the selection signal CHO is of a low level, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a high level, the feedback signal FB is of a low level, and the signal outputted 55 by the second inverter INV2 is of a high level. As a result, the third transmission gate TG3 is turned off, the fourth transmission gate TG4 is turned on, the fifth transmission gate TG5 is turned on, and the second transistor T2 is turned off. The third inverter INV3 processes the signal outputted 60 by the second NOR gate Nor2 when the selection signal CHO is of a high level, i.e. a high level signal, by a NOT operation to obtain a signal, and outputs the obtained signal to an input end of the second NOR gate Nor2 via the fifth transmission gate TG5. Since the second transistor T2 is 65 turned off, and the fourth transmission gate TG4 is turned on, another input end of the second NOR gate Nor2 receives

the feedback signal FB of a low level. Thus, during the first time period where the selection signal is of a low level, the second NOR gate Nor2 still outputs a high level signal.

During the time period where the selection signal CHO is of a high level and the first time period where the selection signal CHO is of a low level, the signal outputted by the latch circuit is of a high level, the signal outputted by the transmission circuit is related to the clock signal received by the first clock signal end of the shift register unit, and the shift register unit is in its operation state.

During a time period from an end of the first time period where the selection signal CHO is of a first low level to a start of the selection signal CHO being turned to be of a high level again, the selection signal CHO is kept to be of a low level. Thus, the third transmission gate TG3 is turned off, the fourth transmission gate TG4 is turned on, the fifth transmission gate TG5 is turned on, and the second transistor T2 is turned off. Once the feedback signal FB is turned to be of a high level, the second NOR gate Nor2 receives a high level signal and outputs a low level signal, thus the third inverter INV3 outputs a high level signal. As a result, the latch circuit keeps being in a state of outputting a low level signal, and the signal outputted by the latch circuit will not change until the selection signal CHO is turned to be of a high level again.

That is, during the time period from the end of the first time period where the selection signal CHO is of a first low level to the start of the selection signal CHO being turned to be of a high level again, once the feedback signal FB is turned to be of a high level, the latch circuit is changed from being in the state of outputting a high level signal to being in a state of outputting a low level signal; and when the latch circuit outputs a low level signal, the transmission circuit outputs a corresponding signal, and the shift register unit is in its non-operation state.

#### Third and Fourth Embodiments Regarding Transmission Circuit

Alternatively, as illustrated in FIG. 5, the transmission gate includes a sixth transmission gate TG6, a third transistor T3 and a first NAND gate Nand1.

A control end of the sixth transmission gate TG6 which is effective when inputted with a high level receives the signal OUT\_Latch outputted by the latch circuit, another control end of the sixth transmission gate TG6 which is effective when inputted with a low level receives a signal OUT\_ Latch\_Inv obtained by processing the signal OUT\_Latch outputted by the latch circuit by a NOT operation, an input end of the sixth transmission gate TG6 is connected to the first clock signal end CLKIN1 of the shift register unit, and the sixth transmission gate TG6 outputs the signal received by the input end of the sixth transmission gate TG6 when the signal OUT\_Latch outputted by the latch circuit is of a high level.

An input end of the first NAND gate Nand1 receives an enable signal EN, another input end of the first NAND gate Nand1 is connected to an output end of the sixth transmission gate TG6 and a first electrode of the third transistor T3 respectively, and a signal outputted by the first NAND gate Nand1 is a signal OUT\_Trans outputted by the transmission circuit. The enable signal EN is of a high level during a time period of one frame for displaying an image.

A gate electrode of the third transistor TG3 receives the signal OUT\_Latch\_Inv obtained by processing the signal OUT\_Latch outputted by the latch circuit by a NOT operation, and a second electrode of the third transistor T3

receives a low level signal VSS. When the first electrode of the third transistor T3 is the source electrode, the second electrode of the third transistor T3 is the drain electrode. In contrast, when the first electrode of the third transistor T3 is the drain electrode, the second electrode of the third transistor T3 is the source electrode.

When the signal OUT\_Latch outputted by the latch circuit is of a high level, the sixth transmission gate TG6 is turned on, the third transistor T3 is turned off, and the sixth transmission gate TG6 outputs the clock signal received by 10 its input end to an input end of the first NAND gate Nand1. At this time, the enable signal EN is of a high level, and if the clock signal received by the input end of the sixth transmission gate TG6 is of a low level, the first NAND gate Nand1 outputs a high level signal. In contrast, if the clock 15 signal received by the input end of the sixth transmission gate TG6 is of a high level, the first NAND gate Nand1 outputs a low level signal. When the signal OUT\_Latch outputted by the latch circuit is of a low level, the sixth transmission gate TG6 is turned off, and the third transistor 20 T3 is turned on. Thus, the low level signal VSS is transmitted to the input end of the first NAND gate Nand1 via the third transistor T3. At this time, the first NAND gate Nand1 outputs a high level signal.

Alternatively, as an alternation of the embodiment as <sup>25</sup> illustrated in FIG. **5**, as illustrated in FIG. **6**, the transmission circuit includes a second NAND gate Nand**2**. An input end of the second NAND gate Nand**2** receives the signal OUT-\_Latch outputted by the latch circuit, another input end of the second NAND gate Nand**2** is connected to the first clock <sup>30</sup> signal end CLKIN**1** of the shift register unit, and a signal outputted by the second NAND gate NAND**2** is a signal OUT\_Trans outputted by the transmission circuit.

When the signal outputted by the latch circuit is of a high level, the signal outputted by the second NAND gate Nand2<sup>35</sup> is a signal obtained by processing the clock signal received by the first clock signal end CLKIN1 of the shift register unit by a NOT operation. In other words, when the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a high level, the second NAND gate Nand2<sup>40</sup> outputs a low level signal. In contrast, when the clock signal received by the first clock signal end CLKIN1 of the shift register unit is a low level signal, the second NAND gate Nand2 outputs a high level signal.

#### Fifth Embodiment Regarding Buffer Circuit

In this optional embodiment of the present disclosure, it is provided that the shift register unit further includes a buffer circuit to enhance the driving capability of the shift 50 register unit. The buffer circuit receives the signal OUT-Trans outputted by the transmission circuit, and processes the signal OUT\_Trans outputted by the transmission circuit by a NOT operation to obtain a signal and output the obtained signal. That is, when the signal OUT\_Trans out- 55 putted by the transmission circuit is of a high level, the signal OUT\_Buffer outputted by the buffer circuit is of a low level. When the signal OUT\_Trans outputted by the transmission circuit is of a low level, the signal OUT\_Buffer outputted by the buffer circuit is of a high level. In embodi- 60 ments of the present disclosure, when the shift register unit includes the buffer circuit, the signal OUT\_Buffer outputted by the buffer circuit is the signal OUT outputted by the shift register unit.

Alternatively, as illustrated in FIG. 7, the buffer circuit  $_{65}$  includes 2k+1 fourth inverts INV4 which are connected in series. An input end of a first fourth inverter of the 2k+1

fourth inverters INV4 receives the signal OUT\_Trans outputted by the transmission circuit. For each of the 2k+1 number of fourth inverters INV4 except the first fourth inverter, an output end of a previous fourth inverter INV4 is connected to an input end of a succeeding fourth inverter INV4, and an output end of the last one of the 2k+1 fourth inverters INV4 is an output end of the buffer circuit. The 2k+1 fourth inverters connected in series process the signal OUT\_Trans outputted by the transmission circuit by NOT operations to obtain a signal and output the obtained signal, wherein k is a nonnegative integer. If k=0, the buffer circuit merely includes one fourth inverter.

#### Sixth Embodiment Regarding Scanning Direction Selecting Circuit

In the embodiment of the present disclosure, the shift register unit further includes a scanning direction selecting circuit, so that the shift register unit may scan forwardly or backwardly. The scanning direction selecting circuit outputs a forward selection signal CHOF as the selection signal CHO when a forward control signal FS is of a high level and a backward control signal BS is of a low level. In contrast, the scanning direction selecting circuit outputs a backward selection signal CHOB as the selection signal CHO when a forward control signal FS is of a low level and a backward control signal BS is of a low level and a backward control signal BS is of a low level and a backward

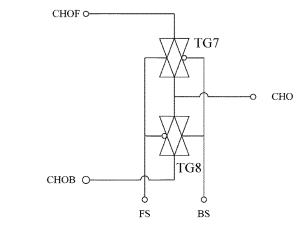

Alternatively, as illustrated in FIG. 8, the scanning direction selecting circuit includes a seventh transmission gate TG7 and an eighth transmission gate TG8. A control end of the seventh transmission gate TG7 which is effective when inputted with a high level receives the forward control signal FS, another control end of the seventh transmission gate TG7 which is effective when inputted with a low level receives the backward control signal BS, and the seventh transmission gate TG7 receives the forward selection signal CHOF, and outputs the forward selection signal CHOF when the forward control signal FS is of a high level and the backward control signal BS is of a low level. Furthermore, when the forward control signal FS is of a high level and the backward control signal BS is of a low level, the seventh transmission gate TG7 is turned on. In contrast, when the forward control signal FS is of a low level and the backward control signal BS is of a high level, the seventh transmission 45 gate TG7 is turned off.

A control end of the eighth transmission gate TG8 which is effective when inputted with a high level receives the backward control signal BS, another control end of the eighth transmission gate TG8 which is effective when inputted with a low level receives the forward control signal FS, and the eighth transmission gate TG8 receives the backward selection signal CHOB, and outputs the backward selection signal CHOB when the forward control signal FS is of a low level and the backward control signal FS is of a high level. Furthermore, when the forward control signal FS is of a high level and the backward control signal FS is of a low level, the eighth transmission gate TG8 is turned off. In contrast, when the forward control signal FS is of a low level, the backward control signal BS is of a low level and the backward control signal BS is of a low level, the eighth transmission gate TG8 is turned on.

In embodiments of the present disclosure, the clock signal received by the first clock signal end of the shift register unit is a first clock signal CLK1 or a second clock signal CLK2. When the first clock signal CLK1 is of a high level, the second clock signal CLK2 is of a low level. When the second clock signal CLK2 is of a high level, the first clock signal CLK2 is of a high level, the first clock signal CLK1 is of a low level.

Alternatively, the feedback signal FB is obtained by processing the forward selection signal CHOF and the backward selection signal CHOB by an OR operation. The forward selection signal CHOF is the selection signal CHO during a forward scanning, and the backward selection 5 signal CHOB is the selection signal CHO during a backward scanning.

Alternatively, the feedback signal FB is a clock signal received by the second clock signal end CLKIN2 of the shift register unit. When the clock signal received by the first 10 clock signal end CLKIN1 of the shift register unit is of a high level, the clock signal received by the second clock signal end CLKIN2 of the shift register unit is of a low level. Furthermore, when the clock signal received by the second clock signal end CLKIN2 of the shift register unit is of a 15 high level, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a low level. Thus, when the signal received by the first clock signal end CLKIN1 of the shift register unit is the first clock signal CLK1, the feedback signal FB, i.e. the signal received by the 20 second clock signal end CLKIN2 of the shift register unit is the second clock signal CLK2. When the clock signal received by the first clock signal end CLKIN1 of the shift register unit is the second clock signal CLK2, the feedback signal FB, i.e. the signal received by the second clock signal 25 end CLKIN2 of the shift register unit is the first clock signal CLK1.

Alternatively, the feedback signal FB is the signal OUT-\_Trans outputted by the transmission circuit.

## Seventh and Eighth Embodiments Regarding Shift Register Unit

In the seventh embodiment of the present disclosure, the shift register unit is as illustrated in FIG. 9, wherein the 35 feedback signal FB is obtained by processing the forward selection signal CHOF and the backward selection signal CHOB by an OR operation, the shift register unit includes the latch circuit, the transmission circuit, the buffer circuit, and the scanning direction selecting circuit. The latch circuit 40 is as illustrated in FIG. 3, the transmission circuit is as illustrated in FIG. 5, the buffer circuit merely includes one fourth inverter, and the scanning direction selecting circuit is as illustrated in FIG. 8.

In the eighth embodiment of the present disclosure, in the 45 shift register unit is as illustrated in FIG. 10, wherein the feedback signal FB is obtained by processing the forward selection signal CHOF and the backward selection signal CHOB by an OR operation, the shift register unit includes the latch circuit, the transmission circuit, the buffer circuit, 50 and the scanning direction selecting circuit. The latch circuit is as illustrated in FIG. 4, the transmission circuit is as illustrated in FIG. 5, the buffer circuit merely includes one fourth inverter, and the scanning direction selecting circuit is as illustrated in FIG. 8. 55

The third NOR gate Nor3 and the fifth inverter INV5 as illustrated in FIGS. 9 and 10 is used to process the forward selection signal CHOF and the backward selection signal CHOB by an OR operation. In the following, it is assumed that the clock signal received by the first clock signal end 60 CLKIN1 of the shift register unit as illustrated in FIG. 9 or 10 is the first clock signal CLK1. Obviously, the clock signal received by the first clock signal end CLKIN1 of the shift register unit as illustrated in FIG. 9 or 10 can alternatively be the second clock signal CLK2.

When the shift register unit as illustrated in FIGS. 9 and 10 scans forwardly, the forward control signal FS is of a high level, the backward control signal BS is of a low level. Thus, the seventh transmission gate TG7 is turned on, the eighth transmission gate TG8 is turned off, the forward selection signal CHOF is the selection signal CHO, and the workflow of the shift register unit is as illustrated in FIG. 11. In the following, it is assumed that the clock signal received by the first clock signal end CLKIN1 of the shift register unit as illustrated in FIG. 9 or 10 is the first clock signal CLK1; obviously, the clock signal received by the first clock signal end CLKIN1 of the shift register unit as illustrated in FIG. 9 or 10 can alternatively be the second clock signal CLK2.

During a first stage, i.e. a time period where the selection signal CHO (i.e. the forward selection signal CHOF) is of a high level, the signal OUT\_Latch outputted by the latch circuit is of a high level. Thus, the sixth transmission gate TG6 as illustrated in FIG. 9 or 10 is turned on, and the third transistor T3 is turned off, so that the clock signal received by the first clock signal end CLKIN1 of the shift register unit is transmitted to an input end of the first NAND gate Nand1, into which a signal Mid\_OUT is inputted. During the first stage, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a low level, and the enable signal EN is of a high level. Thus, in the first stage, the signal OUT outputted by the shift register unit as illustrated in FIG. 9 or 10 is of a low level.

During a second stage, i.e. a time period where the selection signal CHO (i.e. the forward selection signal CHOF) is of a low level, the signal OUT\_Latch outputted by the latch circuit is still of a high level. Thus, the sixth transmission gate TG6 as illustrated in FIG. 9 or 10 is turned on, and the third transistor T3 is turned off, so that the clock signal received by the first clock signal end CLKIN1 of the shift register unit is transmitted to the input end of the first NAND gate Nand1. During the second stage, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a high level, and the enable signal EN is of a high level. Thus, in the second stage, the signal OUT outputted by the shift register unit as illustrated in FIG. 9 or 10 is of a high level.

Upon entering a third stage from the second stage, since the backward selection signal CHOB is turned to be of a high level and the forward selection signal CHOF is still of a low level, the signal obtained by processing the forward selection signal CHOF and the backward selection signal CHOB by the third NOR gate Nor4 and the fifth inverter INV5 is changed from being of a low level to being of a high level, so that the signal OUT Latch outputted by the latch circuit is changed from being of a high level to being of a low level. That is, upon entering the third stage from the second stage, the backward selection signal CHOB is changed from being of a low level to being of a high level, so that the signal OUT Latch outputted by the latch circuit is changed from being of a high level to being of a low level, and thus the sixth transmission gate TG6 as illustrated in FIG. 9 or 10 is turned off, the third transistor T3 is turned on, and a low level signal VSS is transmitted to an input end of the first NAND gate Nand1. Thus, in the third stage, the input end of the first NAND gate Nand1 receives the low level signal VSS, another input end of the first NAND gate Nand1 receives the enable signal EN which is of a high level in the third stage. Thus, in the third stage, the signal OUT outputted by the shift register unit as illustrated in FIG. 9 or 10 is of a low level.

After that, the shift register unit as illustrated in FIG. 9 or 10 is kept to be in the third stage, until the forward selection signal CHOF is turned to be of a high level again. Then the shift register unit as illustrated in FIG. 9 or 10 enters the first

65

stage from the third stage. During the first and second stages, the shift register unit as illustrated in FIGS. 9 and 10 is in the operation state, while during the third stage, the shift register unit as illustrated in FIGS. 9 and 10 is in the non-operation state.

When the shift register unit as illustrated in FIGS. **9** and **10** scans backwardly, the backward control signal BS is of a high level, the forward control signal FS is of a low level. Thus, the seventh transmission gate TG**7** is turned off, the eighth transmission gate TG**8** is turned on, the backward <sup>10</sup> selection signal CHOB is the selection signal CHO, and the workflow of the shift register unit is as illustrated in FIG. **12**. When the shift register unit as illustrated in FIG. **9** or **10** scans backwardly, the operations of the latch circuit, the transmission circuit and the buffer circuit are exactly same <sup>15</sup> as the operations of those circuits when the shifter register unit scans forwardly, and thus the descriptions thereof are omitted herein.

When the shift register unit as illustrated in FIG. **9** or **10** scans, it is unnecessary to adopt a pair of complementary <sup>20</sup> and inverted clock signal to control the turning on and off of the transmission gate, and the clock signals may not be inputted into input ends of logic gates (the NOR gate, the NAND gate, and the inverter). Thus, when the shift register unit is in the non-operation state, the gate capacitor may not <sup>25</sup> be charged and discharged, which reduces the meaningless power consumption of the shift register unit in the non-operation state.

#### Ninth and Tenth Embodiments Regarding Shift Register Unit

In the ninth embodiment of the present disclosure, the shift register unit is as illustrated in FIG. **13**, wherein the feedback signal FB is the signal OUT\_Trans outputted by 35 the transmission circuit, the shift register unit includes the latch circuit, the transmission circuit, the buffer circuit, and the scanning direction selecting circuit. The latch circuit is as illustrated in FIG. **3**, the transmission circuit is as illustrated in FIG. **5**, the buffer circuit merely includes one fourth 40 inverter, and the scanning direction selecting circuit is as illustrated in FIG. **8**.

In the tenth embodiment of the present disclosure, the shift register unit is as illustrated in FIG. **14**, wherein the feedback signal FB is the signal OUT\_Trans outputted by 45 the transmission circuit, the shift register unit includes the latch circuit, the transmission circuit, the buffer circuit, and the scanning direction selecting circuit. The latch circuit is as illustrated in FIG. **4**, the transmission circuit is as illustrated in FIG. **5**, the buffer circuit merely includes one fourth 50 inverter, and the scanning direction selecting circuit is as illustrated in FIG. **8**.

When the shift register unit as illustrated in FIGS. **13** and **14** scans forwardly, the forward control signal FS is of a high level, the backward control signal BS is of a low level. Thus, 55 the seventh transmission gate TG**7** is turned on, the eighth transmission gate TG**8** is turned off, the forward selection signal CHOF is the selection signal CHO, and the workflow of the shift register unit is as illustrated in FIG. **15**. In the following, it is assumed that the clock signal received by the 60 first clock signal end CLKIN1 of the shift register unit as illustrated in FIG. **13** or **14** is the first clock signal end CLKIN1 of the shift register unit as illustrated in FIG. **13** or **14** is the first clock signal end CLKIN1 of the shift register unit as illustrated in FIG. **13** or **14** can alternatively be the second clock signal CLK**2**. 65

During a first stage, i.e. a time period where the selection signal CHO (i.e. the forward selection signal CHOF) is of a

high level, the signal OUT\_Latch outputted by the latch circuit is of a high level. Thus, the sixth transmission gate TG6 as illustrated in FIG. 13 or 14 is turned on, and the third transistor T3 is turned off, so that the clock signal received by the first clock signal end CLKIN1 of the shift register unit is transmitted to an input end of the first NAND gate Nand1, into which a signal Mid\_OUT is inputted. During the first stage, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a low level, and the enable signal EN is of a high level. Thus, in the first time period, the signal OUT outputted by the shift register unit as illustrated in FIG. 13 or 14 is of a low level.

During a second stage, i.e. a time period where the selection signal CHO (i.e. the forward selection signal CHOF) is of a low level, the signal OUT\_Latch outputted by the latch circuit is still of a high level. Thus, the sixth transmission gate TG6 as illustrated in FIG. 13 or 14 is turned on, and the third transistor T3 is turned off, so that the signal received by the first clock signal end CLKIN1 of the shift register unit is transmitted to the input end of the first NAND gate Nand1. During the second stage, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a high level, and the enable signal EN is of a high level. Thus, in the second stage, the signal OUT outputted by the shift register unit as illustrated in FIG. 13 or 14 is of a high level.

Upon entering a third stage from the second stage, since the clock signal received by the first clock signal end CLKIN1 of the shift register unit is turned to be of a low 30 level from being the high level, the sixth transmission gate TG6 and the third transistor T3 are still kept to be in the same state as the state during the second stage, i.e. the sixth transmission gate TG6 is turned on, and the third transistor T3 is turned off. Thus, the signal OUT outputted by the shift register unit as illustrated in FIG. 13 or 14 is changed from being of a high level to be of a low level, i.e. the signal OUT\_Trans outputted by the transmission circuit (i.e. the signal outputted by the first NAND gate Nand1) is changed from being of a low level to be of a high level. That is, the feedback signal FB is changed from being of a low level to be of a high level, so that the signal OUT\_Latch outputted by the latch circuit is changed from being of a high level to be of a low level. That is, upon entering the third stage from the second stage, the time signal received by the first clock signal end CLKIN1 of the shift register unit is changed from being of a high level to be of a low level, so that the signal OUT\_Latch outputted by the latch circuit is changed from being of a high level to be of a low level. Thus, the sixth transmission gate TG6 as illustrated in FIG. 13 or 14 is turned off, the third transistor T3 is turned on, and a low level signal VSS is transmitted to the input end of the first NAND gate Nand1. As a result, during the third stage, one input end of the first NAND gate Nand1 receives the low level signal VSS, and another input end of the first NAND gate Nand1 receives the enable signal EN. In the third stage, the enable signal EN is of a high level. Thus, in the third stage, the signal OUT outputted by the shift register unit as illustrated in FIG. 13 or 14 is of a low level.

After that, the shift register unit as illustrated in FIG. 13 or 14 is kept to be in the third stage, until the forward selection signal CHOF is turned to be of a high level again. Then the shift register unit as illustrated in FIG. 13 or 14 enters the first stage from the third stage. During the first and second stages, the shift register unit as illustrated in FIGS. 13 and 14 is in the operation state, while during the third stage, the shift register unit as illustrated in FIGS. 13 and 14 is in the non-operation state. When scanning forwardly, the backward selection signal CHOB does not affect the various circuits in the shift register unit.

When the shift register unit as illustrated in FIGS. 13 and 14 scans backwardly, the backward control signal BS is of a high level, the forward control signal FS is of a low level. 5 Thus, the seventh transmission gate TG7 is turned off, the eighth transmission gate TG8 is turned on, the backward selection signal CHOB is the selection signal CHO, and the workflow of the shift register unit is as illustrated in FIG. 16. When the shift register unit as illustrated in FIG. 13 or 14 10 scans backwardly, the operations of the latch circuit, the transmission circuit and the buffer circuit are exactly same as the operations of those circuits when the shifter register unit scans forwardly, and thus the descriptions thereof are omitted herein. When scanning backwardly, the backward 15 selection signal CHOF does not affect the various circuits in the shift register unit.

When the shift register unit as illustrated in FIG. **13** or **14** scans, it is unnecessary to adopt a pair of clock signal CLK to control the turning on and off of the transmission gate, and <sup>20</sup> the clock signals may not be inputted into input ends of logic gates (the NOR gate, the NAND gate, and the inverter). Thus, when the shift register unit is in the non-operation state, the gate capacitor may not be charged and discharged, which reduces the meaningless power consumption of the <sup>25</sup> shift register unit in the non-operation state. However, there is a risk of logic competition in the shift register unit as illustrated in FIG. **13** or **14** when a duty ratio of the clock signal is less than 50%.

#### Eleventh and Twelfth Embodiments Regarding Shift Register Unit

In the eleventh embodiment of the present disclosure, the shift register unit is as illustrated in FIG. **17**, wherein the 35 feedback signal FB is the clock signal received by the second clock signal end CLKIN2 of the shift register unit, the shift register unit includes the latch circuit, the transmission circuit, the buffer circuit, and the scanning direction selecting circuit. And the latch circuit is as illustrated in FIG. **4**0 **3**, the transmission circuit is as illustrated in FIG. **5**, the buffer circuit merely includes one fourth inverter, and the scanning direction selecting circuit is as illustrated in FIG. **8**.

In the twelfth embodiment of the present disclosure, the 45 shift register unit is as illustrated in FIG. **18**, wherein the feedback signal FB is the clock signal received by the second clock signal end CLKIN**2** of the shift register unit, the shift register unit includes the latch circuit, the transmission circuit, the buffer circuit, and the scanning direction 50 selecting circuit. The latch circuit is as illustrated in FIG. **4**, the transmission circuit is as illustrated in FIG. **5**, the buffer circuit merely includes one fourth inverter, and the scanning direction selecting circuit is as illustrated in FIG. **8**.

When the shift register unit as illustrated in FIGS. **17** and 55 **18** scans forwardly, the forward control signal FS is of a high level, the backward control signal BS is of a low level. Thus, the seventh transmission gate TG**7** is turned on, the eighth transmission gate TG**8** is turned off, the forward selection signal CHOF is the selection signal CHO, and the workflow 60 of the shift register unit is as illustrated in FIG. **19**.

During a first stage, i.e. a time period where the selection signal CHO (i.e. the forward selection signal CHOF) is of a high level, the signal OUT\_Latch outputted by the latch circuit is of a high level. Thus, the sixth transmission gate 65 TG6 as illustrated in FIG. 17 or 18 is turned on, and the third transistor T3 is turned off, so that the clock signal received

by the first clock signal end CLKIN1 of the shift register unit is transmitted to an input end of the first NAND gate Nand1, into which a signal Mid\_OUT is inputted. During the first stage, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a low level, and the enable signal EN is of a high level. Thus, in the first stage, the signal OUT outputted by the shift register unit as illustrated in FIG. **17** or **18** is of a low level.

During a second stage, i.e. a time period where the selection signal CHO (i.e. the forward selection signal CHOF) is of a low level, the signal OUT\_Latch outputted by the latch circuit is still of a high level. Thus, the sixth transmission gate TG6 as illustrated in FIG. 17 or 18 is turned on, and the third transistor T3 is turned off, so that the signal received by the first clock signal end CLKIN1 of the shift register unit is transmitted to the input end of the first NAND gate Nand. During the second stage, the clock signal received by the first clock signal end CLKIN1 of the shift register unit is of a high level, and the enable signal EN is of a high level. Thus, in the second stage, the signal OUT outputted by the shift register unit as illustrated in FIG. 17 or 18 is of a high level.

Upon entering a third stage from the second stage, the selection signal CHO, i.e. the forward selection signal CHOF is of a low level, so that the fourth transmission gate TG4 is turned on, and the clock signal received by the second backward clock signal end CLKIN2 of the shift register unit is changed from being of a low level to be of a high level. Thus the signal OUT Latch outputted by the latch circuit is changed from being of a high level to be of a low level, so that the sixth transmission gate TG6 as illustrated in FIG. 17 or 18 is turned off, the third transistor T3 is turned on, and a low level signal VSS is transmitted to an input end of the first NAND gate Nand1. As a result, in the third stage, one input end of the first NAND gate Nand1 receives the low level signal VSS, another input end of the first NAND gate Nand1 receives the enable signal EN which is of a high level in the third stage, so that the signal OUT outputted by the shift register unit as illustrated in FIG. 17 or 18 is of a low level.

After that, the shift register unit as illustrated in FIG. 13 or 18 is kept to be in the third stage, until the forward selection signal CHOF is turned to be of a high level again. Then the shift register unit as illustrated in FIG. 17 or 18 enters the first stage from the third stage. During the first and second stages, the shift register unit as illustrated in FIGS. 17 and 18 is in the operation state, while during the third stage, the shift register unit as illustrated in FIGS. 17 and 18 is in the non-operation state. Since the backward selection signal CHOB does not affect the various circuits in the shift register unit, the backward selection signal CHOB is not illustrated in FIG. 19.

When the shift register unit as illustrated in FIGS. **17** and **18** scans backwardly, the backward control signal BS is of a high level, the forward control signal FS is of a low level. Thus, the seventh transmission gate TG**7** is turned off, the eighth transmission gate TG**8** is turned on, the backward selection signal CHOB is the selection signal CHO, and the workflow of the shift register unit is as illustrated in FIG. **20**. When the shift register unit as illustrated in FIG. **17** or **18** scans backwardly, the operations of the latch circuit, the transmission circuit and the buffer circuit are exactly same as the operations of those circuits when the shifter register unit scans forwardly, and thus the descriptions thereof are omitted herein. When scanning backwardly, the backward selection signal CHOF does not affect the various circuits in the shift register unit.

15