US009484205B2

# (12) United States Patent

## Chang et al.

#### (54) SEMICONDUCTOR DEVICE HAVING SELF-ALIGNED GATE CONTACTS

- (71) Applicant: International Business Machines Corporation, Armonk, NY (US)

- Inventors: Josephine B. Chang, Mahopac, NY (US); Paul Chang, Mahopac, NY (US); Michael A. Guillorn, Yorktown Heights, NY (US)

- (73) Assignee: INTERNATIONAL BUSINESS MACHINES CORPORATION, Armonk, NY (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 14/585,381

- (22) Filed: Dec. 30, 2014

#### (65) **Prior Publication Data**

US 2015/0287603 A1 Oct. 8, 2015

#### **Related U.S. Application Data**

- (60) Provisional application No. 61/976,073, filed on Apr. 7, 2014.

- (51) **Int. Cl.**

| H01L 21/28  | (2006.01)   |

|-------------|-------------|

| H01L 21/283 | (2006.01)   |

| H01L 29/417 | (2006.01)   |

|             | (Continued) |

- (52) U.S. Cl.

CPC ...... H01L 21/283 (2013.01); H01L 21/76837 (2013.01); H01L 21/76897 (2013.01); H01L 29/665 (2013.01)

- (58) Field of Classification Search

- CPC ......H01L 21/762; H01L 21/76224; H01L 21/76283; H01L 21/76837; H01L 21/76897; H01L 29/665

## (10) Patent No.: US 9,484,205 B2

## (45) **Date of Patent:** Nov. 1, 2016

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

6,885,055 B2 4/2005 Lee 6,936,508 B2 8/2005 Visokay et al. (Continued)

#### OTHER PUBLICATIONS

I. Saad et al., "Design and simulation of 50 nm vertical double-gate MOSFET (VDGM)," IEEE International Conference on Semiconductor Electronics, 2006, ICSE'06, pp. 549-553.

(Continued)

Primary Examiner — Jerome Jackson, Jr. Assistant Examiner — David Spalla

(74) Attorney, Agent, or Firm — Cantor Colburn LLP; Vazken Alexanian

#### (57) **ABSTRACT**

A semiconductor device and a method for manufacturing the device. The method includes: depositing a first dielectric layer on a semiconductor device; forming a plurality of first trenches through the first dielectric layer; depositing an insulating fill in the plurality of first trenches; planarizing the plurality of first trenches; forming a first gate contact between the plurality of first trenches; depositing a first contact fill in the first gate contact; planarizing the first gate contact; depositing a second dielectric layer on the device; forming a plurality of second trenches through the first and second dielectric layers; depositing a conductive fill in the plurality of second trenches; planarizing the plurality of second trenches; forming a second gate contact where the second gate contact is in contact with the first gate contact; depositing a second contact fill in the second gate contact; and planarizing the second gate contact.

#### 9 Claims, 12 Drawing Sheets

(51) Int. Cl.

| H01L 29/423 | (2006.01) |

|-------------|-----------|

| H01L 29/66  | (2006.01) |

| H01L 29/78  | (2006.01) |

| H01L 21/768 | (2006.01) |

|             |           |

### (56) **References Cited**

## U.S. PATENT DOCUMENTS

| 7,241,649 | B2 | 7/2007 | Donze et al. |

|-----------|----|--------|--------------|

| 7,332,779 | B2 | 2/2008 | Chang        |

| 7,452,758 B2    | 11/2008 | Dyer et al.     |

|-----------------|---------|-----------------|

| 2009/0134469 A1 | 5/2009  | Chang et al.    |

| 2012/0175712 A1 | 7/2012  | Chang et al.    |

| 2013/0020639 A1 | 1/2013  | Thompson et al. |

### OTHER PUBLICATIONS

Z. Guo et al., "FinFET-based SRAM design,". Proceedings of the 2005 International Symposium on Low Power Electronics and Design, Aug. 2005, pp. 2-7.

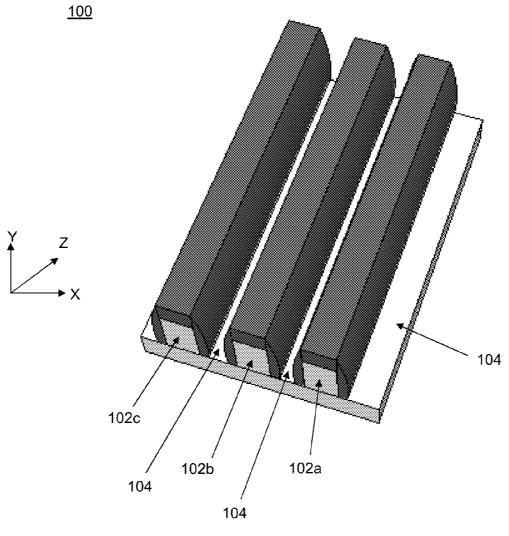

FIG. 1

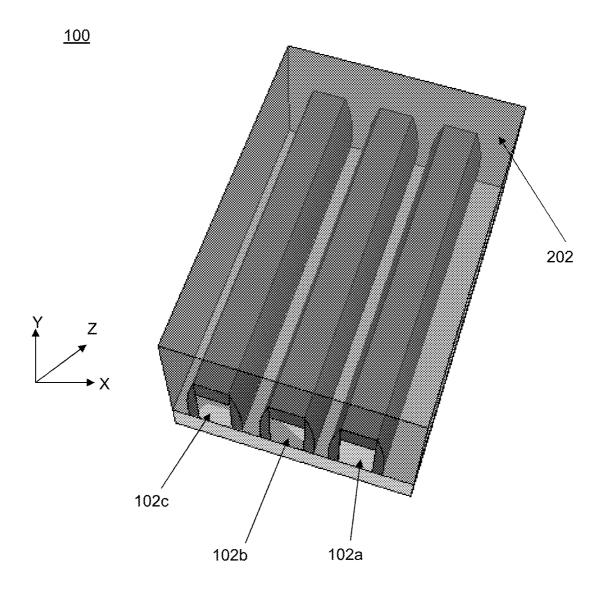

FIG. 2

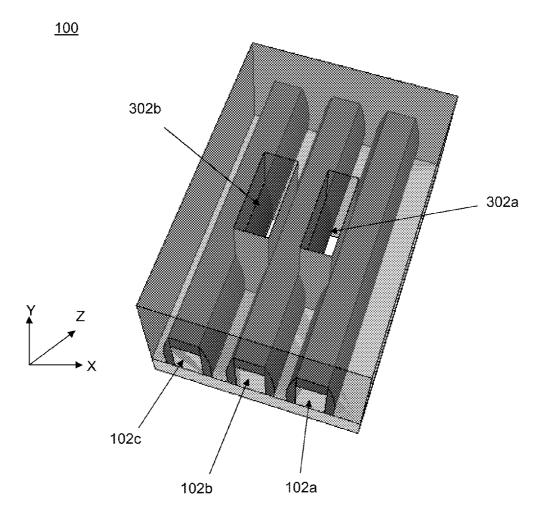

FIG. 3

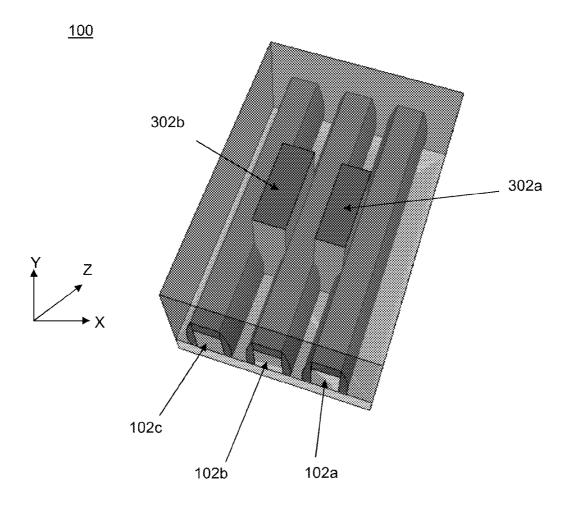

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

10

#### SEMICONDUCTOR DEVICE HAVING SELF-ALIGNED GATE CONTACTS

#### DOMESTIC PRIORITY

This application claims priority to U.S. Provisional Application No. 61/976,073, entitled "SEMICONDUCTOR DEVICE HAVING SELF-ALIGNED GATE CONTACTS,' filed Apr. 7, 2014, which is incorporated herein by reference in its entirety.

#### BACKGROUND

The present invention relates to semiconductor devices. More specifically, the present invention relates to a semiconductor device having self-aligned gate contacts over an active area and a method for manufacturing the device.

Field-effect transistors (FETs) are used in many integrated circuit designs, as switches to open and close the circuits. In general, a FET includes a source region and a drain region 20 connected by a channel, and a gate that regulates electron flow through the channel between the source and drain regions.

For years, the continued minimization of metal oxide semiconductor field-effect transistors (MOSFETs) has 25 driven the worldwide semiconductor industry. Access to and operation of semiconductor devices is provided by contacts to the devices. During manufacture or forming of semiconductor devices, it is important to ensure that gate contacts do not short to the source/drain region. To avoid shorting, a gate 30 must be contacted in a field region. This ground rule limits wiring flexibility at the first metal level and increases the footprint of cells which require multiple gate contacts, especially when adjacent gates must be contacted.

#### SUMMARY

According to a first aspect of the present invention, a method for manufacturing a semiconductor device is provided. The method includes: depositing a first dielectric 40 layer on a semiconductor device having a plurality of gate structures formed on a plurality of active regions, and a plurality of diffusion regions formed alongside the plurality active regions, wherein the plurality of gate structures have a top, a bottom, and two sides, and are encapsulated by an 45 according to an embodiment of the present invention. insulating layer on the top and two sides; forming a plurality of first trenches through the first dielectric laver, wherein the plurality of first trenches are formed at a plurality of first locations and expose a first portion of the plurality of diffusion regions; forming silicide on the first portion of the 50 plurality of diffusion regions exposed by the plurality of the first trenches; depositing an insulating material in the plurality of first trenches; planarizing the plurality of first trenches; forming at least one first gate contact through the first dielectric layer and the insulating layer on the top of at 55 least one of the plurality of gate structures, wherein the at least one first gate contact is formed between the plurality of first trenches; depositing a first contact fill in the at least one first gate contact; planarizing the at least one first gate contact; depositing a second dielectric layer on the first 60 dielectric layer, the plurality of filled first trenches, and the at least one filled gate contact; forming a plurality of second trenches through the first and second dielectric layers, wherein the plurality of second trenches are formed at a plurality of second locations and expose a second portion of 65 the plurality of diffusion regions; forming silicide on the second portion of the plurality of diffusion regions exposed

2

by the plurality of second trenches; depositing a conductive material in the plurality of second trenches; planarizing the plurality of second trenches; forming at least one second gate contact through the second dielectric layer, wherein the at least one second gate contact is in contact with the at least one first gate contact; depositing a second contact fill in the at least one second gate contact; and planarizing the at least one second gate contact.

According to another aspect of the present invention, a semiconductor device is provided. The device includes: a first dielectric layer formed over a semiconductor device having a plurality of gate structures formed on a plurality of active regions, and a plurality of diffusion regions formed along side the plurality of active regions, wherein the plurality of gate structures have a top, a bottom, and two sides, and are encapsulated by an insulating layer on the top and two sides; a plurality of first trenches formed at a plurality of first locations through the first dielectric layer to a first portion of the plurality of diffusion regions, wherein silicide is formed on the first portion of the plurality of diffusion regions and the plurality of first trenches are filled with an insulating material; at least one first gate contact formed through the first dielectric layer and the insulating layer on the top at least one of the plurality of gate structures, wherein the at least one first gate contact is filled a first contact fill and formed between the plurality of first trenches; a second dielectric layer deposited on the first dielectric layer, the plurality of first filled trenches, and the at least one filled gate contact; a plurality of second trenches formed at a plurality of second locations through the first and second dielectric layers to a second portion of the plurality of diffusion regions, wherein silicide is formed on the second portion of the plurality of diffusion regions and the <sup>35</sup> plurality of second trenches are filled with a conductive material; and at least one second gate contact through the second dielectric layer, wherein the at least one second gate contact is filled with a second contact fill and is in contact with the at least one first gate contact.

#### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

FIG. 1 is a diagram of a generic MOSFET device,

FIG. 2 depicts the device from FIG. 1 following the deposition of a first dielectric layer covering device, according to an embodiment of the present invention.

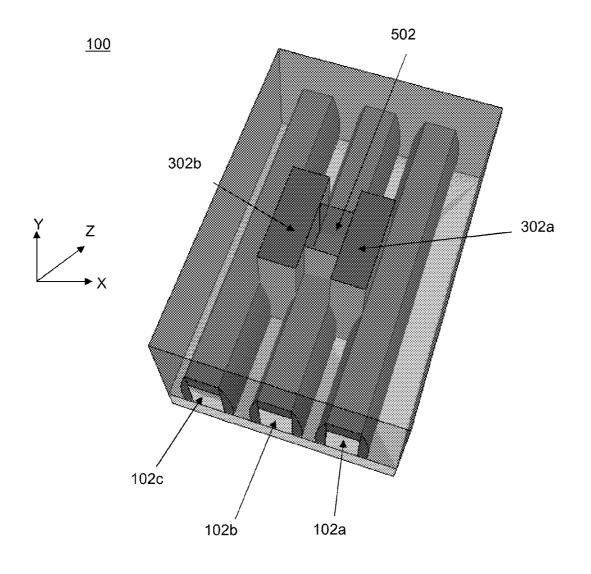

FIG. 3 depicts the device from FIG. 2 after a first set of trenches are formed through the first dielectric layer, according to an embodiment of the present invention.

FIG. 4 depicts the device from FIG. 3 after the first set of trenches are filled with an insulating material and planarized, according to an embodiment of the present invention.

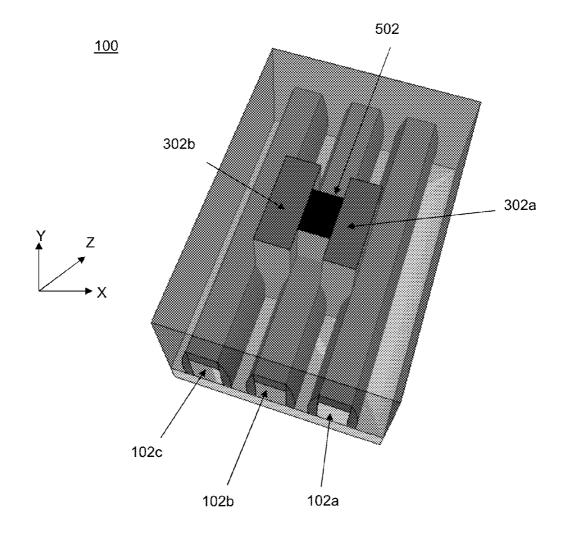

FIG. 5 depicts the device from FIG. 4 following the formation of a first gate contact between the first set of trenches, according to an embodiment of the present invention.

FIG. 6 depicts the device from FIG. 5 after the first gate contact is filled with a metal and planarized, according to an embodiment of the present invention.

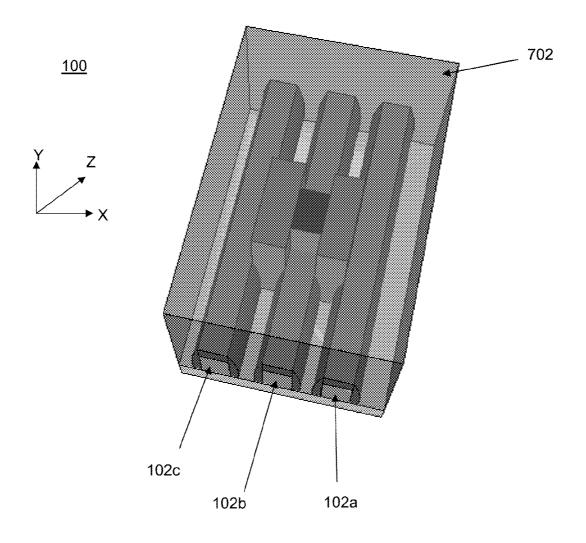

FIG. 7 depicts the device from FIG. 6 following the deposition of a second dielectric layer covering the device, according to an embodiment of the present invention.

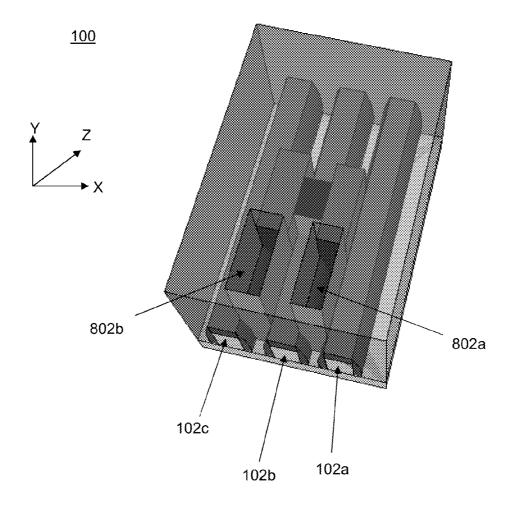

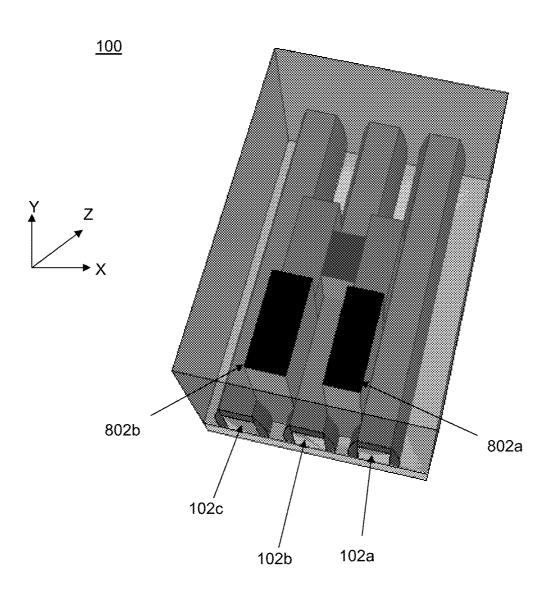

FIG. 8 depicts the device from FIG. 7 after a second set of trenches are formed through the first and second dielectric layers, according to an embodiment of the present invention. 10

15

FIG. 9 depicts the device from FIG. 8 after the second set of trenches are filled with a conductive material and planarized, according to an embodiment of the present invention

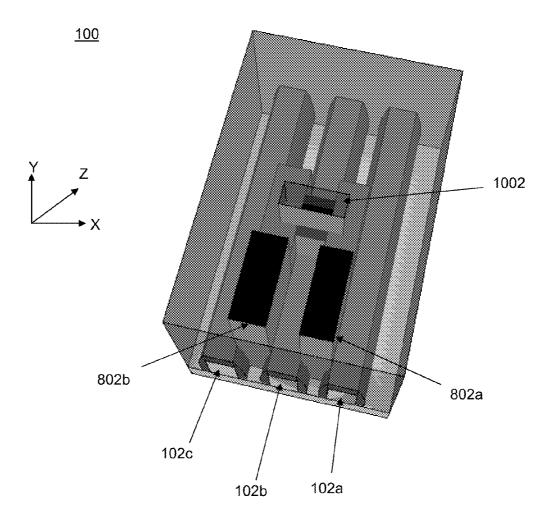

FIG. 10 depicts the device from FIG. 9 following the 5 formation of a second gate contact, according to an embodiment of the present invention.

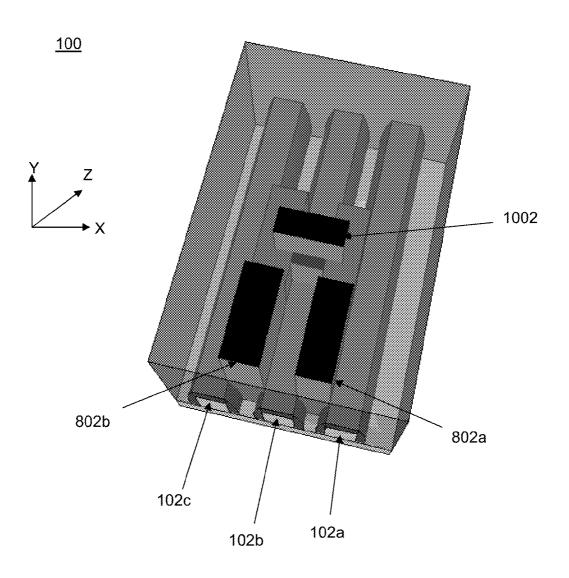

FIG. 11 depicts the device from FIG. 10 after the second gate contact is filled with a metal and planarized, according to an embodiment of the present invention.

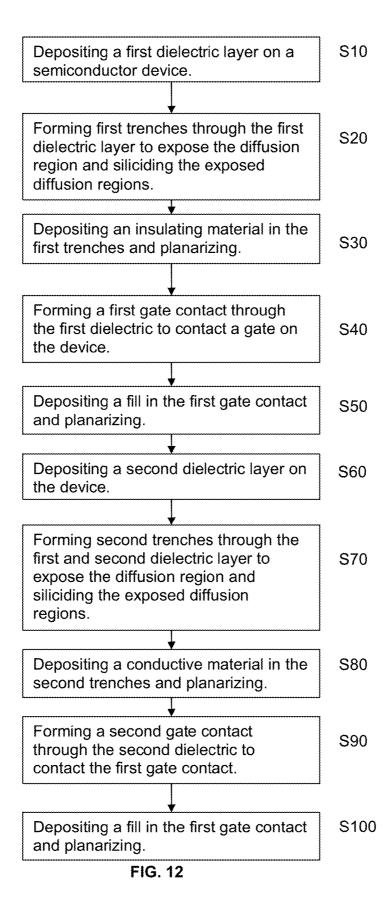

FIG. 12 is a flow chart depicting the operations of the method for fabricating the semiconductor device, according to an embodiment of the present invention.

#### DETAILED DESCRIPTION

Embodiments of the present invention allow gate structures to be contacted over an active region while ensuring that such contacts do not short to the diffusion region or neighboring gate structures.

Referring to FIG. 1, a diagram of a processor 100 is shown. Processor 100 is a generic MOSFET processor that has gate structures 102a, 102b, and 102c, which are formed on active regions. The active regions can be planar, as shown, or they can be fins, nanowires, etc. Diffusion regions 25 104 are alongside the active regions and between gate structures 102a, 102b, and 102c. Gate structures 102a, 102b, and 102c are, as pictured in FIG. 1, encapsulated by an insulating layer, shown as dark gray, on the top and two sides of the gate structures. According to an embodiment of the 30 present invention, gate structures 102a, 102b, and 102c can be at a pitch of 50 nm-100 nm. However, even smaller pitches can be contemplated.

Referring to FIGS. 2 & 12, processor 100 is depicted after the completion of operation S10. In operation S10, a first 35 dielectric layer 202 is deposited on processor 100. As shown in FIG. 2, diffusion regions 104 and gate structures 102a, 102b, and 102c are covered by first dielectric layer 202. First dielectric layer 202 can include a middle of the line (MOL) dielectric, such as SiO<sub>2</sub> or SiCOH. 40

Referring to FIGS. 3 & 12, processor 100 is shown after operation S20 has been performed. In operation S20, first trenches 302a and 302b are formed through first dielectric layer 202 to expose a portion of diffusion regions 104 between gate structures 102a, 102b, and 102c. As depicted 45 in FIG. 3, first trench 302a exposes a portion of diffusion region 104 that is between gate structures 102a and 102b. First trench 302b exposes a portion of diffusion region 104 that is between gate structures 102b and 102c.

Following the formation of first trenches 302a and 302b, 50 silicide is formed on the exposed portions of diffusion region 104 at the bottom of the trenches. The process of forming silicide in such a manner is well known in the art. FIG. 3 depicts first trench 302a between gate structures 102a and 102b, and first trench 302b between gate structures 102b and 55 102c. First trenches 302a and 302b are depicted as being formed at the midpoint of gate structures 102a, 102b, and 102c. However, the present invention is not limited to this design. The trenches can be formed at any position along the width (z direction) of the gate structures. Further, multiple 60 trenches can be formed between a given pair of gate structures, as opposed to what is shown in FIG. 3, where one trench is formed between the given pair of gate structures.

Referring to FIGS. 4 & 12, processor 100 is depicted following the completion of operation S30. In operation 65 S30, first trenches 302a and 302b are filled with an insulating material. The insulating material used to fill the trenches

4

can be a dielectric, such as silicon nitride  $(Si_3N_4)$ . The material used in this operation to fill first trenches 302a and 302b is different than the material used in first dielectric layer 202. The process performed in operations S20 and S30 is a standard trench contact module, know by those skilled in the art, but with one difference. The only difference is that in operation S30, an insulating material is used as a fill instead of a metal that would be used in the standard trench contact module. After the trenches are filled with the insulating material, an etch back or polish of the trenches is performed. Following the etch back or polish of first trenches 302a and 302b, processor 100 is planarized.

Referring to FIGS. 5 & 12, processor 100 is shown after operation S40 has been performed. In operation S40, first gate contact 502 is formed above gate structure 102b and between first trenches 302a and 302b. As shown in FIG. 5, first gate contact 502 is formed through first dielectric layer 202 and through the insulating layer that is on the top side of gate structure 102b. According to an embodiment of the 20 present invention, one or more gate contacts can be formed above a gate structure when there are one or more pairs trenches formed along the gate structure. First gate contact 502 can be formed so that it is shorter (in the y direction) than first trenches 302a and 302b. First trenches 302a and 302b can also be wider (in the z direction) than first gate contact 502. This is ideal in preventing first gate contact 502 from shorting to the diffusion region. First gate contact 502 is protected from shorting to the diffusion regions below and neighboring gates by the insulating material that fills first trenches 302a and 302b. Also, to further prevent shorting to the diffusion or neighboring gate structures, first trenches 302a and 302b are longer (y direction) and wider (z direction) than first gate contact 502.

Referring to FIGS. 6 & 12, processor 100 is depicted after the completion of operation S50. In operation S50, first gate contact **502** is filled with a first contact fill. The first contact fill can include a conductive material such as a metal, for example, titanium, titanium nitride, tungsten, aluminum, copper, platinum, tantalum, tantalum nitride, or any combination thereof. Standard contact processing can be used in order to deposit the first contact fill in first gate contact 502. After first gate contact 502 is filled with the first contact fill, first gate contact 502 is planarized in the same manner as first trenches 302a and 302b, described above.

Referring to FIGS. 7 & 12, processor 100 is shown after operation S60 has been performed. In operation S60, second dielectric layer 702 is deposited on processor 100. As illustrated in FIG. 7, second dielectric layer 702 covers first trenches 302a and 302b, first gate contact 502, and first dielectric layer 202. Second dielectric layer 702, just like first dielectric layer 202, can be a middle of the line (MOL) dielectric.

Referring to FIGS. 8 & 12, processor 100 is shown following the completion of operation S70. In operation S70, second trenches 802a and 802b are formed through both first dielectric layer 202 and second dielectric layer 702. As depicted in FIG. 8, second trenches 802a and 802b are formed between gate structures 102a, 102b, and 102c. Second trench 802a exposes a portion of diffusion region 104 between gate structures 102a and 102b and second trench 802b exposes a portion of diffusion region 104 between gate structures 102b and 102c. Second trenches 802a and 802b are formed at different locations along the width (z-direction) of gate structure 102b than first trenches 302a and 302b. Following the formation of the trenches, silicide is formed on the exposed portions of diffusion region 104 at the bottom of the trenches. Second trenches 802a and 802b can be contiguous with first trenches 302a and 302b, and second trenches 802a and 802b must not contact first gate contact 502. FIG. 8 depicts second trench 802a between gate structures 102a and 102b, and second trench 802bbetween gate structures 102b and 102c. Second trenches 5 802a and 802b are depicted as being formed at the endpoint of gate structures 102a, 102b, and 102c. However, the present invention is not limited to this design. Second trenches 802a and 802b can be formed at multiple positions along the width (z-direction) of the gate structures. For 10 example, a pair of first trenches can be formed at the midpoint of the gate structure and two pair of second trenches can be formed at the ends of the gate structure. As another example, two pairs of first trenches can be formed at the ends of the gate structure and a pair of second trenches 15 can be formed at the midpoint of the gate structure. The designer has the freedom to choose the arrangement of the processor and the arrangement of the first and second trenches

Referring to FIGS. 9 & 12, processor 100 is shown 20 following the completion of operation S80. In operation S80, second trenches 802*a* and 802*b* are filled with a conductive material. The conductive material used to fill the trenches can be metal, such as titanium, titanium nitride, tungsten, aluminum, copper, platinum, tantalum, tantalum 25 nitride, or any combination thereof. After the trenches are filled, an etch back or polish of the trenches is performed in order to planarize processor 100. The process performed in operations S70 and S80 is a standard trench contact module and is know by those skilled in the art. The prior trench 30 contact module performed here, except an insulating material was used as a fill instead of the conductive material used in here.

Referring to FIGS. 10 & 12, processor 100 is depicted 35 after operation S90 has been performed. In operation S90, second gate contact 1002 is formed above first gate contact 502. As illustrated in FIG. 10, second gate contact 1002 is a contact via formed through second dielectric layer 702 to contact first gate contact 502. However, second gate contact 40 1002 does not contact second trenches 802*a* and 802*b*. First trenches 302*a* and 302*b* help to prevent second gate contact 1002 from shorting to the diffusion region, and they give the designer tolerance when forming second gate contact 1002. First trenches 302*a* and 302*b* prevent shorting to the diffusion region and neighboring gate structures, and thus allows the designer more overlay tolerance.

Referring to FIGS. 11 & 12, processor 100 is shown following the completion of operation S100. In operation S100, second gate contact 1002 is filled with a second 50 contact fill. The second contact fill is a metal and can include, for example, titanium, titanium nitride, tungsten, aluminum, copper, platinum, tantalum, tantalum nitride, or any combination thereof. Standard contact processing can be used in order to deposit the second contact fill in second gate 55 contact 1002. After second gate contact 1002 is filled with the second contact fill, second gate contact 1002 is planarized.

The resulting structure after the completion of operations in FIG. **12** includes a semiconductor device with self- 60 aligned gate contacts over an active area. First trenches **302***a* and **302***b* are formed through first dielectric layer **202** and between gate structures **102***a*, **102***b*, and **102***c*. First gate contact **502** contacts gate structure **102***b* and is formed between first trenches **302***a* and **302***b*. Second trenches **802***a* 65 and **802***b* are formed through first dielectric layer **202** and second dielectric layer **702**. Second gate contact **1002** is

formed so that it contacts first gate contact **502** but does not contact second trenches **802***a* and **802***b*. The design of the device prevents the gate contacts from shorting to diffusion region **104** and neighboring gate structures **102***a* and **102***c* due to an insulating material that fills first trenches **302***a* and **302***b*. The overall design of the device allows for greater flexibility and gives the designer of the FET extra overlay tolerance.

The descriptions of the various embodiments of the present invention have been presented for purposes of illustration, but are not intended to be exhaustive or limited to the embodiments disclosed. Many modifications and variations will be apparent to those of ordinary skill in the art without departing from the scope and spirit of the described embodiments. The terminology used herein was chosen to best explain the principles of the embodiments, the practical application or technical improvement over technologies found in the marketplace, or to enable others of ordinary skill in the art to understand the embodiments disclosed herein.

What is claimed is:

**1**. A method of manufacturing a semiconductor device, the method comprising:

- depositing a first dielectric layer on a semiconductor device having a plurality of gate structures formed on a plurality of active regions and a plurality of diffusion regions formed alongside the plurality active regions, wherein the plurality of gate structures have a top, a bottom, and two sides, and are encapsulated by an insulating layer on the top and two sides;

- forming a plurality of first trenches through the first dielectric layer, wherein the plurality of first trenches are formed at a plurality of first locations thereby exposing a first portion of the plurality of diffusion regions;

- forming silicide on the first portion of the plurality of diffusion regions;

- depositing an insulating material in the plurality of first trenches;

planarizing the plurality of first trenches;

- forming at least one first gate contact through the first dielectric layer and the insulating layer on the top of at least one of the plurality of gate structures, wherein the at least one first gate contact is formed between the plurality of first trenches;

- depositing a first contact fill in the at least one first gate contact;

planarizing the at least one first gate contact;

- depositing a second dielectric layer on the first dielectric layer, the plurality of filled first trenches, and the at least one filled gate contact;

- forming a plurality of second trenches through the first and second dielectric layers, wherein the plurality of second trenches are formed at a plurality of second locations thereby exposing a second portion of the plurality of diffusion regions;

- forming silicide on the second portion of the plurality of diffusion regions exposed by the plurality of second trenches;

- depositing a conductive material in the plurality of second trenches;

planarizing the plurality of second trenches;

forming at least one second gate contact through the second dielectric layer, wherein the at least one second gate contact is in contact with the at least one first gate contact; 30

depositing a second contact fill in the at least one second gate contact; and

planarizing the at least one second gate contact.

**2**. The method according to claim **1**, wherein the first and second dielectric layer comprises a first middle of the line 5 dielectric.

**3**. The method according to claim **1**, wherein the plurality of second locations are contiguous with the plurality of first locations.

**4**. The method according to claim **1**, wherein the insulat- 10 ing material comprises a second middle of the line dielectric.

**5**. The method according to claim **4**, wherein the second middle of the line dielectric comprises silicon nitride.

6. The method according to claim 1, wherein the plurality of first trenches extend a distance through the first dielectric 15 layer and the at least one first gate contact extends a distance through the first dielectric layer, the distance the at least one first gate contact extends through the first dielectric layer is less than the distance the plurality of first trenches extend through the first dielectric layer. 20

7. The method according to claim 1, wherein the conductive material, the first contact fill, and the second contact fill comprise a metal.

**8**. The method according to claim **7**, wherein the metal is selected from a group consisting of: titanium, titanium 25 nitride, tungsten, aluminum, copper, platinum, tantalum, tantalum nitride, and combinations thereof.

**9**. The method according to claim **1**, wherein planarizing comprises performing an etch-back or polish.

\* \* \* \* \*