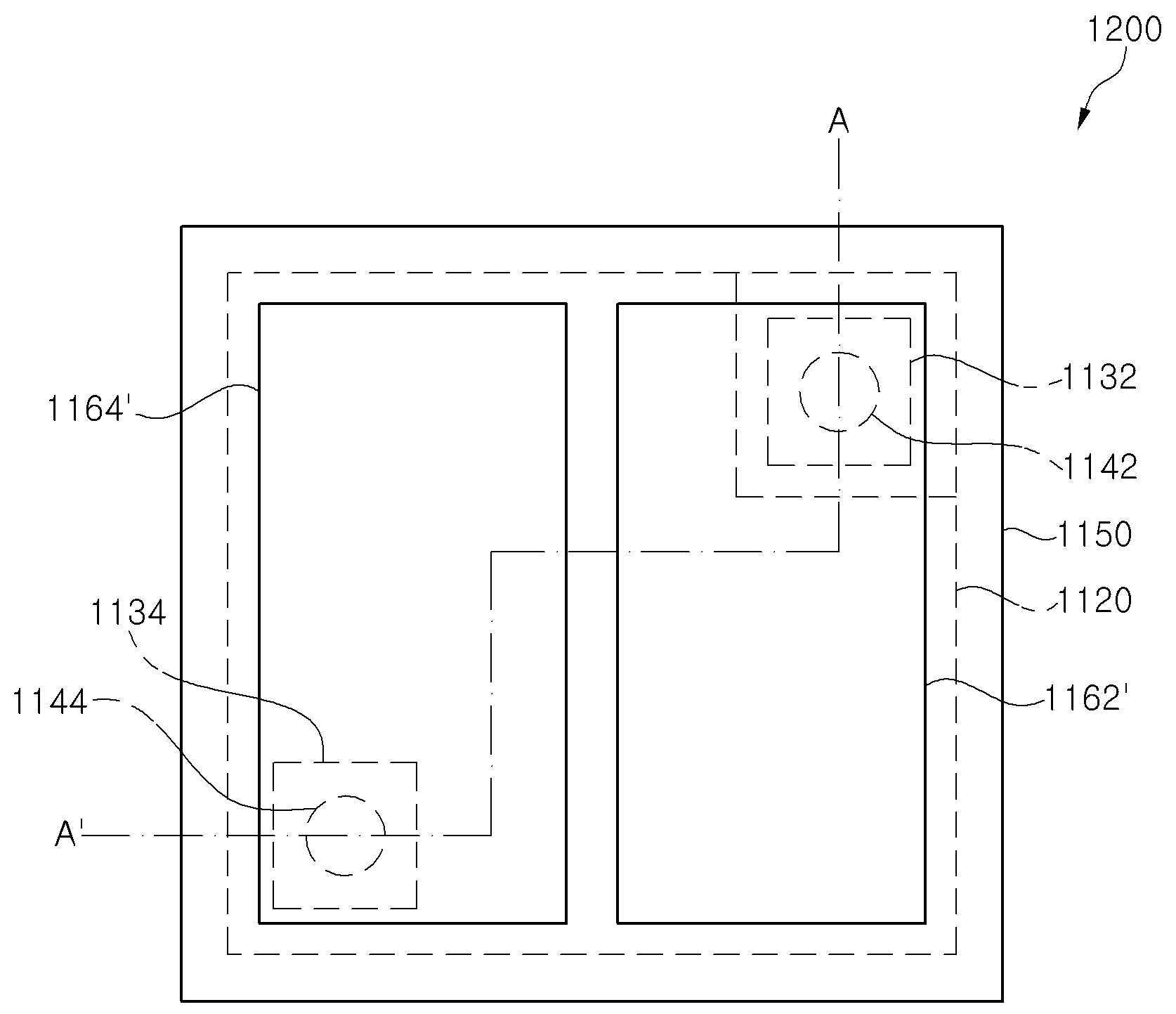

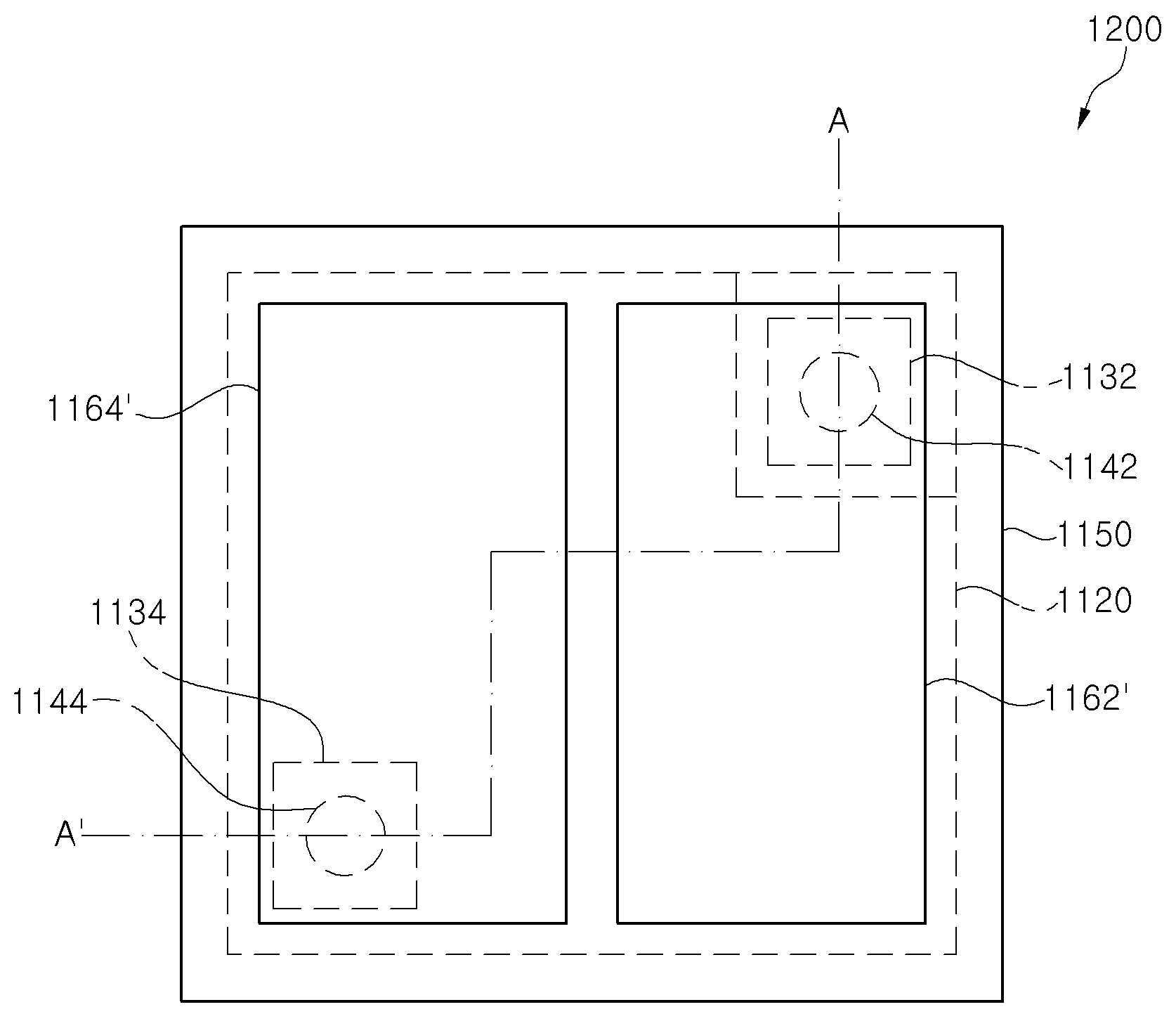

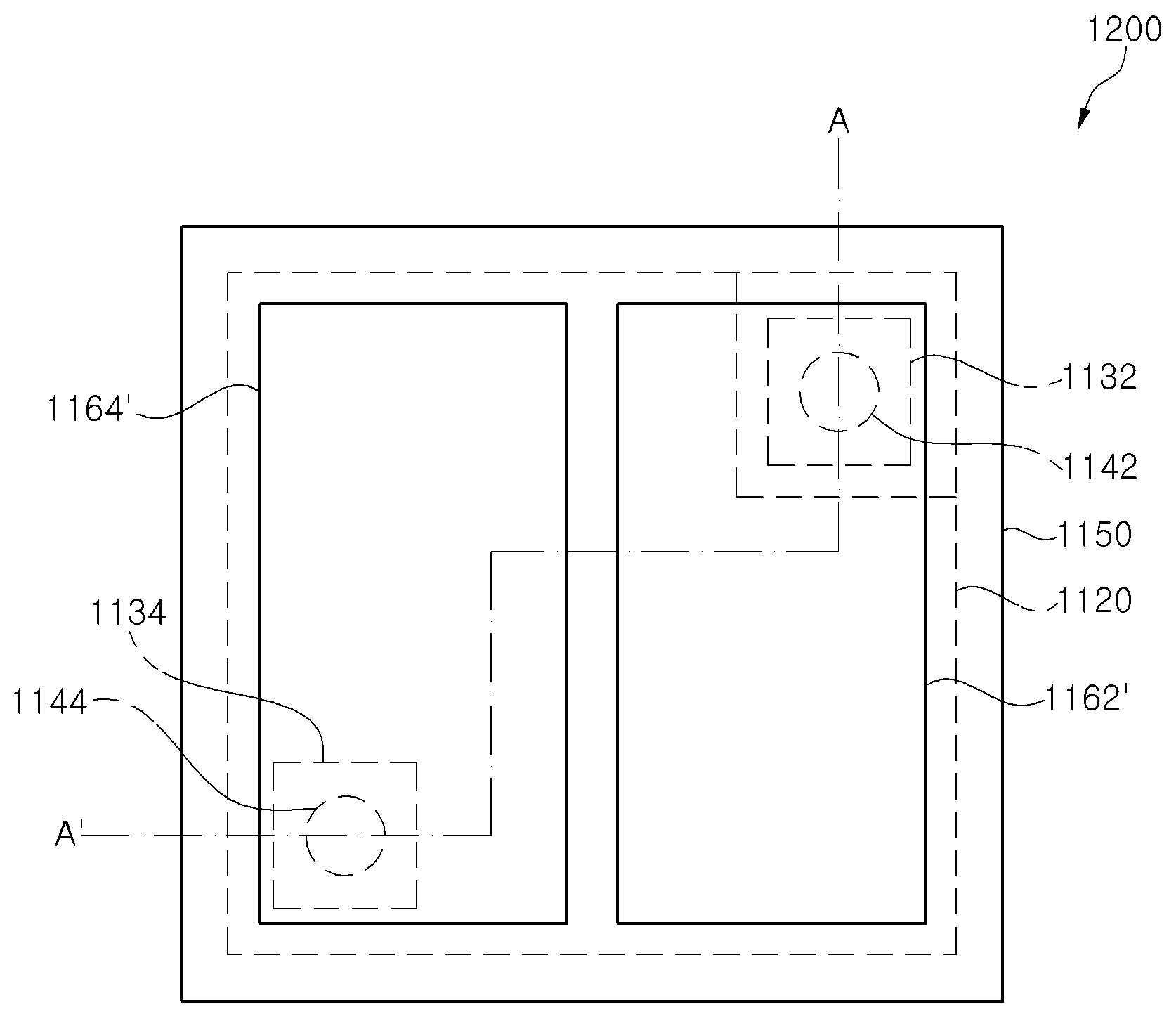

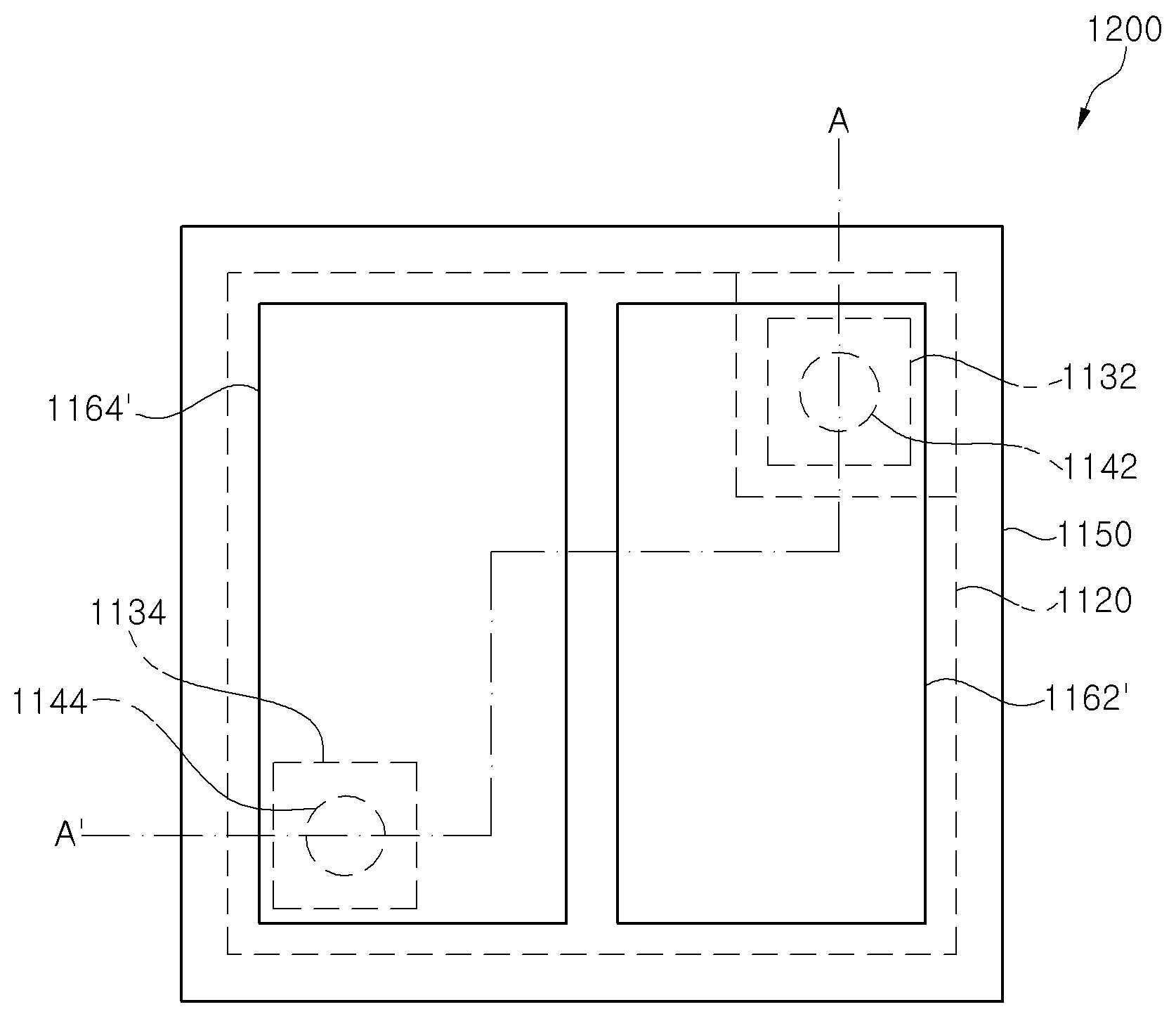

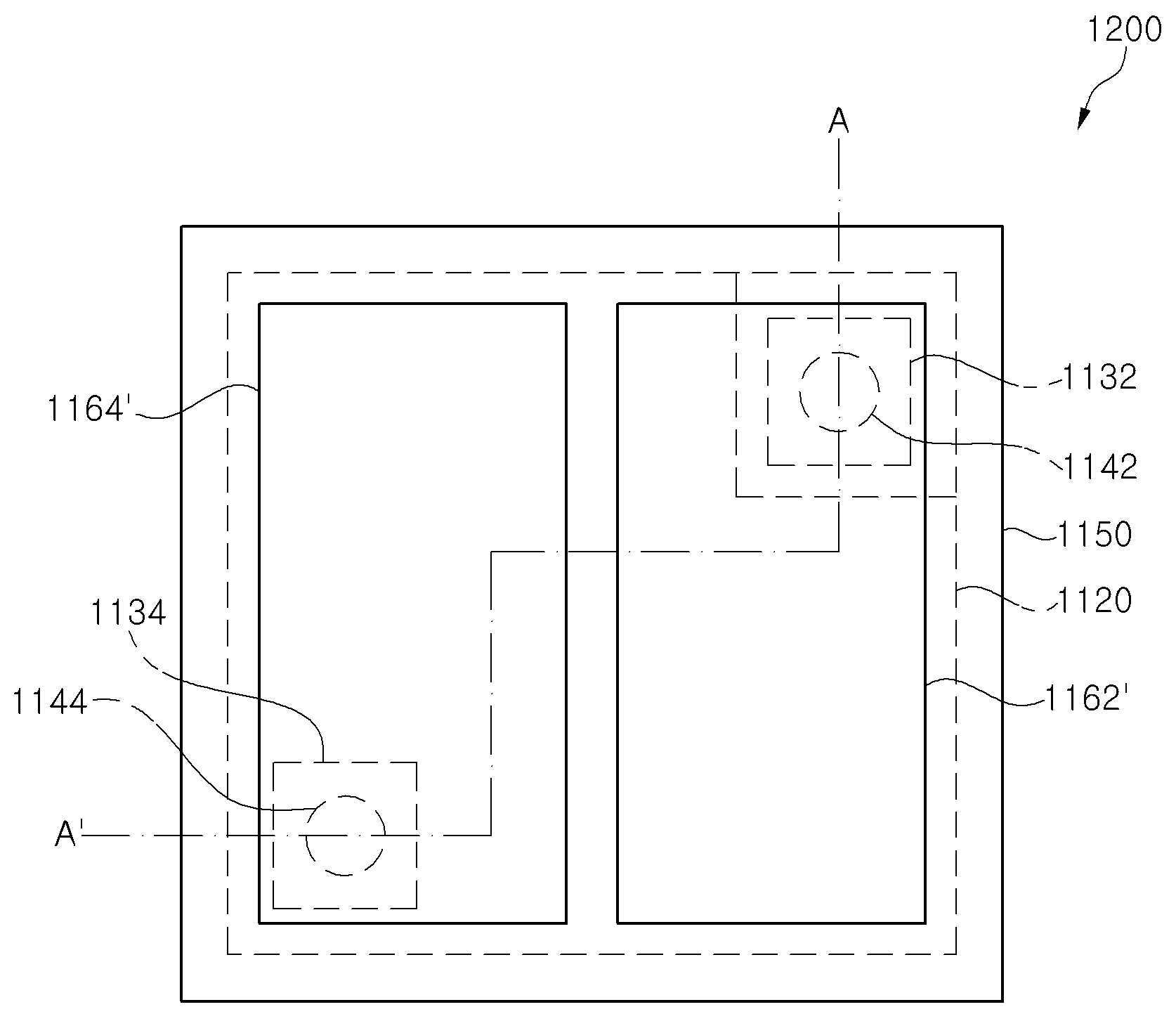

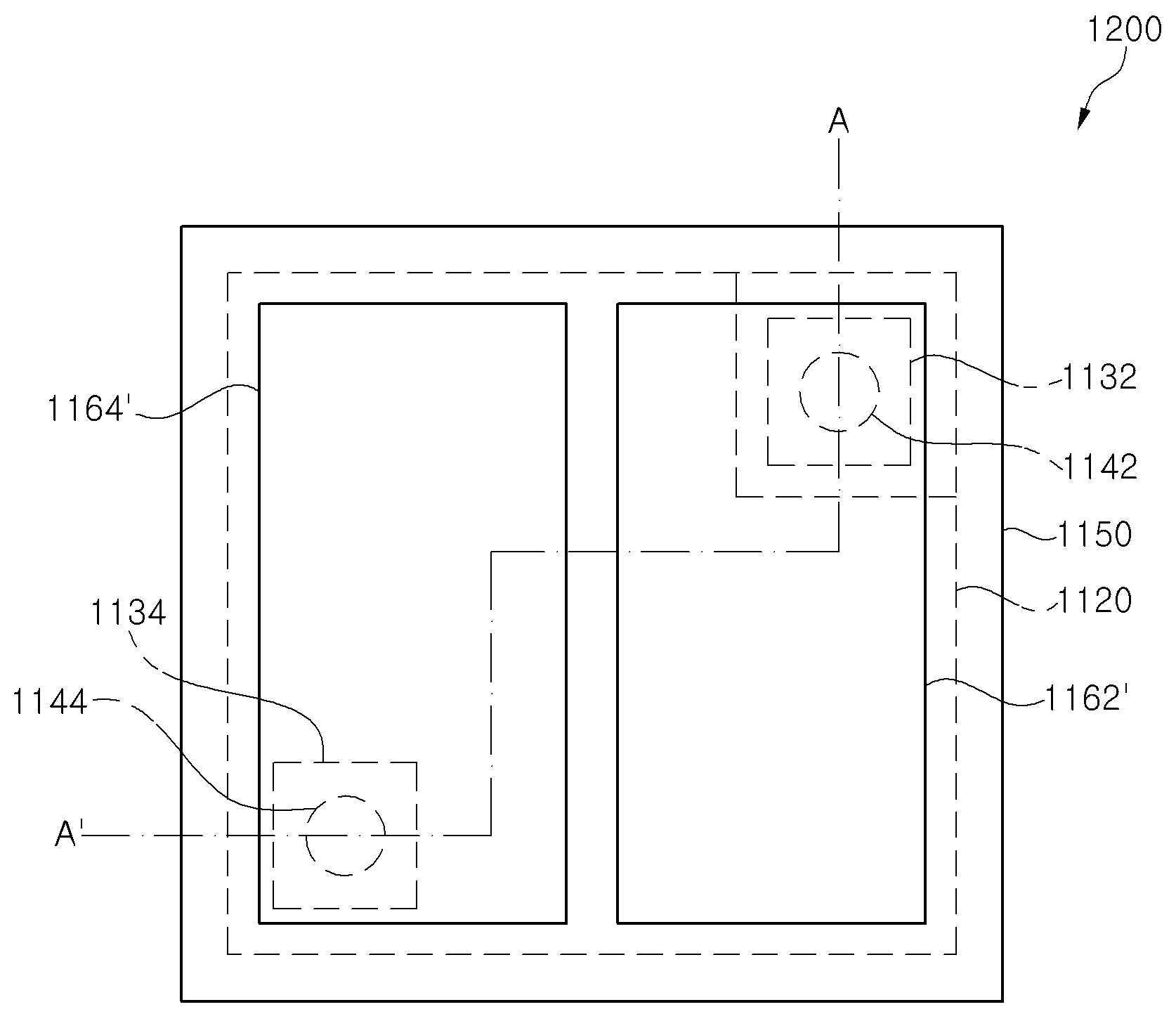

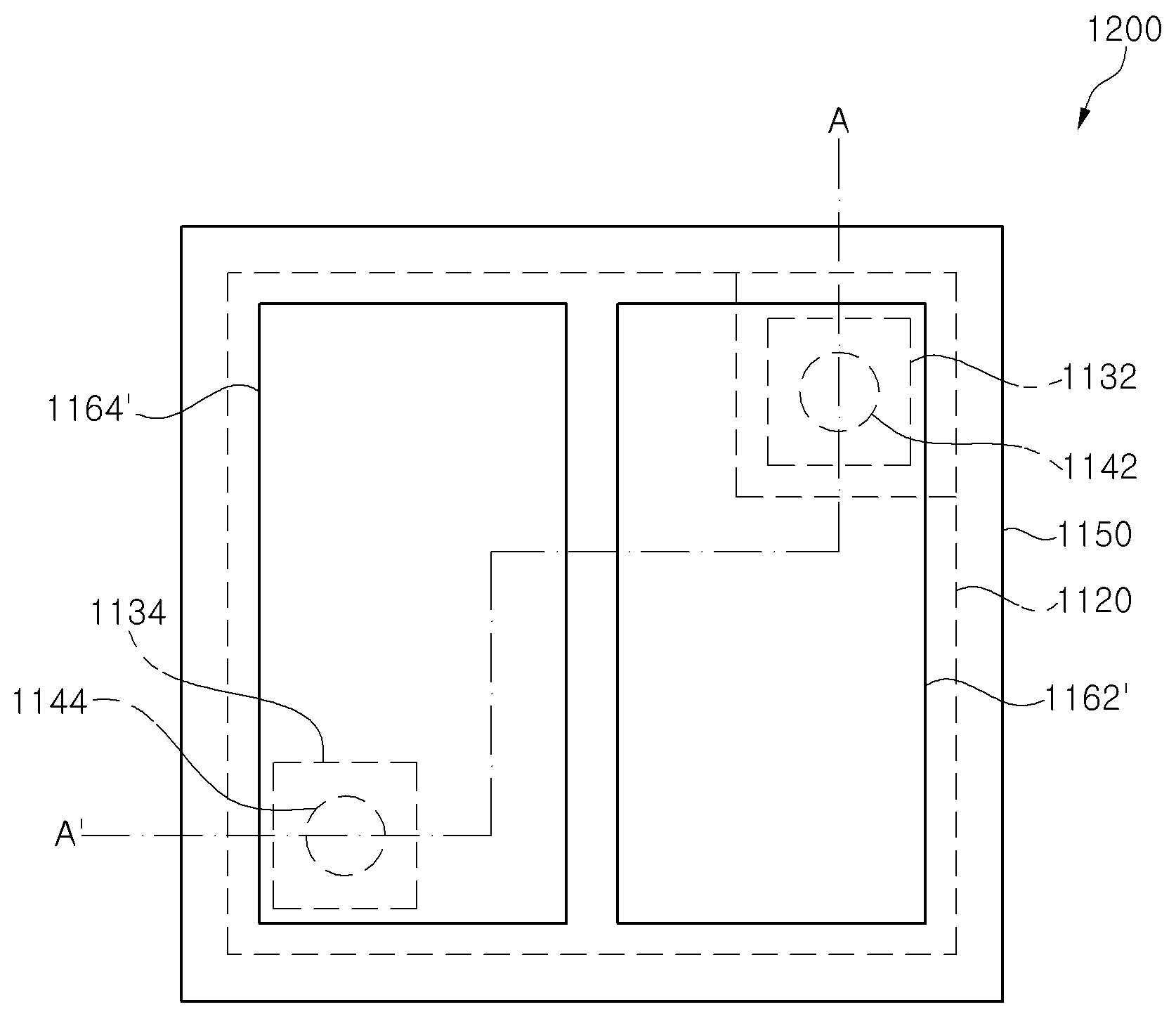

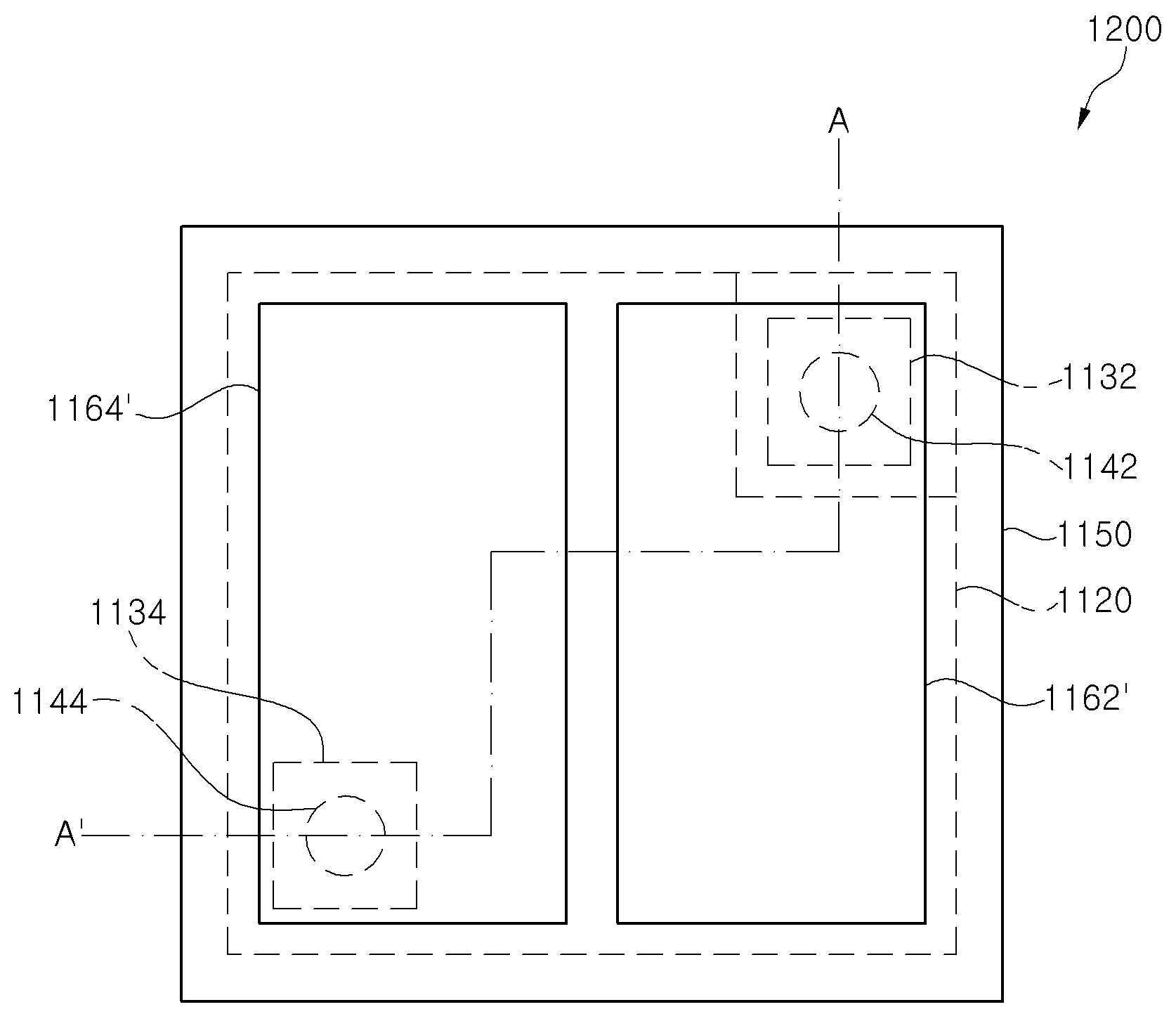

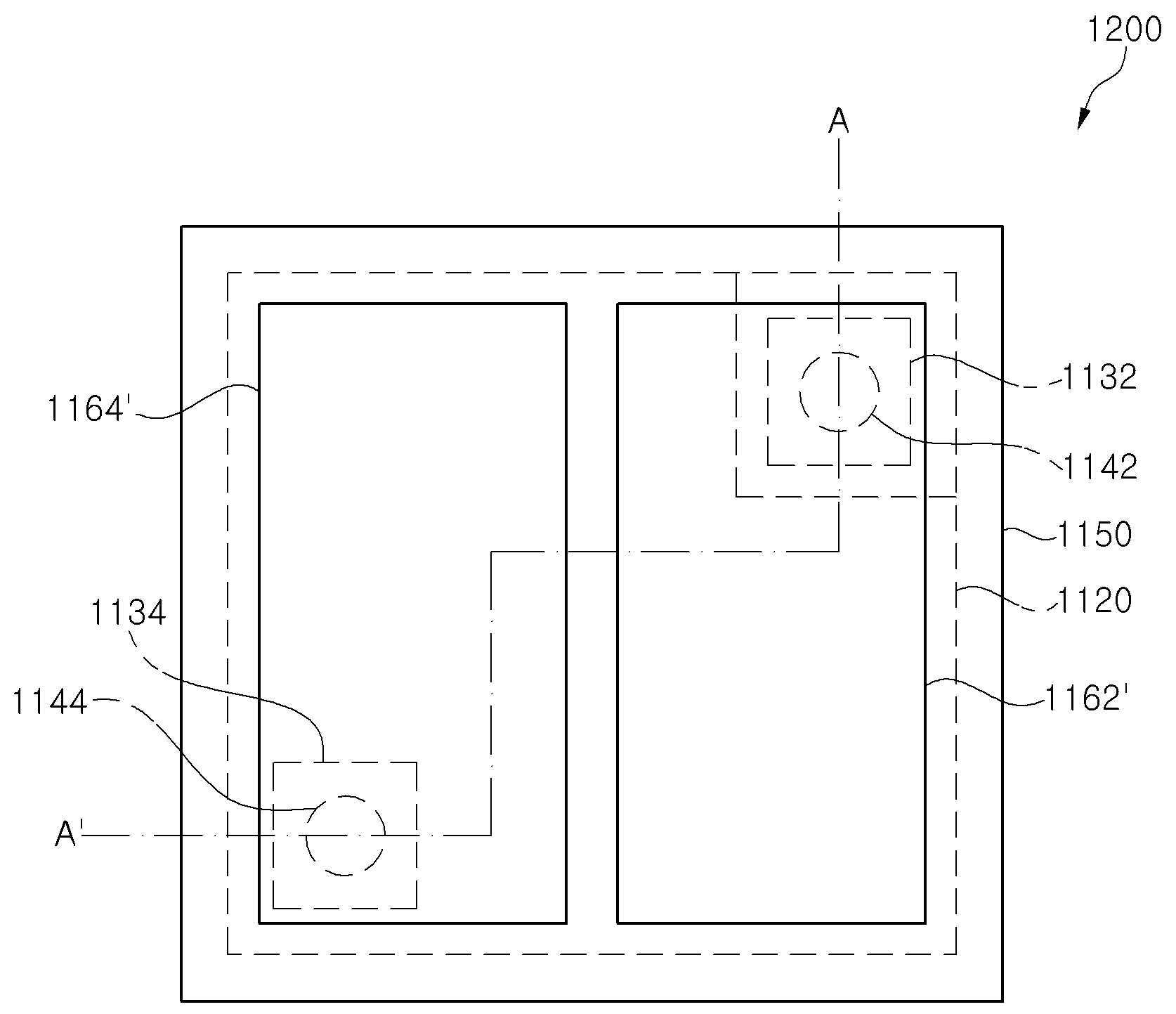

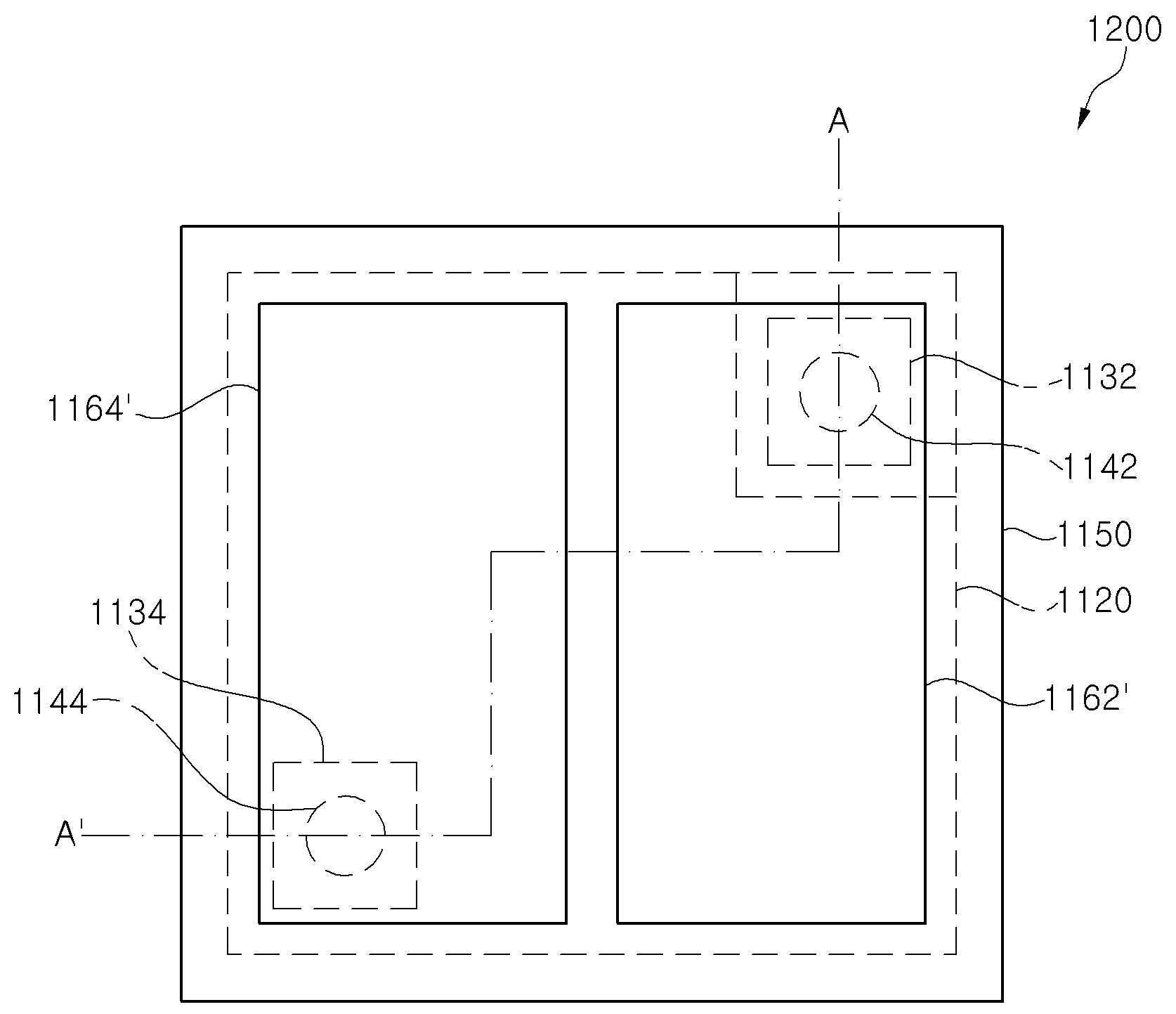

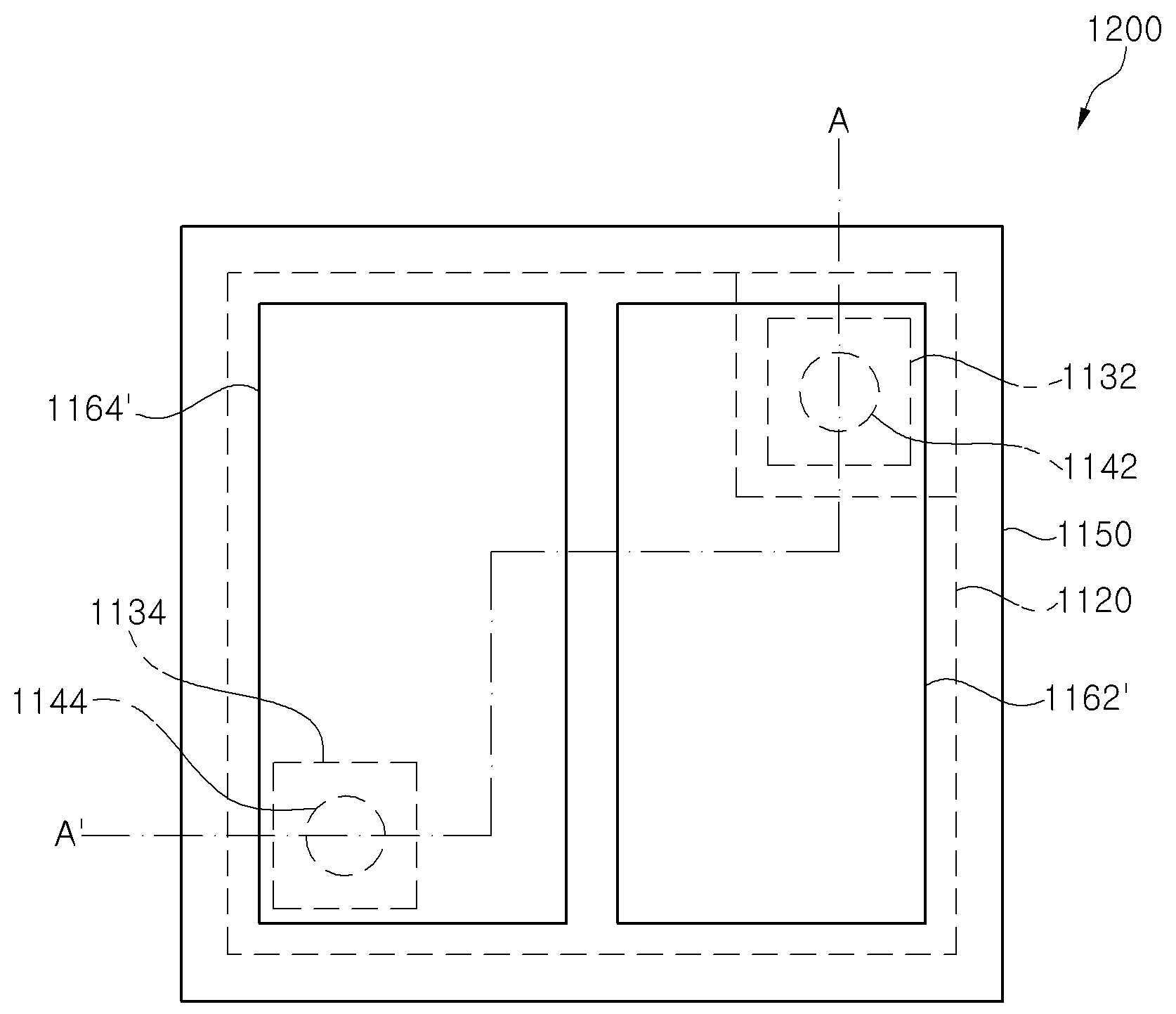

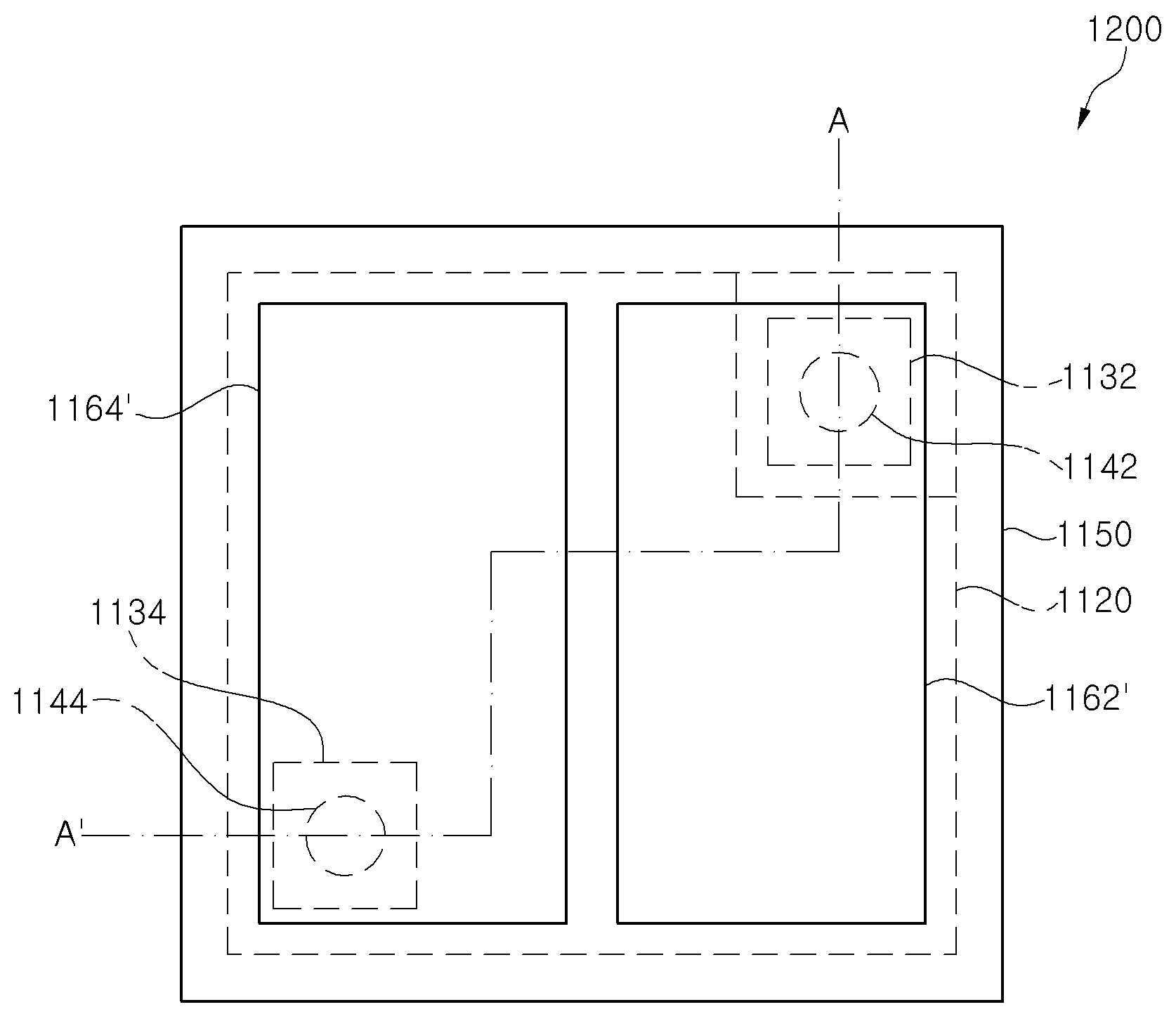

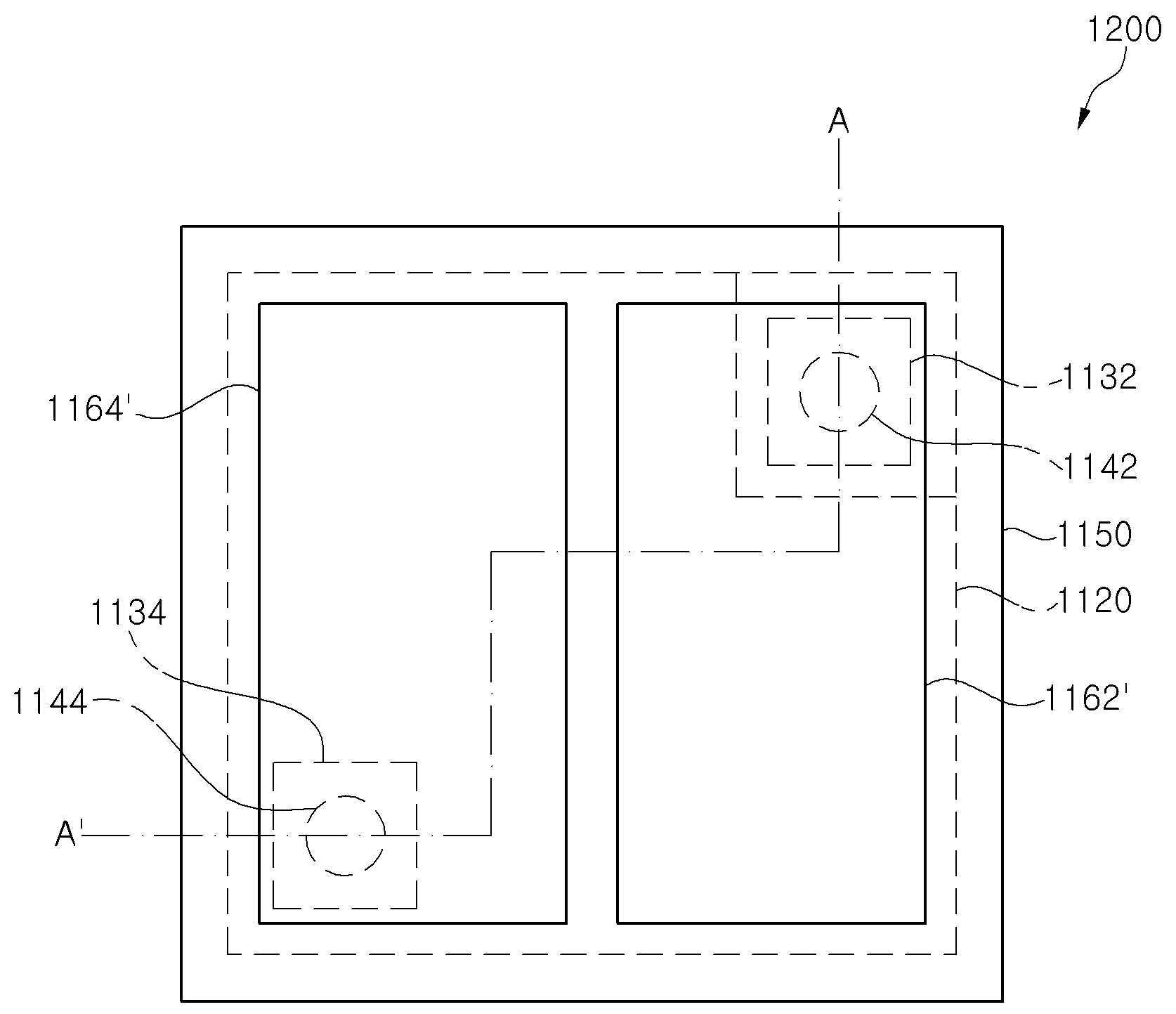

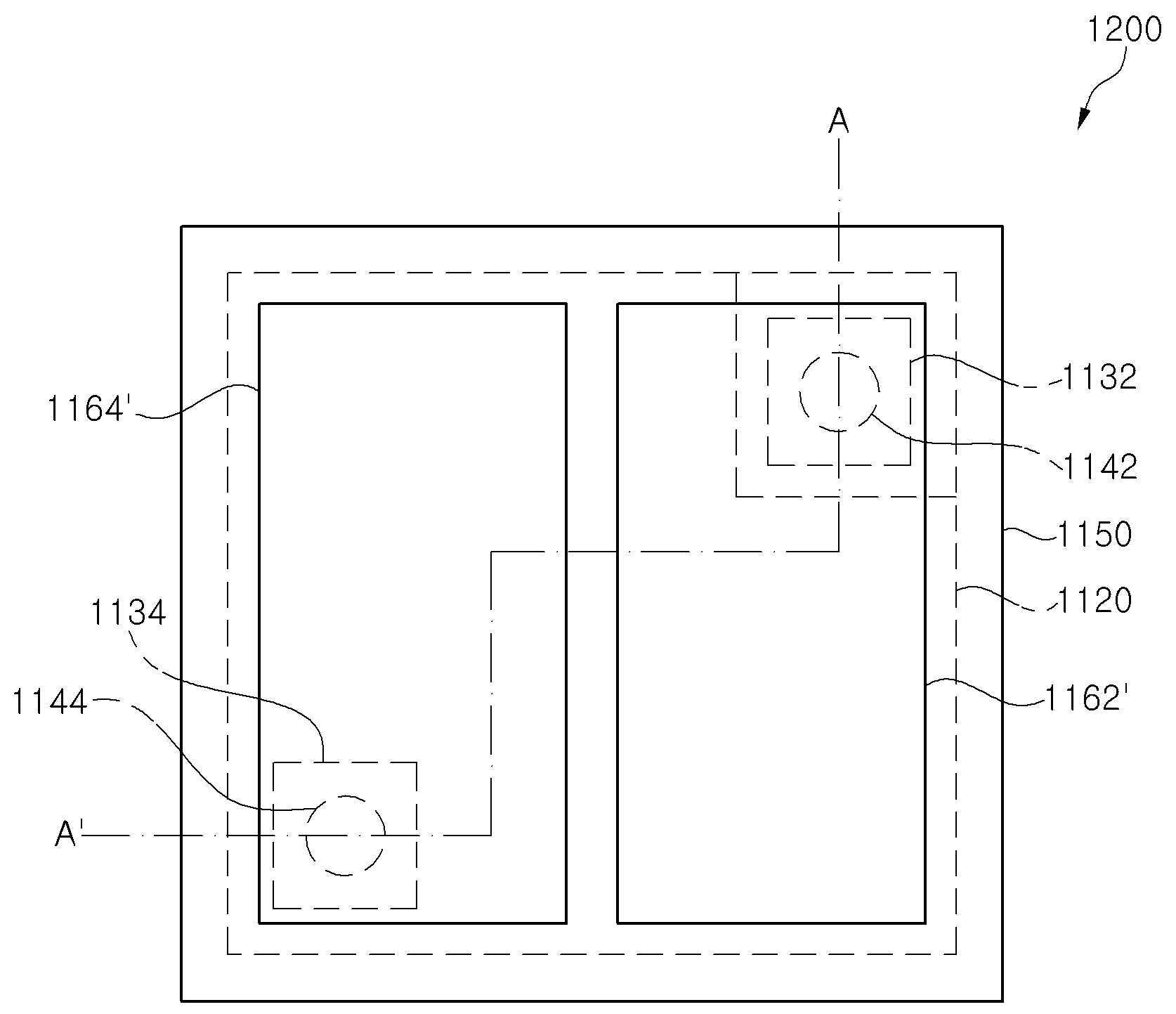

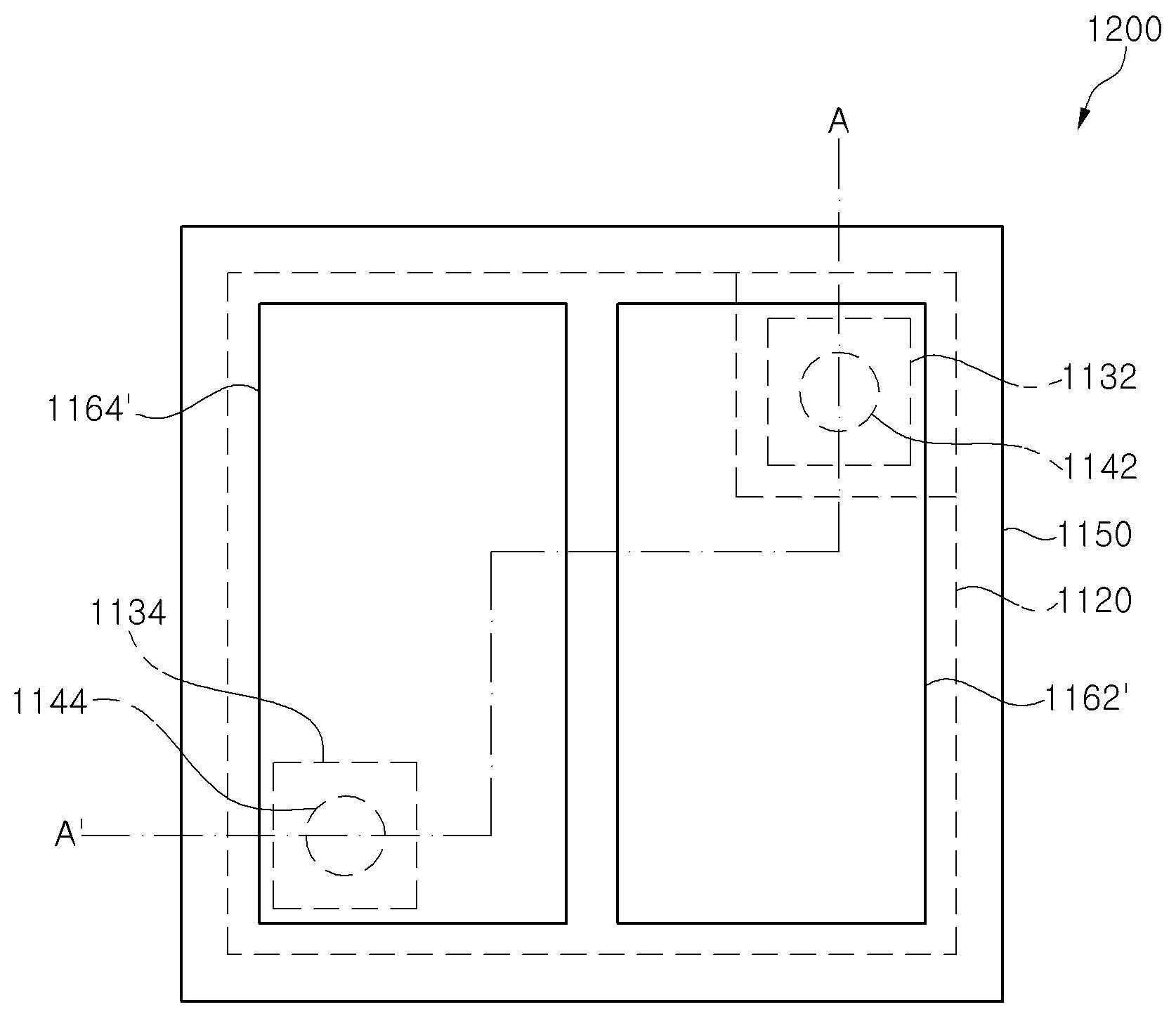

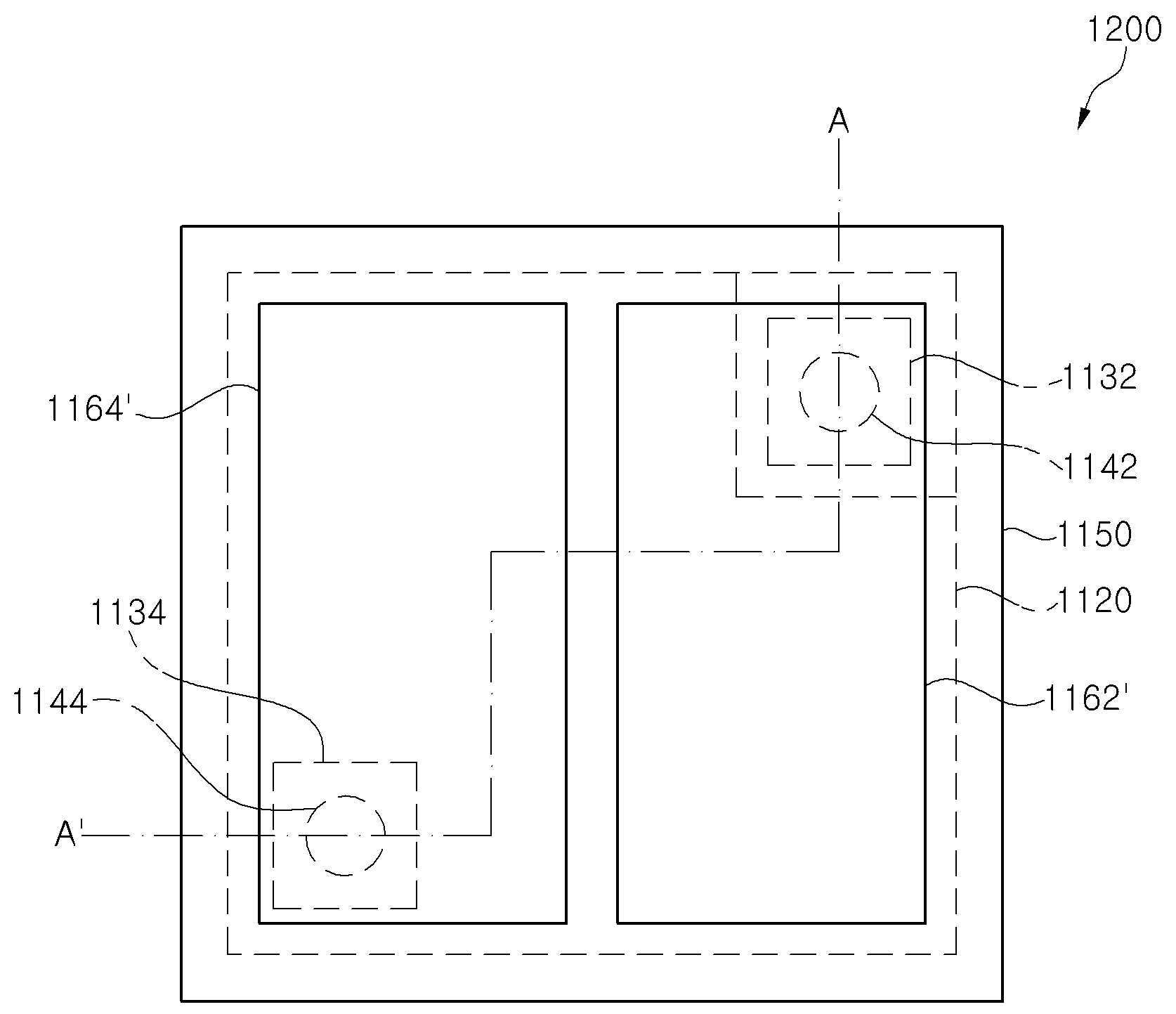

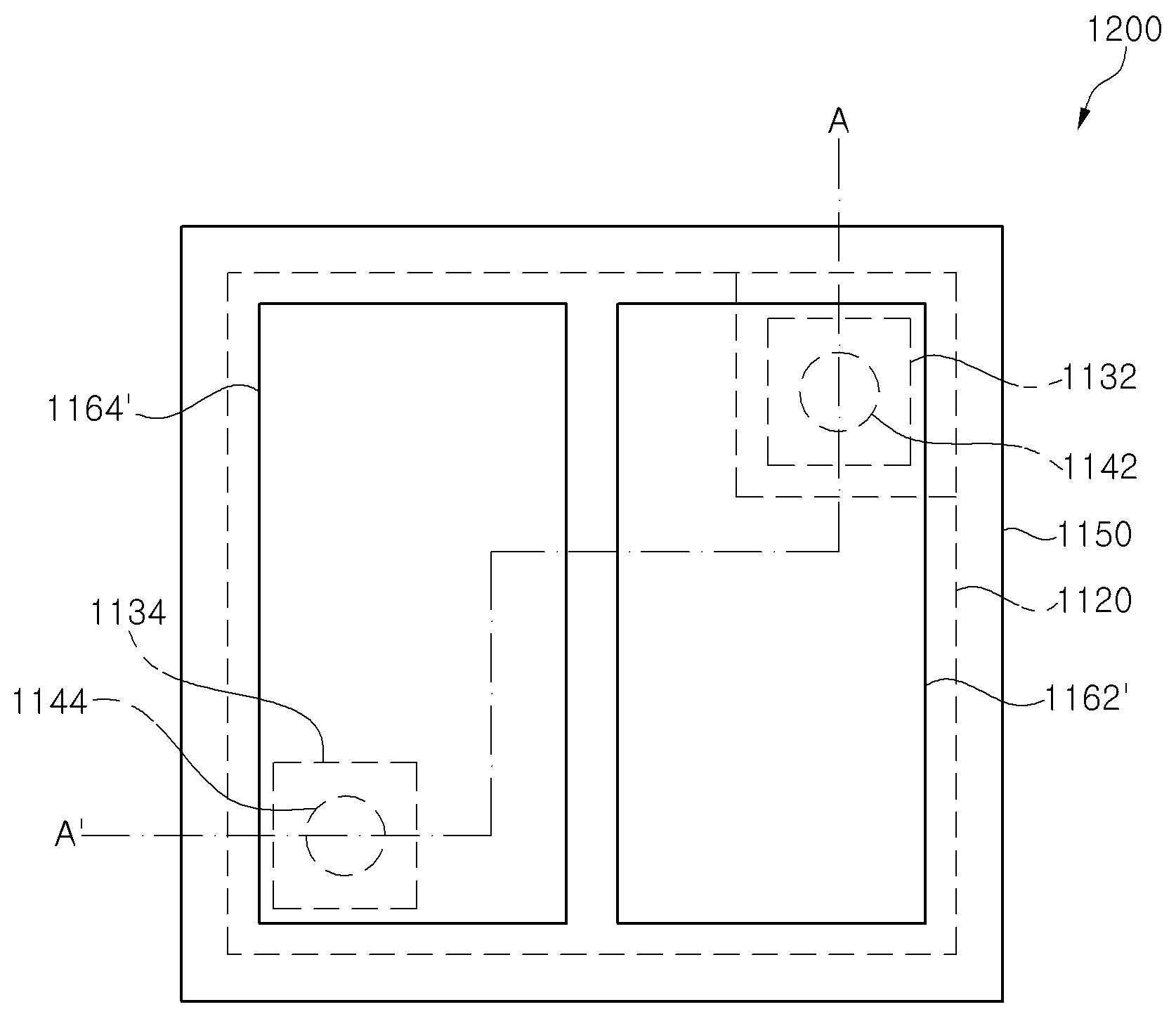

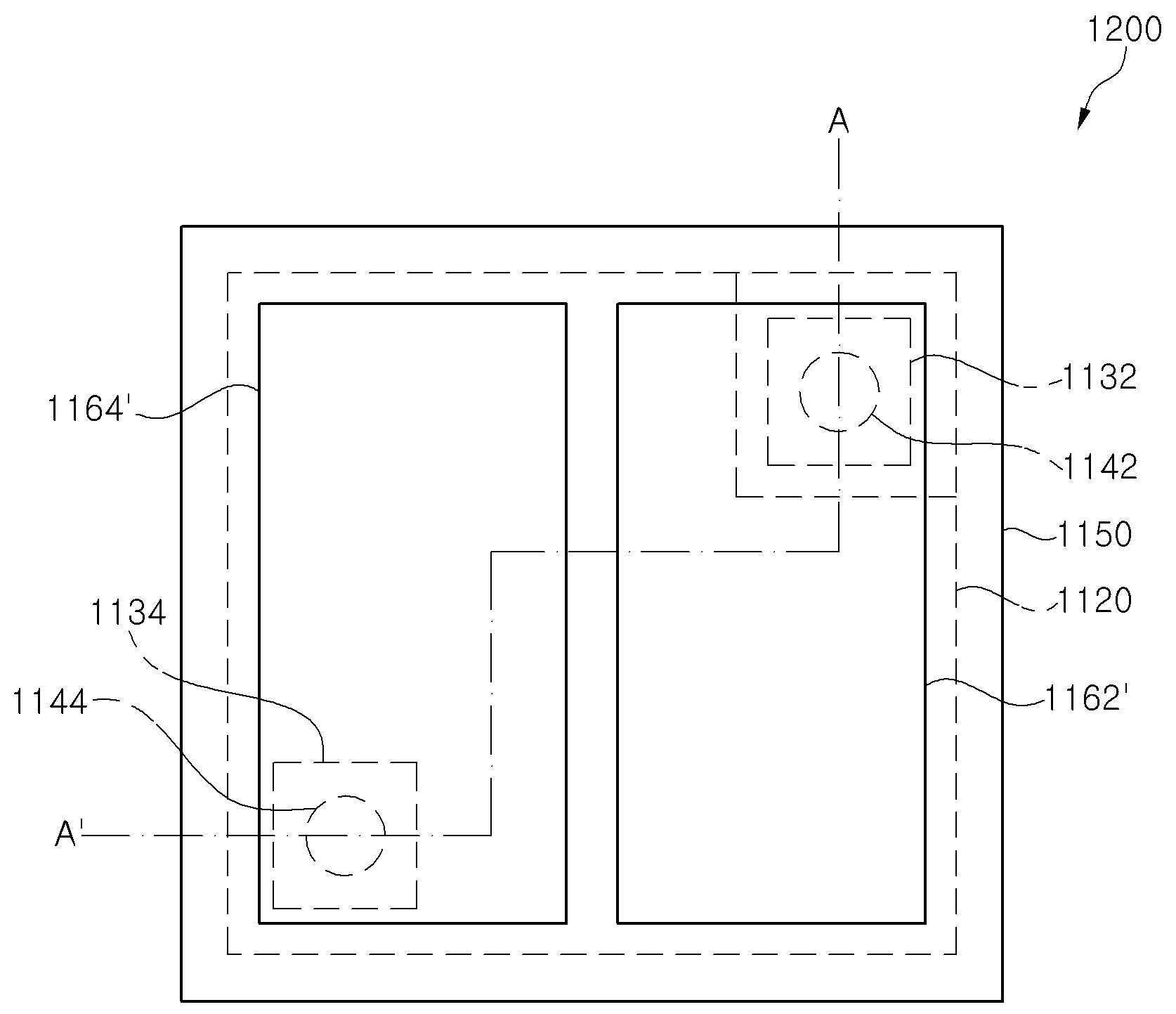

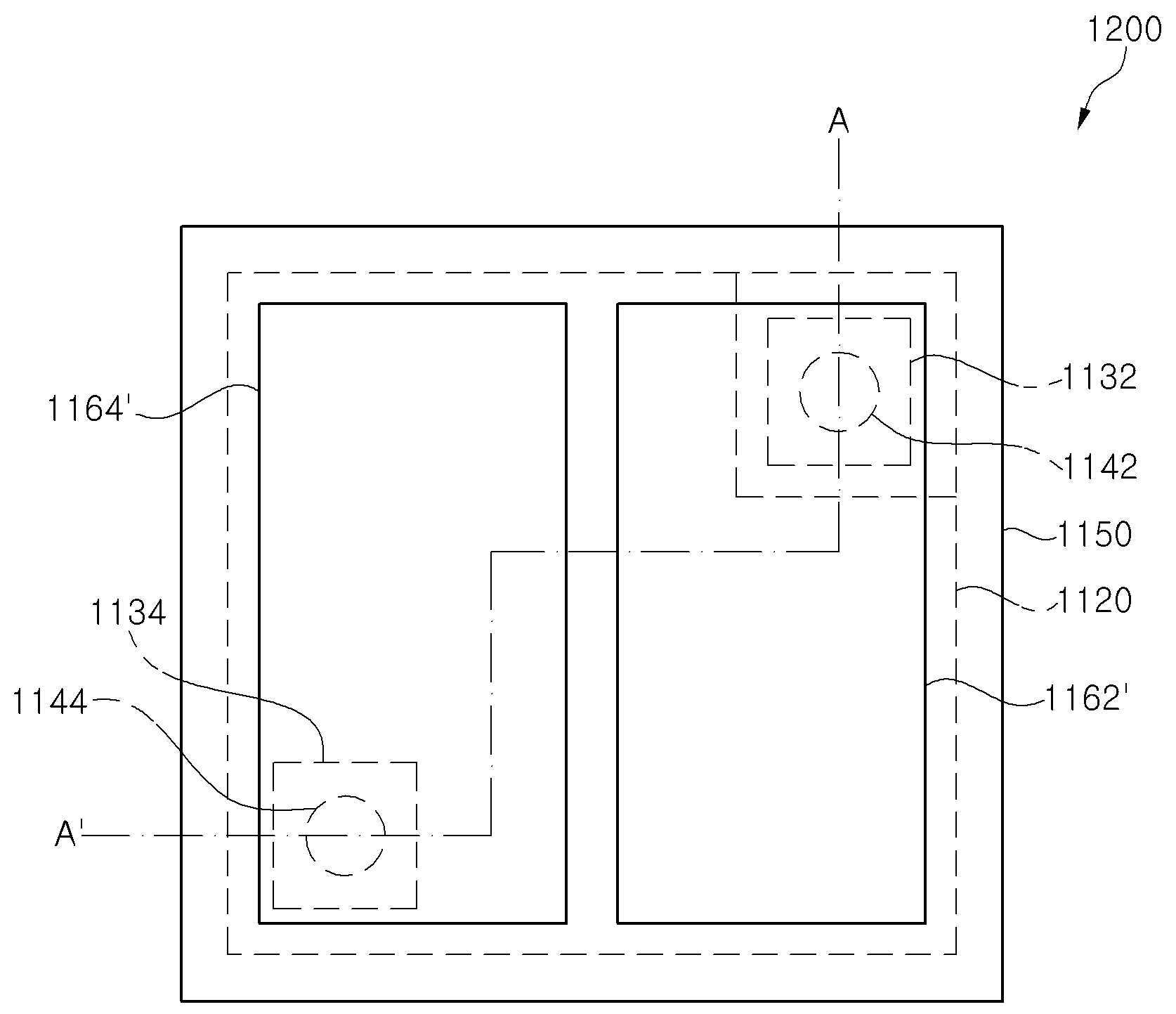

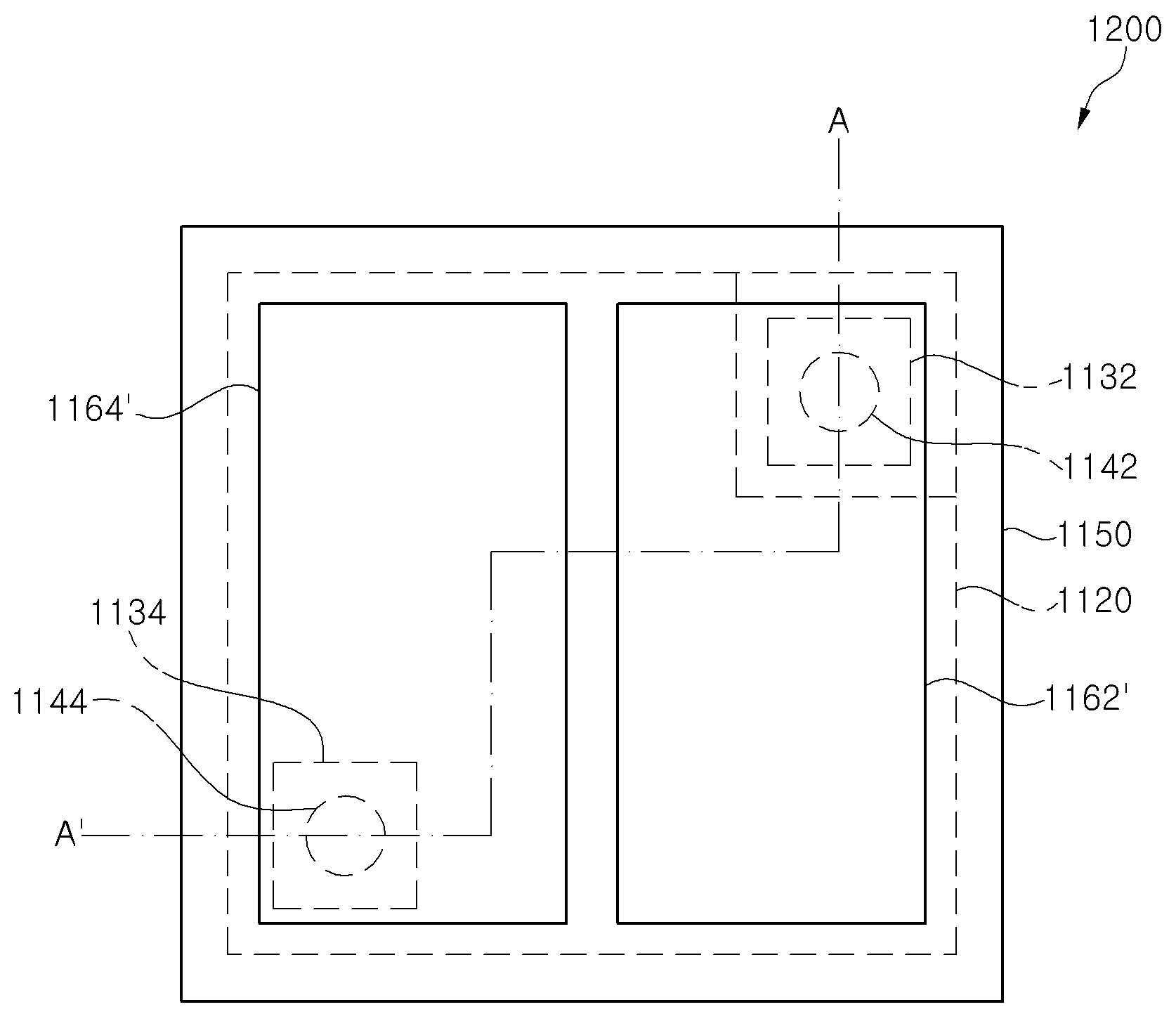

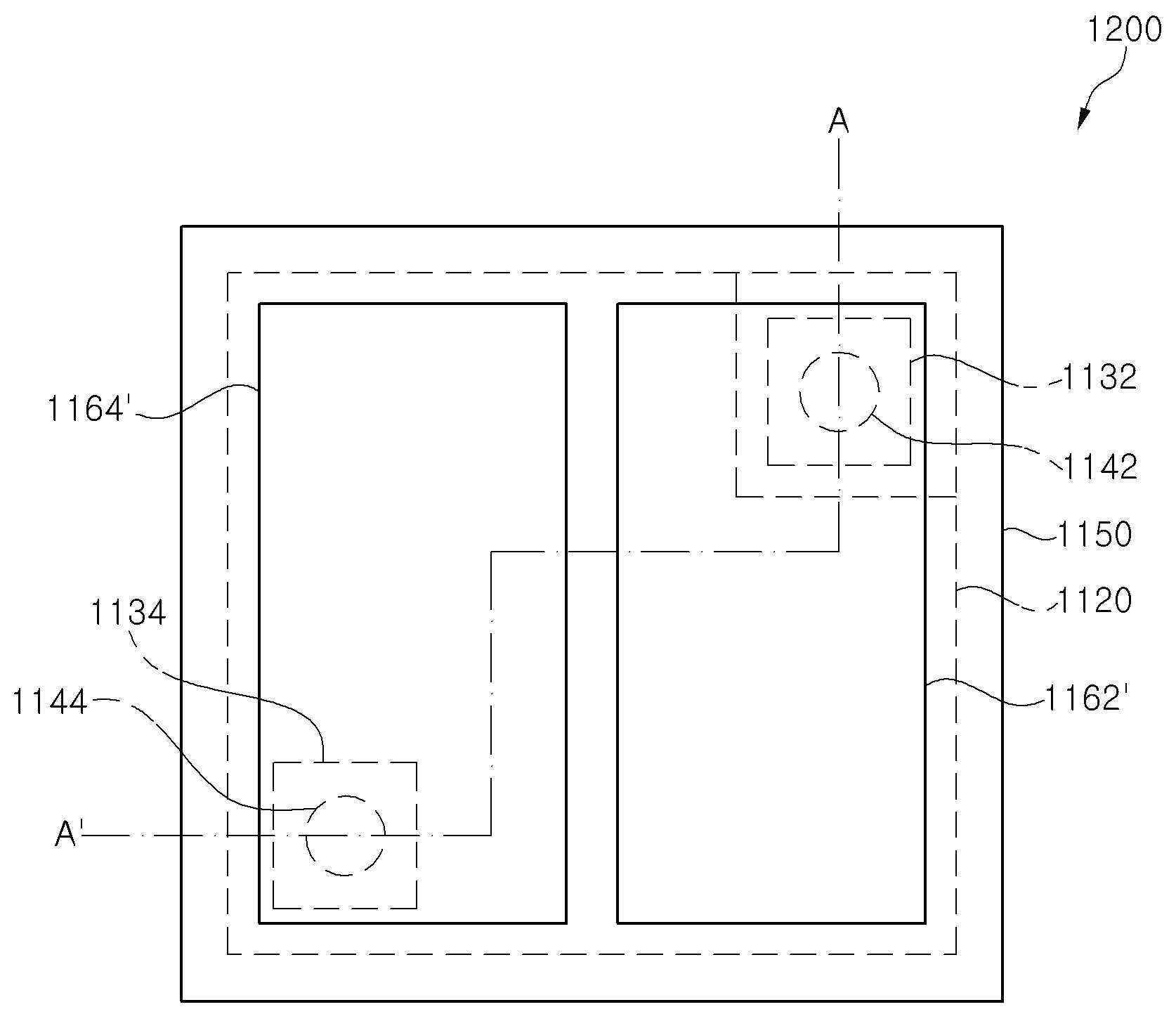

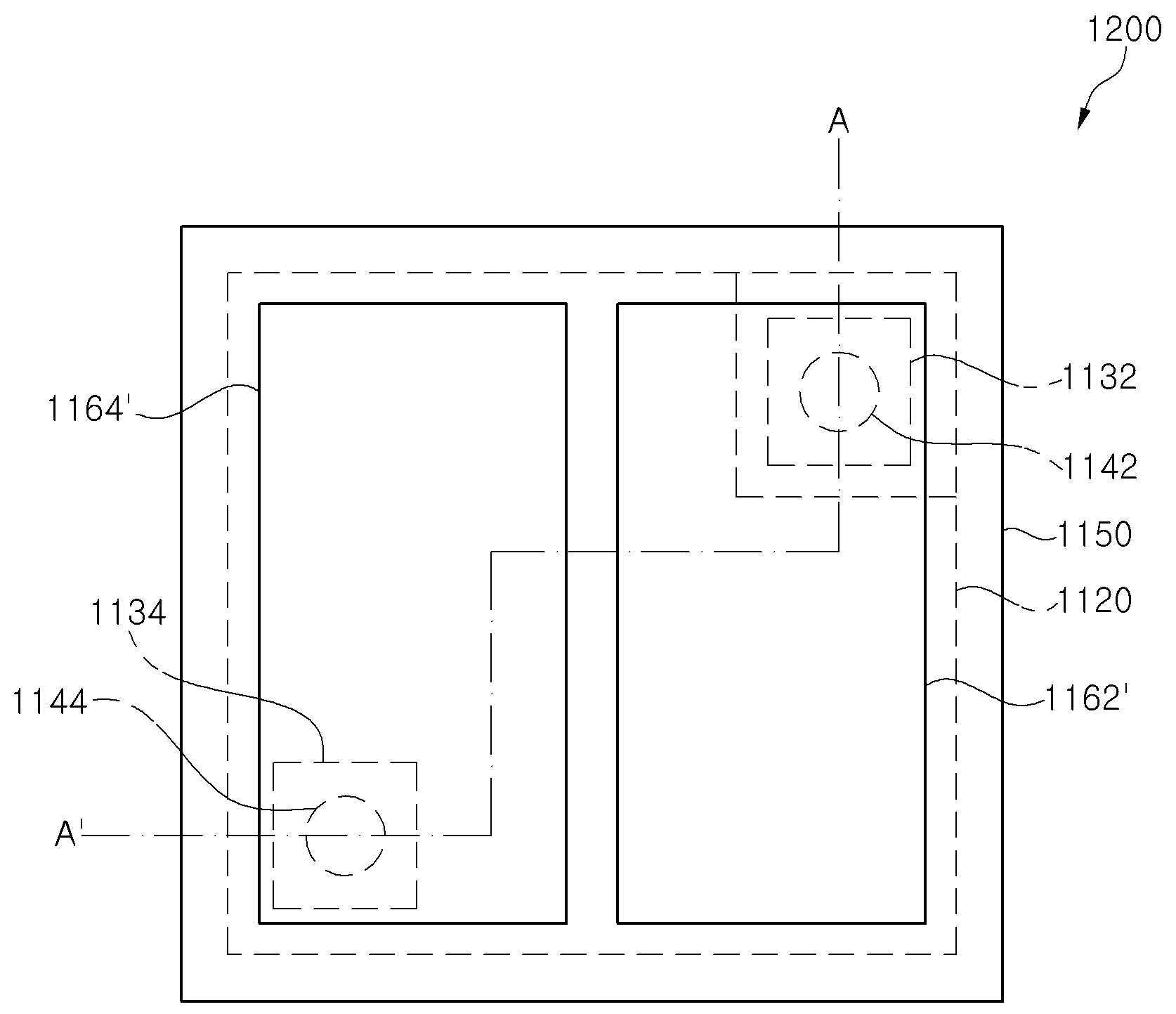

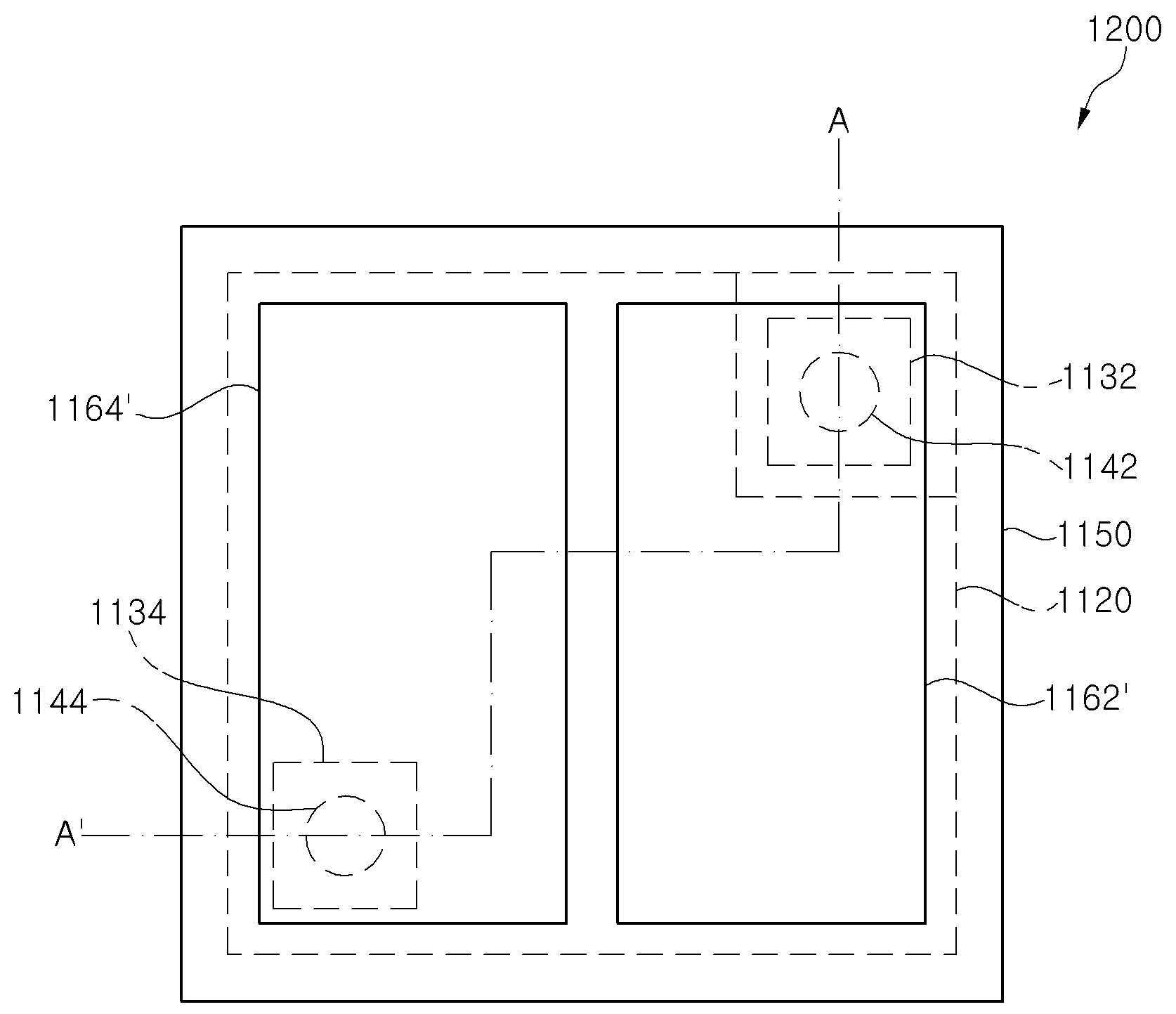

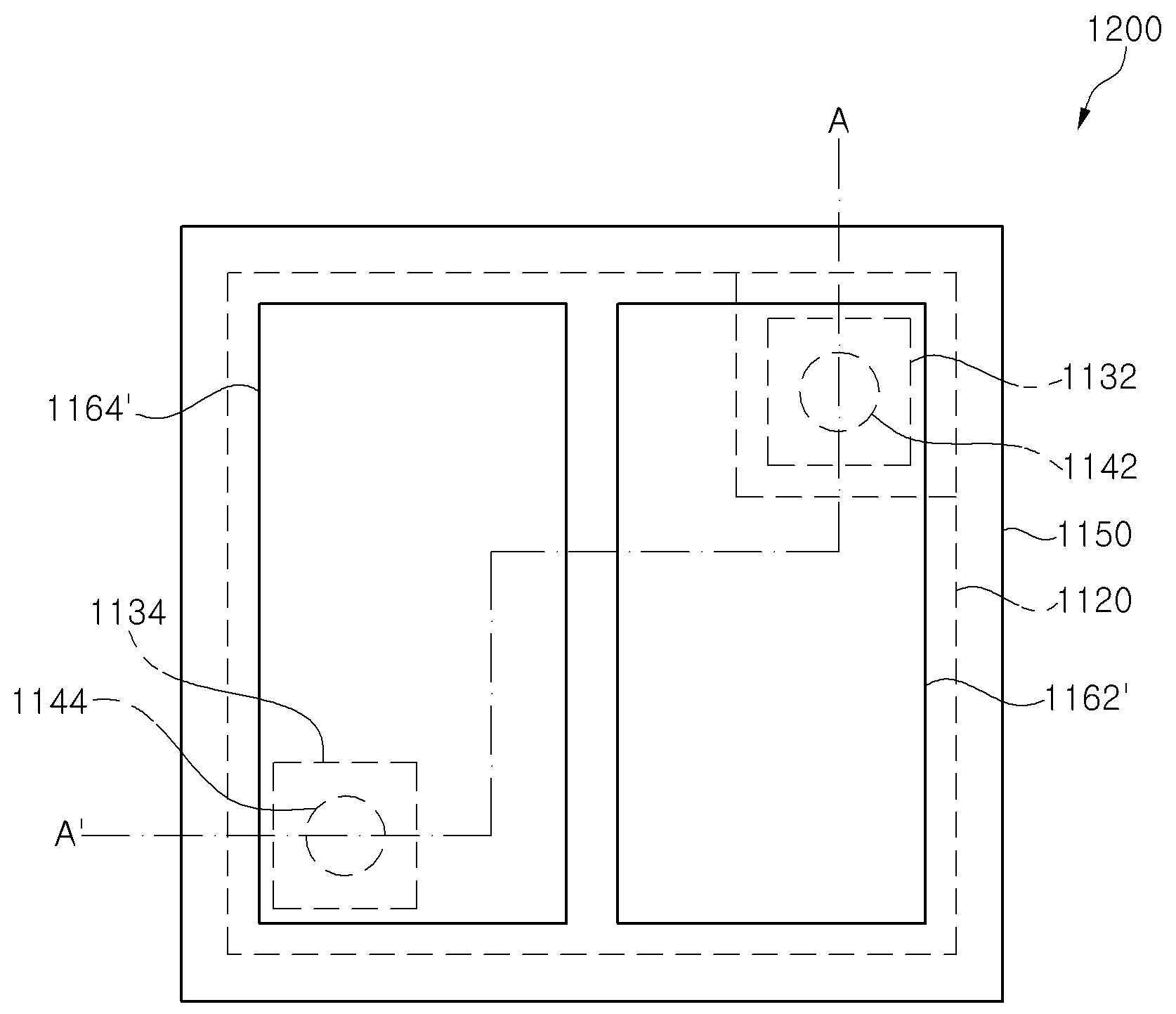

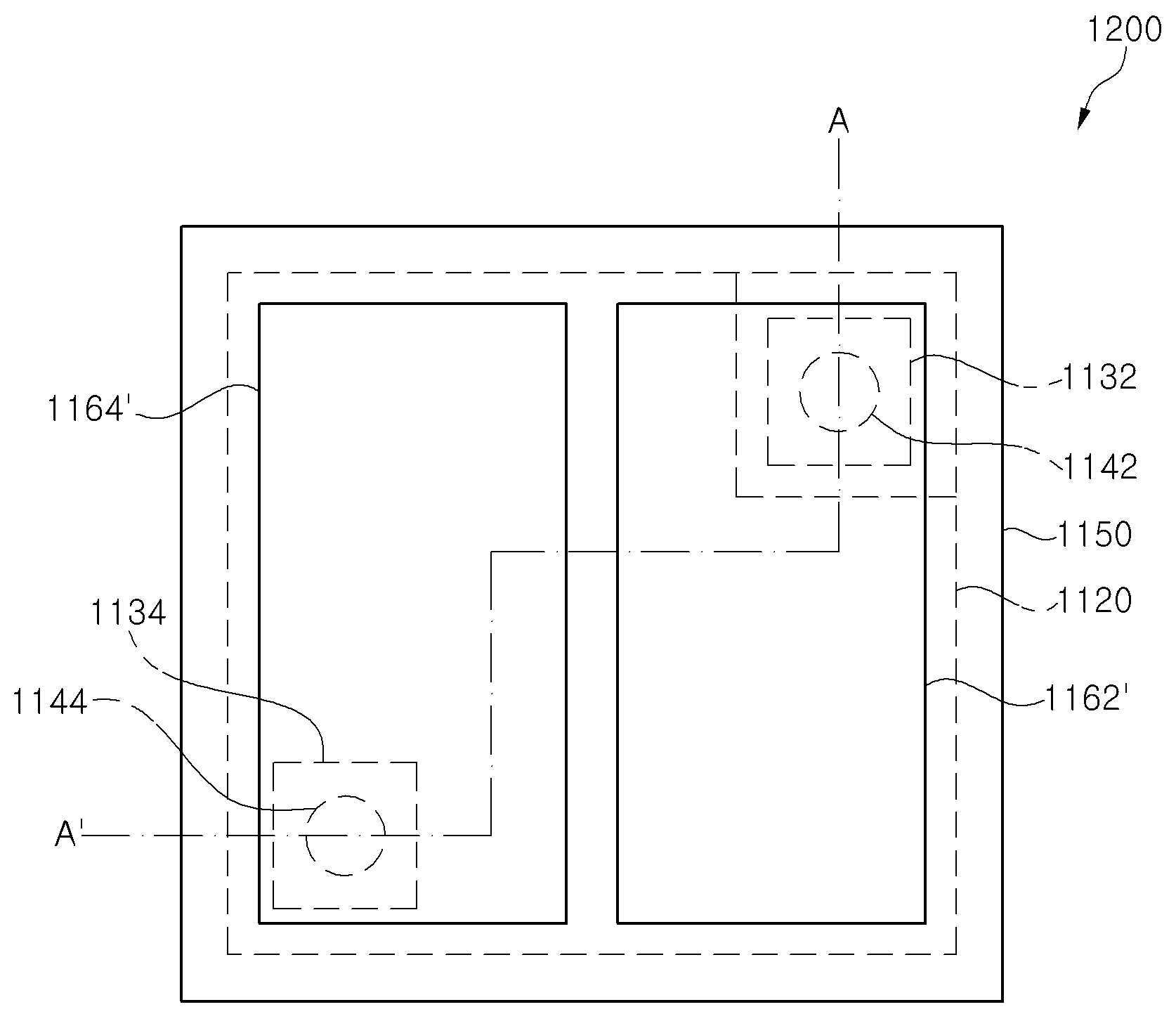

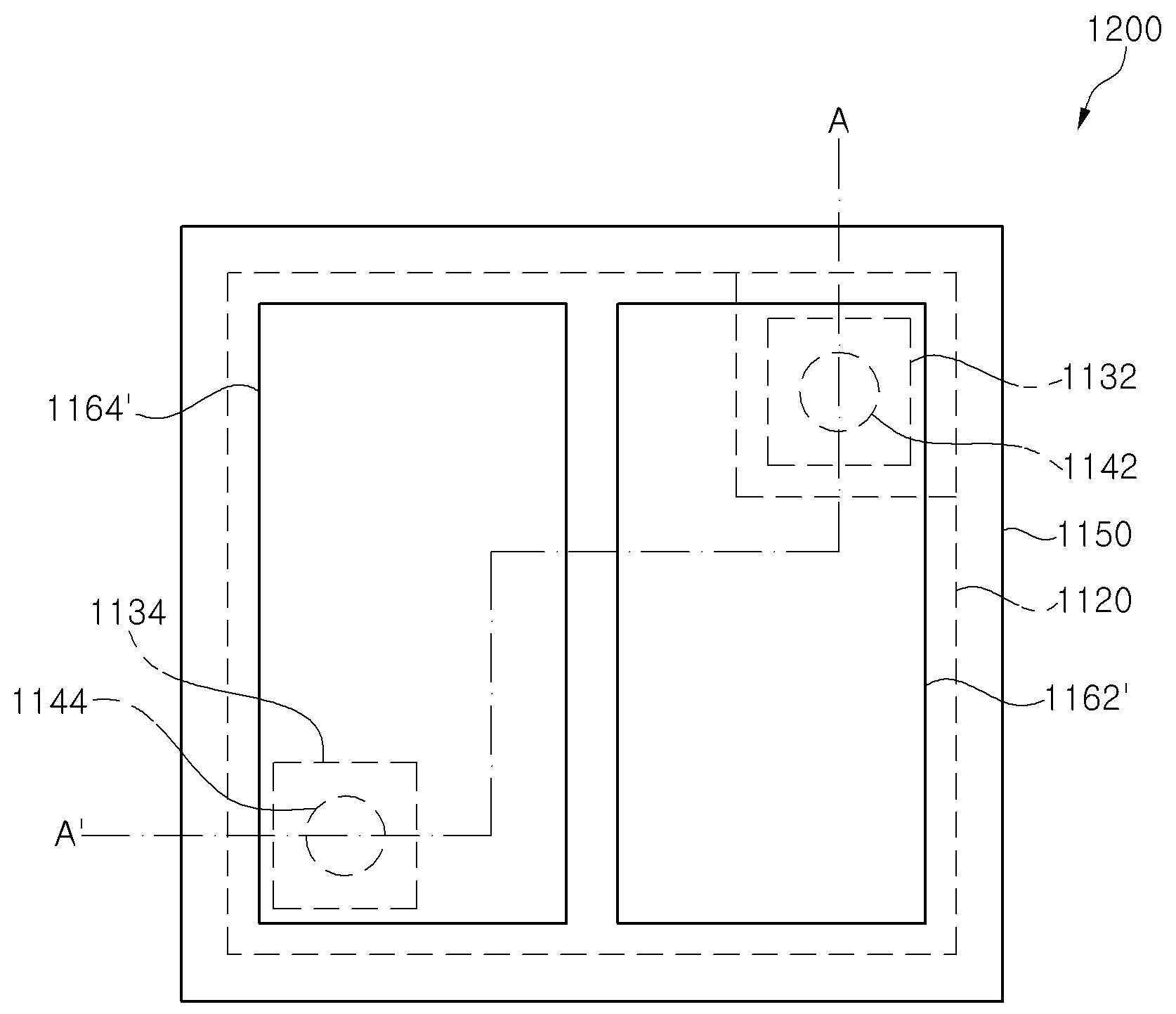

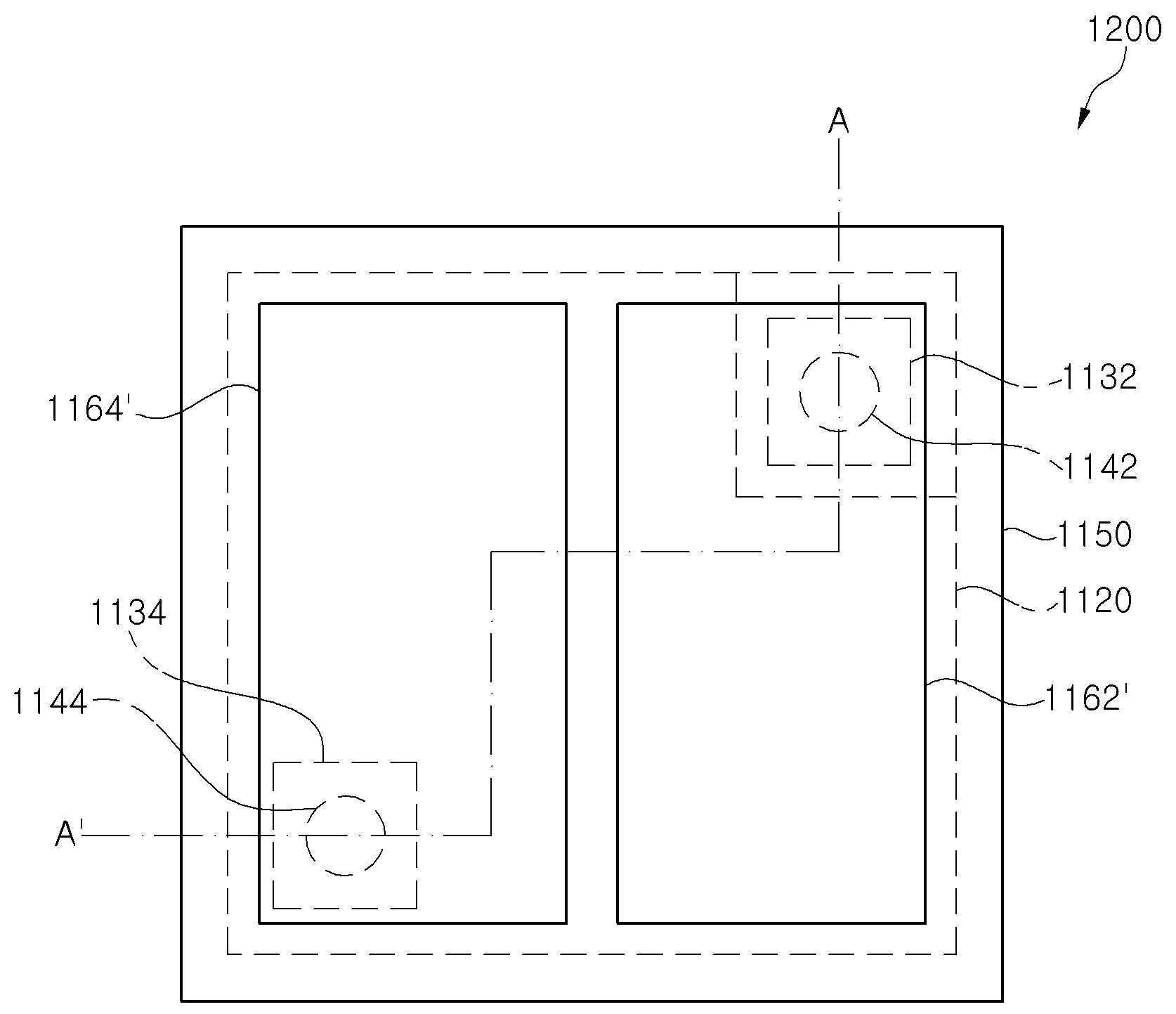

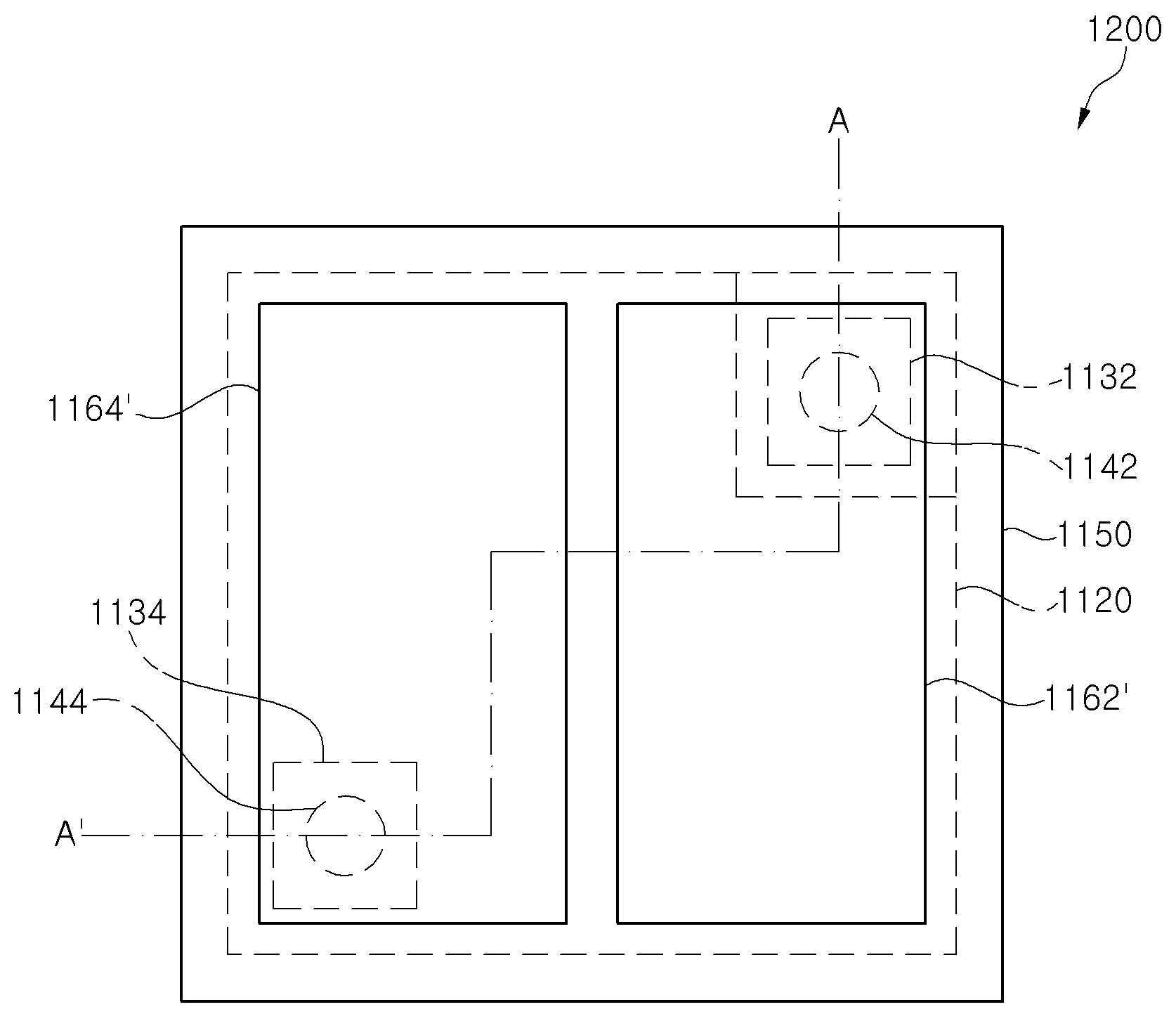

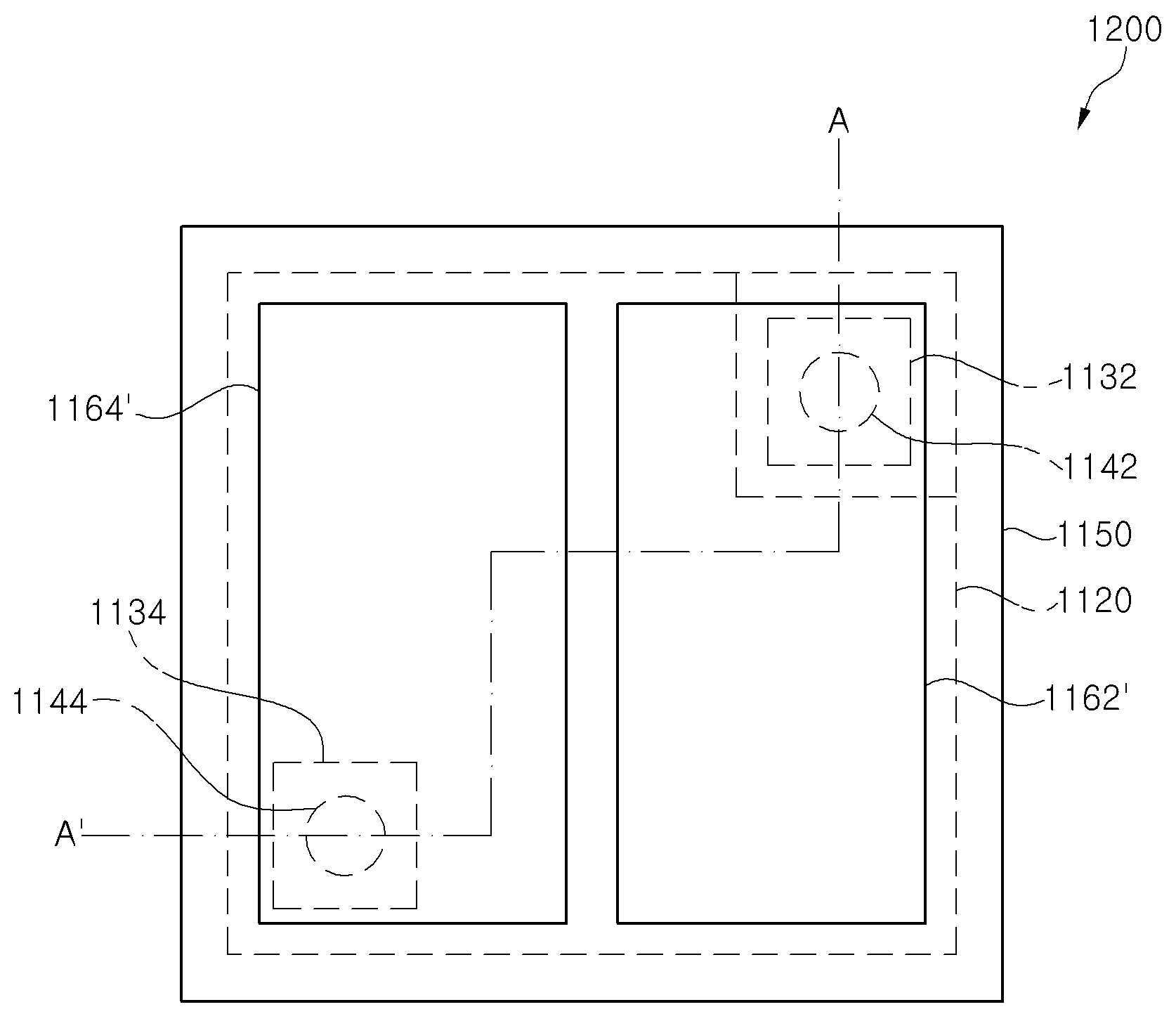

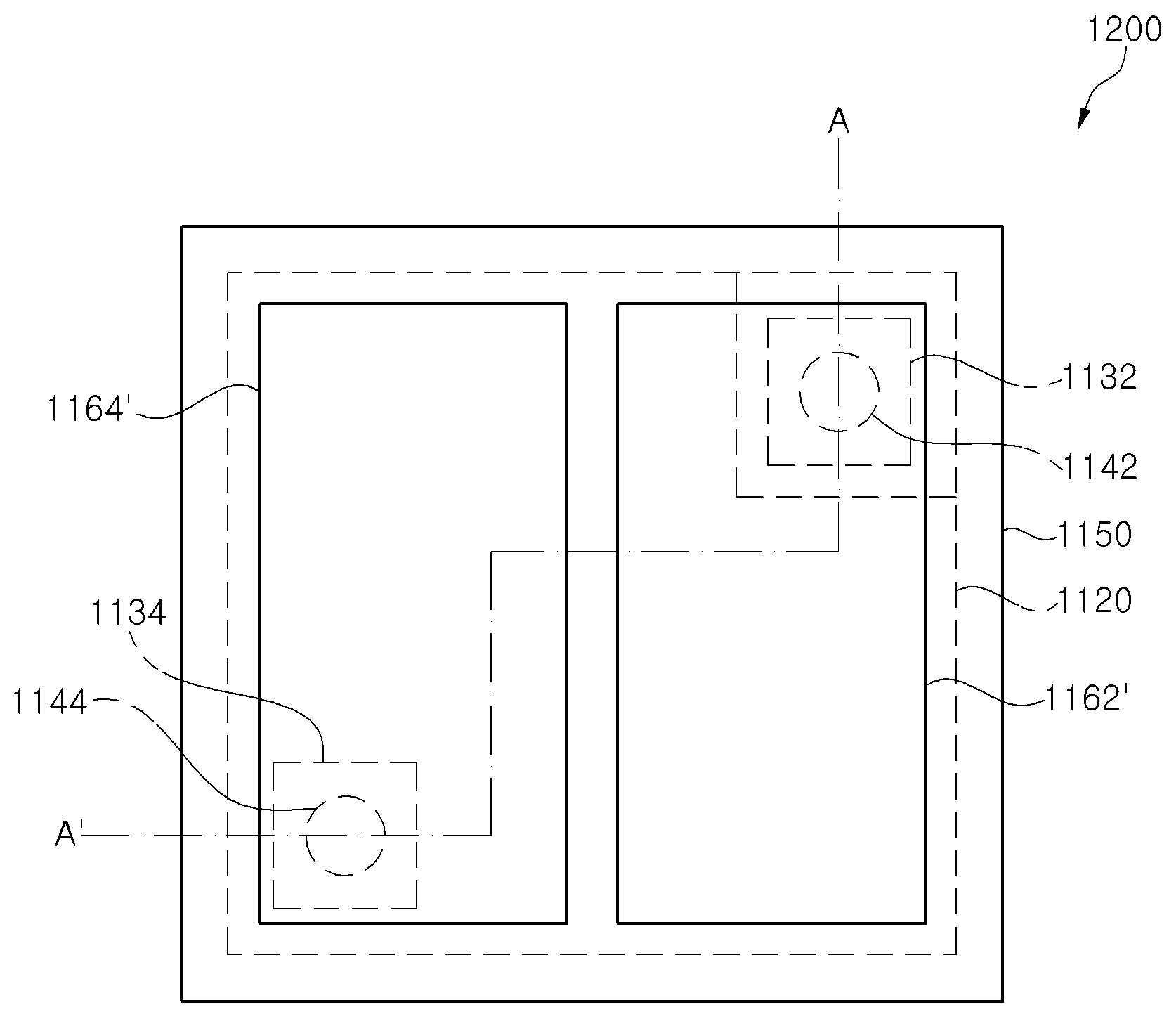

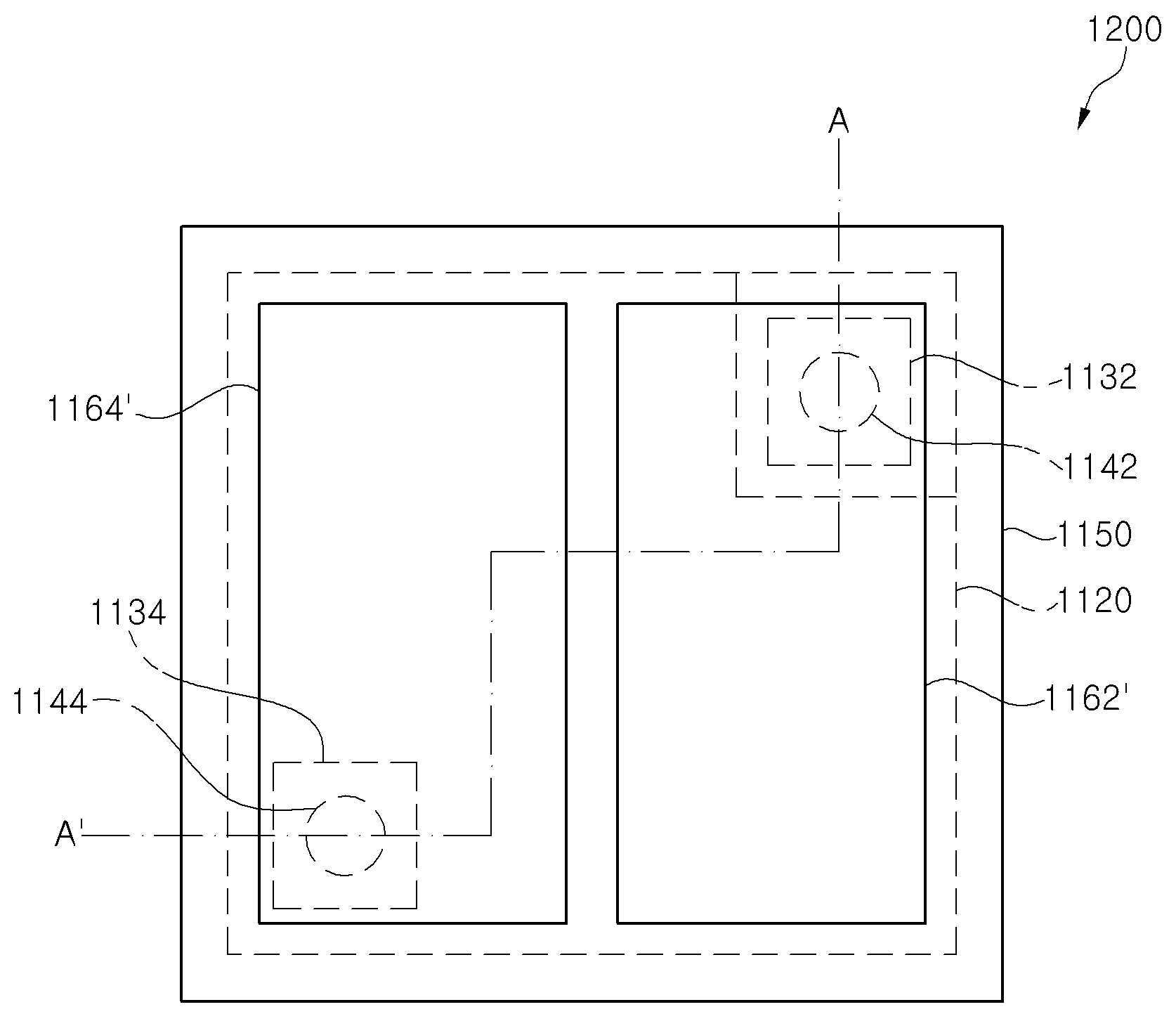

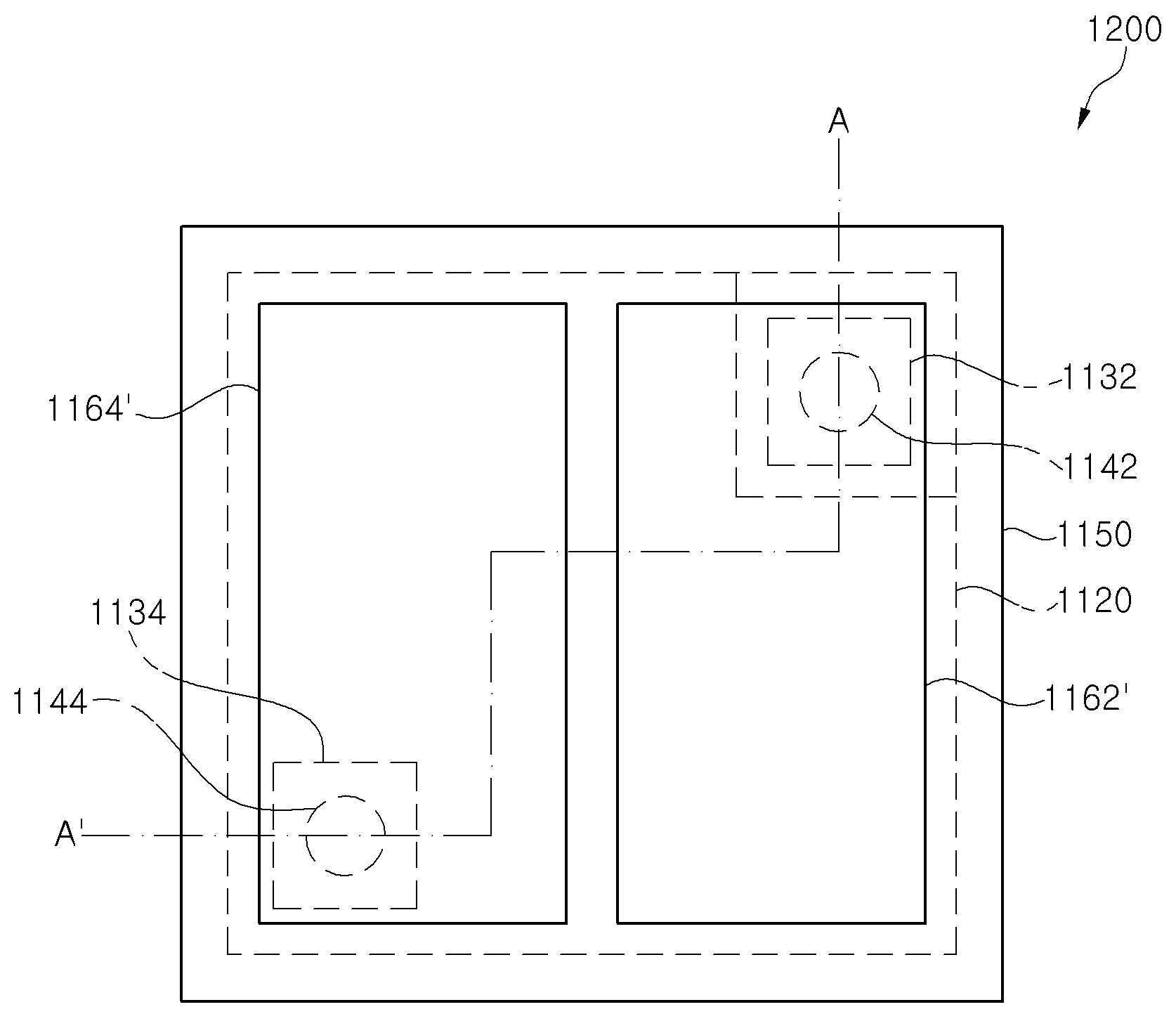

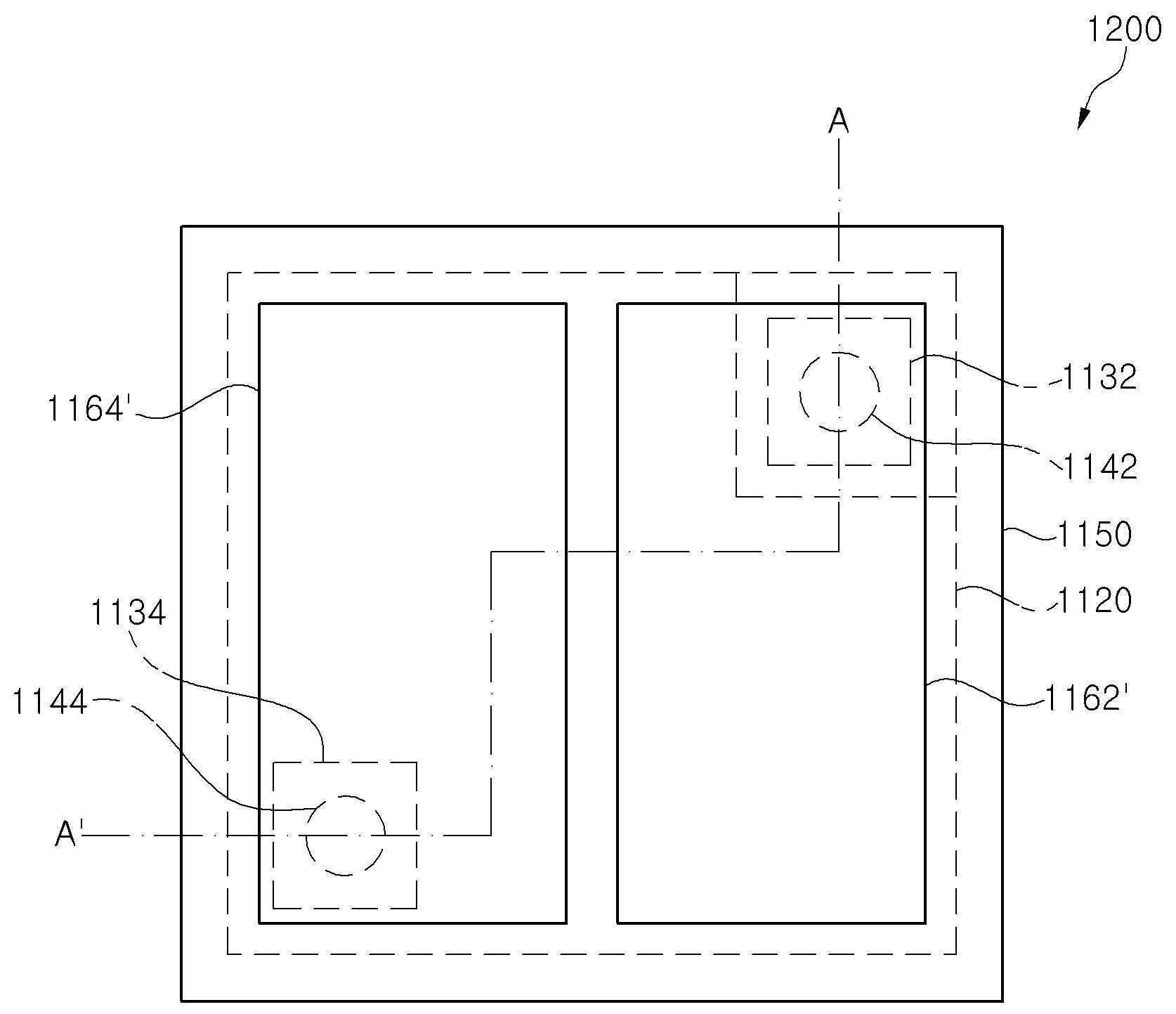

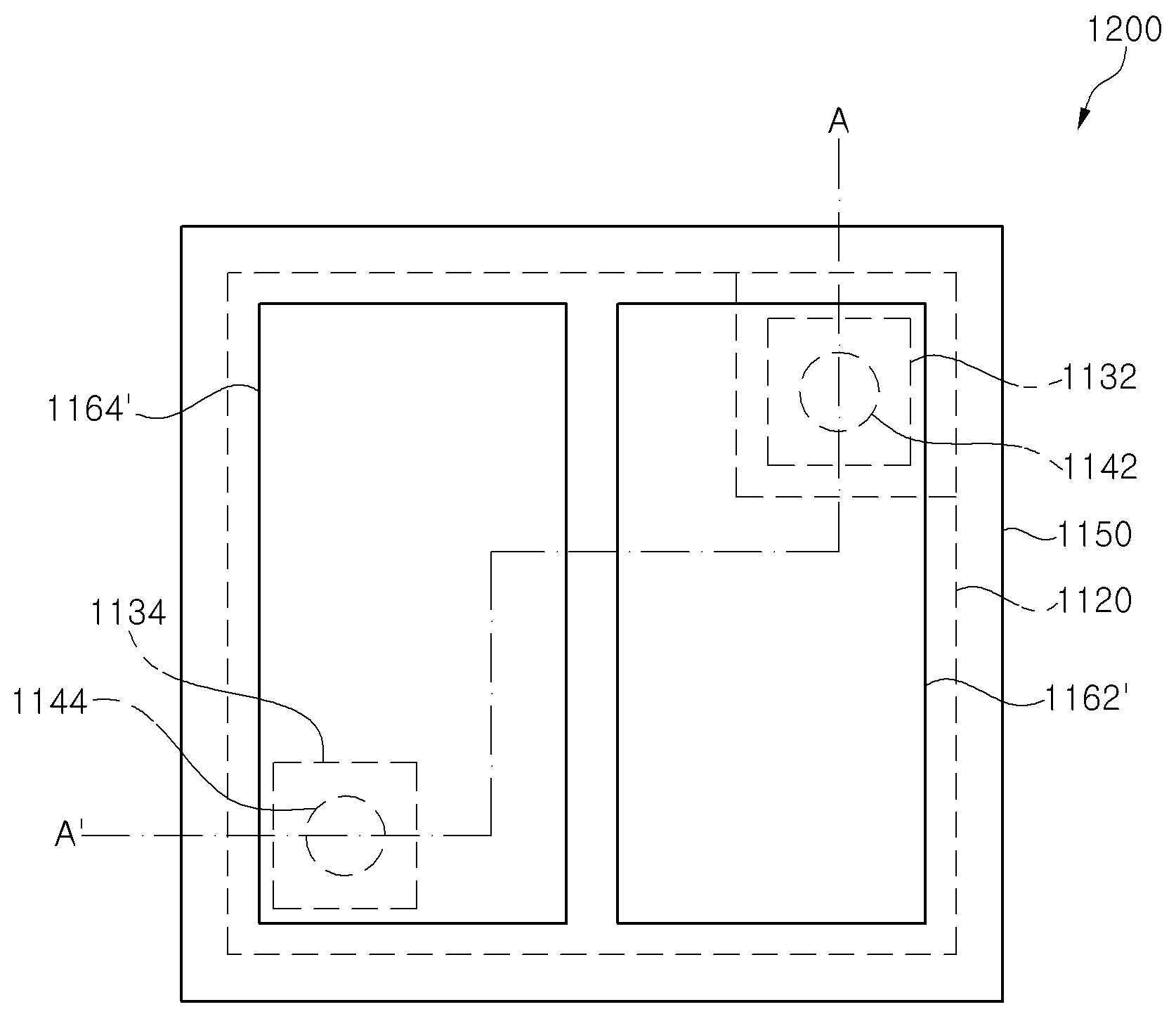

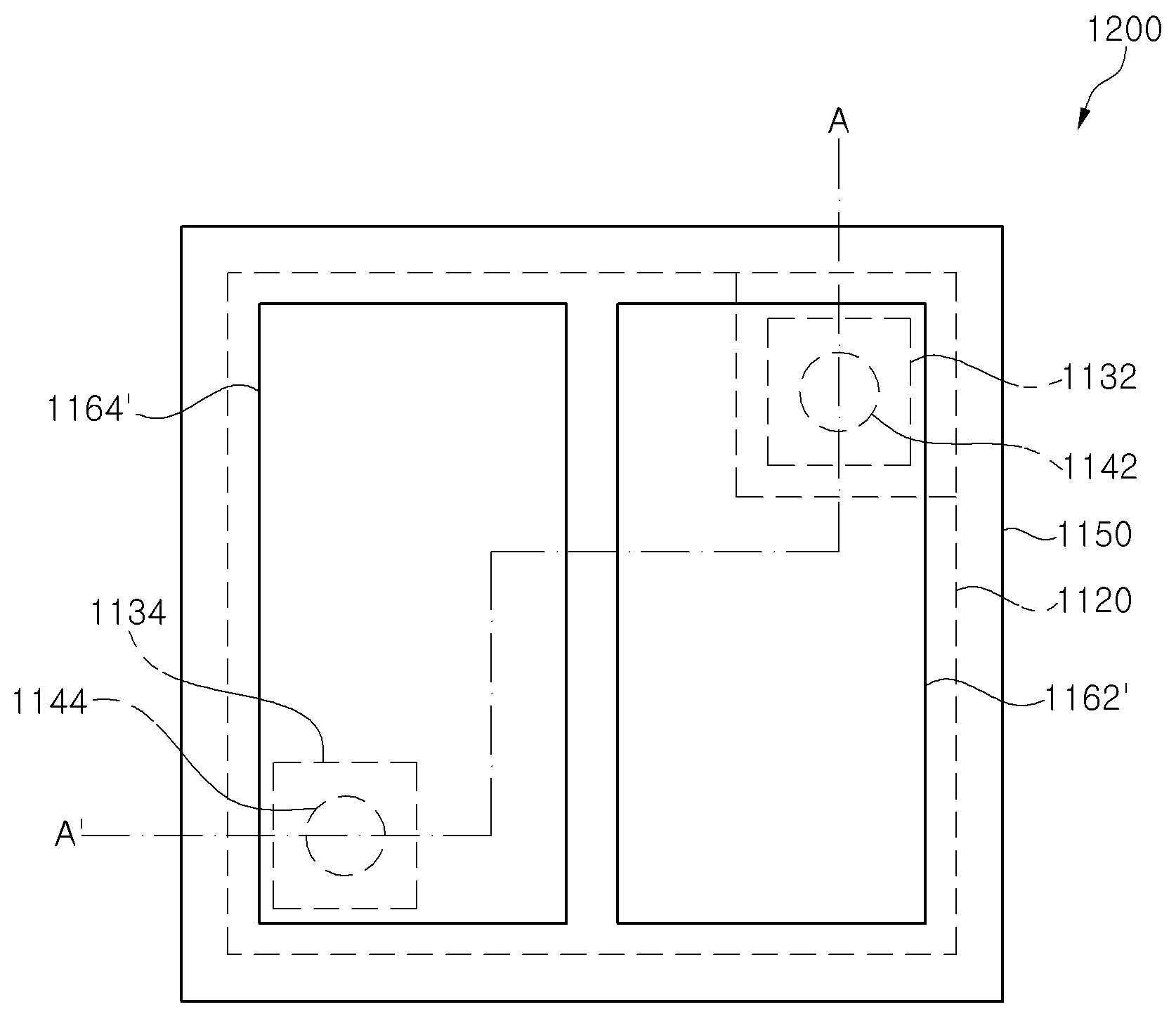

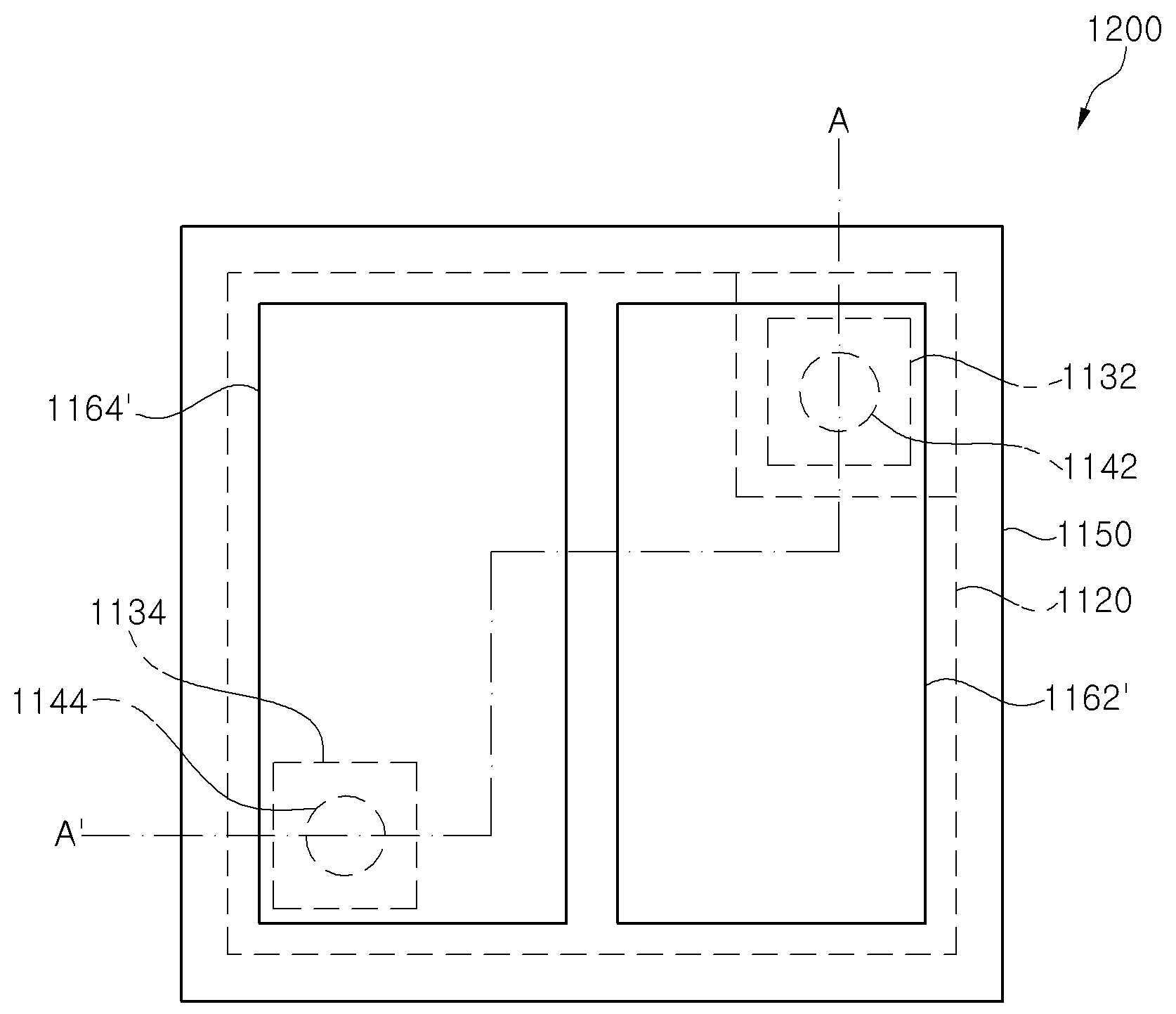

LIGHT EMITTING DIODE PACKAGE