Устройство для кодирования и декодирования дискретной информации

1П5

Изобретение относится к вычислительной технике и технике связки и можат быть использовано в системах

передачи дискретной информации. Известно устройство для кодирования и декодиррвания сигналов в системах

передачи цифрових данных, содержащее в передающей части входной регистр , блок сравнения посьшок, кодер

и хронизатор, а в приемной части формирователь импульсов, блок определения временного положения, декодер

и формирователь тактовых импульсов Ц Недостатком известного устройства

является затрата дополнительного времени на передачу избыточных элементов кода, позволяющих обнаруживать

ошибки, т.е. ухудшение пропускной способности. Наиболее близким к изобретению является

устройство для кодирования и декодирования дискретной информации,

содержащее в передающей преобразователь кода, состоящий из шифраторов , распределителд-накопителя и

блока кодирования, входы которого соед1шены с входами устройства, а выходы

подключены к соответствующим входам преобразователя кода, выходы которого соединены с соответствующими

информационными входами распредели .теля-накопителя, тактЬвьш вход которого соединен с тактовой шиной, а

выход подключен к выходу передающей части, а также генератор эталонного

кода, блоки сумматоров по модулю два синхронизатор и блок считывания, а в

приемной части дешифратор, а также генератор эталонного кода , блоки сумматоров

по модулю два, cинxpoн rзaтop корректоры, инверторы, элементы задержки , элементы И и ИЛИ 2 .

Однако для данного устройства ха рактерно недостаточно эффективное использование канала связи вследствие

того, что дополнительные символы, поз воляющие обнаружить ошибку при передаче

, следуют за информационными символами во время перэдачи кодового сло

ва, снижая тем самым пропускную способность канала при заданных потерях достоверности.

Цель изобретения - снижение потерь пропускной способности. Поставленная цель достигается тем

что в устройство для кодирования и декодирования дискретной информации,

содержащее в передающей части преобра 6 2

зователь кода, состоящий из двух шифраторов , распределитель-накопитель и

блок кодироваЯия входы которого соединены с входами устройства, а выходьт

подключены к соответствующим входаг- шифраторов преобразователя кода, выходы

которых соединены с соответствующими информационными входами распределителя-накопителя

, тактовый вход которого соединен с первой тактовой шиной , а выход подключен к выходу пере

дающей части, ав приемной части дешифратор , введены в передающую часть.- решающий блок, входы которого

подключены к выходам соответствующих шифраторов преобразователя кода, а

выходы - к дополнительным входам распределителя-накопителя , а в приемную

часть - блок обнаружения ошибок, выходной регистр сдвига и распределитель-накопитель

, информационньй и тактовьй входы которого подключены соответственно к входу приемной час

ти и первой тактовой шине, а вьтходы соединены с соответствующими входами

дешифратора, первые, выходы которого подключены к соответствующим входам

выходного регистра сдвига, а вторые выходы - к входам блока обнаружения

ошибки, вькод которого соединен с шиной индикации .ошибкр, тактовый

вход выходного регистра сдвига подключен к второй тактовой шине, а выход

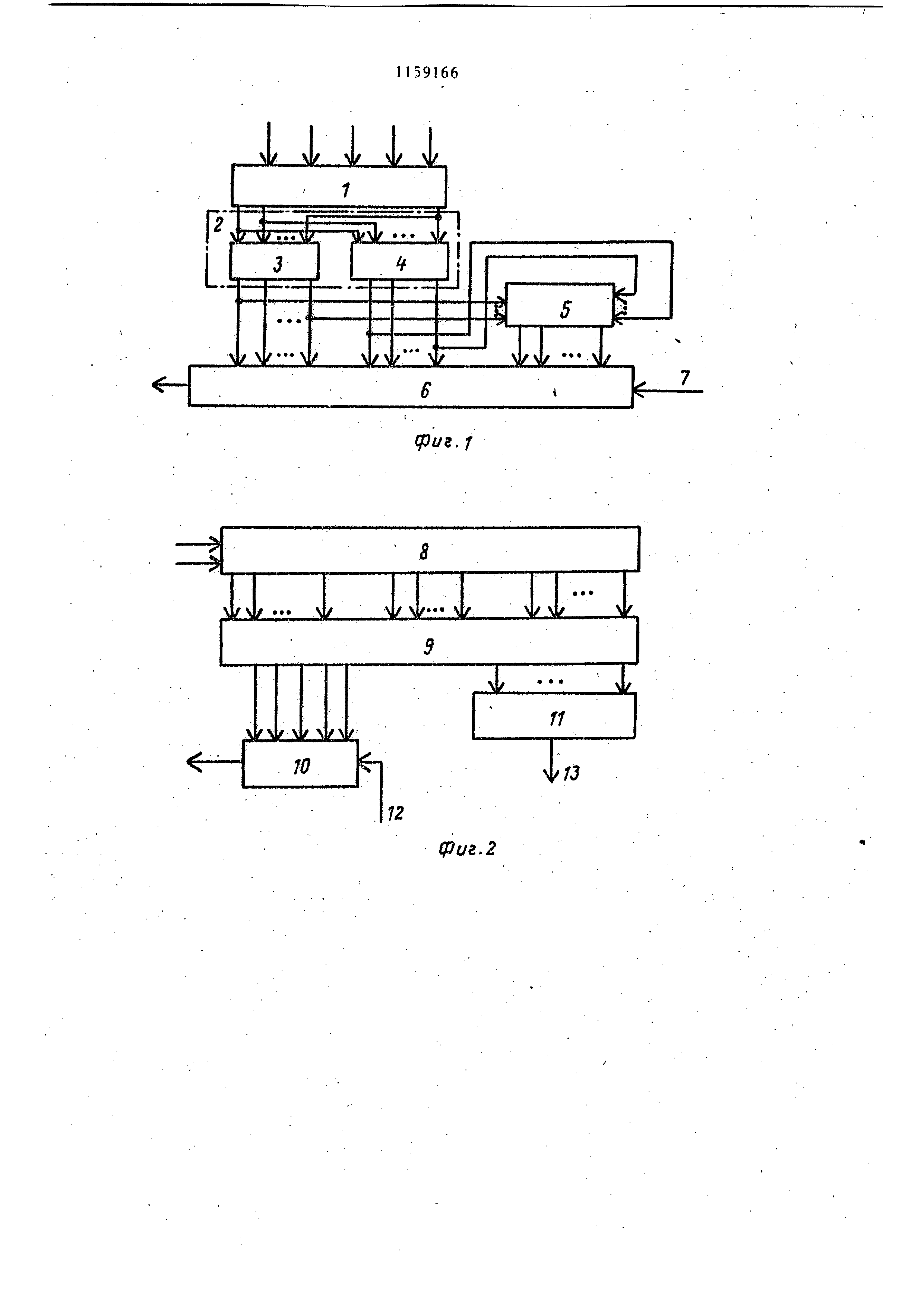

соединен с выходом устройства. На фиг. I показана блок-схёмй передающей части; на фиг, 2 - блоксхема

приемной части;.иа фиг, 3 диаграммы , поясняющие работу устройства .

Передающая, часть (фиг. О содержит блок I кодирования, преобразовател

.ъ 2 кода, состоящий из первого и второго шифраторов 3 и 4, решающий

блок 5, р.аспределитель-накопитель 6, тактовый вход которого подключен

к первой тактовой шине 7, Входы блока 1 кодирования подключены ко входам

устройства, а выходы - к соответствукмцим входам шифраторов 3 и 4 в

преобразователе 2 кода. Выходы первого и второго шифраторов 3 и 4 соединены

соответственно с первыми и вторыми входами решающего блока 5, Выходы шифраторов 3 и 4 и выходы блока

5 подключены к соответствующим информацрюнным входам распределителянакопителя

6, выход которого подключен к выходу передающей части. 3 1.1 Приемная часть (фиг. 2) содержит распределитель-накопитель 8, информационные

н тактовый входы которого соединены со входом приемной части 1 первой тактовой шиной, а. выходы

подключены к соответствующим входам дешифратора 9, первые выходы которого соединены со входами выходного

регистра 10 сдвига, а вторые выходы подключены ко входам блока 11 об наружения ошибки. Вторая тактовая

шина 12 подключена к тактовому входу регистра 10, его выход соединен с выходом устройства. Выход блока

11 подключен к шине 13 индикации 1 ошибки. Блок 1 кодирования служит для представления

исходного пятиэлементного кода МТКг2 в виде многоразрядного (например, трвдцатидвухразрядного) J

числа. В преобразователе 2 кода с помощью шифраторов 3 и 4 импульсы и пауузы

мезкду ними модулируют по длительности и получают таким образом двухвалентньй

м 1огопозиционньй код, в ко-2 тором информация заложена во временномположении

передних и задних информационньк .фронтов. Первый шифратор 3 формирует первый из двух элементов

1664 многопозиционного кода, второй шифратор

4 второй элемент (i). Дпя обнаружения ошибок в каждую двухэлементную кодовую комбинацию вводится с

решающего блока 5 третий эле ° местоположение вы,бирается из условия

А{Х,- + Ajxj + Ajj.x,j OCracd Л,) (1) гдеАр. А:, Ац, А, - коэффициенты, оп ределяемые параметрами

помех в канале и допустимой вероятностью пропуска

ошибки кодового . символа на приеме; - значения элементов i, j и k в кодовой комбинации .

В таблице представлен один из вариантов построения трехэлементного многопозиционного кода, rge каждый

элемент может принимать шесть значений . УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДИСКРЕТНОЙ ИНФОРМАЦИИ

, содержащее в передающей части преобразователь кода, состоящий из двух шифраторов, расп.ргделитель-накопйтель

и блок кодирования, входы которого соединены с входами устройства , а выходы подключены к соответствующим

входам шифраторов преобразователя кода, выходы которых соединены

с соответствующими информацион ными входами распределитель-накопителя , тактовый вход которого соединен с первой тактовой шиной, а выход подключен к выходуiпередающей части, а в приемной части - дешифратор

, отличающееся тем, что, с целью снижения потерь пропускной способности, в него введены

в передающую часть - решающий блок, входы которого подключены к выходам соответствующих шифраторов преобразователя кода, а выходы - к дополнительным входам распределителя-накопителя

, а в приемную часть блок обнаружения ошибок, выходной регистр сдвига и распределитель-накопитель

, информационньй и тактовый входы которого подключены соответственно к входу приемной части и перW

вой тактовой шине, а выходы соедис

нены с соответствующими входами дешифратора, первые вькоды которого подключены к соответствующим входам выходного регистра сдвига, а вторые выходы - к входам блока обнаружения ошибки, выход

которого соединен с шиной индикации ошибки, тактовый ел вход выходного регистра сдвига подключен к второй тактовой шине, а высо

ход соединен с выходом устройства. Ф Здесь N - номер комбинации кода МТК-2 на выходе блока 1, а значения

х(, XJ, х определяют временное полоокение соответствующего перехода i, j и k..55 Распределитель-накопитель 6 пред .ставляет; собой регистр сдвига, причем

выходы шифраторов 3 и 4 подключены к ячейкам этого регистра таким

образом, чтобы временное расстояние между соседними переходами в формируемам

кодовом слове составляло не менее ТГо , где ТГо - длительност элемента, простого кода (т.е.

Распределитель-накопитель 6 при подаче на его тактовый вход импуль5 сов с частотой F 1/Д, где и - длительность единичного временного интервала

в формируемом трехэлементном многопозиционном коде, работает как праобразователь параллельного кода в

последовательный. Распределитель-накопитель 8 представляет

собой аналогичный регистр сдвига, выполняющий обратное преобразование из последовательного кода

в параллельный. Дешифратор 9 служит для преобразования принятого сигнала обратно в

код МТК-2. Выходной регистр 10 сдвига тактируется импульсами с частотой. Fj

- I/To, Устройство работает следующим образом . Информация пяти элементов исходного простого кода МТК-2 поступает

со входов устройства в блок 1 кодирования , где происходит преобразование

ее в .двоичный код. Последний поступает в преобразователь 2 кода,

где с помощью шифраторов 3 и 4 происходит соответствующая модуляция импульсов и пауз путем записи в соот

ветствующие ячейки распределителянакопителя 6 единицы с соответствующего выхода первого шифратора 3 и

нуля со второго шифратора А. Одновременно с решающего блока 5 в соответствующую

ячейку распределителянакопителя 6 записывается единица. На фиг. 3 показан принцип формирования кодовых слов многопозиционного трехэлементного кода на интервале

стартотопного цикла исходного простого кода МТК-2 для случая, когда

информационньй переход в каждом элементе i, j, k формируемого кода занимает

одну из шести возможных позиций СО,1,2,3,4,5), На фиг. 3 обозначено: а старстопный цикл длительностью

Тц для кода МТК-2 с информационным интервалом 5to ; б г местоположение переходов i, j, k на интервале

TU,; в, г, ид- примеры реализации кодовых слов, е - зоны регистрации характеристических моментов

восстановления на приеме. Количество возможных кодовых слов

равно произведению х,-, х/, х, но из них выбираются лишь те что удов59166 летворяввт условию (1) . При считьшании на выход передающей части поступают посылки длительность о Тц,

в которых импульсы и паузы модулированы по длительности. В приемной части эти посылки записьшаются по Д-входу в распределитель-накопитель 8. Запись происходит

с шагом Д , который выбирают так, 0 чтобы принимаемые переходы , х,

х находились в ,серединеДПо окончании Тц, принятая информация запоминается и проверяется на

дешифраторе 9 на вьшолнение условия 5 (1) В случае невыполнения последнего,

блок I1 обнаружения ошибки формирует в тайне 13 сигнал ошибки. Дешифратор

9 преобразуе т комбинацию переходов Xj, Xj , х„ в соответствующий номер коо

довой комбинации, а затем в исход ный код , Последний с помощью регистра 10

преобразуется из параллельной формы а последовательную. Дешифратор 9

5 содержит также кодопреобразователь, позволяющий получить по номеру кодовой

комбинации исходный ток |УГГК-2. Блок 1I обнаружения ошибок представляет собой многовходоввй элемент

Q ИЛИ, подключенный к тем выходам дешифратора 9, на которых появляется

двоичный номер кодовой комбинации, Непоявление сигнала на выходе блока

11 соответствует сигналу Ошибка. . Поскольку из всех возможных комбинаций:

,х,, Xj-, x выбраны лишь раз решенные, удовлетворяющие условию СП, можно по известным синдромам

ошибок производить исправление ошибок в принимаемых-кодовых комбинациях. и

Таким образом, введение в передающей частр решающего блока, в приемную

часть распределителя-накопителя, выходного регистра сдвига и блока 5 обнаружения ошибок с соответствующими связями позволяет формировать

признаки кодовых слов (для обеспечения возможности обнаружения ошибок)

в интервале слова простого кода-, 0 т.е. без внесения временной избыточности

на передаче. Тем самым обеспечивается снижение потерь пропускной

способности канала при заданных потерях достоверности. ч1/ NJ/ 1/ / / ... / / it10 (puz, 1 /

П фг (риг. 2