Формирователь импульсов

2 9iO О .16 18 О) сл ю

Изобретение может быть использовано

в радиоизмерительной технике. Формирователь содержит элемент И 3, 1 блок 7 задержки, элемент ИЛИ 10, элемент

НЕ 13. В устройство введены элементы И 4, 15 и 16, генератор (г) 5 импульсов, делитель 6 частоты, блок 8 задержки, сумматоры 9 и 11 по модулю два, элемент НЕ 14. Благодаря этому повышается

точность работы и расширяется диапазон длительности формируемых импульсов. Разница между длительностями сформированного импуль са, вызванная несинхронностью работы Г, определяется только периодом (частотой

) выходного сигнала Г 5 и будет тем меньше, чем вьш1е частота Г 5. 3 ил. 12 г 15 17 (Л 11 Изобретение относится к устройствам

, предназначенным для формирования импульсов, соответствующих переднему

и заднему фронтам преобразуемого им- - пульса прямоугольной формы и может

быть использовано в радиоизмерительной технике. Целью изобретения является повышение точности работы и расширение дна-.д

пазона длительности формируемых импульсов . На фиг. 1 показана функциональная

схема формирователя импульсов; на фиг. 2 - временные диаграммы сигна- 15

лов; на фиг, 3 - вариант выполнения делителя частоты. Формирователь импульсов содержит входную шину 1, входную шину 2 обнуления

, первый и второй элементы ИЗ 20 и 4, генератор 5 импульсов, делитель

6 частоты, первый и второй 7 и 8 блоки задержки, первый сумматор 9 по модулю

два, элемент ИЛИ 10, второй сумматор 11, по модулю два, триггер 12, 25

первый и второй элементы ИЛИ 13 и 14, третий и четвертый элементы 15 и 16 И,

первую и вторую выходные шины 17 и 18 первого блока 7 задержки. Выход подключен

к первому входу первого элемен- Q та И 3, выход генератора 5 импульсов

подключен к первому входу второго элемента И 4, выход которого через делитель

6 частоты подключен к входу первого блока 7 задержки, выход второго блока 8 задержки соединен с входом

первого элемента НЕ 13 и с первым входом первого сумматора 9 по модулю два,

выход которого п одключен к входу установки в единичное состояние триггера

12 и к входу второго элемента НЕ 14, / выход триггера 12 соединен с вторьгм

входом второго элемента И 4 и с первым входом третьего 15 и четвертого .

16 элементов И, выход первого блока 7 задержки соединен с первым входом вто

рого сумматора 11 по модулю два, вы ход делителя 6 частоты подключен к

второму входу второго сумматора 11 по модулю два, выход которого соединен

с вторым входом первого элемента 50 И 3, выход которого подключен к первому

входу элемента ИЛИ 10, выход которого подключен к входу установки в нулевое состояние триггера 12, вход

второго блока 8 задержки соединен с 55 входной шиной 1 формирователя импульсов

и вторым входом первого сумматора 9 по модулю два, выход второго блока 45 0 5 5 8 задержки подключен к второму входу третьего элемента И 15, выходы первого

1 3 и втрого 14 элементов НЕ подключены соответственно к второму и третьему входам четвертого элемента

И 16, вход установки в нулевое состояние делителя 6 частоты соединен с вторым входом элемента ИЛИ 10 и с

входной шиной 2 установки в нулевое состояние формирователя импульсов,

выходы третьего 15 и четвертого 16 элементов И соединены соответственно

с первой 17 и второй 18 выходными шинами формирователя импульсов, выход второго элемента НЕ 14 соединен

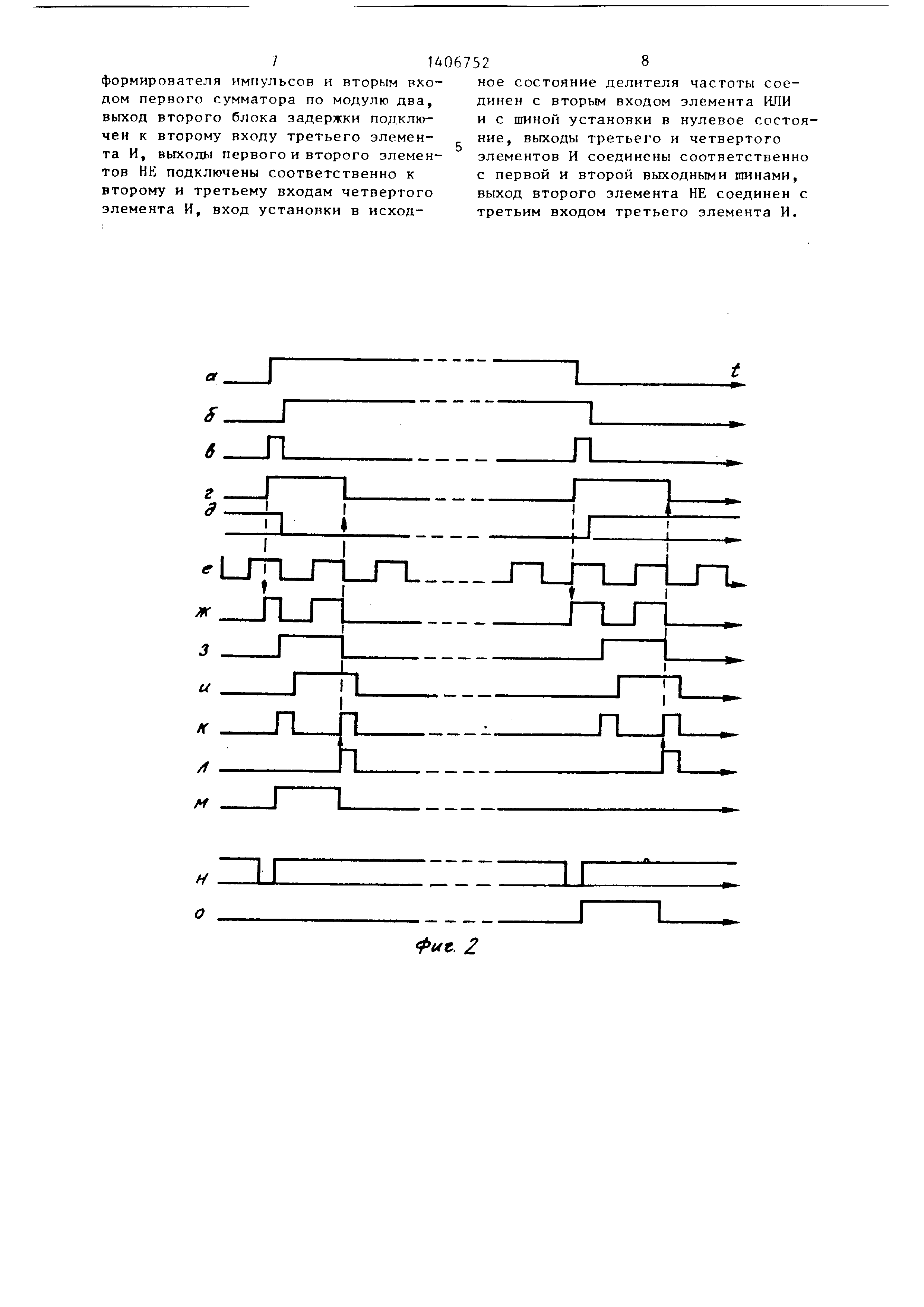

с третьим входом третьего элемента И 15. На фиг. 2 изображены временные диаграммы сигналов: а) на входе 1; б) на

выходе второго блока 8 задержки; в) в) на вькоде первого сумматора 9 по ,

модулю два; г) на выходе триггера 12; д)на выходе первого элемента НЕ 13; е)на выходе генератора 5 импульсов; ж)на выходе второго элемента И 4; з)на выходе делителя частоты 6; и) на выходе первого блока 7 задержки; к) на выходе второго сумматора 11 по модулю два; л) на выходе первого элемента

И 3; м) на выходе третьего элемента И 15; н) на выходе второго элемента

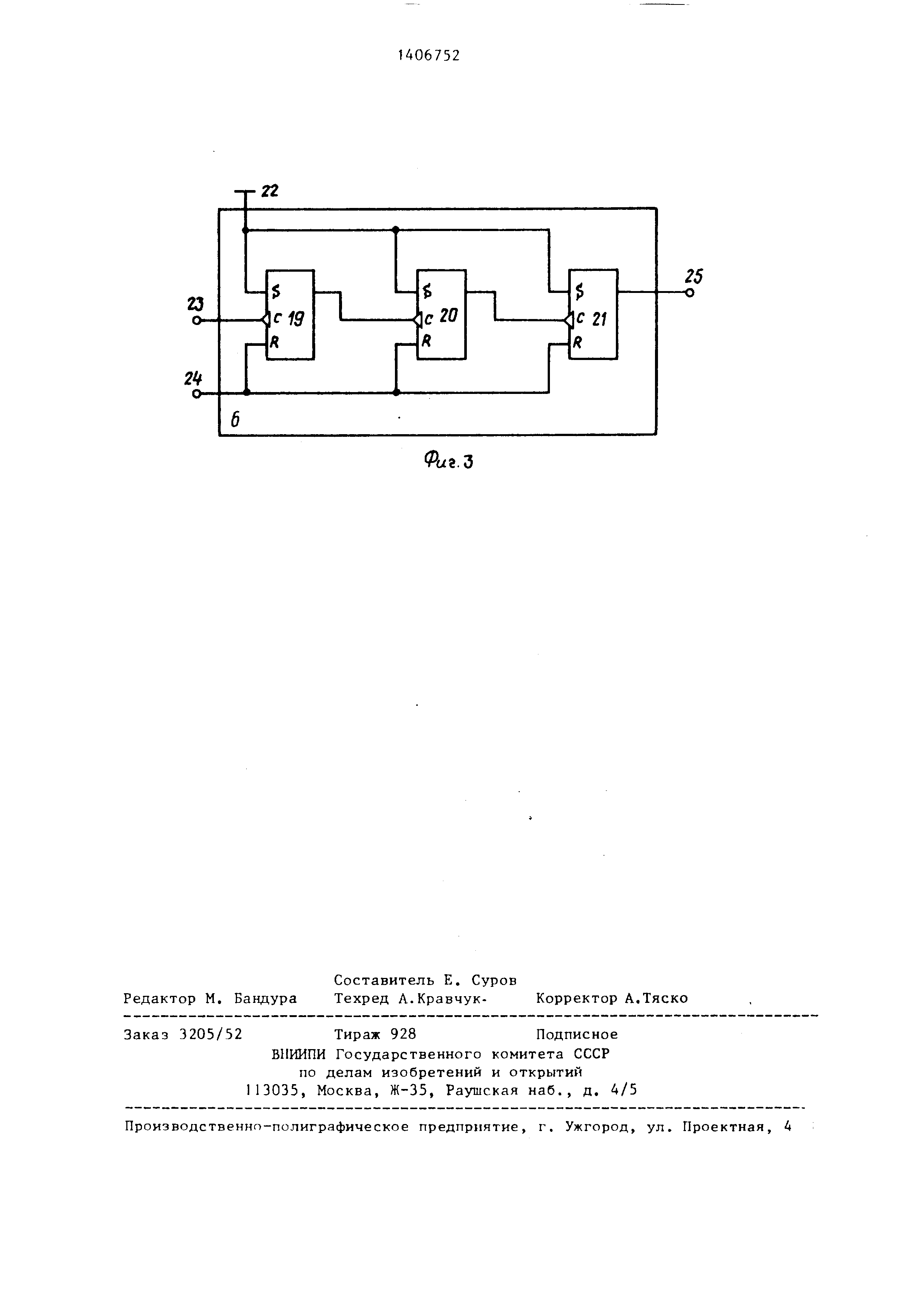

НЕ 14; о) на выходе четвертого элемента И 16. Делитель частоты (фиг. 3) содержит первый, второй и третий триггеры

19, 20, 21, шину 22 нулевого потенциала , вход 23, вход 24 установки в

нулевое состояние делителя частоты, выход 25. Все функциональные блоки, используемые в формирователе импульсов, могут быть выполнены на микросхемах

133 серии. Формирователь импульсов работает . следующим образом.

На вход 2 обнуления поступает импульсный сигнал, устанавливающий де-

Литель 6 частоты и через элемент ИЛИ 10 триггер 12 в начальное (нулевое)

состояние, при котором на выходе делителя 6 частоты и триггера 12 устанавливаются

сигналы, соответствующие низкому уровню (логическому нулю). Формирование импульса, соответствующего переднему фронту входного

сигнала, происходит следующим образом; На вход 1 поступает импульс прямоугольной

формы положительной поляр3Vi ности (фиг. 2). Он задерживается во

втором блоке 8 задержки (фиг, 26) на некоторое фиксированное премя и поступает

на первый вход первого сумматора 9 по модулю два и вход первого элемента НЕ 13, Одновременно сигнал

с входа 1 поступает на второй вход первого сумматора 9 по модулю два,на выходе которого формируется импульс

(фиг. 2б) длительностью, равной времени задержки второго блока 8 задержки

. Длительность этого импульса,т,е. время задержки, выбирается такой величины, чтобы установить триггер

12 в единичное состояние (фиг.2г). Практически длительность импульса, сформированного на выходе первого

сумматора 9 по модулю два, не превышает 50-70 НС, Поэтому блок задержки

может быть выполнен в виде после- довательного соединения нескольких

элементов НЕ, каждый из которых обладает временем задержки импульса 10-15 НС. Импульс с выхода триггера 12 (фиг. 21), соответствующий логической единице, поступает на второй вход

второго элемента И 4 и на первый вход третьего элемента И 15. Одновременно

на первый вход второго элемента И 4 поступают импульсы с выхода генератора 5 импульсов (фиг, 2е).

Фаза этих импульсов не совпадает с фазой импульсов с входа 1, т.е.

сигналы не синхронизованы. , Следует отметить, что длительность импульсов

с входа 1 составляет 0,3 с, период повторения меняется от 0,6 до 2 с. Период повторения сигнала с выхода

генератора 5 импульсов выбран, например, равным 0,25 мкс. На выходе

второго элемента И 4 формируются импульсы (фиг, 2), соответствующие выходному

сигналу генератора 5 импульсов . В делителе 6 частоты происходит

увеличение периода его входного сигнала , например, вдвое, как это изображено на фиг. 2, и на его выходе

формируется сигнал (фиг, 2 з) , Срабатывание делителя 6 частоты происходит

по заднему фронту входного импульса . Выходной сигнал делителя 6 частоты задерживается в первом блоке

7 задержки, в)емя задержки которого выбирается равным времени задержки

второго блока 8 задержки. Выходные g 0 5 5 0 5 0 5 cui Fia.Tf, первого Олока 7 злдгржки

(фиг, 2 ) и делителя 6 частоты (фиг.2з,1 подаются на второй сумматор 11 по модулю

два. Fla его выходе формируется пара импульсов (фиг.2и), которые поступают

на второй вход первого элемента И 3, на первый вход которого поступает сигнал с выхода первого

блока 7 задержки (фиг.2и). Как следует из сопоставления фиг.2 и и фиг.2 и

на выходе первого элемента И 3 формируется импульс (фиг.2л), соответствующий

второму из пары выходных импульсов второго сумматора 11 по модулю два. Импульс с выхода первого

элемента И 3 проходит через элемент ИЛИ 10 и перебрасывает триггер 12 в

исходное (нулевое) состояние (фиг.2г). На первый вход третьего элемента

И 15 поступает сигнал с выхода триггера 12 (фиг. 2т.), а на второй вход -

сигнал с выхода второго блока 8 задержки (фиг.2б), на третий вход -

сигнал с выхода второго элемента НЕ 14 (фиг. 2м). В результате на выходе

третьего элемента И 15, т.е. на первом выходе 17, формируется сигнал

(фиг. 2(у), соответствующий переднему фронту сигнала с входа 1. Формироватение импульса, соответствующего заднему фронту входного

сигнала, происходит следуюгцим образом . На входы первого сумматора 9 по

модулю два поступают сигналы с выхода второго блока задержки и с входа

1, На выходе первого сумматора 9 по модулю два формируется импульс (фиг,25)

соответствующий задним фронтам импульса с входа 1 (фиг. 2 а) и задержанного

импульса с выхода второго блока 8 задержки (фиг.26). Триггер 12 устанав

ливается в единичное состояние (фиг.2 г) и его выходной сигнал поступает

на первый вход четвертого элемента И 16 и на второй вход второго

элемента И 4. Выходной сигнал генератора 5 импульсов (фиг.2) поступает

на второй вход И 4, выходной сигнал которого (фиг.2-«) поступает на делитель 6 частоты. Сигнал с выхода делителя 6 частоты (фиг.24) поступает на второй вход

второго сумматора 11 по модулю два и на вход первого блока 7 задержки, сигнал

с выхода которого (фиг,2м) поступает на первый вход первого элемента

И 3 и первый вход второго сумматора 514 11по модулю два. На его выходе формируется пара И1чпульсов (фиг. 2k), соответствующих заднему фронту сигнй-

ла с входа 1 (фиг. 2oi).. Через первый элемент И 3 пройдет

только второй импульс с выхода второго сумматора 11 по модулю два, так как он существует в момент времени,

когда на другом входе первого элемен- та И 3 действует сигнал с выхода первого

блока 7 задержки (фиг.2и). Сигналом с выхода первого элемента И 3 (фиг. 2л) через элемент ИЛИ 10 тригге

12перебрасьшается в нулевое состоя- ние (фиг. 2 1). На втором входе четвертого элемента И 16 действует сигнал с выхода первого элемента НЕ 13 (фиг. 25), а на

третьем входе - сигнал с выхода вто- рого элемента НЕ 14 (фиг. 2м). В результате на выходе четвертого элемента И 16 формируется импульс (фиг,2 о), соответствующий заднему

фронту сигнала с входа 1 (фиг,2а). Длительности формируемых на первом

и втором выходах 17 и 18 импульсов изменяются от некоторого минимального

значения, определяемого вьфажением мим t,(n-1).

(1) где п - коэффициент деления делителя 6 частоты;

t J - период сигнала генератора 5 импульсов, до некоторого максимального значения, определяемого выражением t Mflk-c t 5- п

(2) Это изменение определяется несинхронностью сигналов с входа 1 и с выхода

генератора 5 импульсов, т.е. синал на входе 1 может появиться в любой момент относительно фазы выходного

сигнала генератора 5 импульсов. Из выражений (1) и (2) следует,

что разница между длительностями сформированного импульса, вызванная несинхронностью работы генератора 5

импульсов, определяется только периодом (частотой) выходного сигнала генератора 5 импульсов и будет тем

меньше, чем выше частота генератора 5 импульсов. Относительное значение этой разницы зависит от коэффициента деления делителя 6 частоты и обратно пропор

5 0 5 0 0 5 0 526 ционально ему, т.е. чем больше коэффициент деления делителя 6 частоты,

тем меньше относительное значение разницы в длительности сформированных импульсов. Например, при выборе частоты (периода ) генератора 5 импульсов, равной

4 МГц (0,25 мкс), и коэффициента делителя 6 частоты, равного 8, среднее значение длительности 1,87 мкс

сформированных импульсов составляет минимальное значение 1,7.5 мкс, максимальное

значение 2,0 мкс, относительное значение возможной разности длительности составляет 14%. Формула изобретения Формирователь импульсов, содержа-

wfifi входную в две выходные шины, первый блок задержки, выход которого подключен

к первому входу первого элемента И, первый элемент НЕ, элемент ИЛИ, отличающийся тем,

что, с целью повышения стабильности длительности выходных импульсов,сформированных

по переднему и заднему фронтам входного сигнала и расширения диапазона длительности формируемых

импульсов, в него введены первый и второй сумматоры по модулю два, генератор

импульсов, делитель частоты, триггер, второй блок задержки, второй

элемент НЕ, второй, третий и четвертый элементы И, причем выход генератора

импульсов подключен к первому входу второго элемента И, выход которого

через делитель частоты подключен к входу первого блока задержки, выход

второго блока задержки соединен с входом первого элемента НЕ и с первым

входом первого сумматора по модулю два, выход которого подключен к входу

установки в единичное состояние триггера и к входу второго элемента НЕ,

выход триггера соединен с вторым входом второго элемента И и первыми входами

третьего и четвертого элементов И, выход первого блока задержки соединен

с первым входом второго сумматора по модулю два, выход делителя

частоты подключен к второму входу вто- рого сумматора по модулю два, выход

которого соединен с вторым входом первого элемента И, выход которого

подключен к первому входу элемента ИЛИ, выход которого подключен к вхо-

ду сброса триггера, вход второго блока задержки соединен с входной шиной формирователя импульсов и вторым входом первого сумматора по модулю два,

выход второго блока задержки подключен к второму входу третьего элемента

И, выходы первого и второго элементов НЕ подключены соответственно к второму и третьему входам четвертого

элемента И, вход установки в исходiГ1 ж 3 и к м н о ное состояние делителя частоты соединен с вторым входом элемента ИЛИ

и с шиной установки в нулевое состояние , выходы третьего и четвертого

элементов И соединены соответственно с первой и второй выходными шинами,

выход второго элемента НЕ соединен с третьим входом третьего элемента И, Л

и put. Z «Риг.З