CROSS-CONDUCTION DETECTOR FOR SWITCHING REGULATOR

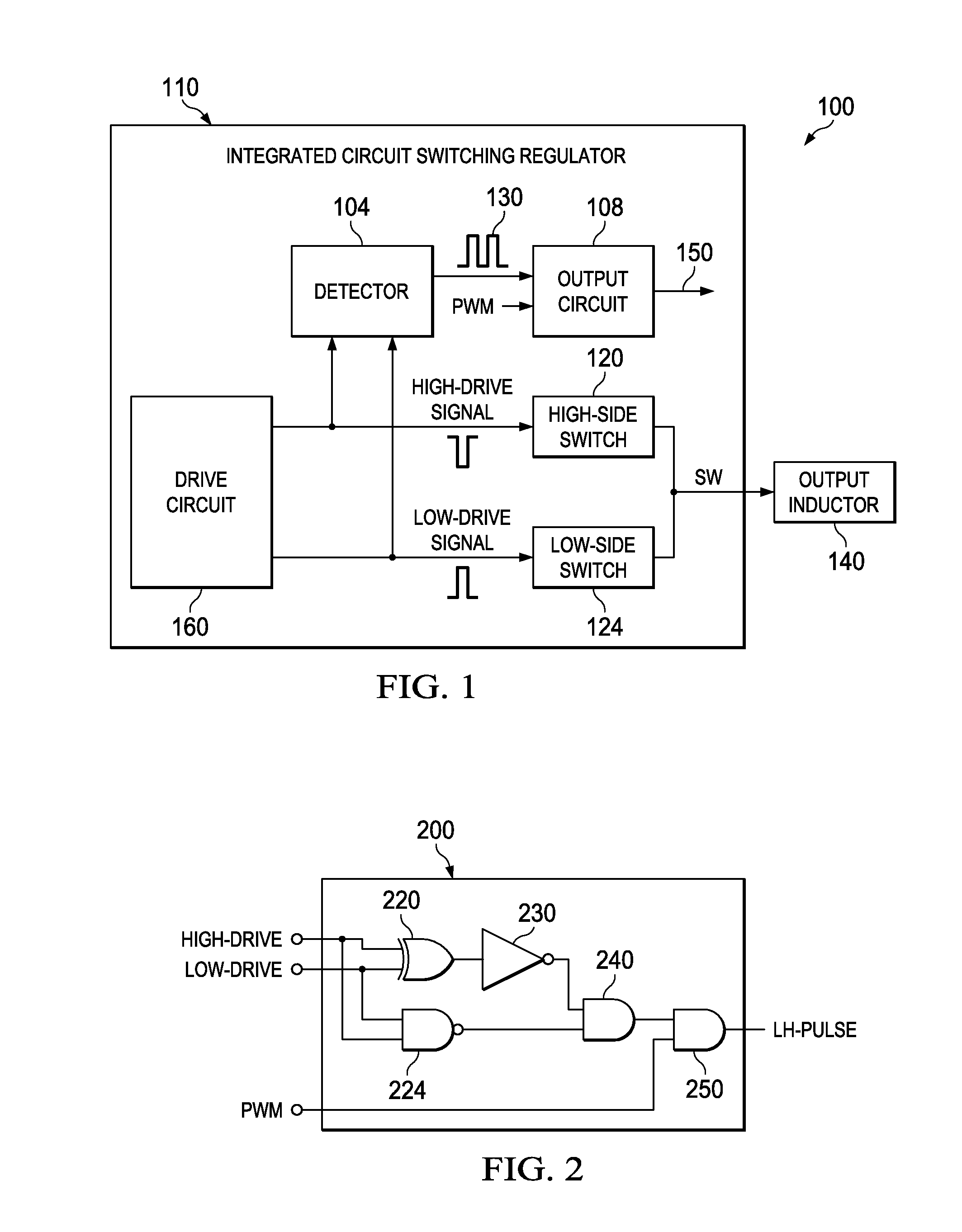

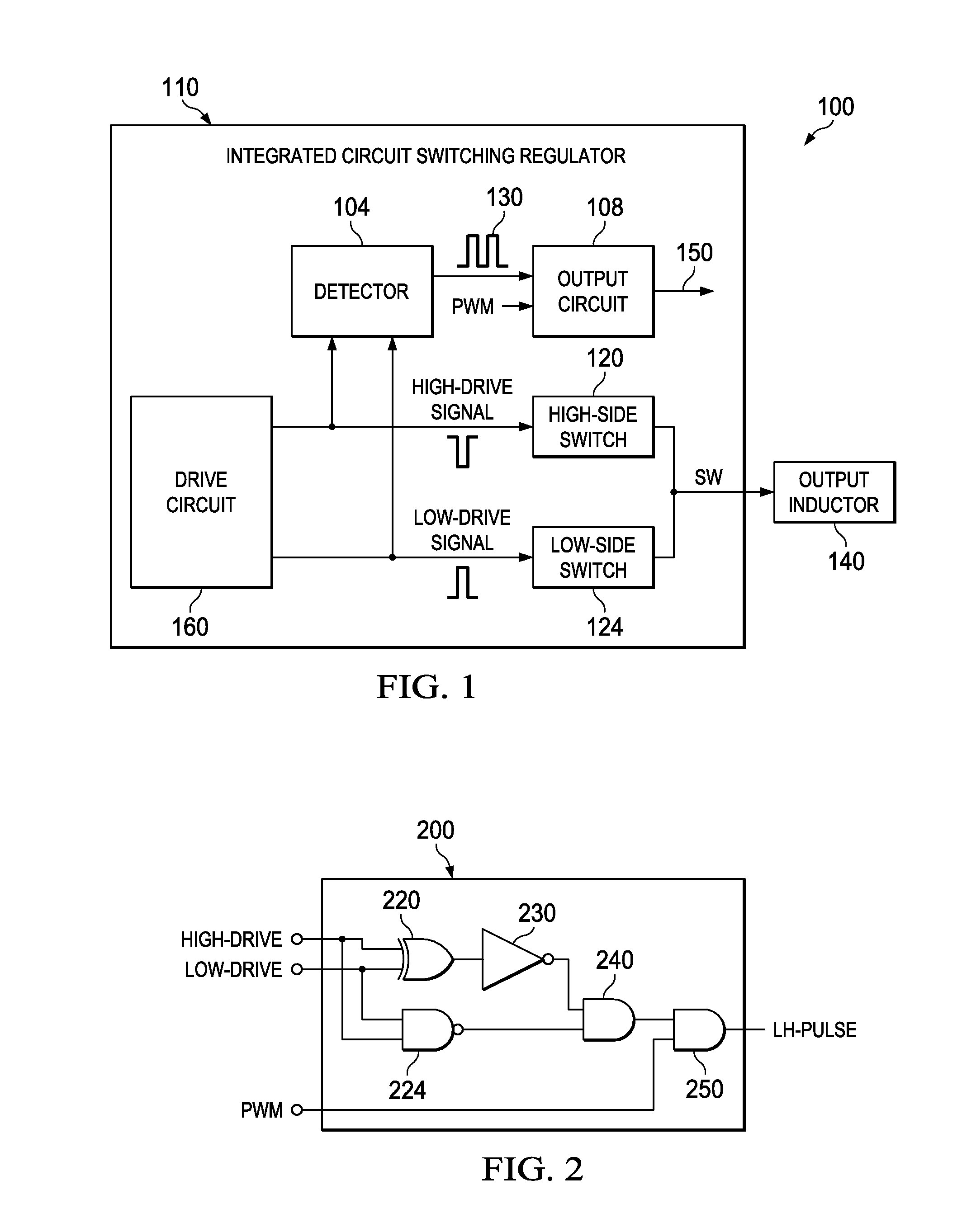

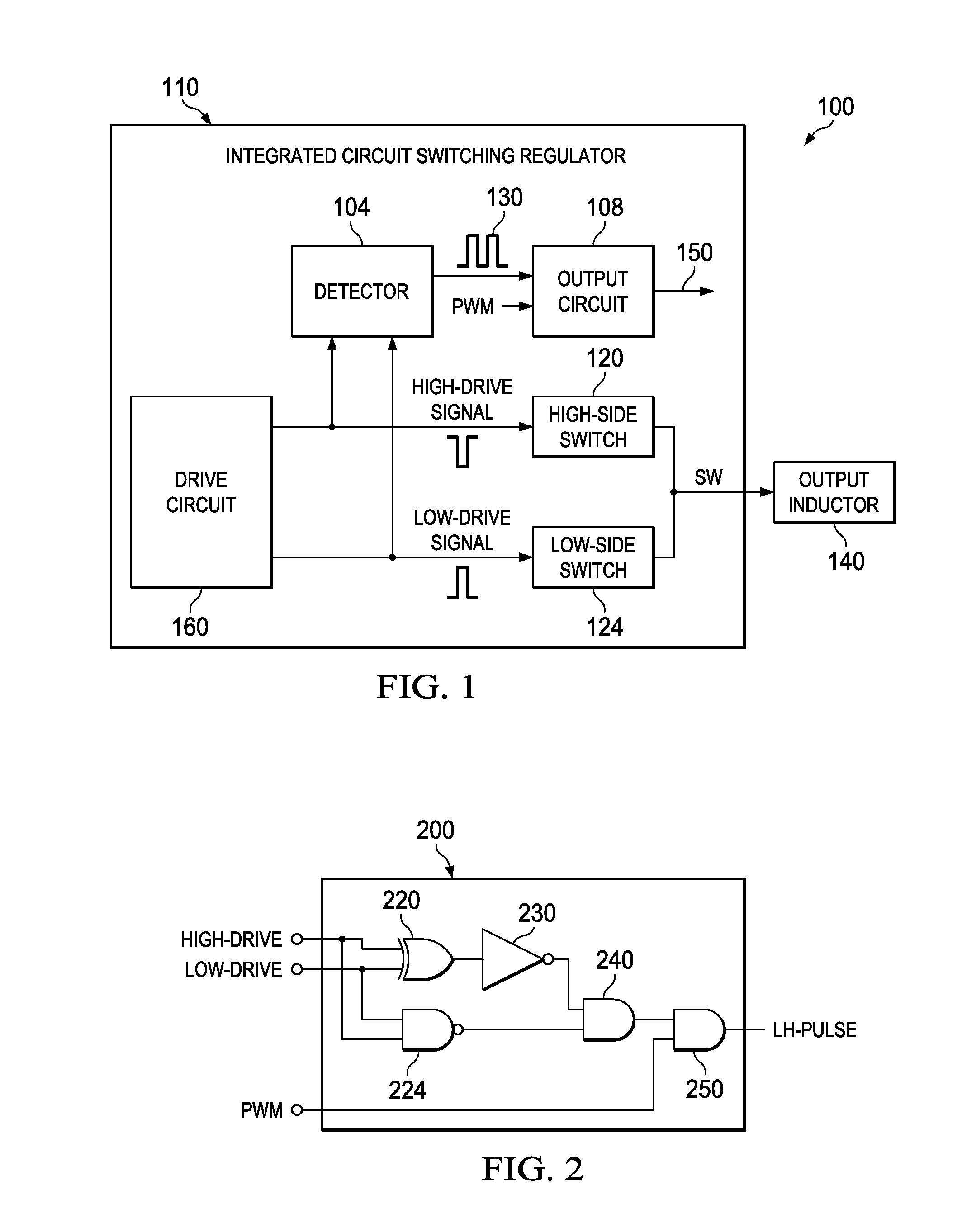

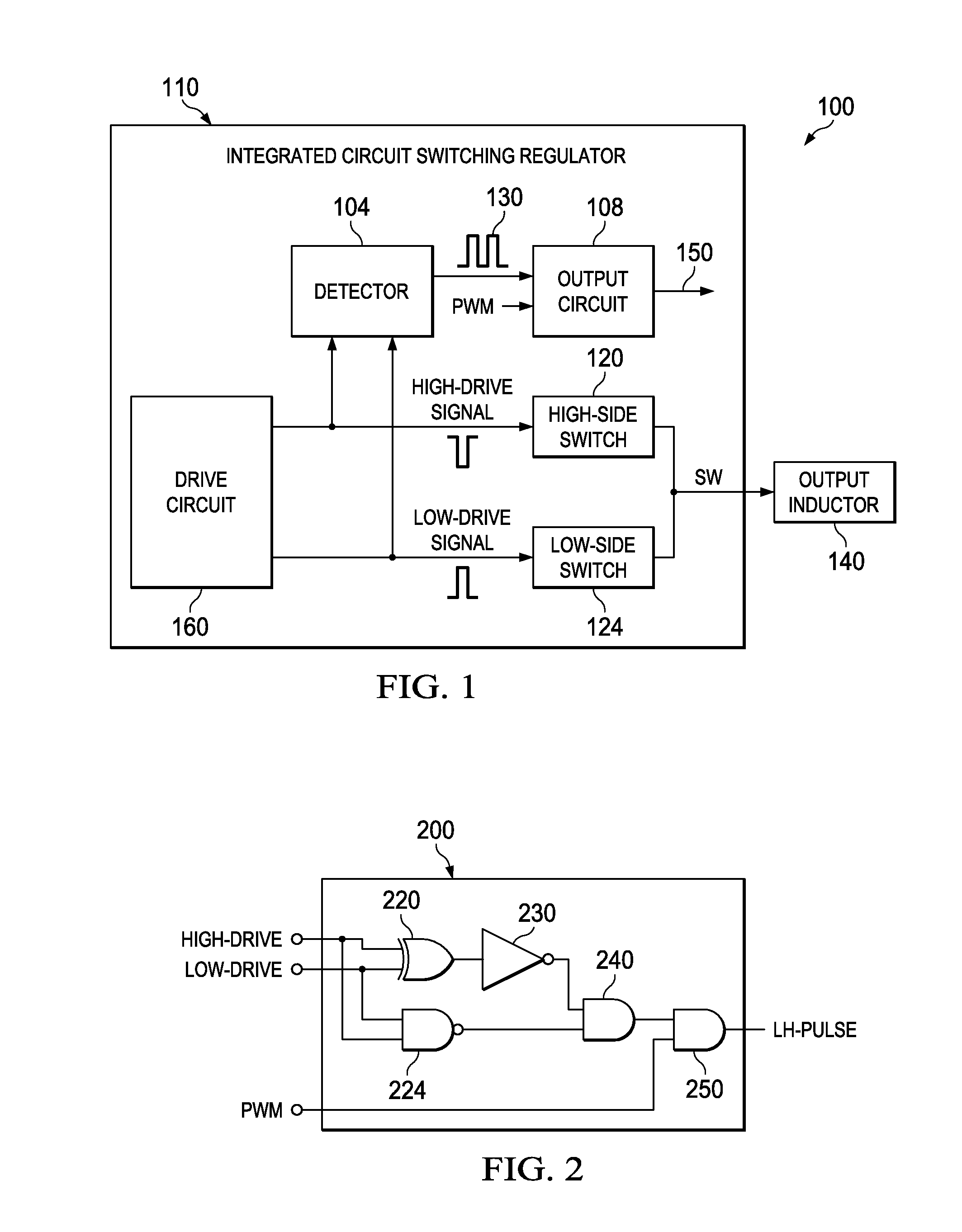

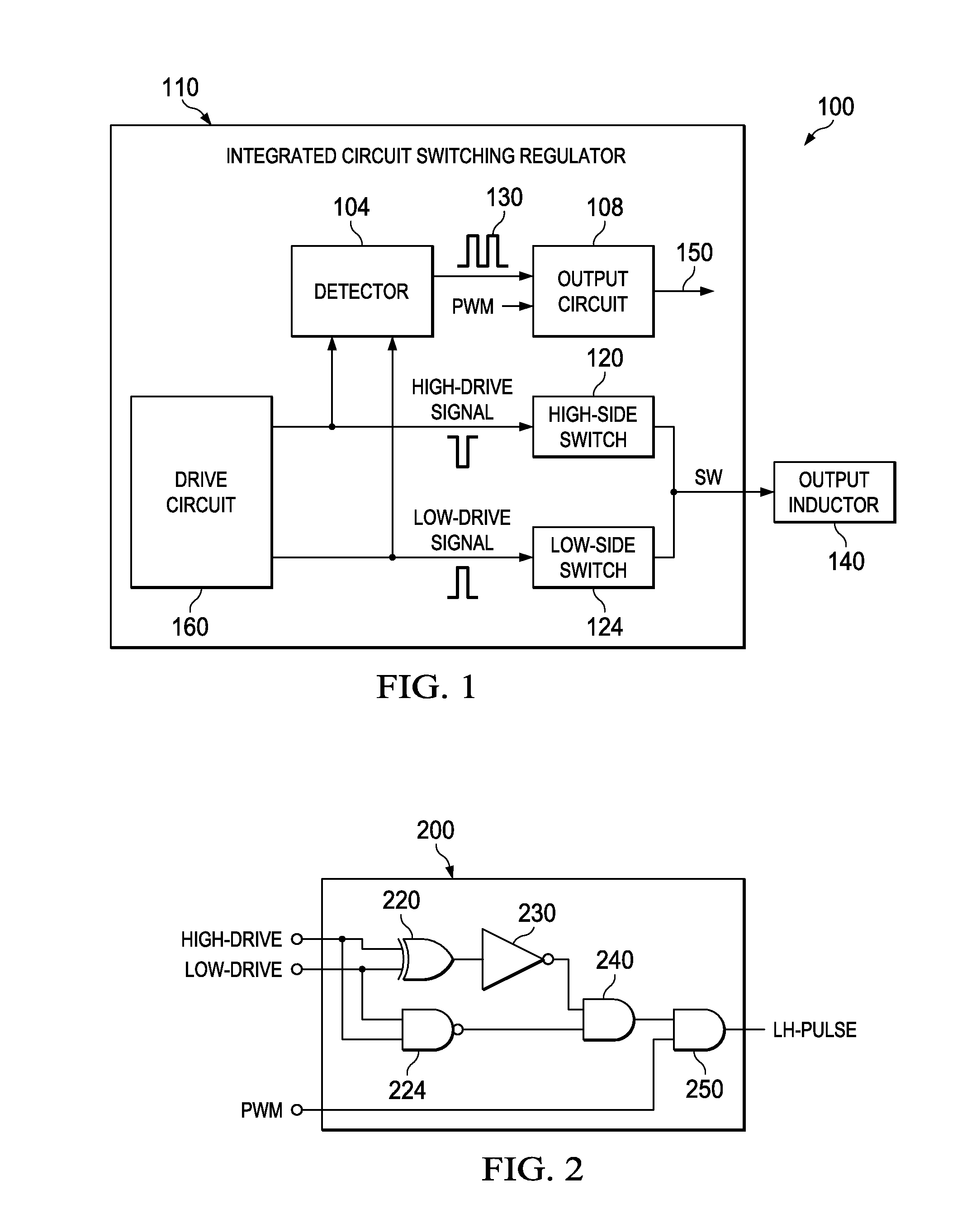

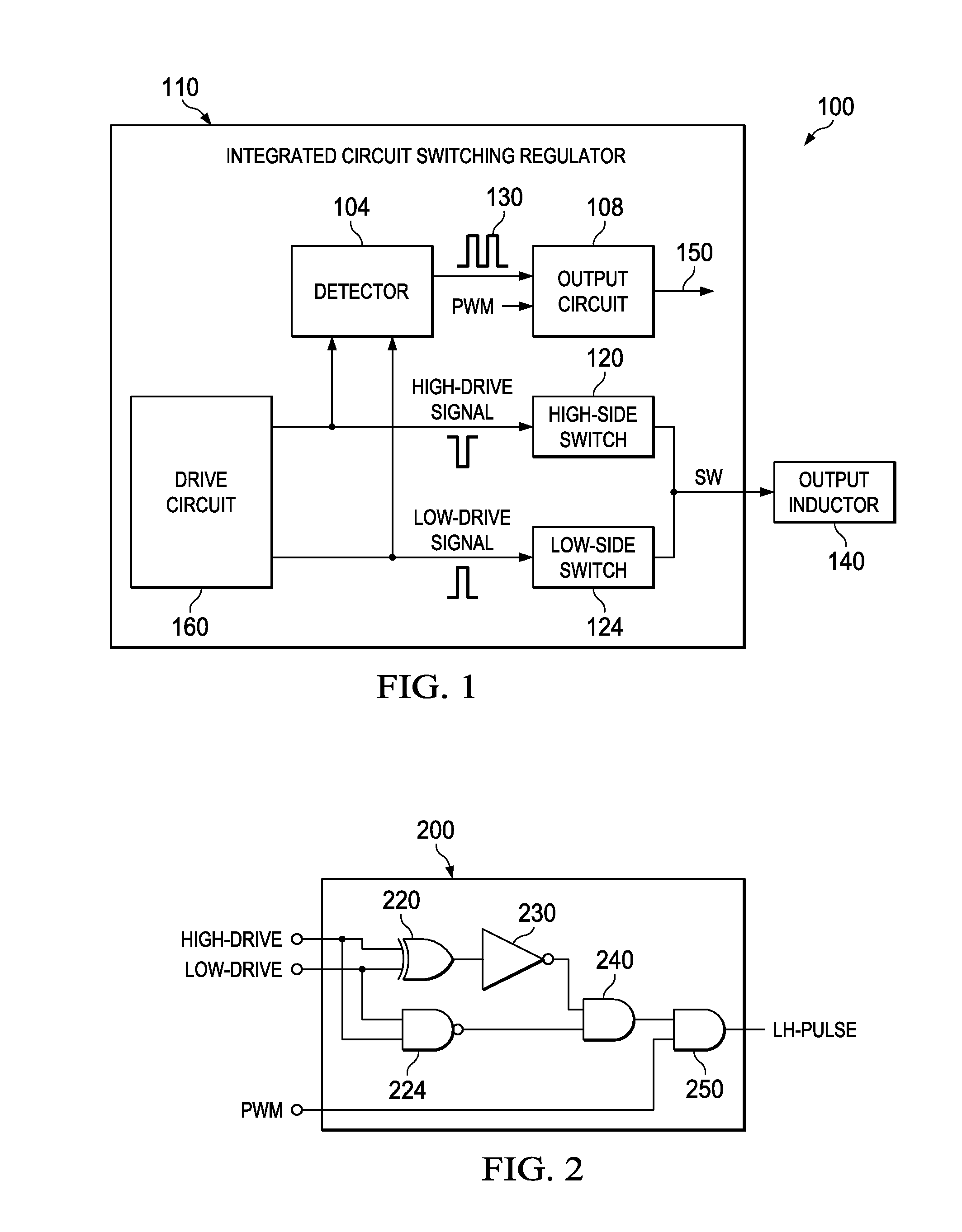

This disclosure relates to power supply circuits, and more particularly to synchronous switching regulator integrated circuits. Cross-conduction in switching regulators occurs when a high-side switch (connected to the input of a power supply) and low-side switch (connected to ground) are turned on at the same time, thereby creating a short circuit from the input supply to ground. This can lead to large current spikes and voltage transients that can degrade the reliability of the switches and decrease performance of precision circuits. Cross-conduction can be avoided by ensuring that the signal that turns on the high-side switch (HDRV) is not high at the same time as the signal that turns on the low-side switch (LDRV). In other words, a non-overlap or “dead-time” between the HDRV and LDRV signals should be provided by circuit design principles and tolerances. One issue with design tolerances is that to ensure there is no signal overlap, more dead-time may be selected than required, which can result in decreased efficiency of the switching regulator. Automated testing systems can be employed to measure the HDRV and LDRV signals to determine if any overlap exists while testing for a minimum of dead-time to promote efficiency. There are two instances when cross-conduction can occur because of signal overlap. In one instance, overlap can occur when the LDRV signal is rising high (low-side switch is turning on) and HDRV is falling low (high-side switch is turning off). The other overlap case is when the HDRV signal is rising high and the LDRV is falling low. Unfortunately, for switching regulator integrated circuits (ICs) having integrated switches, the HDRV and LDRV signals are internal to the chip and thus not readily observable by test equipment to ensure that they do not overlap. An obvious solution is to route the drive signals external to the IC for testing but such strategy can increase costs of the IC by adding extra pins and also introduce noise in the system. This disclosure relates to timing detection and controls for switching regulator integrated circuits. In one example, an integrated circuit includes a detector to monitor a high-drive signal and a low-drive signal that drives a high-side switch and a low-side switch, respectively, of a switching regulator that is part of the integrated circuit. The detector monitors both the rising edge and the trailing edge of each of the high-drive and the low-drive signals, respectively, to determine a timing overlap between the signals and generates a detection signal having a value proportional to the presence or absence of the timing overlap between the high-drive and the low-drive signals. An output circuit processes the detection signal from the detector to provide an output characterizing at least one of a dead-time or cross-conduction of the switching regulator. In another example, an integrated circuit includes a detector monitors a high-drive signal and a low-drive signal that drives a high-side switch and a low-side switch respectively of an integrated circuit switching regulator. The detector monitors both the rising edge and the trailing edge of each of the high-drive and the low-drive signals respectively to determine a timing overlap between the signals and generates a detection signal indicating a dead-time value proportional to the presence or absence of the timing overlap between the signals. An output circuit processes the detection signal from the detector to enable a correction of the timing overlap between the signals if timing overlap is detected. A pulse width modulated signal is monitored by the detector with the high-drive and low-drive signals to clock the detection signal. The detector generates the detection signal as clocked signal pulses having a pulse-width that is proportional to the dead-time value if no timing overlap is detected and generates no signal pulses for the detection signal if the timing overlap is detected. In yet another example, an integrated circuit includes a detector configured to monitor a high-drive signal and a low-drive signal that drives a high-side switch and a low-side switch respectively of an integrated circuit switching regulator. The detector monitors both the rising edge and the trailing edge of each of the high-drive and the low-drive signals respectively to determine a timing overlap between the signals and generates a detection signal indicating a dead-time value proportional to the presence or absence of the timing overlap between the signals. An output circuit processes the detection signal from the detector to enable a correction of the timing overlap between the signals if timing overlap is detected. An internal circuit receives the detection signal from the output circuit to automatically adjust the dead-time value if the timing overlap is detected. An integrated circuit is provided for efficient operation of a synchronous switching regulator. Drive signals which control how current is switched in an output inductor of the synchronous switching regulator are monitored internally by the integrated circuit via a detector. The detector determines the presence or absence of dead-time and/or cross conduction between the drive signals and generates a detection signal indicating whether or not a timing overlap between the signals exists. Rather than merely routing the drive signals external to the integrated circuit for processing which can generate noise and increase the cost of the integrated circuit by increasing pin count, the detection signal is processed internally by an output circuit which can report timing overlap (or lack thereof) between the drive signals and/or initiate automatic timing correction within the integrated circuit, if necessary. The detector 104 can be configured to monitor a high-drive signal and a low-drive signal that drive a high-side switch 120 and a low-side switch 124, respectively, of the integrated circuit switching regulator 110. The detector 104 can monitor both the rising edge and the trailing edge of each of the high-drive and the low-drive signals respectively to determine a timing overlap between the signals. The detector 104 can generate a detection signal 130 indicative of the timing overlap or absence thereof. For example, the detection signal 130 can be a single signal representing a dead-time and/or cross-conduction. For example, the output signal can provide a value, corresponding to a pulse width of the detection signal 130, that is proportional to the presence or absence of the timing overlap between the signals (e.g., indicating dead-time or cross-conduction). By way of example, if timing overlap between the high and low-drive signals is detected by the detector 104, then inadequate dead-time or cross-conduction can be determined to be present, whereas if no timing overlap is detected, then suitable dead-time or lack of cross-conduction may be determined. For example, a DC value detected at about 50% of supply voltage indicates no overlap or cross-conduction and a DC value detected at about the supply voltage or near ground indicates a timing overlap. As shown, a pulse width modulated (PWM) signal can be provided to the output circuit 108 to clock the detection signal 130. The detector 104 thus can generate the detection signal 130 as signal pulses, which are clocked by the PWM signal and having a pulse-width that is proportional to the dead-time value or cross-conduction based on the presence or absence of overlap between the high- and low-drive signals. Output from the high-side switch 120 and low-side switch 124 drives an output inductor 140 to generate a DC voltage. Each switch should be on at different times to avoid cross-conduction in the switches (e.g., when both switches are on at the same time cross-conduction between switches can occur). Ideally, the high-side switch 120 and the low-side switch 124 are controlled to turn on via the high-drive and the low-drive signals such that the switches are not conducting at the same time yet not leaving either switch in the off state for too long to promote efficiency in the switching regulator 110. As shown, a drive circuit 160 generates the high-drive signal and the low-drive signal, respectively. The drive circuit 160 can receive inputs (e.g., digital register value) to alter the timing of the drive signals and ultimately the timing of the high-side switch 120 and the low-side switch 124. For example, in an automated test environment, if inadequate dead-time were detected via an output 150 from the output circuit 108, a register value could be altered inside the drive circuit 160 to change the timing between the drive signals incrementally (e.g., 5 nanosecond increments). In another example, the output 150 could be fed-back to the drive circuit 160 or other control circuitry to implement automatic timing adjustment for the high and low-drive signals (See The output circuit 108 can be configured to provide an output indicative of dead-time or cross-conduction based on the detection signal 130 from the detector 104. In some examples, the signal provided by the output circuit can be processed to enable a correction of the timing overlap between the signals to mitigate dead-time and cross-conduction. Such timing correction can be provided by external circuitry or by one or more possible configurations of the output circuit 108, such as the example output circuits illustrated and described below with respect to In other examples, timing correction can be provided via internal monitoring and adjustments within the switching regulator 110 without external monitoring. In either configuration, pin count of the switching regulator 110 can be reduced since in one configuration only a single pin is employed to monitor the output(s) 150 or, in the internal configuration, no pins are utilized as the output 150 can be processed internally to the IC switching regulator 110. Thus, rather than route both the high-drive and the low-drive signals externally for monitoring as for conventional circuits, one or less (i.e., zero) pins can be employed in the switching regulator 110 since the detector 104 only generates the detection signal 130 from the logic employed for monitoring multiple drive signals. The detector 104 and output circuit 108 cooperate to detect cross-conduction or dead-time for switches 120 and 124 of the IC switching regulator 110 without the need to monitor the high-drive and low-drive signals via an ATE, for example. The circuit 100 can also be modified, such as disclosed herein, to measure dead-time without observing the high-drive and low-drive signals externally. The absence of cross-conduction in switching regulator ICs with integrated switches manifests itself by periodic voltage transitions to (approximately) −1V on the node common to the high- and low-side switch, commonly referred to as the SW node and shown as SW driving the inductor 140. These transitions should be monitored to ensure adequate dead-time. In other examples, since regulators with integrated switches do not provide natural access to the voltage signals that turn on the high-side (high-drive) and low-side (low-drive) switches 120 and 124, these signals could be routed to pins in a test-mode and monitored for overlap. The circuit 100 detects the presence of cross-conduction or dead-time without the need to monitor potentially noisy SW, low-drive, and high-drive signals external to the IC switching regulator 110. The detector 104 and output circuit 108 minimize the need to detect cross-conduction by monitoring the SW node for periodic −1V transitions, for example. Detecting these voltage transients can be difficult in the production test environment because of undesired parasitic elements inherent to the test equipment. Thus, the large transient voltage drops across these parasitic elements that occur when the IC switching regulator 110 is operational can overwhelm the −1V voltage on the SW node, making it difficult to detect. By utilizing the detector 104 and output circuit 108, routing the high-drive signal and low-drive signal to an external pin becomes unnecessary. The high-drive and low-drive signals are switching signals that have the potential of coupling noise onto other noise-sensitive signals and potentially corrupting them. Therefore, routing these noisy signals in the layout of large, complex ICs to an external pin can entail significant risk, and the circuit 100 mitigates such risk. The circuit 100 can be scaled to include an indirect, noise-immune measurement of dead-time or cross-conduction without requiring to measure it directly at the SW node in a noisy environment that does not yield reliable results. The circuit 100 can also be scaled to eliminate the need to measure dead-time on an ATE, thereby reducing test-time and test costs. In one example, the circuit 100 can be provided as a circuit (e.g., integrated circuit, discrete circuit, combination of integrated circuit and discrete circuits) for generating a switched DC voltage via the inductor 140. Discrete control elements can be provided within the drive circuit 160, for example, for adjusting dead-time. This could include a processor operating firmware to control operation of the drive circuit 160. In another example, the drive circuit 160 could be a hard-wired function wherein dedicated logic and switching elements control the drive circuit 160. In yet another example, a combination of programmed elements and circuit logic elements could cooperate to perform the operation of the drive circuit 160. It is noted that the examples described herein can be provided via different analog and/or digital circuit implementations. For instance, in some cases, field effect transistors can be employed and in other cases junction transistors or diodes employed. Some components can be employed as discrete implementations such as a comparator comparing a reference signal to a control signal and in other examples, controllers operating via processor instructions and exchanging data via D/A and A/D converters could be employed to monitor drive signals and generate timing adjustment signals within the switching regulator 110. The circuit 100 can employ various means of monitoring electrical parameters such as monitoring voltage and/or current via the detector 104. It can also employ a microcontroller or other control circuitry capable of digitizing these parameters, storing digital interpretations of these parameters in its memory, and associating acquired values with events in the circuit 100 operation. This includes performing logical and arithmetical operations with the acquired values, for example. An example of timing for the high-drive signal, low-drive signal, PWM signal, and resultant LH-PULSE output in the detector 200 are shown in the timing diagram 310 of Output from the high-side switch 820 and low-side switch 824 drives an output inductor 840 to generate a DC voltage. Each switch should be on at different times to avoid cross-conduction in the switches (e.g., when both switches are on at the same time cross-conduction between switches can occur). Ideally, the high-side switch 820 and the low-side switch 824 are timed to turn on via the high-drive and the low-drive signals such that the switches are not conducting at the same time yet not leaving either switch in the off state for too long to promote efficiency in the switching regulator 810. A drive circuit 860 generates the high-drive signal and the low-drive signal, respectively, based on the PWM signal that is also provided to the detector 804. The drive circuit 860 can receive feedback inputs (e.g., digital register value) from an internal circuit 870 to alter the timing of the drive signals and ultimately the timing of the high-side switch 820 and the low-side switch 824. As shown, an automatic correction signal from the output circuit 808 is fed-back to the internal circuit 870 for automatic timing adjustment of the high-drive and low-drive signals via the drive circuit 860. The automatic correction signal from the output circuit 808 can be an analog value, a digital value, or a combination of analog/digital values representing the timing overlap (or lack thereof) between the high-drive and low-drive signals as detected by the detector 804. What have been described above are examples. It is, of course, not possible to describe every conceivable combination of components or methodologies, but one of ordinary skill in the art will recognize that many further combinations and permutations are possible. Accordingly, the disclosure is intended to embrace all such alterations, modifications, and variations that fall within the scope of this application, including the appended claims. As used herein, the term “includes” means includes but not limited to, the term “including” means including but not limited to. The term “based on” means based at least in part on. Additionally, where the disclosure or claims recite “a,” “an,” “a first,” or “another” element, or the equivalent thereof, it should be interpreted to include one or more than one such element, neither requiring nor excluding two or more such elements. An integrated circuit includes a detector configured to monitor a high-drive signal and a low-drive signal that drives a high-side switch and a low-side switch respectively of an integrated circuit switching regulator. The detector monitors both the rising edge and the trailing edge of each of the high-drive and the low-drive signals respectively to determine a timing overlap between the signals and generates a detection signal indicating a dead-time value proportional to the presence or absence of the timing overlap between the signals. An output circuit can be configured to process the detection signal from the detector to enable a correction of the timing overlap between the signals if timing overlap is detected. 1. An integrated circuit comprising:

a detector configured to monitor a high-drive signal and a low-drive signal that drive a high-side switch and a low-side switch, respectively, of a switching regulator that is part of the integrated circuit, wherein the detector monitors both a rising edge and a trailing edge of each of the high-drive and the low-drive signals, respectively, to determine a timing overlap between the signals, and to generate a detection signal having a value proportional to a presence or absence of the timing overlap between the high-drive and the low-drive signals; and an output circuit configured to process the detection signal from the detector to provide an output characterizing at least one of a dead-time or cross-conduction of the switching regulator and to adjust the timing to control did next time of a next switching cycle to prevent or reduce cross-conduction of the switching regulator. 2. An integrated circuit comprising:

a detector configured to monitor a high-drive signal and a low-drive signal that drive a high-side switch and a low-side switch, respectively, of a switching regulator that is part of the integrated circuit, wherein the detector monitors both a rising edge and a trailing edge of each of the high-drive and the low-drive signals, respectively, to determine a timing overlap between the signals, and to generate a detection signal having a value proportional to a presence or absence of the timing overlap between the high-drive and the low-drive signals; and an output circuit configured to process the detection signal from the detector to provide an output characterizing at least one of a dead-time or cross-conduction of the switching regulator; further comprising a pulse width modulated signal that is monitored by the detector with the high-drive and low-drive signals to clock the detection signal, wherein the detector generates the detection signal as clocked signal pulses having a pulse-width that is proportional to the dead-time if no timing overlap is detected and generates no signal pulses for the detection signal if the timing overlap is detected. 3. The integrated circuit of 4. The integrated circuit of 5. The integrated circuit of 6. The integrated circuit of 7. The integrated circuit of 8. The integrated circuit of 9. The integrated circuit of 10. The integrated circuit of 11. The integrated circuit of 12. An integrated circuit comprising:

a detector configured to monitor a high-drive signal and a low-drive signal that drive a high-side switch and a low-side switch respectively of an integrated circuit switching regulator, wherein the detector monitors both a rising edge and a trailing edge of each of the high-drive and the low-drive signals, respectively, to determine a timing overlap between the signals, and to generate a detection signal indicating a dead-time value proportional to a presence or absence of the timing overlap between the signals; and an output circuit configured to process the detection signal from the detector to enable a correction of the timing overlap between the signals if timing overlap is detected, wherein a pulse width modulated signal is monitored by the detector with the high-drive and low-drive signals to clock the detection signal, wherein the detector generates the detection signal as clocked signal pulses having a pulse-width that is proportional to the dead-time value if no timing overlap is detected and generates no signal pulses for the detection signal if the timing overlap is detected. 13. The integrated circuit of 14. The integrated circuit of 15. The integrated circuit of 16. The integrated circuit of 17. The integrated circuit of 18. The integrated circuit of 19. An integrated circuit comprising:

a detector configured to monitor a high-drive signal and a low-drive signal that drive a high-side switch and a low-side switch respectively of an integrated circuit switching regulator, wherein the detector monitors both a rising edge and a trailing edge of each of the high-drive and the low-drive signals respectively to determine a timing overlap between the signals, and to generate a detection signal indicating a dead-time value proportional to a presence or absence of the timing overlap between the signals; an output circuit configured to process the detection signal from the detector to enable a correction of the timing overlap between the signals if timing overlap is detected; and an internal circuit that receives the detection signal from the output circuit to automatically adjust the dead-time value if the timing overlap is detected and to adjust the timing to control did next time of a next switching cycle to prevent or reduce cross-conduction of the switching regulator. 20. An integrated circuit comprising:

a detector configured to monitor a high-drive signal and a low-drive signal that drive a high-side switch and a low-side switch respectively of an integrated circuit switching regulator, wherein the detector monitors both a rising edge and a trailing edge of each of the high-drive and the low-drive signals respectively to determine a timing overlap between the signals, and to generate a detection signal indicating a dead-time value proportional to a presence or absence of the timing overlap between the signals; an output circuit configured to process the detection signal from the detector to enable a correction of the timing overlap between the signals if timing overlap is detected; and an internal circuit that receives the detection signal from the output circuit to automatically adjust the dead-time value if the timing overlap is detected; further comprising a pulse width modulated signal that is monitored by the detector with the high-drive and low-drive signals to clock the detection signal, wherein the detector generates the detection signal as clocked signal pulses having a pulse-width that is proportional to the dead-time value if no timing overlap is detected and generates no signal pulses for the detection signal if the timing overlap is detected.TECHNICAL FIELD

BACKGROUND

SUMMARY

BRIEF DESCRIPTION OF THE DRAWINGS

DETAILED DESCRIPTION