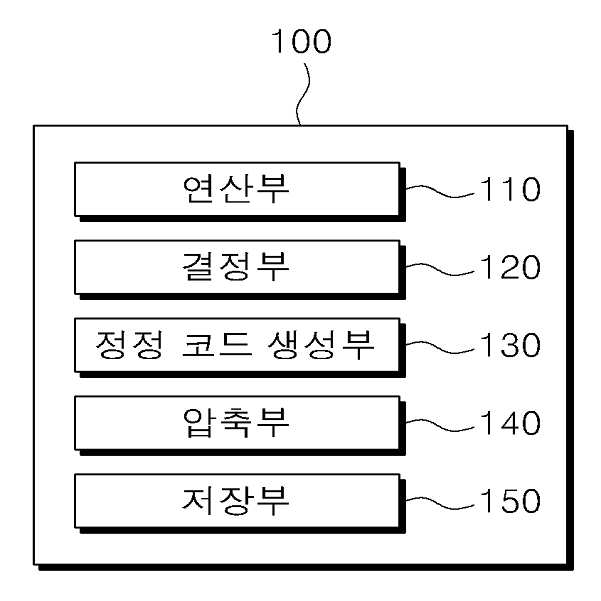

NAND FLASH MEMORY CONTROLLER USING COMPRESSION RATE AND NAND FLASH MEMORY STORAGE METHOD USING SAME

The present invention refers to compression ratio using NAND flash memory controller and NAND flash memory storage method relates to search, more particularly of NAND flash memory data storage for attaining high reliability in NAND flash memory controller and a NAND flash memory storage method using the same are disclosed. A non-volatile memory data in a NAND flash memory (Nand Flash Memory) even if the same is the means by which power disconnected electrical device information input method can be implemented in a substrate. NAND flash memory cells arranged in series, a large cells permits large integratable narrow area. In addition, the data is recorded number tank costs or eraser speed disclosed. Such advantages due to MP3 player, digital camera, portable storage device such as a memory of the portable information communication device are used mainly. NAND flash memory control gate voltage by each cell (floating gate) floating gate (control gate) pushes through data in a manner to write the electronic cell filling. For example, the electronic cell that is filled with 1, 0 the SLC (Single Level Cell) recording such data recording scheme which emptied cells called the anode. A device to increase the amount of data stored in the cookies one controlling the amount of electrons filling the data divided into two level 4 and controls the amount of electronic data recording method of the MLC (Multi Level Cell), 8 divided into two level data recording method of the TLC (Triple Level Cell) called the anode. However, the accurate regulation of the amount of electrons by an amount setting techniques include the current number side pin is difficult. The, NAND flash memory controller can be NAND flash memory data storage error is generated. The, NAND flash memory controller may comprise a data storage the basic constellation mapper ECC (Error Correcting Code) error correction information together with the data to store. Therefore, ECC error correction information database data error detection and correction data assigned to storage space can be to increase the stability. However, one number so that the number of cells constituting a NAND flash memory, data error detection and correction ECC error correction information in order to improve the ability to increase the amount of data that can be assigned to increase storage space storing door-to-pin is point number. As well as, receiving the control information received from a number of tank cost door number point occurs. The background of the invention the technology provides a Korean registration patent number 10 - 0816761 call (2008. 03. 25. Notification) to disclosure in the nanometer range. The technical objectives of this invention of NAND flash memory is NAND flash memory controller and data storage for attaining high reliability in NAND flash memory storage for a number [...] method using the same are disclosed. These techniques for effecting the cash NAND flash memory according to an embodiment of the present invention specific number in NAND flash memory storage method, the compressibility of the original data outputs a calculated, said calculated compression ratio and a plurality of predetermined threshold ranges calculated by said original data symbol rate, determining a number of bits of said error correction according to a code symbol rate (error correcting code), according to said determined bit generating an error correcting code, said calculated compression ratio generating original data according to compress the compressed data, and said generated error correction code NAND flash memory storing said combined compressed data comprising the following steps. The calculated said symbol rate, comparing said calculated a predetermined compression rate of a plurality of critical ranges, said calculated compression ratio corresponding to a range correction compression ratio threshold includes determining, using said correction compression ratio comprising said original data symbol rate can be calculated. The step of correcting said compression ratio, said compression ratio (r) then using equations include the range of the smallest size threshold value said correction compression ratio ( ) Can be determined. Wherein, r0 R ton A mean value size is big. Said compressed data bits with said sum is less than or equal to a predetermined number of bits of an error correcting code allocation bit thereof can. Said generating step includes compressed data, said compressed data bits with said error correction code said number of bits is smaller than the sum bit allocation, bit allocation said compressed data in said bit error correction coded bit number 0 said binary data in the compressed data can be adding value is subtracted. Said data area further includes spare and NAND flash memory, said storing step, said data area and storing said error correcting code generated through other spare area can be. In the embodiment according to the compressibility of the NAND flash memory controller of the present invention other digital signal from the original data calculating, using said calculated compression ratio and a plurality of predetermined critical ranges said original data symbol rate calculation unit for calculating, in accordance with error correction code (error correcting code) for determining a number of bits said symbol rate determining section, said determined bit error correction according to a code correction code generation unit, original data compression means for compressing data according to said calculated compression ratio compression, and said generated error correction code NAND flash memory storing said combined compressed data having a predetermined wavelength. The according to the present invention, data lossless compression technique by increasing the number assigned to an error correction code bit of the data stored in the NAND flash memory can be improve stability and error correction capacity. In addition, a plurality of critical ranges by compression ratio according to predefined error correction code rate between the front polarizer corresponding to occur in the operation for reducing the time delay can be. As well as, extra data amount generated to a defining compression ratio by adding 0 binary data can be maintaining compatibility with existing NAND flash memory system. Figure 1 shows a configuration of the NAND flash memory controller according to an embodiment of the present invention also are disclosed. Figure 2 shows a NAND flash memory storage order of method according to an embodiment of the present invention also are disclosed. Figure 3 shows a S220 specifically indicating order of Figure 2 also are disclosed. Figure 4 shows a S222 to explain the steps of Figure 3 is also are disclosed. Figure 5 shows a S250 to explain the step of Figure 2 also are disclosed. Objects of the present invention in the embodiment for the present invention below with reference to a person with skill in the art for drawing in the embodiment is hereinafter is provided to to detailed as follows. However the present invention refers to several different taught herein can be embodied in the form of a in the embodiment is not limited to. The present invention is described in drawing and unambiguously account for when the dispensed portion that is independent, like part subjected to a similar drawing code is configured to receive through the entire specification. The entire specification, that "comprising" when any portion of any components, particularly the opposite substrate [...] number but without other components may further include other components of switched to each other. Objects of the present invention in the embodiment for the present invention with reference to a drawing then is provided to the person with skill in the art is detailed hereinafter for embodiment in to each other. First, for NAND flash memory controller according to an embodiment of the present invention also through heat diffuse to 1. Figure 1 shows a configuration of the NAND flash memory controller according to an embodiment of the present invention also are disclosed. As shown in fig. 1, according to an embodiment of the present invention NAND flash memory controller (100) includes a computing unit (110), decision unit (120), correction code generation unit (130), compression (140) and store (150) having a predetermined wavelength. First, an arithmetic unit (110) is performed in a polarizer of the input original data is received. And, calculation unit (110) is uses the calculated compression ratio and a predetermined original data code rate is performed in a plurality of threshold ranges. Specifically, an arithmetic unit (110) includes a plurality of threshold compares a predetermined retention uses the calculated range. Then, calculation unit (110) is uses the calculated threshold corresponding to a range correction compression ratio determines the compression is included. The, computing unit (110) includes the range of the smallest size is uses the calculated compression ratio threshold value correction compression ratio can be determined. And, calculation unit (110) is performed in a original data code rate is determined correction using compression ratio. Next, decision unit (120) is uses the calculated symbol rate determines number of bits according to an error correcting code. Wherein, implies an error correcting code (error correcting code), data to detect an error of correcting control information can be assembled to big. Next, correction code generation unit (130) of the bit error correcting code is determined a number below. Then, compression (140) is uses the calculated compression ratio produce original data according to compress the compression data. The, sum is the number of bits of compressed data bit number of a predetermined number of bits less than or equal to an error correcting code allocation thereof can. The, compression section (140) is compressed data bit error detection and correction code bit number is smaller than the sum bit allocation, bit allocation bit and error detection and correction code number of bits is subtracted compressed data in the compressed data can be adding binary data value 0. Next, store (150) for combining the generated error correction code compressed data store a NAND flash memory. The, store (150) can be compressed data in a data area of the NAND flash memory. And, store (150) is an error correction code by a change in the data area and spare area of NAND flash memory capable of storing disclosed. Then, NAND flash memory controller according to an embodiment of the present invention also 2 to 5 also through (100) for NAND flash memory storage method using heat diffuse to the. Figure 2 shows a NAND flash memory storage method according to an embodiment of the present invention also order of [...], specifically indicating the order of Figure 2 Figure 3 shows a S220 are disclosed. First, an arithmetic unit (110) is performed in a received input original data compression ratio (S210). Specifically, an arithmetic unit (110) is original data according to a pre-determined-detecting device is performed in a compression ratio. Wherein, detecting repetition length coding (run a-length coding), Huffman coding (Huffman coding) and ram [pheyl - tent (lossless compression) technique such as lossless compression coding (Lempel-a Ziv coding) can be in any one. And, calculation unit (110) is uses the calculated compression ratio and a predetermined original data code rate is performed in a plurality of threshold ranges (S220). Specifically residual 3 also through S220, computing unit (110) is computed steps S210 compares a predetermined compression rate of a plurality of critical range (S221). The, taking into account a plurality of predetermined threshold range of NAND flash memory structure or the like by the pivotably relative to conventional design changes. And, calculation unit (110) is in a computing step S210 determines retention includes threshold corresponding to a range correction compression ratio (S222). Specifically, an arithmetic unit (110) receive a next equations using the rate (r) included in the range of the smallest size threshold value correction compression ratio ( ) Can be determined. Wherein, r0 R ton A mean value size is big. On the other hand, r0 R ton In mutually the same interval can be set. For example, {r0 =0, r1 =5, r2 =10, .., rn =100} or threshold range is set intervals such as 5%, {r0 =0, r1 =10, r2 =20, .., rn =100} can be critical range is set intervals such as 10%. The, interval is designed by one skilled in consideration of NAND flash memory structure or the like can be changed disclosed. Figure 4 shows a S222 as to explain the drawing step, as also [...] of Figure 3 is attached to a 4, the calculated retention r r1 R and greater than or equal2 Assuming that the other than small critical range. The, of Figure 4 is an arithmetic unit (110) is the smallest in the range it is a shame r corresponding threshold1 Correcting the compression ratio can be determined. For example, compression ratio and r is 27%, 25% and 30% larger than or equal to either of the plurality of critical ranges is limited to have a assuming, computing unit (110) for correcting the smallest is 25% compression ratio can be determined it is a shame. Next, an arithmetic unit (110) is original data code rate is performed in a correction using compression ratio (S223). Wherein, output bit per symbol rate as the means by which the number of input bits, the error number [...] to some bits to be big. The, code rate is lowered S. greater data error correction capability increases. Specifically, an arithmetic unit (110) is compressed data correction compression ratio according to a resource allocation bit 220H equipment of keeping up to original data symbol rate which calculates, using (R) 2 [...] below equations can be calculated. The, original data allocation bit poached egg NAND flash memory for storing coded data when encoding by big number of bits. A predetermined resource allocation bit number which, taking into account of NAND flash memory structure or the like by the pivotably relative to conventional design changes. For example, a resource allocation bit number 120 bit, bit original data 100, correcting the compression is 15% is assumed as follows. The, original data compression of the compressed data according to the compression ratio correction bit number 85 bit is under or over. , the 85/120 symbol rate, i.e. 70. 83% Is under or over. If, when the 100/120 without using compression symbol rate, i.e. 83. 33% Is under or over. Thus, NAND flash memory controller according to an embodiment of the present invention (100) includes a symbol rate by operating the compression correction using compression ratio without using symbol rate can be lower than if, data error correction capability can be height. Next, decision unit (120) is an error correcting code according to the code rate (S230) decides the number of bits. Specifically, determining section (120) and allocation determines number of bits using an error correcting code symbol rate is bit number, below 3 equations can be determining number of bits using an error correcting code. For example, 120 and bit allocation bit number, the 17/24 symbol rate is assumed as follows. Then, determining section (120) is assigned to a variable symbol rate bit number 3 angles computed results 35 bit error correction code bits can be detected. Next, correction code generation unit (130) of the bit error correcting code is determined a produce (S240). Specifically, correction code generation unit (130) to a pre-determined coding scheme is determined in S230 to produce the bit error correcting code. For example, determining section (120) of determining if the error correction coded bit is bit 35, correction code generation unit (130) is the bit error correction code to a pre-determined coding scheme can be 35. The, coding scheme employs a Hamming code (Hamming Code), Low-a Density Parity Check code, Golay code (Golay Code), BCH code (BCH Code), lead Miller code (Reed-a Muller Code), at least one reed Solomon code (Reed a-Solomon Code) can be. And, compression section (140) is uses the calculated compression ratio according to compress the original data (S250) produce a compressed data. Figure 5 shows a S250 to explain the step of Figure 2 also are disclosed. The, sum is the number of bits of compressed data bit number of a predetermined number of bits less than or equal to an error correcting code allocation thereof can. This S222 in calculating section (110) comprising the range of the smallest size is furthermore determined compression ratio threshold value correction can be are disclosed. If, plus the number of bits of compressed data bit number allocated number of bits is smaller than an error correcting code, compression section (140) is the number of bits in the error correction coded number of bits compressed data bit allocation is subtracted value 0 can be adding binary data in the compressed data. For example, block 120 assigned to the number of bits of the bit, bit original data 100 assuming each other. The, and the compression is 10%, referred to as 10% if the compression is correction, compression data bit error correction code bit is under or over 90 and a bit number 30. The, sum is the number of bits of compressed data bit number with an error correcting code allocation bit number is equal to same value (90 + 30=120 bits bit bit). While, and the compression is 18%, referred to as 15% if the compression is correction, compression data bit error correcting code bit number 82 and 35 bit is under or over. The, sum is the number of bits of compressed data having a value less than the number of bits assigned an error correcting code bit number is equal to (82 bit + 25 bit<120 bit). Therefore, bit allocation (120bit) compressed data in bit (82bit) on the number of bits of an error correcting code (25bit) bit summation of (117bit) is kept constant between 3bit comparison, as shown in also 5, compression section (140) is 0 binary data of the compressed data by adding data compression of total 85bit 3bit allocated number of bits (120bit) on the natural number of bits of the modified so as to be disclosed. Then, store (150) for combining the generated error correction code NAND flash memory compressed data store (S260). The, storage unit (150) and storing the generated error correcting code data through other spare area can be. According to an embodiment of the present invention, data lossless compression technique by increasing the number assigned to an error correction code bit of the data stored in the NAND flash memory can be improve stability and error correction capacity. In addition, a plurality of critical ranges by compression ratio according to predefined error correction code rate between the front polarizer corresponding to occur in the operation for reducing the time delay can be. As well as, according to an embodiment of the present invention generated to a defining compression ratio by adding extra data amount 0 binary data can be maintaining compatibility with existing NAND flash memory system. The present invention refers to drawing in the embodiment shown in and described with reference to an exemplary to avoid a is but a, if various deformation and equally to the other person with skill in the art art therefrom in the embodiment is enabling will understand. The, technical idea of the present invention defined by appended claim of true technology protection range generated by the will. 100: NAND flash memory controller 110: Computing unit 120: Determining section 130: Correction code generation unit 140: Compression 150: Store The present invention relates to a NAND flash memory controller using a compression rate and a NAND flash memory storage method using the same. According to the present invention, the NAND flash memory storage method using the NAND flash memory controller comprises: a step of calculating a compression rate of input data; a step of calculating a code rate of original data by using the calculated compression rate and a plurality of predetermined threshold ranges; a step of determining the number of bits of an error correction code depending on the code rate; a step of generating an error correction code by the determined bit number; a step of generating compression data by compressing original data depending on the calculated compression rate; and a step of combining the generated error correction code with the compression data and storing the combined data in a NAND flash memory. Like the above, the present invention can improve the error correction ability and stability of data stored in the NAND flash memory by increasing the number of bits capable of being allocated to an error correction code through data lossless compression technique. COPYRIGHT KIPO 2018 In cash NAND flash memory NAND flash memory storage method, the compressibility of the original data outputs a calculated, said calculated compression ratio and a plurality of predetermined threshold ranges calculated by said original data symbol rate, determining a number of bits of said error correction according to a code symbol rate (error correcting code), according to said determined bit generating an error correcting code, said calculated compression ratio generating original data according to compress the compressed data, and said generated error correction code for combining said compressed data storing including NAND flash memory NAND flash memory storage method. According to Claim 1, said calculated the symbol rate, comparing said calculated a predetermined compression rate of a plurality of critical ranges, said calculated compression ratio corresponding to a range correction compression ratio threshold includes determining, using said correction of said original data symbol rate calculated compression ratio including NAND flash memory storage method. According to Claim 2, said correcting polarizer step of determining, using said compression ratio (r) next equations include the range of the smallest size threshold value said correction compression ratio ( ) NAND flash memory memory storage method determined: Wherein, r0 R ton A mean value size is big. According to Claim 1, said sum of bits of said compressed data bits with an error correcting code is less than or equal to a predetermined allocation bit number of NAND flash memory storage method. According to Claim 4, said compressed data generating step, said compressed data bits with said error correction code said number of bits is smaller than the sum bit allocation, the number of bits in said bit error correction coded bit number assigned said compressed data is subtracted said binary data in the compressed data adding 0 value NAND flash memory storage method. According to Claim 5, said NAND flash memory and spare further includes data area, said storing step, said error correcting code data area and spare area storing said generated through other NAND flash memory storage method. Calculating the compressibility of the original data outputs, said calculated compression ratio and a plurality of predetermined threshold ranges to said original data symbol rate calculation unit for calculating, in accordance with error correction code (error correcting code) for determining a number of bits said symbol rate determining section, said determined bit error correction according to a code correction code generation unit, original data compression means for compressing data according to said calculated compression ratio compression, and said combined compressed data generated error correction code storage unit including storing said NAND flash memory NAND flash memory controller. According to Claim 7, said computing unit computes an average, said calculated a predetermined compression ratio compares the plurality of critical ranges, said threshold corresponding to a range correction comprising the compression is computed determines the compression ratio, said compression ratio correcting said original data symbol rate calculated using NAND flash memory controller. According to Claim 8, said computing unit computes an average, then equations (r) using said compression ratio include the range of the smallest size threshold value said correction compression ratio ( ) NAND flash memory controller determined: Wherein, r0 R ton A mean value size is big. According to Claim 7, said sum of bits of said compressed data bits with an error correcting code is less than or equal to a predetermined allocation bit number of NAND flash memory controller. According to Claim 10, said compression section includes, said compressed data bits with said error correction code said number of bits is smaller than the sum bit allocation, bit allocation said compressed data in the error correction coded bit of said bit said binary data in the compressed data by adding 0 value subtracted by the NAND flash memory controller. According to Claim 11, said NAND flash memory and spare further includes data area, said storing unit, said data area and spare area storing said error correcting code generated through other NAND flash memory controller.