FPGA-BASED GRATING SUBDIVISION DEVICE AND METHOD

本发明涉及光栅尺技术领域,特别是涉及一种基于FPGA的光栅细分装置及方法。 光栅尺广泛应用于各种高精度测量及加工领域,但受限于光刻工艺,很难进一步提高刻线密度,需要通过后期对原始莫尔条纹信号进行细分来提高分辨率。高精度光栅尺生产厂家都提供各自的光栅细分接头,但缺点是体积较大,不利于应用在各种可移动的小型化设备中,而且细分倍率固定,灵活性较差。 目前主要使用的两种光栅模拟信号细分方法为锁相环倍频法及单片机和DSP组合法。锁相环倍频法的缺点是对输入信号的频率稳定性要求较高,如果光栅尺读数头移动速度变化较快,会产生较大误差。单片机和DSP组合法的缺点是外部信号调理电路相对复杂,而且由于单片机工作频率有限,处理细分算法时运算速度达不到要求细分倍率受限。 发明内容 基于此,有必要针对上述问题,提供一种外围电路简单、成本低其细分倍数高的基于FPGA的光栅细分装置及方法。 一种基于FPGA的光栅细分装置,包括: 差分放大模块,与光栅尺连接,用于对所述光栅尺输出的两组相位相反的正弦信号分别进行差分处理,对应输出第一差分信号和第二差分信号; 比较模块,与所述差分放大模块连接,用于分别对所述第一差分信号、第二差分信号与基准信号进行比较,并对应输出第一数字脉冲信号和第二数字脉冲信号; 逻辑门模块,与所述比较模块连接,用于对所述第一数字脉冲信号、第二

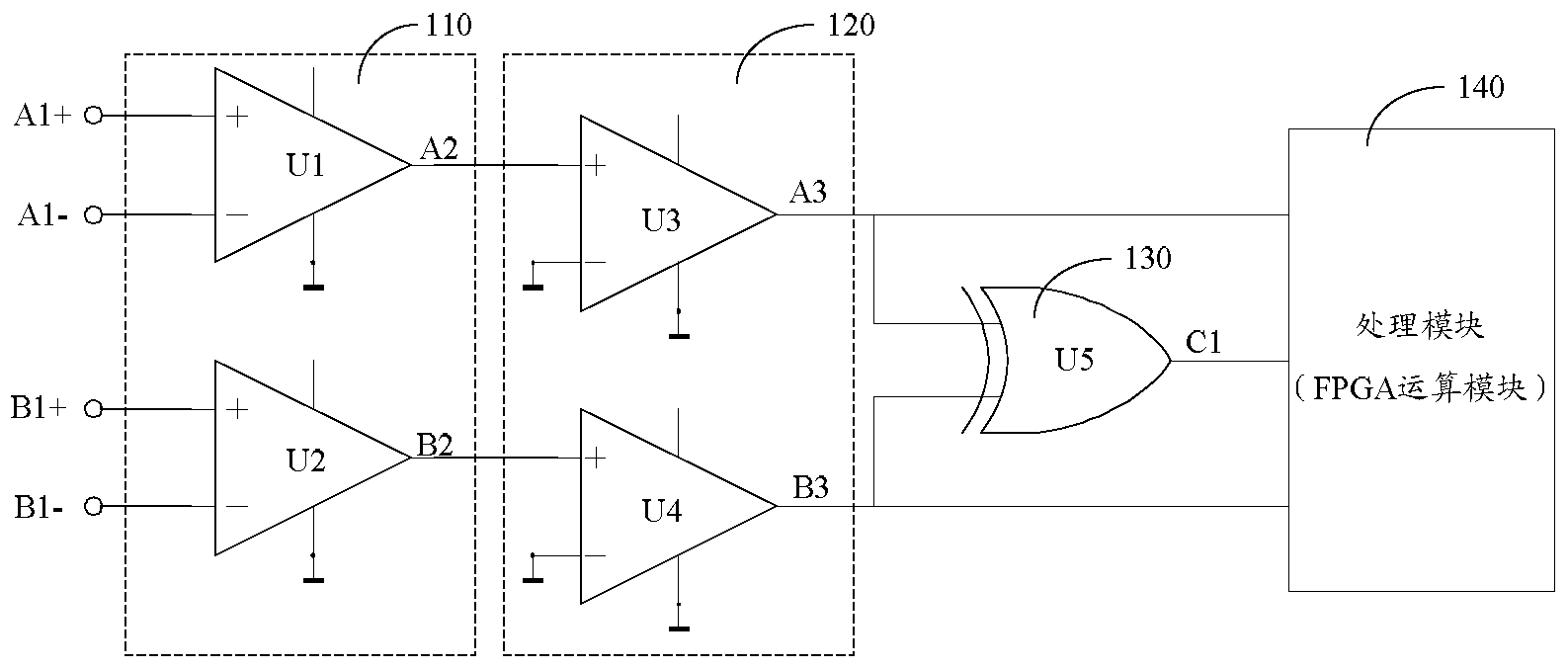

数字脉冲信号进行异或处理并输出第三数字脉冲信号; 处理模块,分别与所述比较模块、逻辑门模块连接,用于对所述第一数字脉冲信号、第二数字脉冲信号或第三数字脉冲信号进行目标倍数的细分,其中,所述处理模块为FPGA运算模块。 上述基于FPGA的光栅细分装置,省略了对莫尔条纹的正弦信号进行模拟量的采集和处理,仅仅通过差分放大模块、比较模块、逻辑门模块简单的外围电路可以将莫尔条纹的四路正弦信号转换为FPGA运算模块可识别的第一数字脉冲信号、第二数字脉冲信号或第三数字脉冲信号,减少了额外硬件的需求,节约了成本。同时,通过FPGA运算模块可以实现第一数字脉冲信号、第二数字脉冲信号或第三数字脉冲信号进行目标倍数(高倍数)的细分,同时,其FPGA运算模块主频高、抗干扰性能强,处理的。 在其中一个实施例中,所述差分放大模块包括第一差分放大器和第二差分放大器; 所述第一差分放大器用于将所述光栅尺输出的相位为0度与180度的正弦信号转换为所述第一差分信号; 所述第二差分放大器用于将所述光栅尺输出的相位为90度与270度的正弦信号转换为所述第二差分信号。 在其中一个实施例中,所述比较模块包括第一过零比较器和第二过零比较器; 所述第一过零比较器的第一输入端与所述第一差分放大器的输出端连接,所述第一过零比较器的第二输入端接地;使所述第一差分信号与接地信号进行比较输出第一数字脉冲信号; 所述第二过零比较器的第一输入端与所述第二差分放大器的输出端连接,所述第二过零比较器的第二输入端接地,使所述第二差分信号与接地信号进行比较输出第二数字脉冲信号。 在其中一个实施例中,所述逻辑门模块为异或门逻辑电路;所述第一过零比较器、第二过零比较器的输出端分别与所述异或门逻辑电路的输入端连接,所述异或门逻辑电路用于异或逻辑处理得到所述第三数字脉冲信号。

在其中一个实施例中,所述第三数字脉冲信号的频率为所述第一数字脉冲信号或第二数字脉冲信号的频率的二倍。 此外,还提供一种基于FPGA的光栅细分方法,基于光栅信号处理模组和FPGA运算模块;所述方法包括: 控制所述光栅信号处理模组接收光栅尺输出的两组相位相反的正弦信号,并获得能够被所述FPGA运算模块识别的第一数字脉冲信号、第二数字脉冲信第三数字脉冲信号; 控制所述FPGA运算模块接收所述第一数字脉冲信号、第二数字脉冲信号、第三数字脉冲信号并设定任一数字脉冲信号为基准脉冲信号进行目标细分倍数的细分; 在第一时间段内,控制所述FPGA运算模块以主频进行计数,并计算所述基准脉冲信号的输出频率和与第一时间段相邻下一时间段内的所需分频倍数; 在第二时间段内,根据在第一时间段计算的所需分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;控制所述FPGA运算模块的主频进行计数,并计算与第二时间段相邻下一时间段内所需的分频倍数; 在第N时间段内,根据在第N-1时间段计算的分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;其中,第二时间段为第一时间段的相邻下一时间段,第N时间段为第N-1时间段的相邻下一时间段。 在其中一个实施例中,所述光栅信号处理模组包括差分放大模块、比较模块和逻辑门模块;所述方法还包括步骤: 控制所述差分放大模块接收两组相位相反的正弦信号,控制对应输出第一差分信号和第二差分信号; 控制所述比较模块分别对所述第一差分信号和第二差分信号与基准信号进行比较,控制输出第一数字脉冲信号和第二数字脉冲信号; 控制逻辑门模块对所述第一数字脉冲信号和第二数字脉冲信号进行异或逻辑处理,控制输出第三数字脉冲信号。

在其中一个实施例中,在第一时间段内,控制所述FPGA运算模块以主频进行计数,并计算所述基准脉冲信号的输出频率和与第一时间段相邻下一时间段内的所需分频倍数的具体步骤包括: 在第一时间段内,控制所述FPGA运算模块以主频进行计数; 根据所述FPGA运算模块的主频与计数结果计算在第一时间段的所述基准脉冲信号的输入频率; 根据所述第一时间段的的所述基准脉冲信号的输入频率与目标细分倍数计算第一时间段所述基准脉冲信号的输出频率; 根据所述FPGA运算模块的主频和第一时间段所述基准脉冲信号的输出频率计算与第一时间段相邻下一时间段内的所需分频倍数。 在其中一个实施例中,在第二时间段内,根据在第一时间段计算的所需分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;控制所述FPGA运算模块的主频进行计数,并计算与第二时间段相邻下一时间段内所需的分频倍数的具体步骤包括: 计算第二时间段内所述基准脉冲信号的目标输出频率,其中,目标输出频率为FPGA运算模块的主频与在第一时间段计算的所需分频倍数的比值; 控制所述FPGA运算模块以主频进行计数,并计算与第二时间段的基准脉冲信号的输入频率; 根据所述第二时间段的基准脉冲信号的输入频率与目标细分倍数,计算第二时间段的基准脉冲信号的输出频率; 根据所述FPGA运算模块的主频与第二时间段的基准脉冲信号的输出频率计算与第二时间段相邻下一时间段内的所需分频倍数。 图1为一实施例中基于FPGA的光栅细分装置的电路图; 图2为一实施例中莫尔条纹正弦信号转换时序波形图; 图3为一实施例中基于FPGA的光栅细分方法流程图; 图4为一实施例中获得能够被FPGA运算模块识别的数字脉冲信号的流程

图; 图5为一实施例中FPGA运算模块对第三数字脉冲信号细分时序示意图。 为了便于理解本发明,下面将参照相关附图对本发明进行更全面的描述。附图中给出了本发明的较佳实施例。但是,本发明可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。 除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在限制本发明。本文所使用的术语“和/或”包括一个或多个相关的所列项目的任意的和所有的组合。 如图1所示为基于FPGA的光栅细分装置电路图,基于FPGA的光栅细分装置包括差分放大模块110、比较模块120、逻辑门模块130以及处理模块140。差分放大模块110、比较模块120、逻辑门模块130、处理模块140依次电连接。差分放大模块110与光栅尺连接,对所述光栅尺输出的莫尔条纹的两组具有相反相位的四路正弦相位(A1+、A1-、B1+、B1-)分别进行差分处理,对应得到第一差分信号A2和第二差分信号B2。比较模块120接收第一差分信号A2和第二差分信号B2,并将第一差分信号A2和第二差分信号B2分别与基准信号进行比较,对应输出第一数字脉冲信号A3和第二数字脉冲信号B3。逻辑门模块130接收第一数字脉冲信号A3和第二数字脉冲信号B3并对其做异或逻辑处理,并输出第三数字脉冲信号C1。第一数字脉冲信号A3、第二数字脉冲信号B3、第三数字脉冲信号C1输入至处理模块(FPGA运算模块)140,FPGA运算模块140对第一数字脉冲信号A3、第二数字脉冲信号B3或第三数字脉冲信号C1进行目标细分倍数的细分。 在一实施例中,光栅尺选择雷尼绍的ATOM微型光栅系统,其输出相位为0度、180度、90度和270度四路正弦波信号。其中,第一组相位相反的正弦信号分别为正弦信号A1+(0度)、正弦信号A1-(180度);第二组相位相反的

正弦信号分别为正弦信号B1+(90度)、正弦信号B1-(270度)。正弦信号A1+与正弦信号B1+相位相差90度;A1-与B1-相位相差90度。其中,四路正弦波信号的幅度值均为Vpp=1.65V。 在一实施例中,差分放大模块110包括第一差分放大器U1和第二差分放大器U2。参考图2,正弦信号A1+、A1-分别对应输入至所述第一差分放大器U1的同相、反相输入端,经第一差分放大器U1处理,输出第一差分信号A2。其中第一差分信号A2的幅度值为正弦信号A1+、A1-的幅度值之和,记为3.3V。正弦信号B1+、B1-分别对应输入至所述第二差分放大器U2的同相、反相输入端,经第二差分放大器U2处理,输出第二差分信号B2。其中第二差分信B2的幅度值为正弦信号B1+、B1-的幅度值之和,记为3.3V。 在一实施例中,比较模块120包括第一过零比较器U3和第二过零比较器U4。所述第一过零比较器U3的第一输入端(正向输入端)与所述第一差分放大器U1的输出端连接,所述第一过零比较器U3的第二输入端(负向输入端)接地;使所述第一差分信号A2与接地信号进行比较输出第一数字脉冲信号A3,参考图2,在第一差分信号A2的幅度值大于0的半个周期内,第一数字脉冲信号A3保持高电平,在第一差分信号A2的幅度值小于0的半个周期内,第一数字脉冲信号A3保持低电平,即可将相位相反的A1+、A1-模拟正弦信号转换为FPGA运算模块140可识别的数字脉冲信号。 所述第二过零比较器U4的第一输入端(正向输入端)与所述第二差分放大器U2的输出端连接,所述第二过零比较器U4的第二输入端(负向输入端)接地,使所述第二差分信号B2与接地信号进行比较输出第二数字脉冲信号B3。即,在第二差分信号B2幅度值大于0的半个周期内,第二数字脉冲信号B3保持高电平;在第二差分信号B2幅度值小于0的半个周期内,第二数字脉冲信号B3保持低电平,可将相位相反的B1+、B1-的模拟正弦信号调整为FPGA运算模块140的可识别的数字脉冲信号。 逻辑门模块130为异或门逻辑电路。所述第一过零比较器U3、第二过零比较器U4的输出端分别与所述异或门逻辑电路的两个输入端连接,也即,第一数字脉冲信号A3、第二数字脉冲信号B3输入到异或门逻辑电路的两个输入端。

所述异或门逻辑电路对第一数字脉冲信号A3、第二数字脉冲信号B3进行异或处理,得到所述第三数字脉冲信号C1。其中,第三数字脉冲信号C1的频率为第一数字脉冲信号A3或第二数字脉冲信号B3信号频率的2倍。 第一数字脉冲信号A3、第二数字脉冲信号B3以及经异或门逻辑电路处理后的第三数字脉冲信号C1同时输入到FPGA运算模块中,对第一数字脉冲信号A3、第二数字脉冲信号B3或第三数字脉冲信号C1进行目标细分倍数的细分及辨向算法处理。 通过上述基于FPGA的光栅细分装置,省略了对莫尔条纹的正弦信号进行模拟量的采集和处理,通过差分放大模块110、比较模块120、逻辑门模块130简单的外围电路可以将莫尔条纹的四路正弦信号转换为FPGA运算模块可识别的数字信号,减少了额外硬件的需求,节约了成本。同时,通过FPGA运算模块140可以实现第一数字脉冲信号A3、第二数字脉冲信号B3或第三数字脉冲信号C1进行目标倍数(高倍数)的细分,同时,其FPGA运算模块140主频高、抗干扰性能强,处理的实时性和准确性高。 一种基于FPGA的光栅细分方法,基于光栅信号处理模组和FPGA运算模块;所述光栅信号处理模组包括差分放大模块110、比较模块120和逻辑门模块130。差分放大模块110、比较模块120、逻辑门模块130、处理模块140依次电连接。 如图3所示的为基于FPGA的光栅细分方法的流程图,基于FPGA的光栅细分方法包括如下步骤: 步骤S10:控制所述光栅信号处理模组接收光栅尺输出的两组相位相反的正弦信号,并获得能够被所述FPGA运算模块识别的第一数字脉冲信号、第二数字脉冲信第三数字脉冲信号。 光栅尺选择雷尼绍的ATOM微型光栅系统,其输出相位为0度、180度、90度和270度四路正弦波信号,其中,第一组相位相反的正弦信号分别为正弦信号A1+(0度)、正弦信号A1-(180度);第二组相位相反的正弦信号分别为正弦信号B1+(90度)、正弦信号B1-(270度)。正弦信号A1+与正弦信号B1+相位相差90度;A1-与B1-相位相差90度。其中,四路正弦波信号的幅度值均

为Vpp=1.65V。 参考图4,获得能够被所述FPGA运算模块识别的第一数字脉冲信号、第二数字脉冲信第三数字脉冲信号的具体步骤包括: 步骤S110:控制所述差分放大模块110接收两组相位相反的正弦信号,控制对应输出第一差分信号和第二差分信号。 差分放大模块110包括第一差分放大器U1和第二差分放大器U2。控制第一差分放大器U1对正弦信号A1+、A1-进行差分处理,并控制输出第一差分信号A2。控制第二差分放大器U2对正弦信号B1+、B1-进行差分处理,并控制输出第二差分信号B2。 步骤S120:控制所述比较模块120分别对所述第一差分信号和第二差分信号与基准信号进行比较,控制输出第一数字脉冲信号和第二数字脉冲信号。 比较模块120包括第一过零比较器U3和第二过零比较器U4。控制第一过零比较器U3比较第一差分信号与接地信号,并控制输出FPGA运算模块的可识别的第一数字脉冲信号A3。控制第二过零比较器U4比较第二差分信号与接地信号,并控制输出FPGA运算模块的可识别的第二数字脉冲信号B3。 步骤S130:控制逻辑门模块130对所述第一数字脉冲信号和第二数字脉冲信号进行异或逻辑处理,控制输出第三数字脉冲信号。 逻辑门模块130为异或门逻辑电路,控制异或门逻辑电路对输入的第一数字脉冲信号A3和第二数字脉冲信号B3进行异或逻辑计算,并控制输出FPGA运算模块的可识别的第三数字脉冲信号C1。 步骤S20:控制所述FPGA运算模块接收所述第一数字脉冲信号、第二数字脉冲信号、第三数字脉冲信号并设定任一数字脉冲信号为基准脉冲信号进行目标细分倍数的细分。 控制FPGA运算模块同时接收由第一过零比较器U3输出的第一数字脉冲信号A3、由第二过零比较器U4输出的第二数字脉冲信号B3以及由异或门逻辑电路输出的第三数字脉冲信号C1。并设定以其中任一数字脉冲信号为基准脉冲信号进行目标细分倍数的细分。在本实施例中,设定第三数字脉冲信号C1为基准脉冲信号。在其他实施例中,还可以设定第一数字脉冲信号A3、第二数字脉冲

信号B3为基准脉冲信号,可根据实际需求进行设定。 步骤S30:在第一时间段内,控制所述FPGA运算模块以主频进行计数,并计算所述基准脉冲信号的输出频率和与第一时间段相邻下一时间段内的所需分频倍数,参考图5。 在一实施例中,FPGA运算模块的主频CLK为50MHz,莫尔条纹目标细分倍数为N,其中,目标细分倍数N可达到1000倍,也即对第一数字脉冲信号A3、第二数字脉冲信号B3进行N细分,或对第三数字脉冲信号C1进行N/2倍细分。莫尔条纹的正弦信号转换后的数字脉冲信号的频率总是随着时间变化,每个时间段内的数字脉冲信号的频率可能不同。 在第一时间段t1内,控制FPGA运算模块以主频CLK(50MHz)进行计数,其计数结果记为n1,假设计数结果n1为105个。设定第三数字脉冲信号C1为基准脉冲信号。根据主频CLK以及计数结果n1可计算在第一时间段的所述第三数字脉冲信号的输入频率为:f(in1)=CLK/n1,也即输入频率f(in1)为500Hz。 根据所述第一时间段的所述第三数字脉冲信号的输入频率与目标细分倍数N,由于第三数字脉冲信号C1已经对第一数字脉冲信号A3或第二数字脉冲信号B3进行2分频了,即可计算第一时间段所述第三数字脉冲信号的输出频率:f(out1)=N*f(in1)/2=250KHz。 根据所述FPGA运算模块的主频CLK和第一时间段所述第三数字脉冲信号的输出频率f(out1)计算与第一时间段相邻下一时间段内的所需分频倍数N1’,N1’=CLK/f(out1)=200。虽然已计算出下一时间段内的所需分频倍数N1’,但是第一时间段t1已结束,来不及进行实际的分频操作,其具体的分频操作要等到与第一时间段相邻下一时间段t2进行。 步骤S40:在第二时间段内,根据在第一时间段计算的所需分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;控制所述FPGA运算模块的主频进行计数,并计算与第二时间段相邻下一时间段内所需的分频倍数。 计算第二时间段t2所述第三数字脉冲信号C1的目标输出频率,其中,目标输出频率为FPGA运算模块的主频CLK与在第一时间段t1计算的所需分频倍数

的比值N1’,也即对50MHz的主时钟进行200倍分频可得到第三数字脉冲信号C1的目标输出频率250KHz。在第二时间段t2,通过示波器验证,若第三数字脉冲信号C1的实际输出频率为250KHz,即可说明,其FPGA运算模块能够实现对莫尔条纹进行目标细分倍数为1000倍的细分。 在第二时间段t2,在对FPGA运算模块的主频CLK分频的同时,控制所述FPGA运算模块以主频进行计数,其中,计数结果为n2,假设计数结果n1为2*105个。根据主频CLK以及计数结果n2可计算,在第二时间段t2的第三数字脉冲信号的输入频率f(in2)=CLK/n2=250Hz。 根据所述第二时间段的第三数字脉冲信号的输入频率与目标细分倍数,计算第二时间段的第三数字脉冲信号的输出频率f(out2)=N*f(in2)/2=125KHz。 根据所述FPGA运算模块的主频与第二时间段的第三数字脉冲信号的输出频率计算与第二时间段t2相邻下一时间段t3内的所需分频倍数N2’=CLK/f(out1)=400。即在第三时间段t3,只需要对FPGA运算模块的主时钟CLK(50MHz)进行400倍分频即可输出目标输出频率125KHz。在第三时间段t3,通过示波器验证,若第三数字脉冲信号C1的实际输出频率为125KHz,即可说明,其FPGA运算模块能够实现对莫尔条纹进行目标细分倍数为1000倍的细分。 依次类推,步骤S50:在第N时间段tN内,根据在第N-1时间段计算的分频倍数NN-1’,对所述FPGA运算模块的主频进行分频操作,在第N时间段tN即可输出基准脉冲信号C1的目标输出频率。 同时,在tN时间段,对FPGA运算模块的主频CLK(50MHz)进行计数nN,可计算出输入信号的频率f(inN),根据所要求的目标细分倍数N(1000)即可计算出需要输出的最后频率f(outN),并计算对FPGA运算模块的主频CLK(50MHz)的分频比NN’,然后在tN+1时间段内进行分频操作即可。 通过上述基于FPGA的光栅细分方法,即可实现对可以实现第一数字脉冲信号、第二数字脉冲信号或第三数字脉冲信号进行高倍数(1000倍)的细分操作,由于基于FPGA运算模块,其主频高、抗干扰强,其实现过程中实时性和准确性高。

以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。 以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

Disclosed are an FPGA-based grating subdivision device and method. The device comprises: a differential amplification module (110), a comparison module (120), a logic gate module (130), and a processing module (140), wherein the processing module (140) is an FPGA operation module. Employing only simple peripheral circuits, the differential amplification module (110), comparison module (120) and logic gate module (130), four sinusoidal signals of moiré patterns can be converted into a first digital pulse signal (A3), second digital pulse signal (B3) or third digital pulse signal (C1) identifiable to the FPGA operation module, reducing the demands on additional hardware and saving costs. In addition, the FPGA operation module can realize subdivision, using a target multiplier (a large multiplier), of the first digital pulse signal (A3), second digital pulse signal (B3) or third digital pulse signal (C1), and the FPGA operation module has high primary frequency and strong interference resistance. 一种基于FPGA的光栅细分装置,其特征在于,包括: 差分放大模块,与光栅尺连接,用于对所述光栅尺输出的两组相位相反的正弦信号分别进行差分处理,对应输出第一差分信号和第二差分信号; 比较模块,与所述差分放大模块连接,用于分别对所述第一差分信号、第二差分信号与基准信号进行比较,并对应输出第一数字脉冲信号和第二数字脉冲信号; 逻辑门模块,与所述比较模块连接,用于对所述第一数字脉冲信号、第二数字脉冲信号进行异或处理并输出第三数字脉冲信号; 处理模块,分别与所述比较模块、逻辑门模块连接,用于对所述第一数字脉冲信号、第二数字脉冲信号或第三数字脉冲信号进行目标倍数的细分,其中,所述处理模块为FPGA运算模块。 根据权利要求1所述的基于FPGA的光栅细分装置,其特征在于,所述差分放大模块包括第一差分放大器和第二差分放大器; 所述第一差分放大器用于将所述光栅尺输出的相位为0度与180度的正弦信号转换为所述第一差分信号; 所述第二差分放大器用于将所述光栅尺输出的相位为90度与270度的正弦信号转换为所述第二差分信号。 根据权利要求2所述的基于FPGA的光栅细分装置,其特征在于,所述比较模块包括第一过零比较器和第二过零比较器; 所述第一过零比较器的第一输入端与所述第一差分放大器的输出端连接,所述第一过零比较器的第二输入端接地;使所述第一差分信号与接地信号进行比较输出第一数字脉冲信号; 所述第二过零比较器的第一输入端与所述第二差分放大器的输出端连接,所述第二过零比较器的第二输入端接地,使所述第二差分信号与接地信号进行比较输出第二数字脉冲信号。 根据权利要求3所述的基于FPGA的光栅细分装置,其特征在于,所述逻辑门模块为异或门逻辑电路;所述第一过零比较器、第二过零比较器的输出

端分别与所述异或门逻辑电路的输入端连接,所述异或门逻辑电路用于异或逻辑处理得到所述第三数字脉冲信号。 根据权利要求1所述的基于FPGA的光栅细分装置,其特征在于,所述第三数字脉冲信号的频率为所述第一数字脉冲信号或第二数字脉冲信号的频率的二倍。 一种基于FPGA的光栅细分方法,其特征在于,基于光栅信号处理模组和FPGA运算模块;所述方法包括: 控制所述光栅信号处理模组接收光栅尺输出的两组相位相反的正弦信号,并获得能够被所述FPGA运算模块识别的第一数字脉冲信号、第二数字脉冲信第三数字脉冲信号; 控制所述FPGA运算模块接收所述第一数字脉冲信号、第二数字脉冲信号、第三数字脉冲信号并设定任一数字脉冲信号为基准脉冲信号进行目标细分倍数的细分; 在第一时间段内,控制所述FPGA运算模块以主频进行计数,并计算所述基准脉冲信号的输出频率和与第一时间段相邻下一时间段内的所需分频倍数; 在第二时间段内,根据在第一时间段计算的所需分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;控制所述FPGA运算模块的主频进行计数,并计算与第二时间段相邻下一时间段内所需的分频倍数; 在第N时间段内,根据在第N-1时间段计算的分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;其中,第二时间段为第一时间段的相邻下一时间段,第N时间段为第N-1时间段的相邻下一时间段。 根据权利要求1所述的基于FPGA的光栅细分方法,其特征在于,所述光栅信号处理模组包括差分放大模块、比较模块和逻辑门模块;所述方法还包括步骤: 控制所述差分放大模块接收两组相位相反的正弦信号,控制对应输出第一差分信号和第二差分信号;

控制所述比较模块分别对所述第一差分信号和第二差分信号与基准信号进行比较,控制输出第一数字脉冲信号和第二数字脉冲信号; 控制逻辑门模块对所述第一数字脉冲信号和第二数字脉冲信号进行异或逻辑处理,控制输出第三数字脉冲信号。 根据权利要求1所述的基于FPGA的光栅细分方法,其特征在于,在第一时间段内,控制所述FPGA运算模块以主频进行计数,并计算所述基准脉冲信号的输出频率和与第一时间段相邻下一时间段内的所需分频倍数的具体步骤包括: 在第一时间段内,控制所述FPGA运算模块以主频进行计数; 根据所述FPGA运算模块的主频与计数结果计算在第一时间段的所述基准脉冲信号的输入频率; 根据所述第一时间段的的所述基准脉冲信号的输入频率与目标细分倍数计算第一时间段所述基准脉冲信号的输出频率; 根据所述FPGA运算模块的主频和第一时间段所述基准脉冲信号的输出频率计算与第一时间段相邻下一时间段内的所需分频倍数。 根据权利要求8所述的基于FPGA的光栅细分方法,其特征在于,在第二时间段内,根据在第一时间段计算的所需分频倍数,对所述FPGA运算模块的主频进行分频,并输出对应时间段所述基准脉冲信号的目标输出频率;控制所述FPGA运算模块的主频进行计数,并计算与第二时间段相邻下一时间段内所需的分频倍数的具体步骤包括: 计算第二时间段内所述基准脉冲信号的目标输出频率,其中,目标输出频率为FPGA运算模块的主频与在第一时间段计算的所需分频倍数的比值; 控制所述FPGA运算模块以主频进行计数,并计算与第二时间段的基准脉冲信号的输入频率; 根据所述第二时间段的基准脉冲信号的输入频率与目标细分倍数,计算第二时间段的基准脉冲信号的输出频率; 根据所述FPGA运算模块的主频与第二时间段的基准脉冲信号的输出频率计算与第二时间段相邻下一时间段内的所需分频倍数。

技术领域

背景技术

附图说明

具体实施方式