Балансный усилитель

1 Предлагаемое изобретение относится к области вычислительной техники и может быть

применено в оперативных запоминающих устройствах (ОЗУ) большой емкости и повышениой

надежности и предназначено для компенсации помехи от полувозбужденных сердечников. Извествы балансные усилители, содержащие два транзистора, эмиттеры и коллекторы

которых через соответствующие резисторы соединены с нсточниками питания, эмиттеры

транзисторов соединены между собой, через конденсатор, а базы подключены к источнику входного сигнала.

Предлагаемый усилитель отличается тем, что между эмиттерами транзисторов последовательно

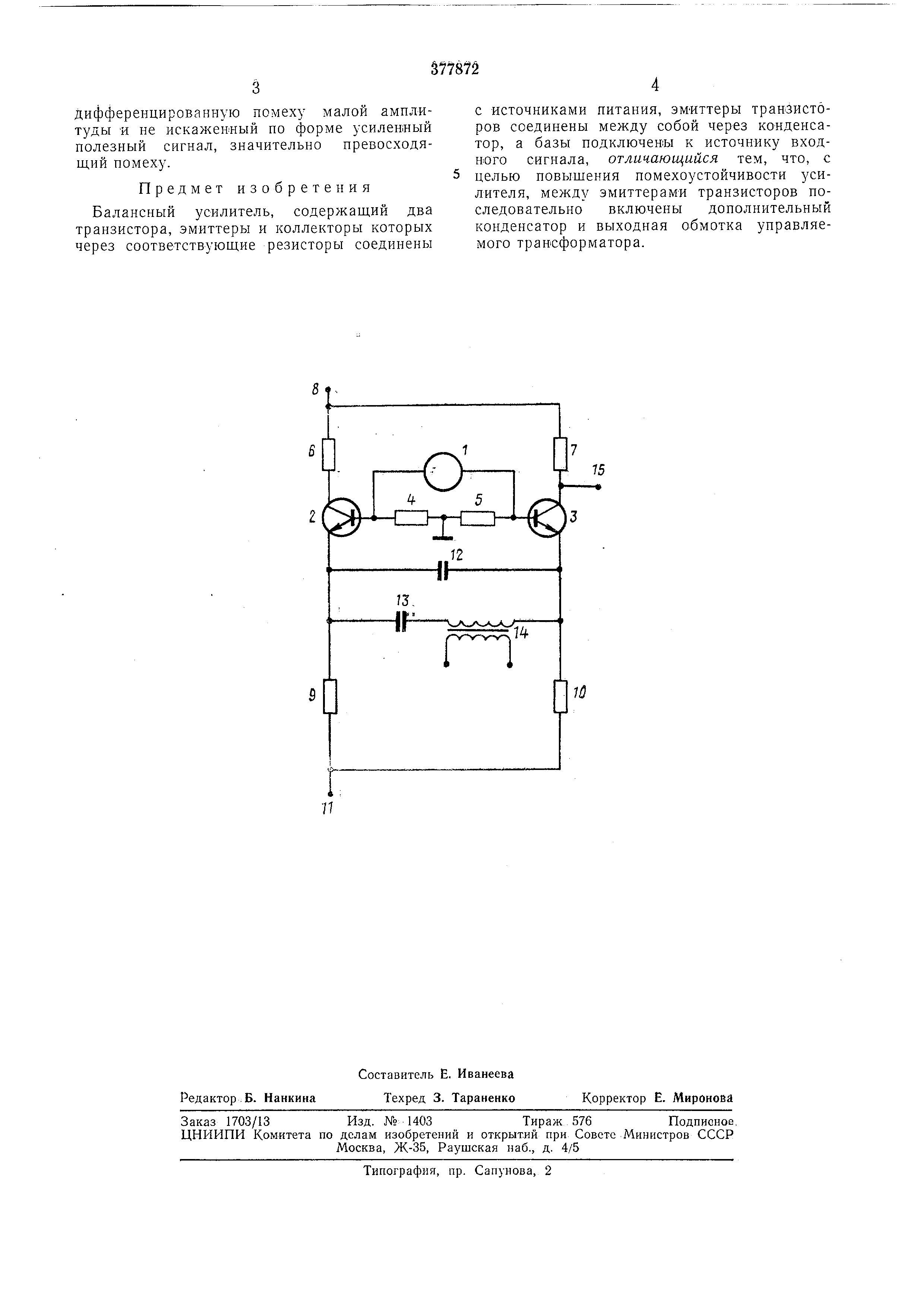

включены дополнительный конденсатор и выходная обмотка управляемого трансформатора. Это позволяет повысить помехоустойчивость усилителя. Схема балансного усилителя оперативного запоминающего устройства большой емкости приведена на чертеже.

Обмотка считывания 1 подсоединяется к базам балансно включенных транзисторов 2

и 5. Базы транзисторов через сопротивления 4 -л 5 заземлены. Коллекторы транзисторов

через сопротивления 6 и 7 подсоединены к источнику питания 8, а эмиттеры через сопротивления 9, 10-к источнику питания //. Между эмиттерами подсоединены емкости 12

и 13. Последовательно с емкостью 13 соедиiteHi управляемый трансформатор 14. При считывании информации из ОЗУ на выход считывающей обмотки / поступает полезный

сигнал совместно с помехой от разности падений напряжения на адресно-разрядных обмотках. До момента поступления полезного сигнала управляемый трансформатор 14 имеет

максимальное сопротивление, и постоянная времени входной цепи балансного усилителя

определяется в основном емкостью 12, величина которой выбирается так, чтобы помеха

от разности падений напряжения на адресноразрядных обмотках, начинающаяся до появления

полезного , была бы сведена к нулю. За время прохождения полезного

управляемый трансформатор 14 имеет нулевое сопротивление относительно сигнала, и

постоянная времени входной цепи усилителя определяется в основном величиной емкости

13, которая значительна по отношению к величине емкости 12. На выходе /5 балансного

усилителя имеем усиленный и неискаженный полезный сигнал. Итак, на выходе балансного усилителя считывания при поступлении помехи имеем 3 дифференцированную помеху малой амплитуды

и не искаженный по форме усиленный полезный сигнал, значительно превосходящий помеху. Предмет изобретения Балансный усилитель, содержащий два

транзистора, эмнттеры и коллекторы которых через соответствующие резисторы соединены с источниками питания, эмиттеры транзисторов соединены между собой через конденсатор

, а базы подключены к источнику входного сигнала, отличающийся тем, что, с

целью повыщения помехоустойчивости усилителя , между эмиттерами транзисторов последовательно

включены дополнительный конденсатор и выходная обмотка управляемого трансформатора.

13