Verfahren und Vorrichtung zum Zugriff auf versteckte Daten in einer Boundary Scan Testschnittstelle

Eine Vorrichtung und ein Verfahren zum Zugriff auf versteckte Daten in einer Boundary Scan Testschnittstelle wird offenbart, das eine Ungültiger-Zustandsübergang-Schleife in einer Boundary Scan Testschnittstelle definiert und anfangs eine Eingabe des Zustandsübergangsdiagramms der Boundary Scan Testschnittstelle überwacht, so dass eine Eingabe erster Daten erzeugt wird, wenn ein erster vorbestimmter Eingabestrom entdeckt wird, der konform geht mit der Ungültiger-Zustandsübergang-Schleife, und als nächstes eine Ausgabe zweiter Daten erzeugt wird, wenn ein zweiter vorbestimmter Eingabestrom entdeckt wird, der konform geht mit der Ungültiger-Zustandsübergang-Schleife, worin, wenn ein Eingabeschlüssel, der in einer Kombination der ersten und der zweiten Daten enthalten ist, mit einem vorbestimmten Schreibschlüssel abgeglichen wird, spezifische Schreibdaten in ein verstecktes Register geladen werden.

HINTERGRUND DER ERFINDUNG 1. Gebiet der Erfindung

[0001] Die vorliegende Erfindung bezieht sich auf das technische Gebiet einer Boundary ScanTestschnittstelle, und genauer auf eine Vorrichtung und ein Verfahren zum Zugriff auf versteckteDaten in einer Boudary Scan Testschnittstelle.

Stand der Technik

2. Beschreibung der verwandten Technik

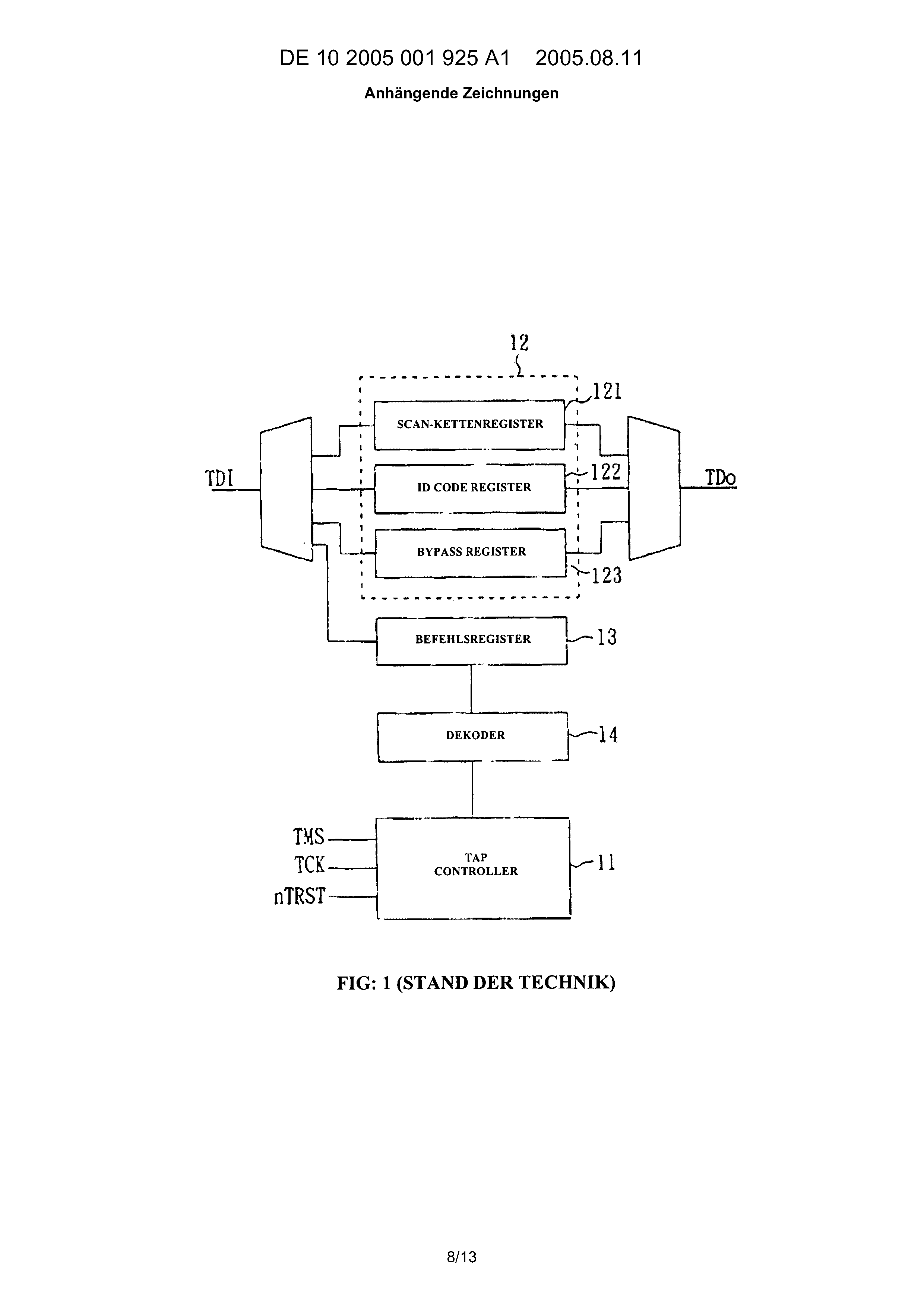

[0002] Da Chippakete und Mehrebenen-Leiterplatten (PCBs) immer komplizierter geworden sind,ist der konventionelle Test im Schaltkreis, der ein Nagelbett verwendet, nicht zufrieden stellend,da es schwierig ist, die Knoten auf einer PCB präzise zu kontaktieren. Wegen des Fortschrittsder Oberflächenmontage-Technologie (Surface Mount Technology SMT) werden die meisten ICs darüberhinaus direkt auf die Oberfläche einer Leiterplatte montiert, was das Problem mit sich bringt,dass interne Signale der ICs nicht direkt getestet werden können. Um dem abzuhelfen, wurde dieBoundary Scan Technologie entwickelt. Die Joint Test Action Group (JTAG) Boundary Scan, früher IEEE-Std-1149.1und IEEE 1149.4 Digital Test Access Port Schnittstelle, definieren z.B. verfügbare BoundaryScan Testschnittstellen zum IC-Testen, das eine serielle Scan-Kette zum Testen der internenModule eines IC verwendet. Fig. 1 zeigt ein Blockdiagramm einer typischen JTAG Schnittstelle.In Fig. 1 benutzt die JTAG Schnittstelle fünf Signalpins (TDI, TDO, TMS, TCK und nTRST) in derScan-Ketten-Datenoperation, d.h.

[0003] TDI-Pin als serielle Dateneingabe, TDO-Pin als serielle Datenausgabe, TMS-Pin als Modusauswahleingabe,TCK-Pin als Takteingabe und nTRST-Pin als System-Reset. Wie in Fig. 1 dargestellt, beinhaltet dieJTAG-Schnittstelle einen Testzugangsport (Test Access Port TAP) Controller 11, ein Testdatenregister12, ein Befehlsregister 13 und einen Decoder 14.

[0004] Das Testdatenregister 12 beinhaltet ein Scan-Ketten-Register 121 als eine Scan-Kette, umserielle Daten zu speichern, die vom TDI-Pin erhalten wurden, ein ID-Code-Register 122, dasspezielle auszugebende Zahlen speichert, ein Bypass-Register 123, um die seriellen Daten direktvom TDI-Pin zum TDO-Pin zur Ausgabe weiterzuleiten.

[0005] Das Befehlsregister 13 speichert einen seriellen Befehl, der vom TDI-Pin erhalten wurde.Der Decoder 14 dekodiert den seriellen Befehl, um so die Operationen des TAP-Controllers 11zu steuern.

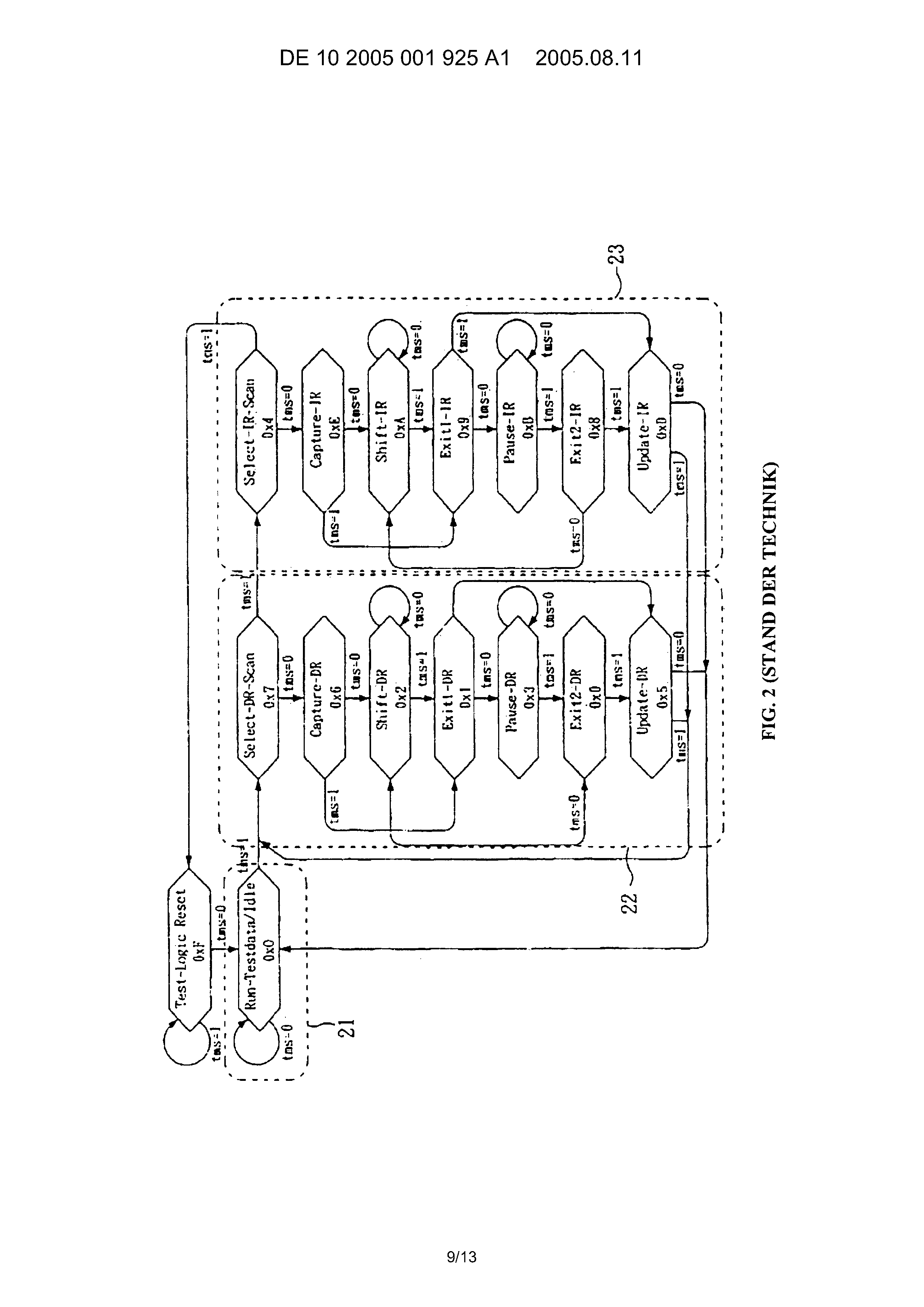

[0006] Der TAP-Controller 11 führt auf der Grundlage der Eingabe am TMS-Pin einen Zustandsübergang durchund arbeitet mit den Daten des Registers 12 und der Ausgabe des Decoders 14. Fig. 2 ist einZustandsübergangsdiagramm des TAP-Controllers 11, wobei ein Zustandsübergang beim Abgreifender TMS-Signaldaten bei den ansteigenden Flanken der TCK-Signalausgabe stattfindet. Wie in Fig. 2dargestellt ist, ist der TAP-Controller 11 anfangs in einem Test-Logic Reset (Test-Logik Reset)Zustand. Als nächstes kann der Controller 11 in die Zustände Leerlaufprozess 21, Datenregisterprozess22 und Befehlsregisterprozess 23 eintreten. Wenn TMS=1, bleibt der Test-Logic Reset Zustandunverändert, und wenn TMS=0, geht der Zustand in den Run-Test/Idle (Testlauf/Leerlauf) Zustanddes Leerlaufesprozesses 21 über. Als nächstes bleibt der Run-Test/Idle Zustand unverändert, wennTMS=0, und er geht in den Select-DR-Scan (DR-Scan-Auswahl) Zustand des Datenregisterprozesses22 über, wenn TMS=1. Im Select-DR-Scan Zustand geht der Zustand in den Capture-DR (DR-Laden)Zustand über, wenn TMS=0, zur Verarbeitung des Registers 12, und andernfalls, wenn TMS=1, gehtder Zustand in den Select-IR-Scan (IR-Scan-Auswahl) Zustand des Befehlsregisterprozesses 23über. Im Select-IR-Scan Zustand geht der Zustand, wenn TMS=0, in den Capture-IR (IR-Laden) Zustandüber. zur Verarbeitung des Registers 13, und andernfalls, wenn TMS=1, geht der Zustand in denanfänglichen Test-Logic Reset Zustand über.

[0007] Die oben erwähnte JTAG kann Steuersignale übertragen oder auf Register durch TDI- undTDO-Pins zum Lesen oder Schreiben von Daten zugreifen. Das Lesen und Schreiben von Daten durchTDI- und TDO-Pins sind jedoch sequentiell und können leicht entdeckt werden. Solche geheimenRegisterdaten können deshalb nicht geschützt werden. Derzeitige Prozessentwicklung muss jedochAusrüstung vor dem Stehlen durch andere schützen. Es ist daher wünschenswert, eine verbesserteVorrichtung und ein Verfahren zur Verfügung zu stellen, um die oben genannten Probleme zu lindernoder zu vermeiden.

Aufgabenstellung

ZUSAMMENFASSUNG DER ERFINDUNG

[0008] Eine Aufgabe der Erfindung ist es, eine Vorrichtung und ein Verfahren zum Zugriff aufversteckte Daten in einer Boundary Scan Testschnittstelle zur Verfügung zu stellen, die Datenlesen und schreiben kann, ohne durch Standarddaten-Eingabe-/Ausgabe-Pins zu gehen, und dadurchsicheren Zugriff für geheime Daten in der Boundary Scan Testschnittstelle erreicht.

[0009] Eine andere Aufgabe der Erfindung ist es, eine Vorrichtung und ein Verfahren zum Zugriff auf versteckte Daten in einer Boundary Scan Testschnittstelle zurVerfügung zu stellen, die geheime Daten als kompatibel mit der Boundary Scan Testschnittstellelesen und schreiben kann und die nicht vollständig den Zustand und Datenpfad der Boundary ScanTestschnittstelle beeinflusst.

[0010] Gemäß einer Eigenschaft der Erfindung wird eine Vorrichtung zum Zugriff auf versteckteDaten in einer Boundary Scan Testschnittstelle zur Verfügung gestellt.

[0011] Die Boundary Scan Testschnittstelle arbeitet mit einem vorbestimmten Zustandsübergangsdiagramm, umZustandsübergang auf der Grundlage einer Eingabe zu durchzuführen, wobei der durchgeführte Zustandsübergang mindestenseine Ungültiger-Zustandsübergang-Schleife beinhaltet. Die Vorrichtung beinhaltet: einen Zustandsdetektorzur Überwachung der Eingabe, um erste Daten auszugeben, wenn ein erster vorbestimmter Eingabestromentdeckt wird, und dann zweite Daten auszugeben, wenn ein zweiter vorbestimmter Eingabestromentdeckt wird, wobei der erste und der zweite vorbestimmte Eingabestrom verschieden sind undbeide mit einer Ungültiger-Zustandsübergang-Schleife konform gehen; ein Schieberegister zurSpeicherung einer Kombination der ersten und der zweiten Daten, wobei die Kombination einenEingabeschlüssel hat; ein verstecktes Register zur Datenspeicherung; und eine Vergleichsvorrichtung zumVergleich des Eingabeschlüssels mit einem vorbestimmten Schreibeschlüssel und zum Laden spezifischer Schreibdatenin das versteckte Register, wenn der Eingabeschlüssel gleich dem vorbestimmten Schreibschlüssel ist.

[0012] Gemäß einer weiteren Eigenschaft der Erfindung wird ein Verfahren zum Zugriff auf versteckteDaten in einer Boundary Scan Testschnittstelle zur Verfügung gestellt. Die Boundary Scan Testschnittellearbeitet mit einem vorbestimmten Zustandsübergangsdiagramm, um Zustandsübergang auf der Grundlageeiner Eingabe zu durchzuführen, wobei der durchgeführte Zustandsübergang mindestens eine Ungültiger-Zustandsübergang-Schleife beinhaltet.Das Verfahren beinhaltet die Schritte: (A) des Überwachens der Eingabe, um erste Daten auszugeben,wenn ein erster vorbestimmter Eingabestrom entdeckt wird, und dann zweite Daten auszugeben,wenn ein zweiter vorbestimmter Eingabestrom entdeckt wird, wobei der erste und der zweite vorbestimmteEingabestrom verschieden sind und beide mit der Ungültiger-Zustandsübergang-Schleife konformgehen; (B) des Zwischenspeicherns einer Kombination der ersten und der zweiten Daten, wobeidie Kombination einen Eingabeschlüssel hat; und (C) des Vergleichens des Eingabeschlüssels miteinem vorbestimmten Schreibschlüssel, so dass spezifische Schreibdaten in ein verstecktes Registergeladen werden, wenn der Eingabeschlüssel gleich dem vorbestimmten Schreibschlüssel ist.

Ausführungsbeispiel

[0013] Andere Aufgaben, Vorteile und neue Eigenschaften der Erfindung werden offensichtlicher werdenaus der folgenden detaillierten Beschreibung, wenn sie in Verbindung mit der beiliegenden Zeichnunggenommen wird.

KURZE BESCHREIBUNG DER ZEICHNUNG

[0014] Fig. 1 ist ein Blockdiagramm einer typischen JTAG-Schnittstelle;

[0015] Fig. 2 ist ein Zustandsübergangsdiagramm eines TAP-Controllers aus Fig. 1;

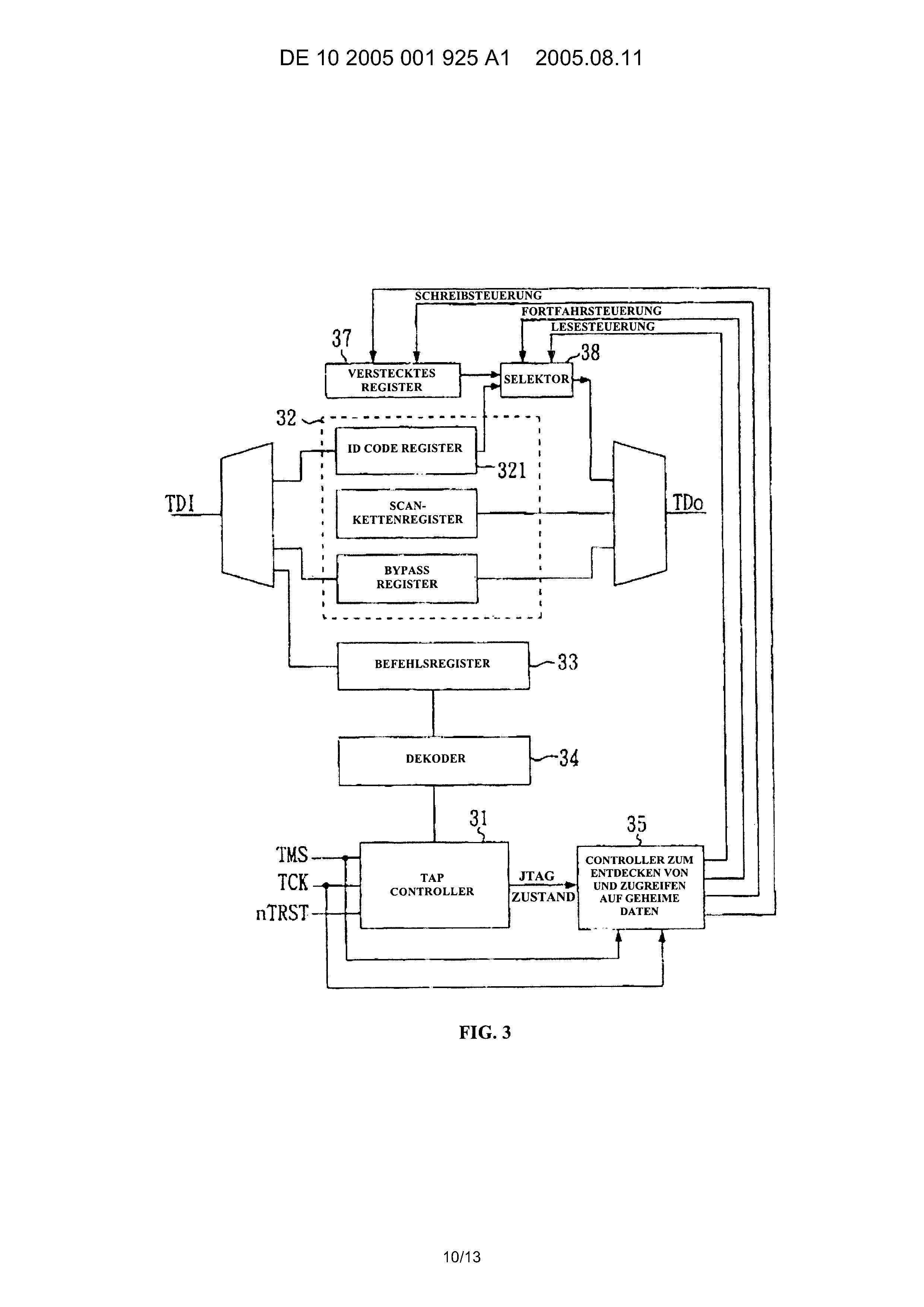

[0016] Fig. 3 ist ein Blockdiagramm einer Vorrichtung und eines Verfahrens zum Zugriff auf versteckteDaten in einer Boundary Scan Testschnittstelle gemäß der Erfindung;

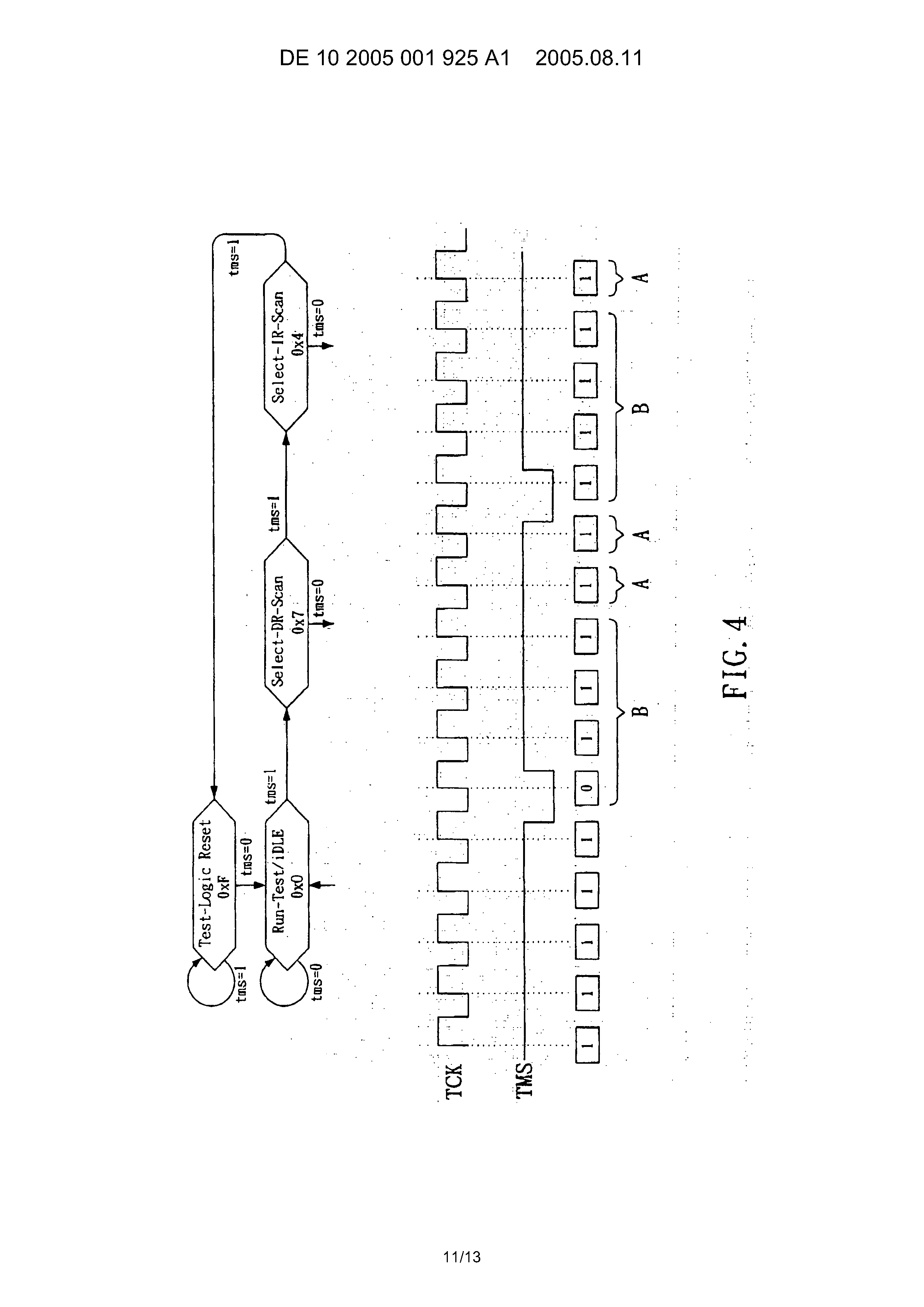

[0017] Fig. 4 ist ein Flussdiagramm einer Ungültiger-Zustandsübergang-Schleife in einem Zustandsübergangsdiagramm einesTAP-Controllers gemäß der Erfindung;

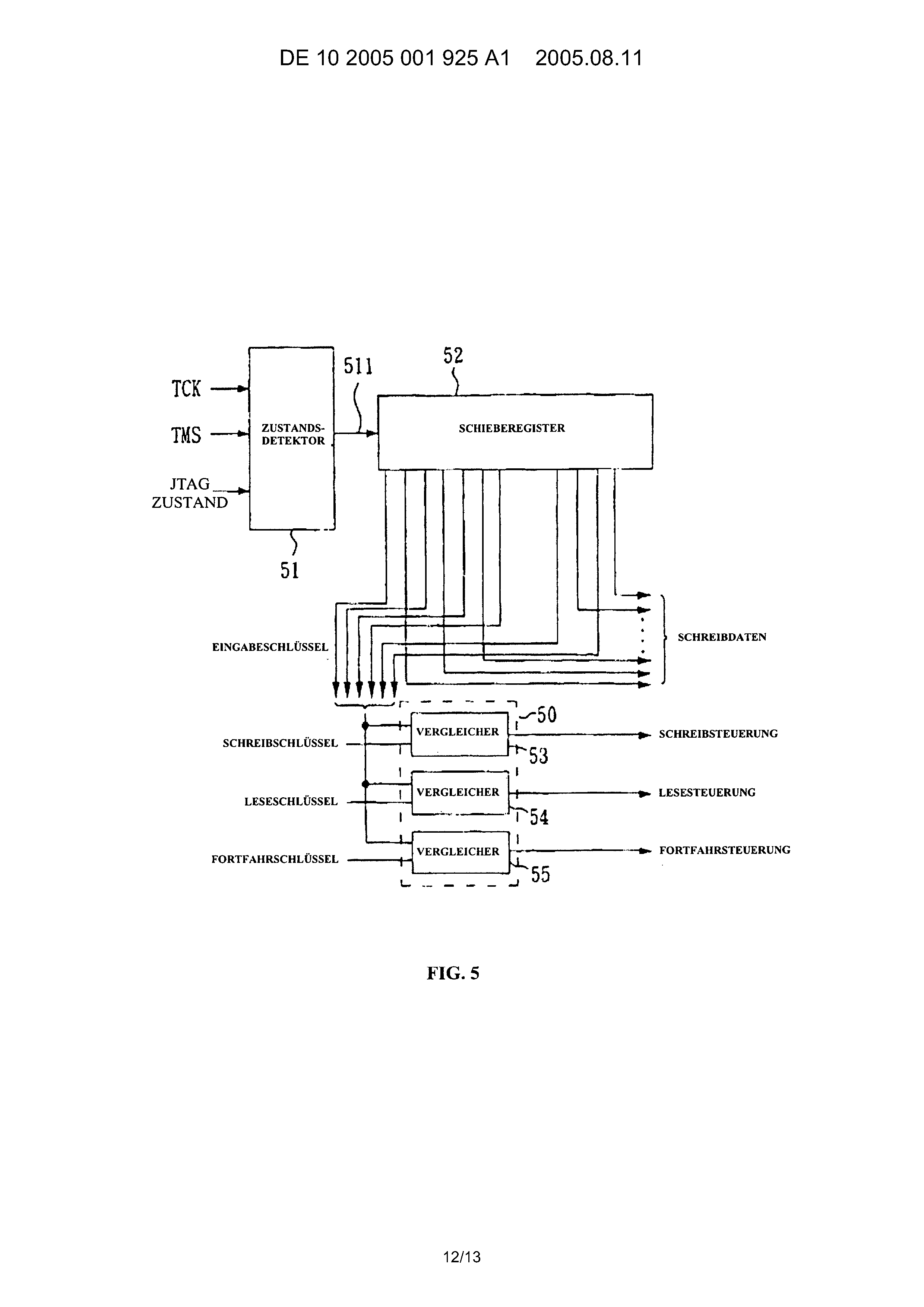

[0018] Fig. 5 ist ein Blockdiagramm eines Controllers zum Entdecken von und Zugreifen auf geheimeDaten aus Fig. 3 gemäß der Erfindung; und

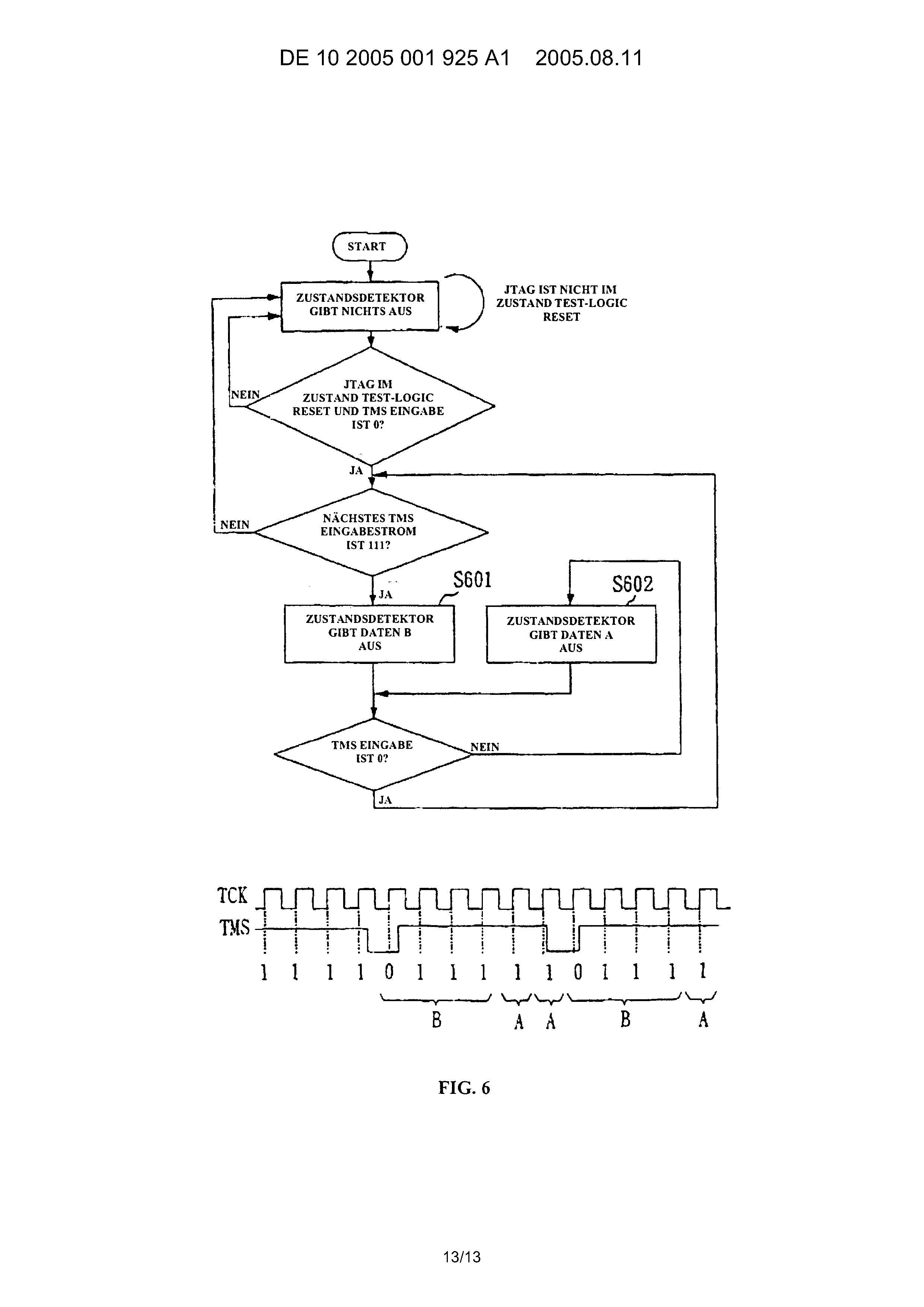

[0019] Fig. 6 ist ein Flussdiagramm einer Operation eines Zustandsdetektors aus Fig. 3 gemäßder Erfindung.

DETAILLIERTE BESCHREIBUNG DER BEVORZUGTEN AUSFÜHRUNGSFORM

[0020] Fig. 3 ist ein Blockdiagramm einer Vorrichtung zum Zugriff auf versteckte Daten in einerBoundary Scan Testschnittstelle gemäß der Erfindung. In Fig. 3 beinhaltet die Vorrichtung einenTAP-Controller 31, ein Testdatenregister 32, ein Befehlsregister 33, einen Decoder 34, einen Controller35 zum Entdecken von und Zugreifen auf geheime Daten, ein verstecktes Register 37 und einenSelektor 38. Die Boundary Scan Testschnittstelle kann JTAG, IEEE 1149.1, IEEE 1149.4 oder Ähnlichessein. In dieser Ausführungsform verwendet die Boundary Scan Testschnittstelle eine JTAG-Schnittstelle zurbeispielhaften Beschreibung. Entsprechend werden der TAP-Controller 31, das Testdatenregister32, das Befehlsregister 33 und der Decoder 34 mit dem JTAG-Standard betrieben, der Pins vonserieller Dateneingabe (Serial Data Input TDI), serieller Datenausgabe (Serial Data Output TDO),Modusauswahleingabe (Mode Selection Input TMS), Tak-teingabe (Clock Input TCK) und System-Reset (nTRST) verwendet, um die Scan-Kettendaten zu handhaben.Der Selektor 38 kann den Inhalt des ID-Coderegisters 321 im versteckten Register 37 oder dasTestdatenregister 32 zur Ausgabe wählen. Der Controller 35 zum Entdecken von und Zugreifen aufgeheime Daten kann geheimes Datenlesen und -schreiben auf der Grundlage einer TMS-Eingabe realisieren.

[0021] Mit Bezug noch einmal auf Fig. 2 ist das durch den JTAG-Standard definierte Zustandsübergangsdiagramm anfänglich imTest-Logic Reset Zustand. Um die JTAG-Schnittstelle inaktiv zu machen, ist eine Eingabe am TMS-Pinbei logischen 1en (d.h., es wird ununterbrochen eine Sequenz von ,1' eingegeben), um im Test-LogicReset Zustand zu bleiben. Wenn es gewünscht wird, die JTAG-Schnittstelle zu aktivieren, wirddie Eingabe am TMS-Pin nach logisch ,0' geändert, für einen Zustandsübergang. Um jedoch zu vermeiden,dass eine ,0' zufällig in einer ,1'-Sequenz auftritt und so die JTAG-Schnittstelle fälschlichaktiviert, kehrt der Zustandsübergang in den anfänglichen Test-Logic Reset Zustand über denSelect-DR-Scan und Select-IR-Scan Zustand zurück, wenn die Eingabe am TMS-Pin bei ,1' bleibt, nachdemder Run-Test/Idle Zustand betreten wurde durch Eingabe von ,0' am TMS-Pin. Eine Ungültiger-Zustandsübergang-Schleife wirdnämlich im Wesentlichen ausgeführt, ohne irgendeinen Zustand zu betreten, der eine tatsächliche Operationdurchführt, um dadurch eine fehlerhafte Operation zu vermeiden.

[0022] Fig. 4 zeigt weiterhin die oben erwähnte Ungültiger-Zustandsübergang-Schleife. Ein TMS-Eingabestrom,der mit der Ungültiger-Zustandsübergang-Schleife konform geht, wird keine tatsächliche Operation inder JTAG-Schnittstelle verursachen. Die Erfindung definiert daher mindestens zwei TMS-Eingabeströme, diemit der Ungültiger-Zustandsübergang-Schleife konform gehen, um zwei unterschiedliche EingabedatenA bzw. B darzustellen. In dieser Ausführungsform ist A binär ,0' und B ist binär ,1'. Wie inFig. 4 dargestellt, ist es bevorzugt, einen TMS-Eingabestrom von ,0111' als die Eingabedaten B(=1) zu definieren, und den nachfolgenden TMS-Eingabestrom von ,1' als die Eingabedaten A (=0).Da der Run-Testdata/Idle Zustand nicht verändert wird, wenn ,0' eingegeben wird, ist es darüber hinausanwendbar, einen TMS-Eingabestrom von ,00111' als die EingabedatenA oder B zu definieren, wobei 0 mindestens eine ,0' darstellt.

[0023] Fig. 5 zeigt ein Blockdiagramm des Controllers 35 aus Fig. 3 zum Entdecken von und Zugreifenauf geheime Daten. In Fig. 5 beinhaltet der Controller 35 zum Entdecken von und Zugreifen aufgeheime Daten einen Zustandsdetektor 51, ein Schieberegister 52 und eine Vergleichsvorrichtung50. Die Vergleichsvorrichtung 50 hat drei Vergleicher 53-55. Die Operation des Zustandsdetektors51 ist in Fig. 6 dargestellt. Wie in Fig. 6 dargestellt, wird auf TCK-Eingabe, TMS-Eingabe unddurch den TAP-Controller 31 erzeugten JTAG-Zustand hin, wenn ermittelt wird, dass der TAP-Controller31 im Test-Logic Reset Zustand ist, die Überwachung der TMS-Eingabe gestartet. Wenn ein TMS-Eingabestromvon ,0111' entdeckt wird, erzeugt die Datenausgabe 511 Daten B (=1) zur Ausgabe (Schritt S601).Als nächstes, wenn ein TMS-Eingabestrom von ,1' entdeckt wird, erzeugt die Datenausgabe 511Daten A (=0) zur Ausgabe (Schritt S602). Daten aus der Datenausgabe 511 werden abgegriffen undim Schieberegister 52 gemäß dem TCK-Signal gespeichert. Eine gewünschte Datenkombination für dieEingabe kann daher durch die Datenausgabe 511 des Zustandsdetektors 51 erzeugt werden durchEingabe einer geeigneten Kombination von Strömen am TMS-Pin. Die Datenkombination wird im Schieberegister52 zwischengespeichert.

[0024] Ein Teil der Datenkombination, die im Schieberegister 52 zwischengespeichert wird, wirdals ein Eingabeschlüssel verwendet und der Rest kann als Schreibdaten verwendet werden. In dieserAusführungsform sind die ungeraden Bits der Datenkombination der Eingabeschlüssel und die geradensind die Schreibdaten. Die Vergleicher 53-55 vergleichen jeweils den Eingabeschlüssel mit einemSchreibschlüssel, einem Leseschlüssel und einem Fortfahrschlüssel. Wenn der Eingabeschlüssel gleichdem Schreibschlüssel ist, gibt der Vergleicher 53 ein Schreibsteuersignal aus. Wenn der Eingabeschlüssel gleichdem Leseschlüssel ist, gibt der Vergleicher 54 ein Lesesteuersignal aus. Wenn der Eingabeschlüssel gleichdem Fortfahrschlüssel ist, gibt der Vergleicher 55 ein Fortfahrsteuersignal aus.

[0025] Unter Bezugnahme auch auf Fig. 3 wird das Schreibsteuersignal zur Verfügung gestellt,um das versteckte Register 37 zu setzen, die Schreibdaten zu laden. Wenn daher Daten geheimgeschrieben werden sollen, wird eine geeignete Kombination von Strömen an den TMS-Pin als Eingabe gesendetund so werden der Eingabeschlüssel gleich dem Schreibschlüssel und die Daten an der Datenausgabe511 des Zustandsdetektors 51 erzeugt, wodurch das Schreibsteuersignal zum Schreiben der Datenin das versteckte Register 37 erzeugt wird.

[0026] Das Lesesteuersignal wird zur Verfügung gestellt, um den Selektor 38 zu steuern, dasser aktuellen Inhalt des versteckten Registers 37 ausgibt. Das Fortfahrsteuersignal wird zurVerfügung gestellt, um den Selektor 38 zu steuern, aktuellen Inhalt des ID-Coderegisters 321auszugeben. Wenn der Inhalt des versteckten Registers 37 gelesen werden soll, wird dementsprechend einegeeignete Kombination von Strömen an den TMS-Pin als eine Eingabe gesendet, so dass der Eingabeschlüsselgleich dem Le-seschlüssel an der Datenausgabe 511 des Zustandsdetektors 51 erzeugt wird, wodurch das Lesesteuersignalerzeugt wird, um den Selektor 38 zu steuern, den Inhalt des versteckten Registers 37 über einenAusgabepfad des ID-Coderegisters 321, das durch die JTAG-Schnittstelle definiert wird, auszugeben.Wenn nicht der Inhalt des versteckten Registers 37 ausgelesen wird, wird eine geeignete Kombinationvon Strömen an den TMS-Pin als Eingabe geschickt, so dass der Eignabeschlüssel gleich dem Fortfahrschlüssel ander Datenausgabe 511 des Zustandsdetektors 51 erzeugt wird, wodurch das Fortfahrsteuersignalerzeugt wird, um den Selektor 38 zu steuern, den Inhalt des ID-Coderegisters 321 auszugeben.Der Ausgabepfad des ID-Coderegisters 321, das durch die JTAG-Schnittstelle definiert wird, gibtnämlich den Inhalt des ID-Coderegisters aus und stellt so den Zustand der JTAG-Schnittstellewieder her.

[0027] In Anbetracht des Vorangegangenen weiß man, dass die Erfindung die Ungültiger-Zustandsübergang-Schleife imZustandsübergangsdiagramm der Boundary Scan Testschnittstelle anwendet, um auf versteckte Daten zuzugreifen,ohne auf die Daten durch die Standarddaten-Eingabe/Ausgabe-Pins zuzugreifen, wodurch geschützter Zugriffauf geheime Daten in der Boundary Scan Testschnittstelle erreicht wird, was vollständig kompatibelmit der Boundary Scan Testschnittstelle sein kann und Zustände und Datenpfade der Boundary ScanTestschnittstelle nicht vollständig beeinflusst.

[0028] Obwohl die vorliegende Erfindung mit Bezug auf ihre bevorzugte Ausführungsform erklärt wurde,muss verstanden werden, dass viele andere mögliche Veränderungen und Variationen gemacht werdenkönnen, ohne vom Geist und vom Schutzbereich der Erfindung, wie sie nachfolgend beanspruchtwird, abzuweichen.

1. Vorrichtung für den Zugriff auf versteckte Daten in einer Boundary Scan Testschnittstelle, wobeidie Boundary Scan Testschnittstelle mit einem vorbestimmten Zustandsübergangsdiagramm arbeitet,um Zustandsübergang auf der Grundlage einer Eingabe durchzuführen, worin der durchgeführte Zustandsübergang mindestenseine Ungültiger-Zustandsübergang-Schleife hat, wobei die Vorrichtung umfasst: einen Zustandsdetektor zur Überwachung der Eingabe, um erste Daten auszugeben, wenn ein erstervorbestimmter Eingabestrom entdeckt wurde, und dann zweite Daten auszugeben, wenn ein zweitervorbestimmter Eingabestrom entdeckt wurde, worin der erste und der zweite vorbestimmte Eingabestromunterschiedlich sind und beide mit der Ungültiger-Zustandsübergang-Schleife konform gehen; ein Schieberegister zur Speicherung einer Kombination der ersten und der zweiten Daten, worindie Kombination einen Eingabeschlüssel hat; ein verstecktes Register zur Datenspeicherung; und eine Vergleichsvorrichtung zum Vergleichen des Eingabeschlüssels mit einem vorbestimmten Schreibschlüsselund Laden spezifischer Schreibdaten in das versteckte Register, wenn der Eingabeschlüssel gleich demvorbestimmten Schreibschlüssel ist.

2. Vorrichtung gemäß Anspruch 1, worin die Kombination weiterhin Informationen der spezifischen Schreibdatenumfasst.

3. Vorrichtung gemäß Anspruch 2, weiterhin umfassend: einen Selektor zum Auswählen einesInhalts des versteckten Registers oder eines spezifischen Registers, das von der Boundary ScanTestschnittstelle als eine Ausgabe definiert wurde.

4. Vorrichtung gemäß Anspruch 3, worin die Vergleichsvorrichtung den Eingabeschlüssel mit einemvorbestimmten Leseschlüssel vergleicht und den Selektor steuert, den Inhalt des versteckten Registersauszugeben, wenn der Eingabeschlüssel gleich dem vorbestimmten Leseschlüssel ist.

5. Vorrichtung gemäß Anspruch 4, worin die Vergleichsvorrichtung den Eingabeschlüssel mit einemvorbestimmten Fortfahrschlüssel vergleicht und den Selektor steuert, den Inhalt des spezifischen Registersauszugeben, wenn der Eingabeschlüssel gleich dem vorbestimmten Fortfahrschlüssel ist.

6. Vorrichtung gemäß Anspruch 2, worin der Eingabeschlüssel die ungeraden Bits der Kombinationist und die spezifischen Lesedaten die geraden Bits der Kombination sind.

7. Vorrichtung gemäß Anspruch 2, worin die Boundary Scan Testschnittstelle eine JTAG Schnittstelle istund die Eingabe eine TMS-Eingabe ist.

8. Vorrichtung gemäß Anspruch 2, worin die Boundary Scan Testschnittstelle eine IEEE 1149.1Schnittstelle ist und die Eingabe eine TMS-Eingabe ist.

9. Vorrichtung gemäß Anspruch 2, worin die Boundary Scan Testschnittstelle eine IEEE 1149.4Digital Test Access Port Schnittstelle ist und die Eingabe eine TMS-Eingabe ist.

10. Vorrichtung gemäß Anspruch 7, worin das Zustandsübergangsdiagramm anfangs in einem Test-LogicReset Zustand ist, unverändert, wenn die TMS-Eingabe ,1' ist, in einen Run-Test/Idle Zustandübergeht, wenn die TMS-Eingabe ,0' ist, im Run-Test/Idle Zustand bleibt, wenn die TMS-Eingabe,0' ist, und in den Test-Logic Reset Zustand übergeht, wenn die TMS-Eingabe auf drei aufeinanderfolgende 1 en stößt, um die mindestens eine Ungültiger-Zu-standsübergang-Schleife zu bilden.

11. Vorrichtung gemäß Anspruch 10, worin der erste vorbestimmte Eingabestrom ,0111' ist undder zweite vorbestimmte Eingabestrom ,1' ist.

12. Vorrichtung gemäß Anspruch 11, worin die ersten Daten ,1' sind und die zweiten Daten,0' sind.

13. Vorrichtung gemäß Anspruch 10, worin der erste vorbestimmte Eingabestrom ,00111' ist und der zweite vorbestimmte Eingabestrom ,1' ist, wobei 0 mindestens eine ,0' darstellt.

14. Vorrichtung gemäß Anspruch 13, worin die ersten Daten ,1' sind und die zweiten Daten,0' sind.

15. Vorrichtung gemäß Anspruch 7, worin Daten, die durch den Zustandsdetektor ausgegebenwerden, abgegriffen und im Schieberegister gespeichert werden gemäß einem TCK-Signal, das durchdie JTAG definiert ist.

16. Vorrichtung gemäß Anspruch 2, worin das spezifische Register ein Identifizierungs-(ID)-Coderegister ist.

17. Verfahren zum Zugriff auf versteckte Daten in einer Boundary Scan Testschnittstelle,wobei die Boundary Scan Testschnittstelle mit einem vorbestimmten Zustandsübergangsdiagramm arbeitet,um Zustandsübergang auf der Grundlage einer Eingabe durchzuführen, worin der durchgeführte Zustandsübergang mindestenseine Ungültiger-Zustandsübergang-Schleife hat, wobei das Verfahren die Schritte umfasst: (A) des Überwachens der Eingabe, um erste Daten auszugeben, wenn ein erster vorbestimmter Eingabestromentdeckt wird, und dann zweite Daten auszugeben, wenn ein zweiter vorbestimmter Eingabestromentdeckt wird, worin der erste und der zweite vorbestimmte Eingabestrom verschieden sind undbeide mit der Ungültiger-Zustandsübergang-Schleife konform gehen; (B) des Zwischenspeicherns einer Kombination der ersten Daten und der zweiten Daten, worin dieKombination einen Eingabeschlüssel hat; und (C) des Vergleiches des Eingabeschlüssels mit einem vorbestimmten Schreibschlüssel, so dassspezifische Schreibdaten in ein verstecktes Register geladen werden, wenn der Eingabeschlüssel gleichdem vorbestimmten Schreibschlüssel ist.

18. Verfahren gemäß Anspruch 17, worin die Kombination weiterhin Informationen der spezifischen Schreibdatenumfasst.

19. Verfahren gemäß Anspruch 18, das weiterhin den Schritt umfasst: (D) des Vergleichens des Eingabeschlüssels mit einem vorbestimmten Leseschlüssel und des Ausgebenseines Inhalts des versteckten Registers durch einen Ausgabepfad eines spezifischen Registers,das durch die Boundary Scan Testschnittstelle definiert ist, wenn der Eingabeschlüssel gleich demvorbestimmten Leseschlüssel ist.

20. Verfahren gemäß Anspruch 19, das weiterhin den Schritt umfasst: (E) des Vergleichens des Eingabeschlüssels mit einem vorbestimmten Fortfahrschlüssel und desAusgebens des Inhalts des versteckten Registers durch den Ausgabepfad des spezifischen Registers,das durch die Boundary Scan Testschnittstelle definiert ist.

21. Verfahren gemäß Anspruch 18, worin in Schritt (B) der Eingabeschlüssel die ungeradenBits der Kombination ist und die spezifischen Schreibdaten die geraden Bits der Kombinationsind.

22. Verfahren gemäß Anspruch 18, worin die Boundary Scan Testschnittstelle eine JTAG-Schnittstelle verwendetund die Eingabe eine TMS-Eingabe ist.

23. Verfahren gemäß Anspruch 18, worin die Boundary Scan Testschnittstelle eine IEEE 1149.1Schnittstelle verwendet und die Eingabe eine TMS-Eingabe ist.

24. Verfahren gemäß Anspruch 18, worin die Boundary Scan Testschnittstelle eine IEEE 1149.4Digital Test Access Port Schnittstelle verwendet und die Eingabe eine TMS-Eingabe ist.

25. Verfahren gemäß Anspruch 22, worin das Zustandsübergangsdiagramm anfangs in einem Test-LogicReset Zustand ist, unverändert, wenn die TMS-Eingabe ,1' ist, in einen Run-Test/Idle Zustandübergeht, wenn die TMS-Eingabe ,0' ist, im Run-Test/Idle Zustand bleibt, wenn die TMS-Eingabe,0' ist, und in den Test-Logic Reset Zustand übergeht, wenn die TMS-Eingabe auf drei aufeinanderfolgende 1 en stößt, um die mindestens eine Ungültiger-Zustandsübergang-Schleife zu bilden.

26. Verfahren gemäß Anspruch 25, worin in Schritt (A) der erste vorbestimmte Eingabestrom,0111' ist, während die ersten Daten ,1' sind; der zweite vorbestimmte Eingabestrom ,1' ist,während die zweiten Daten ,0' sind.

27. Verfahren gemäß Anspruch 25, worin in Schritt (A) der erste vorbestimmte Eingabestrom,00111' ist, während die ersten Daten ,1' sind, wobei 0 mindestens eine ,0' darstellt; der zweite vorbestimmte Eingabestrom ,1'ist, während die zweiten Daten ,0' sind.

28. Verfahren gemäß Anspruch 19, worin das spezifische Register ein ID-Coderegister ist.

Es folgen 6 Blatt Zeichnungen