Printed circuit assembly having conductive pad array with in-line via placement

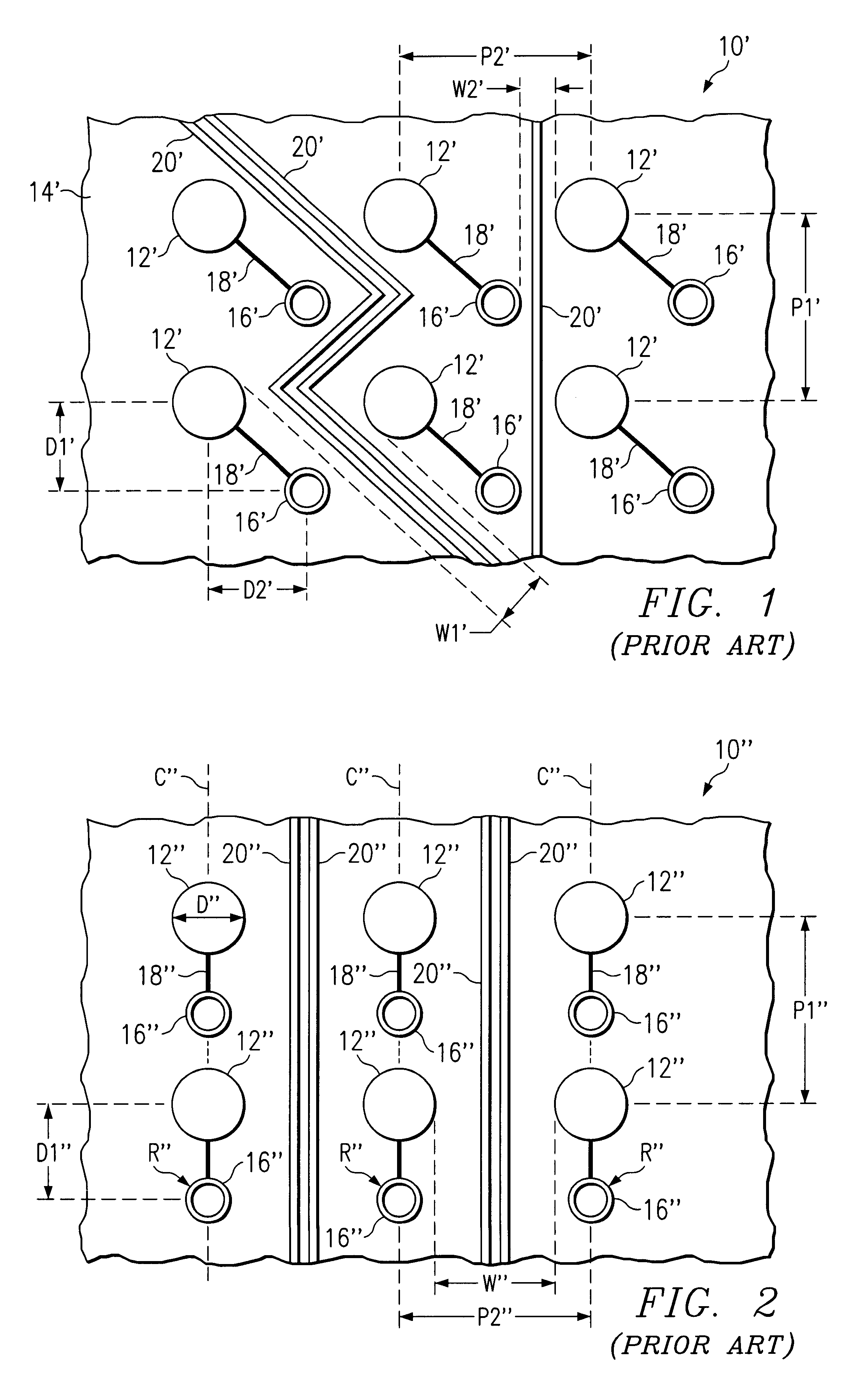

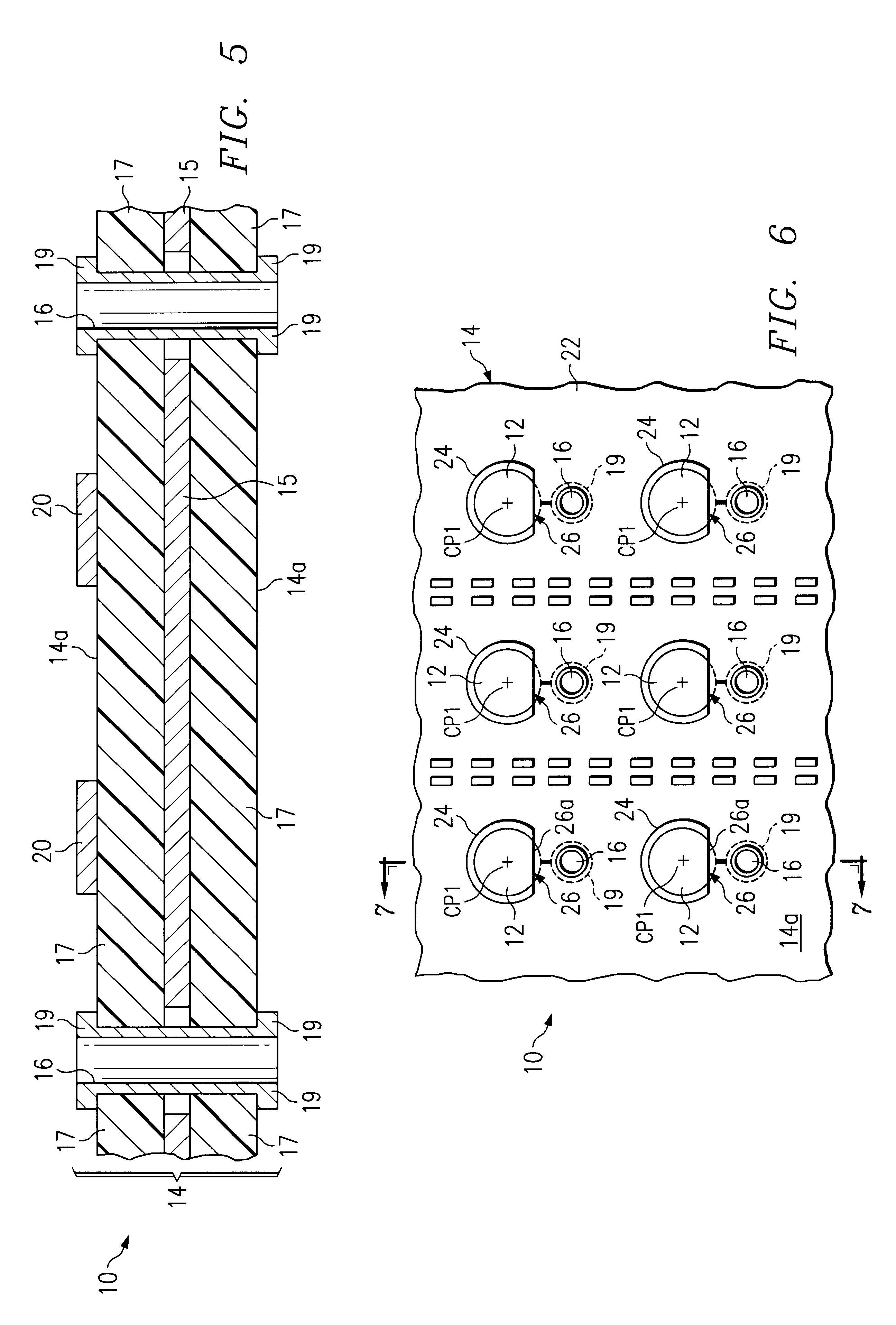

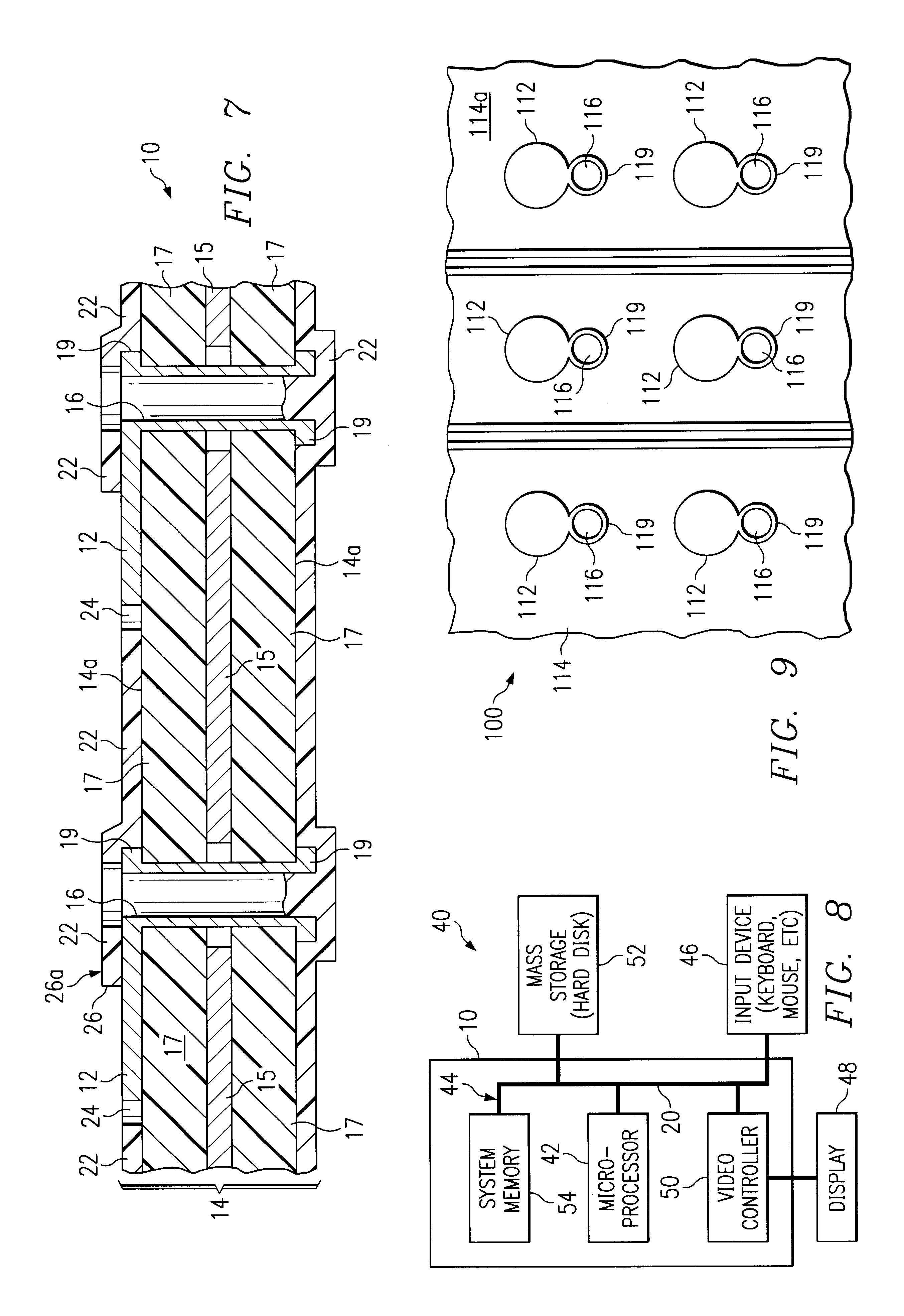

The disclosures herein relate generally to computer systems and more particularly to a printed circuit assembly having a conductive pad array with in-line via placement. Printed circuit assemblies such as rigid printed circuit boards and flexible printed circuits, are widely used components in all types of electronic devices. For example, printed circuit assemblies are commonly used as motherboards or other types of system boards in computer systems. Printed circuit assemblies provide for dense routing of electrical signals and power, and are relatively inexpensive to fabricate. The size of electronic components continues to decrease and circuit routing densities continue to increase. Accordingly, it is necessary to increase the density of printed circuit assembly components, such as interconnect pads, conductive vias, and traces. Increasing the density of the printed circuit assembly components requires spacing such components closer together without increasing the occurrence of short circuits between adjacent printed circuit assembly components. U.S. Pat. No. 5,875,102 discloses a ball grid array integrated circuit package which has a plurality of conductive vias connected to a plurality of solder pads located on a bottom surface of a package substrate. Each conductive via has a portion located within a solder pad to increase the routing space of the substrate, and a portion located outside the solder pad to allow outgassing from the conductive via. The bottom surface also has a solder mask which covers the conductive vias and contains a number of holes that expose the solder pads. The holes allow solder balls to be connected to the solder pads. The solder balls can be reflowed to attach the package to a printed circuit board. This type of package configuration increases routing space, but is relatively expensive to fabricate. U.S. Pat. No. 5,706,178 discloses a ball grid array integrated circuit package which has a plurality of elliptically shaped solder pads located on a bottom surface of a package substrate. The bottom surface also has a solder mask which contains a number of holes that expose the solder pads. The holes allow solder balls to be attached to the solder pads. The solder balls can be reflowed to attach the package to a printed circuit board. The elliptically shaped solder pads have a width that is smaller than the length of the pads. The narrow width portion of each solder pad provides additional routing space on the bottom surface of the package. The solder mask hole diameters are less than the length of the solder pads so that portions of the solder pads are anchored beneath the solder mask. The anchored portions of the solder pads increase the solder pad peel strength. U.S. Pat. No. 5,585,162 discloses a flexible circuit construction that allows solder balls to be mass reflow attached to the ground plane of a double-sided flexible circuit. The circuit includes a first conductive via which is separate from the remainder of the ground plane. The first conductive via is electrically connected to the ground plane through a second conductive via. The second conductive via is positioned at a distance from the first conductive via by a circuit trace on the side of the flexible circuit opposite the ground plane. In high density printed circuit assemblies, the distance between one printed circuit assembly component relative to another is decreased. By rearranging selected printed circuit assembly components, additional space between such selected components is provided. The additional space can be used for adding more printed circuit assembly components such as interconnect pads and conductive vias, or for routing additional traces or larger traces between the selected components. Conventional printed circuit assemblies that provide additional trace routing space are known and are discussed herein below. These conventional printed circuit assemblies provide additional routing space at the expense of reliability and manufacturability. Each conductive via and adjacent non-connected interconnect pad are susceptible to shorting during reflow of a connected interconnect element, such as a solder ball. In some of these conventional printed circuit assemblies, each conductive via is centered between two interconnect pads. Because of the close proximity of each conductive via relative to the adjacent non-connected interconnect pad, the potential exists for one or more of the conductive vias to be inadvertently connected to the adjacent non-connected interconnect pad during a solder reflow operation. Therefore, what is needed is a low-cost and reliable printed circuit assembly that provides additional space for routing wider traces or an increased number of traces through an array of conductive vias and interconnect pads. Accordingly, in one embodiment, a printed circuit assembly includes a conductive via that provides additional space for routing traces without sacrificing reliability or manufacturability. To this end, a printed circuit assembly includes a circuit substrate having spaced apart first and second major surfaces. A first and a second interconnect pad are spaced apart on the first major surface of the circuit substrate. The first and the second interconnect pads are positioned on a reference axis. The first interconnect pad is spaced apart from the second interconnect pad by a first distance. A first and a second conductive via extend through the circuit substrate between the first and the second major surfaces. The first and the second conductive vias are positioned adjacent to and electrically connected to respective ones of the interconnect pads. Each one of the conductive vias is positioned on the reference axis and is spaced apart from the respective interconnect pad by a second distance. The first distance is substantially greater than the second distance wherein each conductive via is offset toward the connected interconnect pad. A principal advantage of this embodiment is that an array of conductive vias and an array of interconnect pads can be configured to provide increased space for routing traces therethrough. A first conventional printed circuit assembly 10′, An interconnect trace 18′ connects each interconnect pad 12′ with a respective one of the conductive vias 16′. One or more routing traces 20′ are routed between the interconnect pads 12′ and the conductive vias 16′. The routing traces 20′ can be routed in a straight configuration or in a zig-zag configuration. A first trace routing width W1′ is defined between adjacent interconnect pads 12′, extending generally parallel to the interconnect traces 18′. A second trace routing width W2′ is defined between each interconnect pad 12′ and adjacent pairs of non-connected conductive vias 16′. The first trace routing width W1′ is substantially greater than the second trace routing width W2′. In many applications, such as when routing traces to RAMBUS™ memory modules offered by Rambus Incorporated, it is necessary to provide additional space for the routing traces 20′. The routing traces 20′ for RAMBUS memory modules are typically about 18 mils wide whereas conventional routing traces are about 6 mils wide. A second conventional printed circuit assembly 10″, A plurality of rows R″ of conductive vias 12″ and interconnect pads 16″ are spaced apart, defining a trace routing width W″ therebetween. Each adjacent pair of interconnect pads 12″ in each row R″ has a conductive via 16″ centered therebetween on a common axis C″. The trace routing width W″ is equal to the second direction pitch P2′ minus the interconnect pad diameter D″. Accordingly, relative to the routing widths W1′ and W2′ of the first conventional printed circuit assembly 10′, The second conventional printed circuit assembly 10″ provides additional trace routing space at the expense of reliability and manufacturability. Each conductive via 16″ and the adjacent non-connected interconnect pad 12″ in each row R″ are susceptible to shorting during reflow of a connected interconnect element, such as a solder ball. Because each conductive via 16″ is centered between two interconnect pads 12″ and because of the close proximity of each conductive via 16″ relative to the adjacent non-connected interconnect pad 12″, the potential exists for one or more of the conductive vias 16″ to be inadvertently connected to the adjacent non-connected interconnect pad 12″ during a solder reflow operation. An embodiment of a printed circuit assembly 10 that provides a reduced potential for shorting and an increased space for the routing of traces is illustrated in The circuit substrate 14, Each conductive via 16 is electrically connected to one of the interconnect pads 12 by an interconnect trace 18. Each interconnect pad 12, connected conductive via 16 and respective interconnect trace 18 define an interconnect assembly. Each conductive via 16 is offset from a connected interconnect pad 12 in only a first direction by a first direction offset distance D1, FIG. 3. The arrays of interconnect pads 12 and conductive vias 16 have a first direction pitch P1 and a second direction pitch P2. The first direction pitch P1 and the second direction pitch P2 are substantially the same. In other embodiments (not shown), the first direction pitch P1 is different from the second direction pitch P2. Each conductive via 16 includes a conductive land 19 on each major surface 14 A plurality of rows R of conductive vias 12 and interconnect pads 16, A key aspect of the printed circuit assembly 10 disclosed herein is that the offset distance D1 is substantially less than one-half of the first direction pitch P1. By offsetting each conductive via 16 closer to the connected interconnect pad 12, the potential for shorting between each conductive via 16 and the adjacent non-connected interconnect pad 12 is substantially reduced. The reduced potential for shorting improves initial yield rates and rework yield rates while still providing additional space for routing a plurality of routing traces 20. The printed circuit assembly 10 typically has first and second direction pitches P1, P2, respectively, of about 50 mils, a conductive land diameter of about 25 mils and a solder mask clearance from each interconnect pad of about 2.5 mils. Accordingly, the trace routing width W of the printed circuit assembly 10 having such a configuration is about 25 mils. Referring to The solder mask layer 22 extends over a portion of each interconnect pad 12 and over at least a portion of each conductive land 19. The solder mask layer 22 on the major surface 14 Each one of the openings 24 in the solder mask layer 22 has a generally round shape with a truncated edge segment 26, FIG. 6. Each truncated edge segment 26 is positioned between the respective interconnect pad 12 and the connected conductive via 16. Each truncated edge segment 26 defines a transverse edge 26a of the solder mask layer 22 that is offset from a perimeter edge of the respective interconnect pad 12 toward the respective center point CP1. Another key aspect of the printed circuit assembly 10 is that the openings 24 are patterned to include the truncated edge segments 26. Each truncated edge segment 26 provides an increased distance between the exposed portion of each interconnect pad 12 and the conductive land 19 of the connected conductive via 16. The increased distance reduces the potential for a flowable conductive material, such as solder from a solder ball (not shown), to wick into the conductive vias 16 during a solder reflow process. The printed circuit assembly 10 can be manufactured by contract manufacturers such as Compeq Manufacturing Company, Ltd. and HADCO Corporation using conventional manufacturing techniques. Furthermore, the printed circuit assembly 10 can be manufactured from commercially available materials. A preferred material for the dielectric layers 17 is a flame retardant fully cured epoxy resin commonly referred to as FR-4. A preferred material for the conductive layers 15 is copper. An embodiment of a computer system 40 is illustrated in FIG. 8. The computer system 40 includes at least one microprocessor 42. The microprocessor 42 is connected to a bus 44. The bus 44 serves as a connection between the microprocessor 42 and other components of the computer system 40. The bus 44 typically includes one or more traces such as the routing traces 20 discussed above. An input device 46 is coupled to the microprocessor 42 to provide input to the microprocessor 42. Examples of input devices include keyboards, touchscreens, and pointing devices such as a mouse, a trackball and a trackpad. The computer system 40 may also include a display 48, which is coupled to the microprocessor 42 typically by a video controller 50. Programs and data are stored on a mass storage device 52 which is coupled to the microprocessor 42. Mass storage devices include components such as hard disks, optical disks, magneto-optical drives, floppy drives, and the like. A system memory 54 provides the microprocessor 42 with fast storage to facilitate execution of computer programs by the microprocessor 42. The microprocessor 42, video controller 48 and system memory 54 are mounted on a printed circuit assembly 10, as discussed above. It should be understood that other busses and intermediate circuits can be employed between the components described above and microprocessor 42 to facilitate interconnection between the components and the microprocessor 42. Referring to As a result, one embodiment of a printed circuit assembly includes a circuit substrate having spaced apart first and second major surfaces. A first and a second interconnect pad are spaced apart on the first major surface of the circuit substrate. The first and the second interconnect pads are positioned on a reference axis. The first interconnect pad is spaced apart from the second interconnect pad by a first distance. A first and a second conductive via extend through the circuit substrate between the first and the second major surfaces. The first and the second conductive vias are positioned adjacent to and electrically connected to respective ones of the interconnect pads. Each one of the conductive vias is positioned on the reference axis and is spaced apart from the respective interconnect pad by a second distance. The first distance is substantially greater than the second distance wherein each conductive via is offset toward the connected interconnect pad. Another embodiment provides a computer system including a microprocessor and a system memory coupled to provide storage to facilitate execution of computer programs by the microprocessor. An input is coupled to provide input to the microprocessor. A display is coupled to the microprocessor by a video controller and a mass storage is coupled to the microprocessor. A printed circuit board is electrically coupled to the microprocessor. The printed circuit board includes a circuit substrate having two spaced apart major surfaces and a plurality of rows of interconnect assemblies. Each row of interconnect assemblies includes a first and a second interconnect pad spaced apart on a major surface of the circuit substrate. The first and the second interconnect pads are positioned on a respective reference axis. The first interconnect pad is spaced apart from the second interconnect pad by a first distance. A first and a second conductive via extend through the circuit substrate. The first and the second conductive vias are positioned adjacent to and electrically connected to respective ones of the interconnect pads. Each one of the conductive vias is positioned on the respective reference axis and is spaced apart from the respective interconnect pad by a second distance. The first distance is substantially greater than the second distance wherein each conductive via is offset toward the connected interconnect pad. A further embodiment provides a method of providing increased routing space on a major surface of a printed circuit assembly. The method includes forming a first and a second interconnect pad spaced apart on a major surface of a circuit substrate. The first and the second interconnect pads are positioned on a reference axis with the first interconnect pad spaced apart from the second interconnect pad by a first distance. A first and a second conductive via are formed through the circuit substrate. The first and the second conductive vias are positioned on the reference axis adjacent to respective ones of the interconnect pads with each conductive via spaced apart from the respective interconnect pad by a second distance. The second distance is substantially less than the first distance wherein each conductive via is offset toward the respective interconnect pad. Lastly, each conductive via is connected to the respective interconnect pad. As it can be seen, the embodiments disclosed herein provide several advantages. An array of conductive vias and interconnect pads can be configured to provide increased space for routing traces therethrough. The printed circuit assemblies can be cost-effectively manufactured using conventional manufacturing techniques. The potential for shorting between adjacent conductive features is significantly reduced. The uninterrupted web area of interior conductive layers is substantially increased. The impedance of conductive features such as routing traces is more controlled. Although illustrative embodiments have been shown and described, a wide range of modification, change and substitution is contemplated in the foregoing disclosure and in some instances, some features of the embodiments may be employed without a corresponding use of other features. Accordingly, it is appropriate that the appended claims be construed broadly and in a manner consistent with the scope of the embodiments disclosed herein. A computer system including a microprocessor and a system memory coupled t provide storage to facilitate execution of computer programs by the microprocessor. An input is coupled to provide input to the microprocessor. A display is coupled to the microprocessor by a video controller and a mass storage is coupled to the microprocessor. A printed circuit board is electrically coupled to the microprocessor. The printed circuit board includes a circuit substrate having two spaced apart major surfaces and a plurality of rows of interconnect assemblies. Each row of interconnect assemblies includes a first and a second interconnect pad on a major surface of the circuit substrate. The first and the second interconnect pads are positioned on a respective reference axis. The first interconnect pad is spaced apart from the second interconnect pad by a first distance. A first and a second conductive via extend through the circuit substrate. The first and the second conductive vias are positioned adjacent to and electrically connected to respective ones of the interconnect pads. Each one of the conductive vias is positioned on the respective reference axis and is spaced apart from the respective interconnect pad by a second distance. The first distance is substantially greater than the second distance wherein each conductive via is offset toward the connected interconnect pad. 1. A printed circuit assembly, comprising: a circuit substrate having spaced apart first and second major surfaces; a plurality of rows of interconnect assemblies on the substrate; a first and a second interconnect pad on the first major surface of the circuit substrate, the first and the second interconnect pads positioned on a reference axis extending therebetween; each interconnect pad having a pad diameter; a conductive via positioned between each interconnect pad, the conductive via being electrically connected to and offset toward the first one of the interconnect pads, the conductive via having a center on the reference axis; a first directional pitch extending between adjacent pads in one row and a second directional pitch extending between adjacent pads in adjacent rows; the rows being spaced apart to define a trace routing width; the trace routing width being equal to the second directional pitch minus the pad diameter; a trace extending between a first row and a second row on the interconnect assemblies; and the first row of interconnect assemblies being spaced apart from the second row of interconnect assemblies by a distance of about 25 mils and wherein the trace has a width of about 18 mils. 2. The printed circuit assembly of a conductive trace electrically connected between each conductive via and the respective interconnect pad. 3. The printed circuit assembly of 4. The printed circuit assembly of 5. The printed circuit assembly of a solder mask layer on the circuit substrate, the solder mask layer having openings therein and each interconnect pad being exposed within a respective one of the openings. 6. The printed circuit assembly of 7. The printed circuit assembly of 8. The printed circuit assembly of 9. The printed circuit assembly of 10. The printed circuit assembly of 11. A computer system, comprising: a microprocessor; a mass storage coupled to the microprocessor; and a printed circuit board electrically coupled to the microprocessor, the printed circuit board including a circuit substrate having two spaced apart major surfaces and a plurality of rows of interconnect assemblies, each row of interconnect assemblies including: a first and a second interconnect pad on a major surface of the circuit substrate, the first and the second interconnect pads positioned on a respective reference axis extending therebetween; each interconnect pad having a pad diameter; a conductive via positioned between each interconnect pad, the conductive via being electrically connected to and offset toward the first one of the interconnect pads, the conductive via having a center on the reference axis; a first directional pitch extending between adjacent pads in one row and a second directional pitch extending between adjacent pads in adjacent rows; the rows being spaced apart to define a trace routing width; the trace routing width being equal to the second directional pitch minus the pad diameter; a trace extending between a first row and a second row on the interconnect assemblies; and the first row of interconnect assemblies being spaced apart from the second row of interconnect assemblies by a distance of about 25 mils and wherein the trace has a width of about 18 mils. 12. A method of providing increased routing space on a major surface of a printed circuit assembly, comprising the steps of: forming a plurality of rows of first and a second interconnect pads on a major surface of a circuit substrate with the first and the second interconnect pads positioned on a reference axis extending therebetween, each pad having a pad diameter; positioning a conductive via between each interconnect pad such that the conductive via has a center on the reference axis; electrically connecting the conductive via to the first one of the interconnect pads; offsetting the conductive via toward the first one of the interconnect pads; extending a first directional pitch between adjacent pads in one row and extending a second directional pitch between adjacent pads in adjacent rows; spacing the rows apart to define a trace routing width which is equal to the second directional pitch minus the pad diameter; extending a trace between a first row and a second row on the interconnect assemblies; spacing the first row from the second row by a distance of about 25 mils; and providing the trace to have a width of about 18 mils. 13. The method of forming the interconnect pads and forming the conductive vias to have a substantially round shape wherein the round shade defines a respective center point thereof; and positioning the center point of each interconnect pad and the center point of each conductive via on the reference axis. 14. The method of 15. The method of forming a solder mask layer on the circuit substrate; and forming openings in the solder mask layer wherein each interconnect pad is exposed within a respective one of the openings. 16. The method of 17. A printed circuit assembly, comprising: a circuit substrate having spaced apart first and second major surfaces; a plurality of rows of interconnect assemblies on the substrate; a first and a second interconnect pad on the first major surface of the circuit substrate, the first and the second interconnect pads positioned on a reference axis extending therebetween; each interconnect pad having a pad diameter; a conductive via positioned between each interconnect pad, the conductive via being electrically connected to and offset toward the first one of the interconnect pads, the conductive via having a center on the reference axis; a first directional pitch extending between adjacent pads in one row and a second directional pitch extending between adjacent pads in adjacent rows; the rows being spaced apart to define a trace routing width; the trace routing width being equal to the second directional pitch minus the pad diameter; a trace extending between a first row and a second row on the interconnect assemblies; and the first row being spaced apart from the second row by a distance of about 25 mils, and wherein the trace has a width of about 75% of the distance between the first row and the second row.BACKGROUND

SUMMARY

BRIEF DESCRIPTION OF THE DRAWING FIGURES

DETAILED DESCRIPTION

CPC - классификация

HH0H05H05KH05K1H05K1/H05K1/1H05K1/11H05K1/114H05K2H05K22H05K220H05K2201H05K2201/H05K2201/0H05K2201/09H05K2201/092H05K2201/0922H05K2201/09227H05K2201/099H05K2201/1H05K2201/10H05K2201/107H05K2201/1073H05K2201/10734H05K3H05K3/H05K3/3H05K3/34H05K3/345H05K3/3452H05K3/4H05K3/42H05K3/429Цитирование НПИ

174/260174/261

174/264

174/266

204/15

257/679

257/700

257/737

29/593

365/51

365/63

428/209

439/66