DISPLAY PANEL, DISPLAY DEVICE, AND MANUFACTURING METHOD FOR DISPLAY PANEL

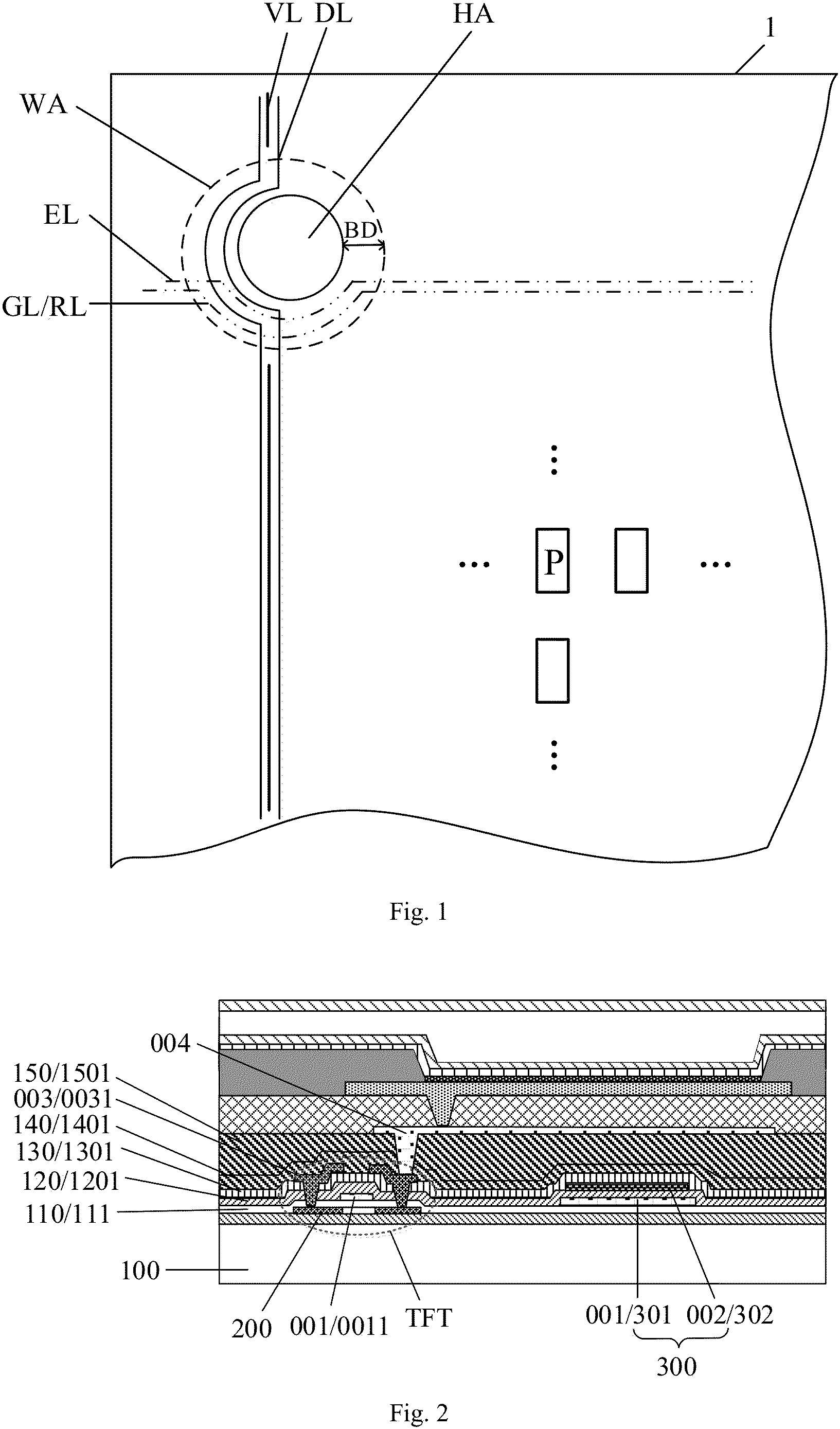

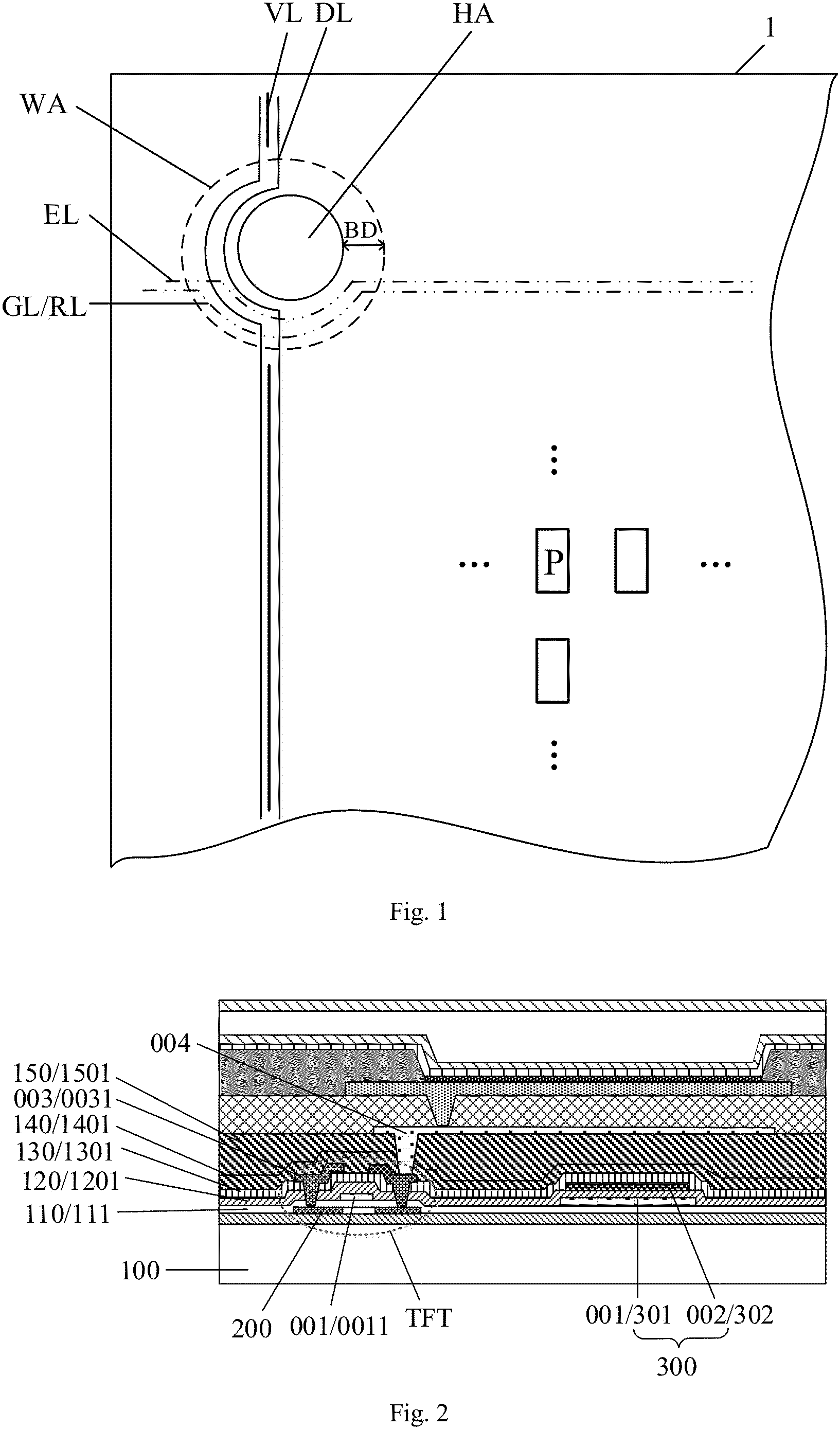

The present disclosure is a National Stage of International Application No. PCT/CN2021/092722, filed on May 10, 2021, which claims the priority to Chinese Patent Application No. 202010490145.X, filed to China National Intellectual Property Administration on Jun. 2, 2020, which are incorporated in their entirety herein by reference. The present disclosure relates to the technical field of display, and in particular to a display panel, a display device, and a manufacturing method for the display panel. As display electronic products such as mobile phones develop, a screen-to-body ratio of a display screen tends to increase. For full-screen display, a hole area can be arranged on the display screen, and a wire structure surrounding the hole area needs to be wound. In a first aspect, an embodiment of the present disclosure provides a display panel. The display panel includes a substrate, and a first metal layer, a second metal layer and a third metal layer that are stacked on the substrate sequentially, and further includes wires, where the wires include: a first wire extending in a first direction, where the first wire includes a first sub-wire portion, a second sub-wire portion, a first auxiliary portion and a second auxiliary portion; and a second wire extending in a second direction, the second wire including a third sub-wire portion and a third auxiliary portion; where the first direction is different from the second direction; the first sub-wire portion and the second sub-wire portion are at the third metal layer, the first auxiliary portion is at the first metal layer, the second auxiliary portion is at the second metal layer, the third sub-wire portion is at the first metal layer, and the third auxiliary portion is at the third metal layer; the substrate of the display panel further includes a hole area and a non-hole area, and the non-hole area includes a winding area; and the first auxiliary portion, the second auxiliary portion, and the third auxiliary portion each include a winding structure provided within the winding area. In a possible implementation, orthographic projections of the first auxiliary portion and the second auxiliary portion on the substrate are arranged alternately. In a possible implementation, the first sub-wire portion is electrically connected to the first auxiliary portion through a first via hole; the second sub-wire portion is electrically connected to the second auxiliary portion through a second via hole; and the third sub-wire portion is electrically connected to the third auxiliary portion through a third via hole. In a possible implementation, the second wire further includes a fourth sub-wire portion, and the fourth sub-wire portion is at the first metal layer. In a possible implementation, the display panel further includes a fourth metal layer on one side of the third metal layer away from the substrate. In a possible implementation, the second wire further includes a fourth auxiliary portion, and the fourth auxiliary portion is at the fourth metal layer; and the fourth auxiliary portion includes a winding structure in the winding area. In a possible implementation, orthographic projections of the third auxiliary portion and the fourth auxiliary portion on the substrate are arranged alternately. In a possible implementation, the display panel further includes: a first bridge portion at the third metal layer, where the first bridge portion is electrically connected to the fourth sub-wire portion through a fifth via hole. In a possible implementation, the first bridge portion is electrically connected to the fourth auxiliary portion through a fourth via hole. In a possible implementation, an orthographic projection of the fourth via hole on the substrate does not overlap an orthographic projection of the fifth via hole on the substrate. In a possible implementation, the third sub-wire portion, the fourth sub-wire portion and the first auxiliary portion at the first metal layer are insulated from one another; the first sub-wire portion, the second sub-wire portion, the first bridge portion and the third auxiliary portion that are at the third metal layer are insulated from one another; and the first auxiliary portion, the second auxiliary portion, the third auxiliary portion and the fourth auxiliary portion are insulated from one another. In a possible implementation, the display panel further includes: a first insulating layer between the first metal layer and the substrate, a second insulating layer between the first metal layer and the second metal layer, a third insulating layer between the second metal layer and the third metal layer, a fourth insulating layer on one side of the third metal layer away from the substrate, and a fifth insulating layer on one side of the fourth insulating layer away from the substrate. In a possible implementation, the display panel further includes pixel units arranged in an array, where each of the pixel units includes a drive circuit and a storage capacitor, the drive circuit includes a thin film transistor, and the thin film transistor includes: an active layer on the substrate; a first gate insulating layer on one side of the active layer away from the substrate, where the first insulating layer includes the first gate insulating layer; a first gate on one side of the first gate insulating layer away from the substrate, where the first metal layer includes the first gate; an interlayer insulating layer on one side of the first gate away from the substrate, where the third insulating layer includes the interlayer insulating layer; a source-drain layer on one side of the interlayer insulating layer away from the substrate, where the third metal layer includes the source-drain layer; a passivation layer on one side of the source-drain layer away from the substrate, where the fourth insulating layer includes the passivation layer; and a planarization layer on one side of the passivation layer away from the substrate, where the fifth insulating layer includes the planarization layer. In a possible implementation, the first via hole is a through hole at least penetrating the third insulating layer to cause the first sub-wire portion to be electrically connected to the first auxiliary portion. In a possible implementation, the second via hole is a through hole at least penetrating the third insulating layer to cause the second sub-wire portion to be electrically connected to the second auxiliary portion. In a possible implementation, the third via hole is a through hole at least penetrating the third insulating layer to cause the third sub-wire portion to be electrically connected to the third auxiliary portion. In a possible implementation, the fourth via hole is a through hole at least penetrating the fourth insulating layer and the fifth insulating layer to cause the first bridge portion to be electrically connected to the fourth auxiliary portion. In a possible implementation, the fifth via hole is a through hole at least penetrating the third insulating layer to cause the fourth sub-wire portion to be electrically connected to the first bridge portion. In a possible implementation, the first sub-wire portion and the second sub-wire portion are electrically connected to sources or drains of thin film transistors of different pixel units separately and are configured to transmit data signals. In a possible implementation, the third sub-wire portion is electrically connected to the first gate of the thin film transistor and configured to transmit a first gate signal. The fourth sub-wire portion is configured to transmit a light-emitting control signal. In a possible implementation, a first bridge portion electrically connected to a fourth sub-wire portion configured to transmit an (n+1)th row of light-emitting control signal is electrically connected to a fourth sub-wire portion configured to transmit an nth row of light-emitting control signal by means of a second bridge portion, where n is an integer greater than or equal to 1. In a possible implementation, the second bridge portion is at the third metal layer, the second bridge portion is provided with a sixth via hole, and the sixth via hole is a via hole at least penetrating the third insulating layer to cause the fourth sub-wire portion configured to transmit the nth row of light-emitting control signal to be electrically connected to the second bridge portion. In a possible implementation, the fourth sub-wire portion configured to transmit the nth row of light-emitting control signal is electrically connected to the second bridge portion through the sixth via hole, the first bridge portion and the second bridge portion that are electrically connected to the fourth sub-wire portion configured to transmit the (n+1)th row of light-emitting control signal are electrically connected to the fourth auxiliary portion jointly through the fourth via hole, and an orthographic projection of the sixth via hole on the substrate does not overlap an orthographic projection of the fourth via hole on the substrate. In a possible implementation, projections of the fourth sub-wire portion and the winding area on the substrate do not overlap with each other, and the fourth sub-wire portion configured to transmit one row of light-emitting control signal is cut off in the winding area. In a possible implementation, the second wire further includes a fifth sub-wire portion. In a possible implementation, the fifth sub-wire portion is configured to transmit a reset signal. In a possible implementation, a fifth sub-wire portion configured to transmit an (m+1)th row of reset signal is electrically connected to a third sub-wire portion configured to transmit an mth row of first gate signal by means of the third bridge portion, where m is an integer greater than equal to 1. In a possible implementation, the third bridge portion is at the third metal layer, the third bridge portion is provided with a seventh via hole and an eighth via hole, the seventh via hole is a via hole at least penetrating the third insulating layer to cause the third sub-wire portion configured to transmit the mth row of first gate signal to be electrically connected to the third bridge portion, and the eighth via hole is a via hole at least penetrating the third insulating layer to cause the fifth sub-wire portion configured to transmit the (m+1)th row of reset signal to be electrically connected to the third bridge portion. In a possible implementation, the third bridge portion is electrically connected to the third auxiliary portion through the seventh via hole or the eighth via hole. In a possible implementation, at least some of the first via hole, the second via hole, the third via hole, the fourth via hole, the fifth via hole, the sixth via hole, the seventh via hole, or the eighth via hole are in a multi-via-hole parallel structure. In a possible implementation, the storage capacitor includes a first plate electrode and a second plate electrode, the first plate electrode is at the first metal layer, the second plate electrode is at the second metal layer, a second gate insulating layer is between the first plate electrode and the second plate electrode, and the second insulating layer includes the second gate insulating layer. In a possible implementation, a shape of the hole area includes a circle, an oval, a triangle, a quadrangle, or an irregular shape. In a second aspect, an embodiment of the present disclosure provides a display device. The display device includes the above display panel provided in any one of the embodiments of the present disclosure. In a possible implementation, the display device further includes a sensor below the hole area. In a possible implementation, the sensor includes a camera, an infrared sensor, a fingerprint detection unit, and a pressure sensing unit. In a third aspect, an embodiment of the present disclosure provides a manufacturing method for a display panel. The manufacturing method includes: providing a substrate, and manufacturing a first insulating layer, a first metal layer, a second insulating layer, a second metal layer, a third insulating layer, a third metal layer, a fourth insulating layer and a fifth insulating layer on the substrate sequentially, where the substrate includes a hole area and a non-hole area; manufacturing a first wire extending in a first direction in the non-hole area, where the first wire includes a first sub-wire portion, a second sub-wire portion, a first auxiliary portion and a second auxiliary portion; and manufacturing a second wire extending in a second direction in the non-hole area, where the second wire includes a third sub-wire portion and a third auxiliary portion, and the first direction is different from the second direction; where the third sub-wire portion and the first auxiliary portion are manufactured at the first metal layer, the second auxiliary portion is manufactured at the second metal layer, and the first sub-wire portion, the second sub-wire portion and the third auxiliary portion are manufactured at the third metal layer; and the non-hole area includes a winding area, and at least some of the first auxiliary portion, the second auxiliary portion or the third auxiliary portion are manufactured in the winding area. In a possible implementation, the method further includes: manufacturing an active layer, a first gate insulating layer, a first gate, an interlayer insulating layer, a source-drain layer, a passivation layer and a planarization layer on the substrate sequentially; where the first gate insulating layer is a part of the first insulating layer, the first gate is a part of the first metal layer, the interlayer insulating layer is a part of the third insulating layer, the source-drain layer is a part of the third metal layer, the passivation layer is a part of the fourth insulating layer, and the planarization layer is a part of the fifth insulating layer; and the manufacturing method for a display panel further includes: manufacturing a first via hole at least penetrating the third insulating layer to cause the first sub-wire portion to be electrically connected to the first auxiliary portion; manufacturing a second via hole at least penetrating the third insulating layer to cause the second sub-wire portion to be electrically connected to the second auxiliary portion; and manufacturing a third via hole at least penetrating the third insulating layer to cause the third sub-wire portion to be electrically connected to the third auxiliary portion. In a possible implementation, the method further includes: manufacturing a fourth metal layer on one side of the third metal layer away from the substrate, and manufacturing a fourth auxiliary portion at the fourth metal layer; wherein the manufacturing the second wire extending in the second direction in the non-hole area further includes: manufacturing a fourth sub-wire portion extending in the second direction; manufacturing a first bridge portion and a second bridge portion at the third metal layer; manufacturing a sixth via hole at least penetrating the third insulating layer to cause an nth row of fourth sub-wire portion to be electrically connected to the second bridge portion; manufacturing a fifth via hole at least penetrating the third insulating layer to cause an (n+1)th row of fourth sub-wire portion to be electrically connected to the first bridge portion; and manufacturing a fourth via hole at least penetrating the fourth insulating layer and the fifth insulating layer to cause the first bridge portion and the second bridge portion to be electrically connected to the fourth auxiliary portion, where n is an integer greater than or equal to 1. In a possible implementation, the method further includes: the manufacturing the second wire extending in the second direction in the non-hole area includes: manufacturing a fifth sub-wire portion extending in the second direction; manufacturing a third bridge portion at the third metal layer; manufacturing a seventh via hole at least penetrating the third insulating layer to cause an mth row of third sub-wire portion to be electrically connected to the third bridge portion; and manufacturing an eighth via hole at least penetrating the third insulating layer to cause an (m+1)th row of fifth sub-wire portion to be electrically connected to the third bridge portion; where the third bridge portion is electrically connected to the third auxiliary portion through the seventh via hole or the eighth via hole, and m is an integer greater than or equal to 1. The patent or application file contains at least one drawing executed in color. Copies of this patent or patent application publication with color drawing(s) will be provided by the Office upon request and payment of the necessary fee. In order to make the objectives, technical solutions, and advantages in the embodiments of the present disclosure clearer, the technical solutions in the embodiments of the present disclosure will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present disclosure. It is obvious that the described embodiments are some rather than all of the embodiments of the present disclosure. Based on the described embodiments of the present disclosure, all other embodiments obtained by a person of ordinary skill in the art without making inventive efforts fall within the scope of protection of the present disclosure. Unless otherwise defined, technical or scientific terms used herein should have ordinary meanings as understood by those of ordinary skill in the art to which the present disclosure belongs. “First”, “second” and similar words used in the present disclosure do not mean any order, quantity or importance, but are only used for distinguishing different components. Similarly, “comprise”, “include” and similar words are intended to mean that an element or item in front of the word encompasses elements or items that are listed behind the word and equivalents thereof, but do not exclude other elements or items. “Connect”, “connected” and similar words are not limited to a physical or mechanical connection, but can include an electrical connection, whether direct or indirect. “Up”, “down”, “left”, “right”, etc. are merely configured to indicate relative position relations, and when the absolute position of an object described changes, the relative position can change accordingly. In the description below, when an element or layer is described as being “on” or “connected to” another element or layer, it can be directly on or connected to another element or layer, or an intervening element or layer can be present. When an element or layer is described as being “on” “one side” of another element or layer, it can be directly on or connected to another element or layer, or an intervening element or layer can be present. However, when an element or layer is described as being “directly on” or “directly connected to” another element or layer, an intervening element or layer is absent. The term “and/or” includes any and all combinations of one or more of the associated listed items. In order to pursue increase in a screen-to-body ratio of a display screen, punch-hole screens are increasingly used. As shown in The first sub-wire portion 011 and the second sub-wire portion 021 are at the third metal layer 003, the first auxiliary portion 012 is at the first metal layer 001, the second auxiliary portion 022 is at the second metal layer 002, the third sub-wire portion 031 is at the first metal layer 001, and the third auxiliary portion 032 is at the third metal layer 003. The first auxiliary portion 012 includes a first winding structure 0121 in the winding area WA and further includes a first connection structure 0122 between the first winding structure 0121 and the first sub-wire portion 011. The second auxiliary portion 022 includes a second winding structure in the winding area WA and further includes a second connection structure 0222 between the second winding structure 0221 and the second sub-wire portion 021. The third auxiliary portion 032 includes a third winding structure 0321 in the winding area WA, and further includes a third connection structure 0322 between the third winding structure 0321 and the third sub-wire portion 031. Wire widths shown in the figures of the present disclosure are merely for clearer illustration and to distinguish different wires, are not representative of actual wire widths, and are not intended to be limiting of the present disclosure. Sizes and proportions of the hole area, the winding area, the display panel and other areas in the figures are merely schematic and are not intended to be limiting of the present disclosure. Projections of the first auxiliary portion and the second auxiliary portion on the substrate are arranged alternately. As shown in In the embodiment of the present disclosure, the third sub-wire portion 031 at the first metal layer is switched to the third auxiliary portion 032 at the third metal layer, to carry out winding transmission in the winding area. The first sub-wire portion 011 at the third metal layer is switched to the first auxiliary portion 012 at the first metal layer, to carry out winding transmission in the winding area. The second sub-wire portion 021 at the third metal layer is switched to the second auxiliary portion 022 at the second metal layer, to carry out winding transmission in the winding area. In a direction from the hole area HA to an outer boundary of the winding area WA, the projections of the first auxiliary portion 012 and the second auxiliary portion 022 on the substrate are arranged alternately. In this way, the adjacent winding structures in the winding area are distributed on different metal layers, signal interference between adjacent wires is weakened, a distance between the adjacent wires may be shortened, and then the border of the hole area may be reduced on the premise that the number of the wires is not reduced. Illustratively, the third sub-wire portion 031 originally at the first metal layer is switched to the third connection structure 0322 at the third metal layer and then is connected to the third winding structure 0321 to carry out winding transmission in the winding area. The first sub-wire portion 011 originally at the third metal layer is switched to the first connection structure 0122 at the first metal layer and then is connected to the first winding structure 0121 to carry out winding transmission in the winding area. The second sub-wire portion 021 originally at the third metal layer is switched to the second connection structure 0222 at the second metal layer and then is connected to the second winding structure 0221 to carry out winding transmission in the winding area. Projections of the first winding structure 0121 and the second winding structure 0221 on the substrate are arranged alternately. The adjacent winding structures in the winding area are distributed on different metal layers, signal interference between adjacent wires is weakened, a distance between the adjacent wires may be shortened, and then the border of the hole area may be reduced on the premise that the number of the wires is not reduced. In the embodiment of the present disclosure, the first sub-wire portion is electrically connected to the first auxiliary portion through a first via hole, the second sub-wire portion is electrically connected to the second auxiliary portion through a second via hole, and the third sub-wire portion is electrically connected to the third auxiliary portion through a third via hole. Illustratively, at a dashed box AA in Illustratively, at a dashed box BB in Illustratively, at a dashed box CC in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, the display panel further includes a first bridge portion, the first bridge portion is at the third metal layer, a fifth via hole is provided in the first bridge portion, and the fifth via hole makes the fourth sub-wire portion be electrically connected to the first bridge portion. The first bridge portion is electrically connected to the fourth auxiliary portion through a fourth via hole. Illustratively, at a dashed box DD in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, projections of the fourth sub-wire portion and the winding area on the substrate do not overlap with each other, and the fourth sub-wire portion configured to transmit one row of light-emitting control signal is cut off in the winding area. Illustratively, as shown in In another embodiment of the present disclosure, as shown in As shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, as shown in In the embodiment of the present disclosure, a shape of the hole area includes a circle, an oval, a triangle, a quadrangle, or an irregular shape, but is not limited thereto. Specifically, the shape of the hole area may be designed according to a shape, an appearance, or other conditions of a product, and is not limited by the present disclosure. The shape of the winding area may be determined according to the shape of the hole area and may also be different from the shape of the hole area, and is not limited by the present disclosure. Preferably, the hole area and the winding area are the same in shape and are both of a circular or oval, and such a shape is conducive to wire winding. In the embodiment of the present disclosure, as shown in According to the embodiment provided in the present disclosure, parts of the first wire and the second wire in the winding area are switched into different metal layers, such that the adjacent wires in the winding area are distributed at the different metal layers, signal interference between the wires may be reduced, the wires may be more densely distributed, and therefore, the border of the hole area is reduced on the premise that the wires are not reduced. In addition, the embodiment provided in the present disclosure proposes that the fifth sub-wire portion configured to transmit the (m+1)th row of reset signal and the third sub-wire portion configured to transmit the mth row of first gate signal are combined for transmission in the winding area, such that the number of the wires in the winding area may be reduced, and the border of the hole area may be reduced. Moreover, the embodiment provided in the present further proposes that the fourth sub-wire portion configured to transmit the light-emitting control signal is cut off in the winding area, such that the number of the wires in the winding area may be further reduced, and a smaller border of the hole area may be obtained. The embodiment provided in the present disclosure is favorable for full-screen display. According to the embodiment of the present disclosure, the display panel includes one hole area as an example, but the present disclosure is not limited thereto, one, two or more hole areas may be provided in the display panel, and wires surrounding different hole areas may use the design of the present disclosure. Based on the same inventive concept, an embodiment of the present disclosure further provides a display device. As shown in Illustratively, as shown in The display device provided in the embodiment of the present disclosure may be any product or component with a display function, such as a mobile phone, a tablet computer, a television, a display, a notebook computer, a digital photo frame and a navigator. Other essential components of the display device will be understood by those of ordinary skill in the art, and are not repeated herein, nor are they intended to be limiting of the present disclosure. Based on the same inventive concept, an embodiment of the present disclosure further provides a manufacturing method for a display device. As shown in A substrate is provided, and a first insulating layer, a first metal layer, a second insulating layer, a second metal layer, a third insulating layer, a third metal layer, a fourth insulating layer and a fifth insulating layer are sequentially manufactured on the substrate. The substrate of the display panel includes a hole area and a non-hole area; manufacture a first wire extending in a first direction in the non-hole area, where the first wire includes a first sub-wire portion, a second sub-wire portion, a first auxiliary portion and a second auxiliary portion; and manufacture a second wire extending in a second direction in the non-hole area, where the second wire includes a third sub-wire portion and a third auxiliary portion, and the first direction is different from the second direction. The third sub-wire portion and the first auxiliary portion are manufactured at the first metal layer, the second auxiliary portion is manufactured at the second metal layer, and the first sub-wire portion, the second sub-wire portion and the third auxiliary portion are manufactured at the third metal layer. The non-hole area includes a winding area, and at least some of the first auxiliary portion, the second auxiliary portion or the third auxiliary portion are manufactured in the winding area. The manufacturing method for a display panel provided in the embodiment of the disclosure further includes: manufacturing a thin film transistor on the substrate, where this step by the following. An active layer, a first gate insulating layer, a first gate, an interlayer insulating layer, a source-drain layer, a passivation layer and a planarization layer are sequentially manufactured on the substrate. The first gate insulating layer is a part of the first insulating layer, the first gate is a part of the first metal layer, the interlayer insulating layer is a part of the third insulating layer, the source-drain layer is a part of the third metal layer, the passivation layer is a part of the fourth insulating layer, and the planarization layer is a part of the fifth insulating layer. The manufacturing method for a display panel further includes: manufacturing a first via hole at least penetrating the third insulating layer to make the first sub-wire portion be electrically connected to the first auxiliary portion; manufacturing a second via hole at least penetrating the third insulating layer to make the second sub-wire portion be electrically connected to the second auxiliary portion; and manufacturing a third via hole at least penetrating the third insulating layer to make the third sub-wire portion be electrically connected to the third auxiliary portion. The manufacturing method for a display panel provided in the embodiment of the disclosure further includes: manufacturing a fourth metal layer on one side of the third metal layer away from the substrate, and manufacturing a fourth auxiliary portion at the fourth metal layer. The step of manufacturing the second wire extending in the second direction in the non-hole area further includes: manufacturing a fourth sub-wire portion extending in the second direction; manufacturing a first bridge portion and a second bridge portion at the third metal layer; manufacturing a sixth via hole at least penetrating the third insulating layer to make an nth row of fourth sub-wire portion be electrically connected to the second bridge portion; manufacturing a fifth via hole at least penetrating the third insulating layer to make an (n+1)th row of fourth sub-wire portion be electrically connected to the first bridge portion; and manufacturing a fourth via hole at least penetrating the fourth insulating layer and the fifth insulating layer to make the first bridge portion and the second bridge portion be electrically connected to the fourth auxiliary portion. Where n is an integer greater than or equal to 1. In the manufacturing method for a display panel provided in the embodiment of the disclosure, the step of manufacturing the second wire extending in the second direction in the non-hole area further includes: manufacturing a fifth sub-wire portion extending in the second direction; manufacturing a third bridge portion at the third metal layer; manufacturing a seventh via hole at least penetrating the third insulating layer to make an mth row of third sub-wire portion be electrically connected to the third bridge portion; and manufacturing an eighth via hole at least penetrating the third insulating layer to make an (m+1)th row of fifth sub-wire portion be electrically connected to the third bridge portion. The third bridge portion is electrically connected to the third auxiliary portion through the seventh via hole or the eighth via hole, and m is an integer greater than or equal to 1. Apparently, those skilled in the art can make various modifications and variations to the present disclosure without departing from the spirit and scope of the present disclosure. In this way, if amendments and variations to the present disclosure fall within the scope of the claims of the present disclosure and the equivalents thereof, it is intended that the present disclosure also encompasses these amendments and variations. A display panel (1), a display device, and a manufacturing method for the display panel (1). The display panel (1) comprises a base substrate (100). The base substrate (100) is provided with a first metal layer (001), a second metal layer (002), and a third metal layer (003) thereon. The display panel (1) further comprises traces. The traces comprise a first trace extending in a first direction, and a second trace extending in a second direction. The first trace comprises a first sub-trace portion (011), a second sub-trace portion (021), a first auxiliary portion (012), and a second auxiliary portion (022). The second trace comprises a third sub-trace portion (031) and a third auxiliary portion (032). The first direction is different from the second direction. The first sub-trace portion (011) and the second sub-trace portion (021) are located at the third metal layer (003). 1. A display panel, comprising: a substrate, and a first metal layer, a second metal layer and a third metal layer that are stacked on the substrate sequentially, and

further comprising wires, wherein the wires comprise: a first wire extending in a first direction, wherein the first wire comprises a first sub-wire portion, a second sub-wire portion, a first auxiliary portion and a second auxiliary portion; and a second wire extending in a second direction, wherein the second wire comprises a third sub-wire portion and a third auxiliary portion; wherein the first direction is different from the second direction; the first sub-wire portion and the second sub-wire portion are at the third metal layer, the first auxiliary portion is at the first metal layer, the second auxiliary portion is at the second metal layer, the third sub-wire portion is at the first metal layer, and the third auxiliary portion is at the third metal layer; the substrate comprises a hole area and a non-hole area, and the non-hole area comprises a winding area; and the first auxiliary portion, the second auxiliary portion, and the third auxiliary portion each comprise a winding structure provided within the winding area. 2. The display panel according to 3-4. (canceled) 5. The display panel according to 6. (canceled) 7. The display panel according to 8-10. (canceled) 11. The display panel according to the first sub-wire portion, the second sub-wire portion, the first bridge portion and the third auxiliary portion that are at the third metal layer are insulated from one another; and the first auxiliary portion, the second auxiliary portion, the third auxiliary portion and the fourth auxiliary portion are insulated from one another. 12. The display panel according to 13. The display panel according to the drive circuit comprises a thin film transistor, and the thin film transistor comprises: an active layer on the substrate; a first gate insulating layer on one side of the active layer away from the substrate, wherein the first insulating layer comprises the first gate insulating layer; a first gate on one side of the first gate insulating layer away from the substrate, wherein the first metal layer comprises the first gate; an interlayer insulating layer on one side of the first gate away from the substrate, wherein the third insulating layer comprises the interlayer insulating layer; a source-drain layer on one side of the interlayer insulating layer away from the substrate, wherein the third metal layer comprises the source-drain layer; a passivation layer on one side of the source-drain layer away from the substrate, wherein the fourth insulating layer comprises the passivation layer; and a planarization layer on one side of the passivation layer away from the substrate, wherein the fifth insulating layer comprises the planarization layer. 14. The display panel according to 15-18. (canceled) 19. The display panel according to 20. The display panel according to 21. (canceled) 22. The display panel according to 23. The display panel according to 24. The display panel according to 25. The display panel according to 26. The display panel according to 27. (canceled) 28. The display panel according to 29. The display panel according to 30. The display panel according to 31. (canceled) 32. The display panel according to 33. (canceled) 34. A display device, comprising the display panel according to 35-40. (canceled)CROSS REFERENCE TO RELATED APPLICATION

FIELD

BACKGROUND

SUMMARY

BRIEF DESCRIPTION OF THE DRAWINGS

DETAILED DESCRIPTION OF THE EMBODIMENTS