ONE-TIME PROGRAMMABLE MEMORY CELL

CELLULE MEMOIRE A PROGRAMMATION UNIQUE La présente invention concerne le domaine des mémoires à programmation unique (OTP) et, plus particulièrement, la réalisation d'une cellule mémoire à programmation unique qui permet le stockage d'un code binaire dans un circuit intégré, sans que ce code soit observable. Aujourd'hui, pour réaliser une mémoire à programmation unique, on peut utiliser des éléments de type fusibles constitués de pistes en silicium polycristallin. De tels fusibles ont l'inconvénient d'avoir un état (ouvert ou fermé) détectable optiquement. En effet, un élément fusible en silicium polycristallin est détruit en le soumettant à un courant de l'ordre du dixième d'ampère, ce qui engendre une détérioration physique de la piste conductrice le constituant. Un autre inconvénient est que le fort courant nécessaire impose de détruire le fusible à la fabrication et est peu compatible avec la réalisation d'une cellule mémoire à programmation unique dont la programmation peut être faite dans la vie du produit. Une deuxième catégorie connue de mémoires à programmation unique est constituée des mémoires EPROM. Ces mémoires ont l'inconvénient de nécessiter des transistors (transistors à grilles flottantes) qui engendrent des étapes de fabrication supplémentaires par rapport aux étapes des

technologies MOS standard. Un autre inconvénient est que le contenu d'une telle cellule mémoire est observable, hors fonctionnement, par examen des charges contenues dans cette cellule, c'est-à-dire au moyen d'un microscope à balayage électronique. En effet, le nombre de charges dans les grilles flottantes des transistors est différent selon la programmation de la cellule mémoire. Cette différence du nombre de charges peut être détectée par un microscope à balayage électronique, ce qui nuit à 1 'inviolabilité du stockage. On trouve aussi des mémoires à programmation unique réalisées par des EEPROM et des mémoires flash non effaçables qui présentent des inconvénients similaires à ceux indiqués ci-dessus. Un autre inconvénient des mémoires EPROM est qu'elles sont sensibles aux ultraviolets. Un exemple d'application de la présente invention concerne le domaine des cartes à puce dans lesquelles des codes binaires doivent être stockés sans risquer d'être piraté par un fraudeur. Ces codes peuvent représenter des clés d'algorithme de transaction ou tout autre clé de chiffrement, d'identification ou d'authentification. Plus généralement, la présente invention s'applique à tout système dans lequel on souhaite programmer de façon irréversible (c'est-à-dire par une programmation unique), ou à tout le moins un nombre de fois limité, un mot binaire dans un circuit intégré, sans que le résultat de cette programmation soit observable. La présente invention vise à proposer une nouvelle structure de cellule mémoire à programmation unique qui présente ces caractéristiques. L' invention vise également à proposer une cellule mémoire à programmation unique qui puisse être programmée après fabrication du circuit intégré, alors que celui-ci est dans son environnement applicatif . L'invention vise également à proposer une cellule mémoire dont la programmation ne soit pas observable, que ce

soit optiquement ou, hors fonctionnement, par microscope à balayage électronique. L'invention vise également à proposer une cellule mémoire à programmation unique qui puisse être réalisée dans la même technologie que les transistors MOS du circuit intégré auquel elle est jointe, et sans être sensible aux ultraviolets. L'invention vise également à proposer une mémoire à base de telles cellules qui soit compatible avec une structure différentielle . Pour atteindre ces objets et d'autres, la présente invention prévoit de façon générale une cellule mémoire d'une valeur binaire comportant : deux branches parallèles comprenant chacune au moins une résistance de programmation en silicium polycristallin connectée entre une première borne d'alimentation et un point ou borne de lecture différentielle de 1 'état de la cellule ; et au moins un premier interrupteur reliant, lors d'une programmation, une desdites bornes de lecture à une deuxième borne d'alimentation. Selon un mode de réalisation de la présente invention, chaque branche comporte un premier interrupteur reliant, lors d'une programmation, la borne de lecture de la branche à ladite deuxième borne d'alimentation. L'invention prévoit également une cellule mémoire d'une valeur binaire, comportant : deux branches parallèles comprenant chacune, en série entre deux bornes d'application d'une tension d'alimentation, une résistance de programmation en silicium polycristallin et une résistance fixe, les résistances fixes des deux branches étant, de préférence, identiques ; un amplificateur différentiel dont les entrées respectives sont reliées aux points milieux entre les résistances de chaque branche constituant des point de lecture différentielle de l'état de la cellule, la sortie de

1 ' amplificateur fournissant la valeur binaire stockée dans la cellule ; et au moins un premier interrupteur court-circuitant, lors d'une programmation, une desdites résistances fixes. L' invention prévoit également une cellule mémoire d'une valeur binaire, comportant : deux branches parallèles comprenant chacune, en série entre deux bornes d'application d'une tension d'alimentation, une résistance de programmation en silicium polycristallin, un premier transistor et un deuxième transistor, le point milieu entre la résistance et le premier transistor définissant une borne de lecture directe ou inverse de la valeur binaire stockée dans la cellule, les grilles des deuxièmes transistors recevant un signal de sélection de la cellule et la grille du premier transistor de chaque branche étant reliée au point de lecture de 1 ' autre branche ; et au moins un premier interrupteur reliant, lors d'une programmation, une desdites bornes de lecture à une desdites bornes d'application de la tension d'alimentation. L'invention prévoit également une cellule mémoire d'une valeur binaire, comportant deux branches parallèles comprenant chacune, en série entre une première borne d'alimentation et un point ou borne de lecture différentielle de l'état de la cellule, une résistance de programmation en silicium polycristallin et un premier transistor, deux premiers interrupteurs reliant chacune desdites bornes de lecture respective à une deuxième borne d'application de la tension d' alimentatio . L'invention prévoit également une cellule mémoire d'une valeur binaire, comportant : deux branches parallèles comprenant chacune, en série entre deux bornes d'application d'une tension d'alimentation, un premier transistor deux résistances de programmation en silicium polycristallin et un deuxième transistor, la grille du deuxième transistor de chaque branche étant reliée à 1 ' interconnexion

entre une des résistances et le deuxième transistor de 1 ' autre branche ; un amplificateur différentiel dont deux entrées respectives sont reliées aux points milieux entre les résistances de chaque branche et dont deux sorties inversées sont respectivement reliées aux grilles des premiers transistors ; et au moins un premier interrupteur court-circuitant, lors d'une programmation, un desdits deuxièmes transistors. Selon un mode de réalisation de la présente invention, une des bornes d'alimentation est reliée, par l'intermédiaire d'un sélecteur, à au moins deux tensions d'alimentation parmi lesquelles une tension d'alimentation de fonctionnement en lecture relativement faible et une tension d'alimentation de programmation relativement élevée. L'invention prévoit également une cellule mémoire d'une valeur binaire comportant : deux branches parallèles comprenant chacune, en série entre une première borne et d'application d'un potentiel de lecture et une borne d'application d'un potentiel de référence, un premier transistor, une résistance de programmation en silicium polycristallin et un deuxième transistor, le point milieu entre la résistance et le premier transistor de chaque branche définissant un point de lecture différentielle de l'état de la cellule relié aux grilles des transistors de l'autre branche ; et au moins deux premiers interrupteurs d'application, lors d'une programmation, d'un potentiel de programmation à une desdites bornes de lecture. Selon un mode de réalisation de la présente invention, deux deuxièmes interrupteurs de sélection de la cellule sont intercalés entre lesdits points de lecture et les premiers interrupteurs respectifs qui y sont connectés. Selon un mode de réalisation de la présente invention, un interrupteur d'alimentation relie ladite première borne à une

borne d'alimentation en potentiel de lecture, pour interrompre la consommation de la cellule une fois l'état généré. Selon un mode de réalisation de la présente invention, deux troisièmes transistors relient les grilles des premiers et deuxièmes transistors des branches respectives à la borne d'application du potentiel de référence, pour stabiliser l'état généré . Selon un mode de réalisation de la présente invention, ledit interrupteur d'alimentation et lesdits troisièmes transistors sont commandés en même temps. Selon un mode de réalisation de la présente invention, lesdites résistances de programmation sont identiques en taille et en dopage éventuel. Selon un mode de réalisation de la présente invention, la programmation s'effectue en diminuant, de façon irréversible et stable dans la plage de courants de fonctionnement en lecture de la cellule, la valeur d'une des résistances de programmation, en forçant la circulation d'un courant dans une des résistances en silicium polycristallin qui soit supérieur au courant pour lequel la valeur de cette résistance présente un maximum, la programmation étant non destructrice de cette résistance. L'invention prévoit également une mémoire à programmation unique comprenant une pluralité de cellules mémoire se partageant des mêmes premiers interrupteurs. L'invention prévoit également un procédé de programmation d'une cellule mémoire, consistant à imposer temporairement, dans l'une des branches sélectionnée par un des premiers interrupteurs, la circulation d'un courant supérieur à un courant pour lequel la valeur de la résistance de programmation de la branche concernée présente un maximum. Selon un mode de mise en oeuvre de la présente invention, le procédé comprend les étapes suivantes : augmenter pas à pas le courant dans la résistance de programmation sélectionnée par 1 'interrupteur de programmation d'une des branches ; et

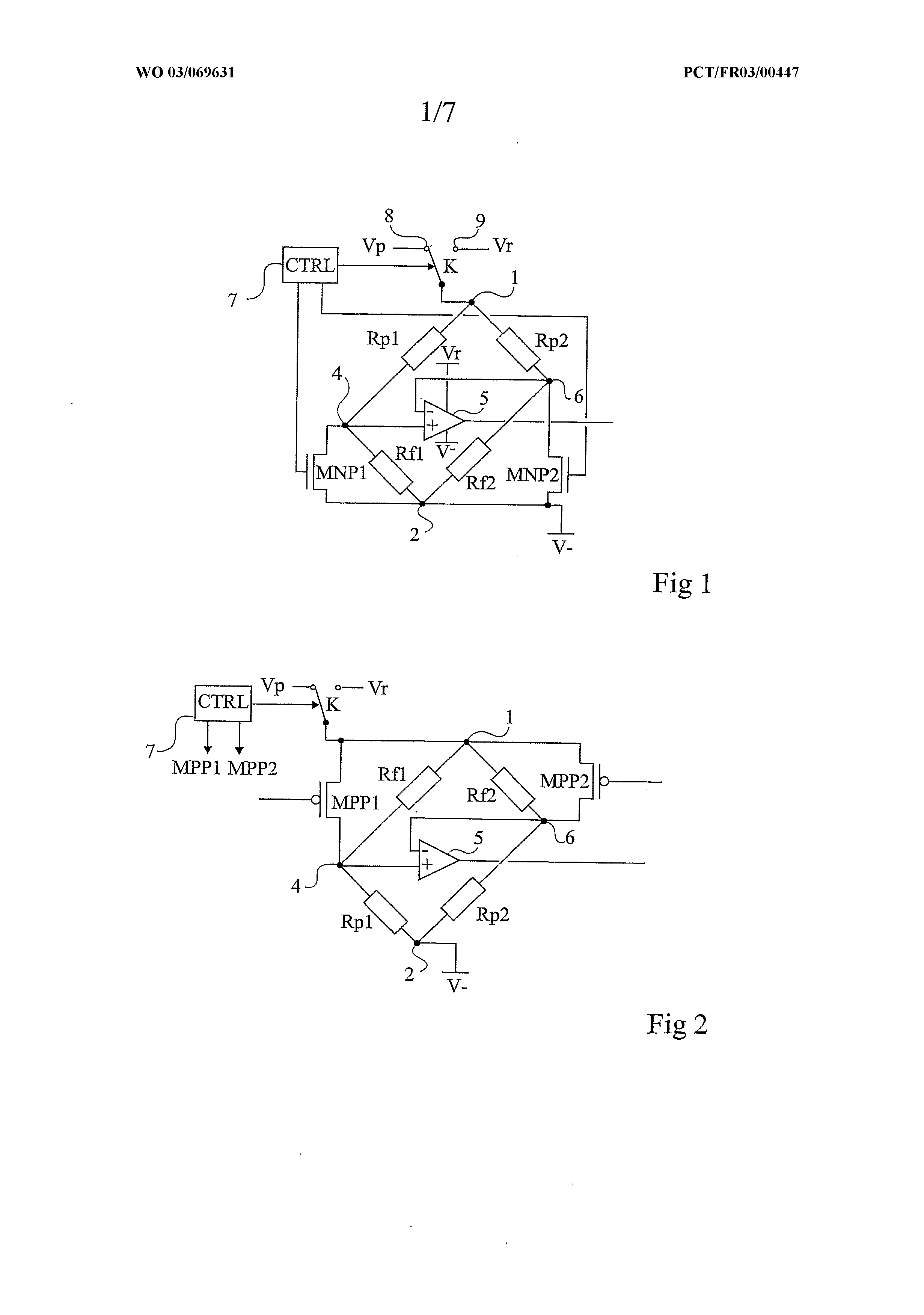

mesurer, après chaque application d'un courant supérieur, la valeur de cette résistance dans son environnement fonctionnel de lecture. Selon un mode de mise en oeuvre de la présente invention, une table prédéterminée de correspondance entre le courant de programmation et la résistance finale souhaitée est utilisée pour appliquer, à la résistance de programmation sélectionnée, le courant de programmation adapté. Ces objets, caractéristiques et avantages, ainsi que d'autres de la présente invention seront exposés en détail dans la description suivante de modes de mise en oeuvre et de réalisation particuliers, faite à titre non-limitatif en relation avec les figures jointes parmi lesquelles : la figure 1 représente le schéma électrique d'une cellule mémoire à programmation unique selon un premier mode de réalisation de la présente invention ; la figure 2 représente le schéma électrique d'une cellule mémoire à programmation unique selon un deuxième mode de réalisation de la présente invention ; la figure 3 représente le schéma électrique d'une cellule mémoire à programmation unique selon un troisième mode de réalisation de la présente invention ; la figure 4 représente le schéma électrique d'une colonne de cellules mémoire selon un quatrième mode de réalisation de l'invention ; la figure 5 représente le schéma électrique d'un mode de réalisation de l'amplificateur de lecture différentiel de la figure 4 ; la figure 6 représente le schéma électrique d'un autre mode de réalisation du circuit de lecture différentiel de la figure 4 ; la figure 7 représente le schéma électrique d'une cellule mémoire à programmation unique selon un cinquième mode de réalisation de l'invention ;

la figure 8 représente un exemple de réalisation d'un amplificateur avec trigger de Schmitt utilisé dans le mode de réalisation de la figure 7 ; la figure 9 représente le schéma électrique d'une cellule mémoire à programmation unique selon un sixième mode de réalisation de la présente invention ; la figure 10 représente, par une vue partielle en perspective très schématique, un mode de réalisation d'une résistance en silicium polycristallin constitutive d'une cellule mémoire selon la présente invention ; la figure 11 illustre, par un réseau de courbes, la programmation d'une cellule mémoire selon un mode de mise en oeuvre de la présente invention ; et la figure 12 représente, de façon très schématique et sous forme de blocs, un exemple d'application de la présente invention à la génération d'un identifiant d'un circuit intégré. Les mêmes éléments ont été désignés par les mêmes références aux différentes figures. Pour des raisons de clarté, seuls les éléments qui sont nécessaires à la compréhension de l'invention ont été représentés aux figures et seront décrits par la suite. En particulier, les différents circuits de lecture et d'exploitation des mots binaires stockés dans une cellule mémoire selon 1 ' invention n'ont pas été détaillés . L' invention peut être mise en oeuvre quelle que soit l'exploitation faite du code binaire stocké dans une ou plusieurs de ces cellules mémoires . Une caractéristique d'une cellule mémoire selon la présente invention est qu'elle comprend deux branches résistives en parallèle. Chaque branche est constituées d'au moins une résistance programmable en silicium polycristallin. La figure 1 représente un premier mode de réalisation d'une cellule mémoire selon l'invention. Selon ce mode de réalisation, chaque branche résistive est constituée de deux résistances en série, la mesure d'un niveau mémorisé s'effectuant en connectant les points milieux

des associations en série aux entrées respectives d'un amplificateur différentiel. La résistance non programmable de chaque branche est court-circuitable au moyen d'un interrupteur de programmatio . Une première branche de la cellule mémoire comprend, en série entre deux bornes 1 et 2 d'application d'une tension d'alimentation, une première résistance programmable Rpl et une première résistance fixe Rfl. Une deuxième branche de la cellule mémoire comprend, en série entre les bornes 1 et 2, une deuxième résistance programmable Rp2 et une deuxième résistance fixe Rf2. Le point milieu 4, entre les résistances Rpl et Rfl, est relié à une première entrée (par exemple, non inverseuse) d'un amplificateur différentiel 5 de lecture. Le point milieu 6, entre les résistances Rp2 et Rf2, est relié à l'autre entrée (par exemple inverseuse) de l'amplificateur différentiel 5. La sortie de 1 ' amplificateur différentiel 5 fournit 1 'état 0 ou 1 stocké dans la cellule mémoire. On voit bien que, si les résistances Rfl et Rf2 sont de même valeur, la moindre différence entre les résistances Rpl et Rp2 conditionne l'état de sortie de l'amplificateur de lecture 5. En d'autres termes, dans l'exemple représenté, si la résistance Rpl est supérieure à la résistance Rρ2, le potentiel du point 6 est supérieur au potentiel du point 4. Il en découle un état zéro (niveau V-) en sortie de l'amplificateur 5. Dans le cas contraire (résistance Rpl inférieure à résistance Rp2) , le point 4 est à un potentiel supérieur au point 6. Il en découle un niveau haut en sortie de l'amplificateur 5 donc un état 1. Selon l'invention, au moins un interrupteur (dans cet exemple, un transistor MOS à canal N MNP1 ou MNP2 de programmation) relie chaque résistance programmable (les points 4 et 6) à la borne 2. Cette borne 2 constitue une borne d'application d'un potentiel d'alimentation de référence V- (par exemple, la masse) . Les transistors MNP1 et MNP2 sont commandables individuellement par un circuit 7 de programmation (CTRL) . Côté alimentation positive (borne 1) , la tension de

fonctionnement (lecture) Vr est, selon ce mode de réalisation, différente d'une tension de programmation Vp. La sélection entre les deux tensions s'effectue, par exemple, au moyen d'un sélecteur K dont une borne est reliée à la borne d'alimentation positive 1 de la cellule mémoire. Les deux autres bornes 8 et 9 de 1 ' interrupteur K sont respectivement reliées à des bornes d'application des potentiels de programmation Vp et de lecture Vr. Dans l'exemple représenté, l'amplificateur 5 est alimenté par la tension de lecture Vr. Cette tension est de préférence telle que le courant dans la cellule est inférieur à la centaine de microampères et plus précisément de l'ordre de 1 à 10 microampères. Selon l'invention, les résistances Rpl et Rp2 sont réalisées de façon identique, c'est-à-dire constituées de pistes en silicium polycristallin ayant des dimensions identiques et des dopages identiques. Les résistances Rfl et Rf2 sont également préférentiellement identiques. La programmation opérée par 1 ' invention sert à déséquilibrer les résistances de programmation Rpl et Rp2 comme cela sera expliqué par la suite. Une caractéristique de la présente invention est de prévoir une programmation de la cellule mémoire en provoquant une diminution irréversible de la valeur d'une des résistances de programmation Rpl ou Rp2 selon l'état souhaité, en forçant la circulation d'un courant dans la résistance à programmer qui soit supérieure au courant pour laquelle la valeur de la résistance présente un maximum. Cette caractéristique de l'invention sera mieux comprise par la suite en relation avec les figures 10 et 11. Pour l'instant, on se contentera de dire que le transistor MNP1 permet de court-circuiter la résistance Rfl et de faire circuler, dans la résistance Rpl, un courant imposé par le niveau de la tension de programmation Vp qui a pour effet d'en diminuer la valeur. Quant au transistor MNP2, il sert, pour l'autre branche, à court-circuiter la résistance Rf2 et à diminuer la valeur de la résistance Rp2 lorsque celle-ci est alimentée par la tension de programmation Vp. Selon celle

des résistances Rpl ou Rp2 dont on diminue la valeur par rapport à l'autre, l'état stocké dans la cellule est différent. Selon ce mode de réalisation de l'invention, la tension de programmation (propre à engendrer un courant, par exemple, de 1 'ordre d'un à 10 milliampères) est supérieure à la tension de lecture pour que le courant de programmation soit situé au-delà de la plage de courants (jusqu'à 100 microampères) de fonctionnement en lecture de la cellule mémoire. Les transistors MNP1 et MNP2 permettent également ici de protéger les résistances Rfl et Rf2 lorsque la cellule mémoire est alimentée par la tension Vp sensiblement plus élevée que la tension Vr. Ils évitent alors, si les résistances Rfl et Rf2 sont en silicium polycristallin, de modifier leurs valeurs lors de la programmation. Initialement (en sortie de fabrication), l'état de la cellule mémoire est indéterminé pourvu que les résistances Rpl et Rp2, respectivement Rfl et Rf2, soient de dimensions identiques. En variante, on peut pré-programmer la valeur d'origine (avant programmation des résistances Rpl et Rp2) en prévoyant des valeurs différentes pour les résistances Rfl et Rf2. Une telle variante permet, connaissant l'état non programmé des cellules, de n'utiliser qu'un transistor de programmation pour diminuer la résistance Rpl ou Rp2 de la branche contenant la résistance Rfl ou Rf2 la plus faible. Bien sûr, on doit alors tenir compte, pour le choix des résistances Rpl et Rp2, de la différence entre les valeurs des résistances Rfl et Rf2 et de la diminution de valeur qui sera effectuée pour programmer la cellule. L'état programmé dans une cellule mémoire selon l'invention n'est observable, ni optiquement, ni au moyen d'un microscope électronique à balayage. En effet, contrairement à l'accumulation de charges effectuée dans une grille flottante, la programmation opérée par l'invention est invisible dans la mesure où elle ne fait que modifier la valeur d'une des résis-

tances en silicium polycristallin, sans qu'elle soit chargée en permanence. De plus, cette modification caractéristique de l'invention est non destructrice à la différence d'un fonctionnement fusible qui consiste à détériorer physiquement la structure d'une résistance en silicium polycristallin. Elle est donc également invisible optiquement. Un autre avantage de l'invention qui ressort déjà de la description qui précède est que le niveau stocké dans une cellule mémoire n'est pas observable par des attaques de type observation de consommation électrique. En effet, la signature en courant (consommation en courant) de la cellule mémoire est indépendante de l'état stocké, la résistance équivalente des deux branches en parallèle étant la même, quelle que soit celle des résistances Rpl ou Rp2 qui a vu sa valeur diminuer pour fixer l'état programmé. La figure 2 représente, par une vue à rapprocher de celle de la figure 1, un deuxième mode de réalisation d'une cellule mémoire à programmation unique selon la présente invention. La seule différence entre ces deux modes de réalisation est que, en figure 2, on prévoit une programmation au moyen de deux transistors MOS à canal P MPP1 et MPP2 au lieu de transistors MOS à canal N. Cela revient à retourner la structure par rapport aux bornes 1 et 2 d'alimentation. En d'autres termes, les résistances fixes Rfl et Rf2 relient la borne d'alimentation positive 1 aux drains respectifs 4 et 6 des transistors MPP1 et MPP2. Les résistances de programmation Rpl et Rp2 relient respectivement ces points 4 et 6 à la borne d'alimentation de référence 2. Les transistors MPP1 et MPP2 sont commandés individuellement par le circuit 7 qui contrôle également la position du commutateur K sélectionnant le mode de fonctionnement en programmation ou en lecture. Bien que cela n'ait pas été représenté en figure 2, l'amplificateur différentiel 5 est toujours alimenté par la tension Vr. Fonctionnellement, la seule différence entre les figures 1 et 2 est que les niveaux de commande fournis par le

circuit 7 sont inversés pour les transistors MPP1 et MPP2 en raison de leur type de canal. Le mode de réalisation de la figure 1 constitue toutefois un mode de réalisation préféré en raison du moindre encombrement des transistors MOS à canal N par rapport aux transistors à canal P. La figure 3 représente un troisième mode de réalisation d'une cellule mémoire à programmation unique selon la présente invention. Comme pour les deux autres modes de réalisation, la cellule comporte deux branches résistives en parallèle entre deux bornes 1 et 2 d'alimentation, et deux interrupteurs de programmation MNP1 et MNP2 (dans cet exemple, des transistors MOS à canal N) , un circuit de commande 7 et un sélecteur K entre deux tensions d'alimentation, respectivement de lecture Vr et de programmation Vp. La programmation d'une cellule telle qu'illustrée par la figure 3 est similaire à celle des cellules des figures 1 et 2. Ce qui change ici, c'est la structure de la cellule pour en permettre la lecture. Une caractéristique de ce mode de réalisation est d'intégrer l'amplificateur de lecture différentiel dans les branches résistives, évitant ainsi le recours aux résistances fixes Rfl et Rf2. Dans le mode de réalisation des figures 1 et 2, les résistances Rfl et Rf2 peuvent être réalisées sous la forme de transistors MOS. Dans le mode de réalisation de la figure 3, une première branche, dite gauche dans l'orientation de la figure, comporte en série, la résistance Rpl, un transistor MOS de lecture MNRl, et un transistor MOS de sélection MNS1. L'inter- connexion entre la résistance Rpl et le transistor MNRl (donc le drain de ce transistor) constitue une première borne S de sortie dite arbitrairement directe (non inversée) . La borne S correspond également au point 4 de liaison de la résistance Rpl au transistor de programmation MNP1. Une deuxième branche, dite droite dans l'orientation de la figure, comporte en série, la

résistance Rp2, un transistor MOS de lecture MNR2, et un transistor MOS de sélection MNS2. L' interconnexion entre la résistance Rp2 et le transistor MR2 (donc le drain de ce transistor) constitue une deuxième borne NS de sortie inverse par rapport à la borne S. La borne NS correspond également au point 6 de liaison de la résistance Rp2 au transistor de programmation MNP2. La grille du transistor MNR2 est reliée à la borne 4 tandis que la grille du transistor MNRl est reliée à la borne 6 pour obtenir l'effet d'un bistable. Les grilles des transistors MNS1 et MNS2 sont reliées ensemble à une borne R destinée à recevoir un signal de sélection en lecture de la cellule 1. Ce signal correspond, de préférence, au signal de sélection de la cellule dans un agencement matriciel de plusieurs cellules mémoires. Il est alors fourni par le décodeur de colonnes ou de lignes. Dans l'exemple représenté, tous les transistors sont à canal N. Le fonctionnement en lecture d'une cellule selon ce mode de réalisation est le suivant. Le circuit 7 de commande provoque la commutation du sélecteur K vers le potentiel Vr. De préférence, il s'agit de son état de repos dans la mesure où l'autre état ne sert qu'en programmation (donc en principe une seule fois) . La borne d'entrée R reçoit un signal (actif à l'état haut) de sélection (ou de configuration en lecture) de la cellule, rendant conducteur les deux transistors MNS1 et MNS2. II en découle qu'une des bornes S et NS voit son potentiel croître plus vite que 1 ' autre . Ce déséquilibre provient de la différence de valeur entre les résistances Rpl et Rp2. Il provoque la conduction d'un des transistors MNRl et MNR2. En raison du croisement des grilles de ces transistors, celui qui conduit le premier est celui dont la grille participe au chemin électrique (depuis la borne 1) de constante de temps la plus faible (la résistance de valeur la plus faible engendre une constante de temps plus faible) , donc celui dont le potentiel de drain croît moins vite que 1 'autre. Une fois conducteur, ce transistor MNR force son drain (donc la borne de

sortie S ou NS correspondante) à la masse, ce qui confirme le blocage du transistor MNR de l'autre branche, donc l'état haut sur la borne de sortie correspondant. La programmation d'une cellule selon ce mode de réali- sation s 'effectue de la même manière que pour les deux premiers modes de réalisation à l'aide des transistors MNP1 et MNP2. Toutefois, les transistors MNS1 et MNS2 de la cellule doivent être bloqués dans la programmation (entrée R au niveau bas) . Ils servent à protéger les transistors de lecture MNRl et MNR2 en rendant leurs sources flottantes. En déconnectant les transistors MNR par leurs sources, les transistors MNS empêchent qu'ils voient entre drain et source la tension élevée Vp. Par conséquent, les transistors MNR et MNS peuvent être dimensionnés en fonction de la tension de lecture Vr. Seuls les transistors de programmation MNP ont besoin d'être dimensionnés pour tenir la tension Vp et supporter le courant relativement élevé (par rapport à la plage de fonctionnement en lecture) servant à programmer la cellule. Un avantage de ce mode de réalisation est qu'il combine la cellule de stockage et son amplificateur de lecture. Comme pour les modes de réalisation des figures 1 et 2, le mode de réalisation de la figure 3 s'applique à des transistors MOS à canal N (mode de réalisation représenté) ou à canal P. La transposition du mode de réalisation de la figure 3 à des transistors MOS à canal P est à la portée de l'homme du métier. Selon une variante de réalisation, on pourra utiliser une seule tension d'alimentation pour la cellule mémoire. On évite ainsi la sélection de la tension d'alimentation entre les niveaux Vp et Vr. Dans ce cas, on choisit une tension d'alimentation suffisante pour imposer la contrainte souhaitée à la programmation des résistances Rpl et Rp2 (figures 1, 2 et 3) . Les valeurs des résistances Rfl et Rf2 (figures 1 et 2) ou les dimensions des transistors MNS1, MNS2, MNRl et MNR2 (figure 3) sont alors choisies en conséquence (par exemple, des valeurs

suffisamment élevées des résistances Rfl et Rf2 pour imposer aux bornes des résistances de programmation une tension suffisamment faible garantissant un fonctionnement dans une plage de courants inférieure à la dizaine ou centaine de microampères) . Un tel mode de réalisation ne constitue cependant pas un mode de réalisation préféré dans la mesure où il impose une consommation permanente de courant relativement important. La figure 4 représente une colonne de cellules mémoire MCI, ... MCi, ... MCn selon un quatrième mode de réalisation de l'invention. Cette figure illustre la possibilité d'association des cellules mémoire à résistance de programmation propre à l'invention dans un réseau matriciel. Pour simplifier, la figure 4 ne représente qu'une seule colonne. On notera toutefois que plusieurs colonnes parallèles peuvent être prévues. Chaque cellule mémoire MCi de la colonne est constituée de deux branches parallèles comprenant chacune, entre une borne 1 d'application d'une tension d'alimentation et une borne respective 4 ou 6 de sortie destinée à être lue par un élément de lecture différentiel 5, une résistance programmable RPli, respectivement RP2i, et un interrupteur (ici, un transistor MOS à canal N) MNSli, respectivement MNS2i, de sélection de la cellule de la colonne. Les bornes 4 et 6, correspondant à des bornes S et NS d'entrée de 1 ' amplificateur différentiel 5 ou de sortie de l'arrangement mémoire, sont respectivement connectées à la deuxième borne 2 d'application de la tension d'alimentation (par exemple, la masse GD) par 1 ' intermédiaire de transistors de programmation MNP1 et MNP2. Les différentes cellules mémoire MCi sont donc en parallèle entre la borne 1 et les bornes 4 et 6. Dans l'exemple représenté, la borne 1 est reliée à des potentiels d'alimentation (lignes 1" et l') respectivement de lecture Vr et de programmation Vp par l'intermédiaire d'un interrupteur K commandé par un circuit de commande (non représenté) selon que l'on souhaite un fonctionnement en lecture ou programmation.

Dans l'exemple représenté, les transistors de programmation MNP1 et MNP2 reçoivent des signaux respectifs Pgl et Pg2 du circuit de commande. En variante, et comme on le verra par la suite en relation avec certains des modes de réalisation de l'amplificateur différentiel, les signaux Pgl et Pg2 peuvent être un seul et même signal de commande en programmation. Dans le circuit de la figure 4, les transistors de sélection MNSli et MNS2i de chaque cellule mémoire sont commandés ensemble par des signaux respectifs Li de sélection de lignes de mots. Cette notation de lignes de mots est utilisée en référence aux désignations habituelles des lignes et colonne dans un plan mémoire. En variante, les signaux de sélection de lignes WLi pourront être divisés en deux signaux séparés de sélection d'une branche par rapport à l'autre, notamment si cela est requis pour la programmation d'une des deux branches alors qu'un unique signal de commande en programmation est utilisé pour les transistors MNP1 et MNP2 simultanément. De l'exposé qui précède, on voit bien que chaque cellule mémoire comprend, en parallèle entre deux bornes d'application de la tension d'alimentation, deux branches comprenant chacune une résistance en silicium polycristallin, et au moins un interrupteur de programmation reliant chaque résistance à la deuxième borne d'alimentation. En raison du besoin de sélection des lignes mémoire, un deuxième interrupteur est connecté en série entre le transistor de programmation et la résistance. Il s'agit du transistor de sélection MNS de la cellule concernée. Différents exemples de réalisation d'éléments de lecture différentielle 5 seront décrits ci-après en relation avec les figures 5 et 6. Les transistors de sélection y ont été omis en raison de l'unicité de l'élément de lecture pour une colonne entière de cellules mémoires telles qu' illustrées par la figure 4. Les transistors de programmation MNP1 et MNP2 ont été représentés pour mieux faire apparaître la liaison avec la

figure 4. On notera toutefois que ceux-ci ne font pas à proprement parler partie des éléments de lecture différentielle. La figure 5 représente un premier exemple d'amplificateur différentiel 5 de lecture détectant une différence de courant entre les deux branches d'une cellule mémoire . Le schéma de la figure 5 est basé sur l'utilisation de deux amplificateurs à transconductance comprenant chacun au moins deux branches parallèles de miroirs de courant. Dans l'exemple représenté, trois branches en parallèles sont prévues pour chacune des branches (S et NS) de sortie de la cellule mémoire . Par exemple, côté borne S (arbitrairement côté branche gauche dans l'orientation de la figure), chaque branche comprend un transistor 41G, 42G et 43G respectivement (par exemple, des transistors MOS à canal N) montés en miroir de courant. Le transistor 41G relie la borne S à la masse 2 et est monté en diode, sa grille et son drain étant interconnectés. Le transistor 42G de la deuxième branche est connecté par sa source à la borne 2 et par son drain au drain d'un transistor MOS à canal P 44G dont la source est reliée à la ligne 1" d'alimentation de la tension de lecture. Côté troisième branche, le transistor 43G est connecté à la ligne 1" d'alimentation par l'intermédiaire d'un transistor MOS à canal P 45G, la source du transistor 43G étant connectée à la masse 2. La même structure est reproduite côté droit de la figure pour la connexion de la borne NS. Le transistor 1D de la première branche est encore monté en diode. Le transistor 44 D de la deuxième branche a sa grille reliée à celle du transistor 44G sur lequel il est monté en miroir de courant, le transistor 44G étant monté en diode avec sa grille interconnectée à son drain. Côté troisième branche, le transistor 45D est monté en diode avec sa grille interconnectée à son drain, et sa grille est reliée à la grille du transistor 45G de la branche de gauche.

La mesure différentielle s 'effectue au moyen d'un amplificateur opérationnel 46 dont les entrées inverseuse et non inverseuse respectives sont connectées aux points 47 et 48 d'interconnexion des transistors 45G, 43G de la troisième branche gauche et 44D et 42D de la deuxième branche droite. En outre, une résistance de mesure R relie les bornes d'entrée de l'amplificateur 46. La sortie OUT de l'amplificateur 46 fournit 1 'état de la cellule mémoire lue. Un avantage du mode de réalisation de la figure 5 est qu'il permet de s'affranchir des dissymêtries éventuelles des constitutions des transistors MOS de sélection et, plus précisément, des dissymétries entre les capacités présentes dans le circuit. Il s'agit donc d'un amplificateur de mesure de résistance pure. On notera que, comme pour l'alimentation de l'amplificateur 46 de la figure 5, seule la tension de lecture Vr alimente les miroirs de courant. La figure 6 représente un autre exemple d'amplificateur de lecture différentielle applicable aux cellules mémoire de la figure 4. La lecture s 'effectue ici en tension. L'amplificateur est constitué de deux transistors MOS (ici à canal N 51G et 51D) reliant respectivement les bornes S et NS à la masse 2, l'un des transistors (par exemple 51G) étant monté en diode et les grilles des transistors 51G et 51D étant interconnectées. Il s'agit donc d'un miroir de courant équilibrant les tensions entre les bornes S et NS en lecture. Le miroir de courant amplifie le décalage, la branche de gauche fixant le courant pour l'autre branche. Par conséquent, si la résistance de la branche de gauche S de la cellule mémoire sélectionnée est plus faible que la résistance de droite de cette cellule, un courant plus important circule dans cette branche de gauche. Comme le transistor miroir de 1 ' autre branche appelle le même courant, le fait que sa résistance de cellules mémoire soit plus forte conduit à ce que le point A de lecture en tension chute à une tension basse (la masse aux résistances

série des transistors à l'état passant prêt). Ce point A est relié à la grille d'un transistor MOS 52 de lecture, connecté en série avec une source de courant constant 53 entre la borne 1 ' d'application de la tension de lecture Vr et la masse 2. Le point d'interconnexion entre le transistor 52 et la borne 53 traverse, le cas échéant, un inverseur 54 dont la borne de sortie fournit l'état de la cellule sélectionnée. Quand le point A est à un potentiel voisin de la masse, le transistor 52 est bloqué. Dans le cas inverse, ce transistor conduit. On obtient bien un basculement de la sortie OUT de l'amplificateur de lecture différentielle. Selon une variante de réalisation, le point de lecture (grille du transistor 52) est relié à la ligne S pourvu que ce soit alors le transistor 51D de la ligne qui soit monté en diode. Comme pour le montage de la figure 5, lorsqu'on veut effectuer une programmation d'une des cellules mémoire, celle-ci est sélectionnée grâce à son signal WLi (figure 4) et on rend conducteur le transistor MNP1 ou MNP2 de la branche dont on souhaite diminuer la valeur de la résistance de programmation en silicium polycristallin. La figure 7 représente un cinquième mode de réalisation d'une cellule mémoire à programmation unique selon l'invention. Cette cellule est basée sur l'utilisation d'un amplificateur ou comparateur avec hystérésis (communément appelée trigger de Schmitt) 61 constituant en même temps un élément de lecture différentielle. Comme pour les autres modes de réalisation, la cellule comporte deux branches parallèles comprenant, chacune en série entre des bornes 1 et 2 d'application d'une tension d'alimentation, un élément résistif RP1, RP2 programmable et au moins un interrupteur constituant un transistor de programmation MNP1, MNP2. Dans l'exemple de la figure 7, chaque branche comporte également, pour sa lecture, un transistor MOS à canal P 62G, 62D reliant la borne 1 à une première borne de l'élément

résistif RP1, RP2 respectivement et un transistor MOS à canal N 63G, 63D reliant respectivement l'autre borne de l'élément résistif RP1, RP2 à la masse 2. Les grilles respectives des transistors 63G et 63D sont reliées au drain du transistor opposé, c'est-à-dire aux drains respectifs des transistors de programmation MNP1 et MNP2. Les éléments résistifs RP1 et RP2 sont chacun constitués de deux résistances en série RP11, RP12 et RP21, RP22 dont les points milieux respectifs sont connectés aux entrées non inverseuse et inverseuse du trigger de Schmitt 61. Les sorties respectives du trigger de Schmitt sont connectées aux grilles des transistors 62G et 62D. La borne 1 d'alimentation positive est connectée aux tensions Vp et Vr au moyen d'un circuit d'interrupteurs K. Ici, une variante du circuit d'interrupteurs a été illustrée sous la forme de deux interrupteurs Kl et K2 reliant respectivement les bornes l' et 1" d'application des tensions Vr et Vp à la borne 1. Bien entendu, les interrupteurs Kl et K2 ne sont pas fermés simultanément . En lecture, dès que la cellule est alimentée sous la tension Vr, le trigger de Schmitt 61 rend passant les deux transistors 62G et 62D. Le montage à bascule du bas de la cellule (transistors 63G et 63D) détecte le déséquilibre entre les résistances Rpl et Rp2. Le trigger 61 lit ce déséquilibre et bloque le transistor 62G ou 62D de la branche possédant la valeur de résistance RP1 ou RP2 la plus élevée. Un avantage de la cellule mémoire de la figure 7 est qu'une fois la lecture effectuée, aucun courant ne circule dans la cellule. Un autre avantage de la présence du trigger 61 est qu'il permet la détection d'un faible déséquilibre sans attendre que la bascule 63G, 63D ait bloqué complètement un des transistors 63G et 63D. Dans l'exemple représenté, les sorties respectives directes OUT et inverse NOUT de la cellule sont constituées par

les grilles des transistors 63D et 63G. En variante et comme cela est illustré en pointillés en figure 7, les grilles des transistors 62G et 62D (les sorties du trigger de Schmitt) peuvent également servir de sortie de la cellule. La programmation d'une cellule mémoire telle qu'illustrée par la figure s'effectue en deux temps. Dans une première phase, on rend passant l'un des transistors de programmation (par exemple MNP2) grâce au signal Pg2. Le déséquilibre alors introduit bloque le transistor 62D et passant le transistor 62G. Cet état est stable dans la mesure où on impose une résistance inférieure sur la branche de gauche. Dans une deuxième étape, on commute vers la tension de programmation Vp grâce aux interrupteurs Kl et K2, et on ferme 1 ' interrupteur de programmation MNP1 grâce au signal Pgl pour forcer ce courant à circuler dans la branche de gauche et programmer ainsi, par diminution de leurs valeurs, les résistances RP11 et RP12. Aucun courant ne circule dans les résistances de droite grâce à l'état ouvert du transistor 62D qui l'isole de la tension de programmation. Si l'on souhaite programmer la cellule dans l'autre sens, on inverse le fonctionnement exposé ci-dessus. Le trigger de Schmitt 61 sert donc non seulement en lecture à éviter la consommation de la cellule mais également à sélectionner la branche à programmer. Selon une variante de réalisation où 1 ' on souhaite simplement confirmer un état initial (de fabrication) de la cellule, les signaux Pgl et Pg2 peuvent être confondus, la programmation confirme alors 1 'état initial en diminuant la valeur de la résistance RP1 ou RP2 qui, à l'état issu de fabrication, présente déjà une valeur légèrement inférieure. On notera que le mode de réalisation de la figure 7 est compatible avec l'utilisation d'une seule tension d'alimentation, celle-ci étant alors fixée au niveau de la tension de programmation Vp. En effet, en lecture, dès que l'état est confirmé par le trigger de Schmitt, on ne risque pas

de programmer les résistances dans la mesure où il n'y a plus de courant. On doit pour cela veiller à ce que le courant de lecture ne dure pas suffisamment longtemps pour entraîner une programmation. En d'autres termes, la durée d'application de la tension d'alimentation de la cellule doit être choisie suffisamment faible pour être compatible avec l'utilisation d'une seule tension d'alimentation. Dans le cas où les deux tensions sont utilisées, le trigger de Schmitt 61 est alimenté sous la tension Vr. En variante, la programmation peut s'effectuer en une seule étape en prévoyant des transistors supplémentaires court- circuitant les transistors 62G et 62D respectivement pour programmer la cellule. Le trigger 61 ne sert alors qu'en lecture . La figure 8 illustre un exemple de réalisation du trigger de Schmitt 61 de la figure 7. Celui-ci comprend deux structures symétriques en parallèle entre une source de courant 64 alimentée par la tension Vp ou Vr (borne 1) et la masse 2. Chaque structure comporte, entre la borne 65 de sortie de la source 64 et la masse, un transistor MOS à canal P 66D ou 66G dont les grilles respectives constituent les bornes inverseuse - et non-inverseuse + d'entrée, et dont les drains respectifs définissent les bornes de sortie reliées aux grilles des transistors 62G et 62D. Chacune des bornes 62G et 62D est reliée à la masse 2 par une association en série de deux transistors MOS à canal N 67G, 68G et 67D, 68D. Les transistors 67G et 67D sont montés en diodes, leurs grilles et drains respectifs étant interconnectés. Les grilles respectives des transistors 68G et 68D sont connectées aux drains des transistors 67D et 67G de la branche opposée. Un transistor MOS à canal N 69G ou 69D respectivement est monté en miroir de courant sur les transistors 67G et 67D. Ces transistors sont connectés entre les bornes 62D et 62G respectivement et, par l'intermédiaire de deux transistors MOS à canal N 70G et 70D, à la masse 2 pour garantir l'hystérésis pendant la lecture. Les grilles des transistors 70G

et 70D reçoivent un signal CT de commande, actif uniquement pendant la lecture et bloquant les transistors 70G et 70D afin d'éviter une consommation dans l'amplificateur après lecture. Le fonctionnement d'un trigger de Schmitt 61 tel que qu'illustré par la figure 8 est parfaitement connu. Dès qu'un déséquilibre apparaît entre le niveau de tension d'une des entrées - ou + (grille des transistors 66D et 66G) , ce déséquilibre est verrouillé grâce à la structure en miroir de courant croisée de la partie basse du montage. La cellule 9 représente un sixième mode de réalisation d'une cellule selon la présente invention. Comme la cellule mémoire précédente, la cellule de la figure 9 présente 1 ' avantage de verrouiller un état stable permettant de supprimer l'alimentation permanente (la consommation) de la cellule une fois l'état lu généré. La cellule mémoire MC proprement dite comprend deux branches parallèles constituées chacune d'un transistor MOS à canal P 81G, 81D, d'une résistance de programmation RP1, RP2, d'un transistor MOS à canal N 82G, 82D entre une borne 83 reliée à la tension d'alimentation de lecture Vr (borne l') par 1 ' intermédiaire d'un transistor MOS à canal P 84, et la masse 2. Le transistor 84 est destiné à être commandé par un signal COM d'alimentation de la structure lors d'une lecture. Quand il est ouvert, aucune consommation n'est engendrée dans les branches parallèles décrites précédemment. Le signal COM est également envoyé aux grilles de deux transistors MOS à canal N 85G, 85D connectés entre les grilles respectives des transistors 81G et 81D et la masse. Les grilles des transistors 81G et 82G sont interconnectées au drain du transistor 82D tandis que les grilles des transistors 81D et 82D sont interconnectées au drain du transistor 82G, de façon à stabiliser l'état lu. Les bornes 4, 6 des résistances RP1 et RP2 opposées aux transistors 82 sont respectivement reliées, par l'intermédiaire de transistors MOS à canal P de sélection MPS1 et MPS2, à des bornes BL et NBL de sortie de la cellule. De

façon optionnelle, ces bornes BL et NBL sont reliées par l'intermédiaire d'amplificateurs suiveurs ou adaptateurs de niveau 86G et 86D générant des signaux logiques DATA et NDATA d'état de lignes de bit de la mémoire. Les transistors de sélection MPS1 et MPS2 sont commandés par un signal ROW de sélection de la cellule mémoire dans une colonne du type de celui représentée en figure 4. En se contentant d'une lecture de la cellule, la structure décrite précédemment permet bien d'obtenir, sur les bornes BL et NBL, l'état programmé de la cellule identifiée par la différence de valeur des résistances RPl et RP2, même infime. Cette différence est amplifiée et 1 'état de la cellule est stabilisé grâce à sa structure croisée. La programmation d'une cellule mémoire telle qu'illustrée par la figure 9 s'effectue grâce à deux transistors de programmation MPP1 et MPP2 (ici des transistors MOS à canal P) dont les drains respectifs sont connectés aux bornes S et NS (comme dans les figures précédentes) et dont les sources respectives sont destinées à recevoir la tension de programmation Vp. Les grilles des transistors MPP1 et MPP2 reçoivent les signaux Pgl et Pg2. On notera toutefois que, s 'agissant de transistors MOS à canal P, les états de ces signaux doivent être inversés par rapport aux structures précédemment décrites utilisant des transistors de programmation à canal N. Avant sélection de la cellule, les transistors MPS1 et MPS2 sont tous deux bloqués par le signal ROW. La structure est donc isolée. Une lecture commence par la mise à 1 'état haut du signal COM qui impose un niveau bas à l'ensemble des noeuds de la structure de la cellule. Lorsque le signal COM est remis à zéro, les grilles des transistors 81D et 85D sont chargées à travers la résistance RPl tandis que les grilles des transistors 81G et 85G sont chargées à travers la résistance RP2, les capacités de grilles étant équivalentes par symétrie. En supposant que la résistance RPl présente la valeur la plus

faible, le drain du transistor 82G a un potentiel supérieur au drain du transistor 82D. Cette réaction s'amplifie pour donner un niveau haut sur la borne 4 et un niveau bas sur la borne 6. Cette opération est faite une seule fois tant que la tension d'alimentation Vr est maintenue. Pour lire cette cellule, on la sélectionne par la mise à l'état haut du signal ROW. Les transistors MPS1 et MPS2 sont alors rendus passants, ce qui permet de transférer l'état des noeuds 4 et 6 sur les lignes de bits BL et NBL générant les niveaux logiques de sortie DATA et NDATA. Pour programmer la cellule de la figure 9, on part d'un état où les transistors de sélection MPS1 et MPS2 sont bloquées . On commute le signal COM à 1 ' état haut pour tirer les drains respectifs des transistors 82G et 82D à la masse. Comme le transistor 84 est bloqué, toute fuite de courant vers 1 ' alimentation Vr est impossible . On impose alors grâce à l'un des transistors MPP1 et MPP2, un niveau de tension suffisant (Vp) sur la borne BL ou NBL selon la résistance RPl ou RP2 que 1 'on souhaite programmer par diminution irréversible de sa valeur. Puis, on provoque la fermeture des transistors MPS1 et MPS2 par la commutation du signal ROW. La tension de programmation est immédiatement transférée sur la résistance à programmer, alors que le noeud NS ou S opposé reste flottant. Les tensions de programmation et de lecture peuvent être différentes comme cela sera exposé ci-après. Dans le montage illustré en figure 9, associé à la cellule MC, les sources respectives des transistors MPP1 et MPP2 sont reliées en sortie d'éléments suiveurs 87G et 87D alimentés par la tension de programmation Vp. Les entrées respectives des éléments suiveurs 87G et 87D reçoivent la tension Vp au moyen d'un amplificateur suiveur 88 dont l'entrée reçoit un signal Prg binaire de déclenchement d'une programmation et dont la sortie est reliée directement en entrée de l'amplificateur 87G et, par l'intermédiaire d'un inverseur 89 alimenté par la tension Vp, en

entrée de l'amplificateur 87D. Le rôle de l'inverseur 89 est de sélectionner celle des branches à soumettre à la tension Vp selon l'état du signal PRG. Dans ce cas, les transistors MPP1 et MPP2 peuvent être commandés par un même signal. En l'absence d'inverseur 89, on utilise des signaux Pgl et Pg2 séparés. Pour éviter une inversion accidentelle de l'état de la cellule quand les transistors de sélection sont fermés en raison de niveau de précharge sur des lignes non contrôlées de la structure, on prévoit deux transistors, respectivement 90G et 90D (ici des transistors MOS à canal N) , reliant les lignes respectivement BL et NBL à la masse. Ces transistors sont commandés simultanément par une combinaison de signaux W et R indicateurs respectivement par un état haut d'une phase d'écriture et d'une phase de lecture. Ces deux signaux sont combinés par une porte de type NON-OU Exclusif 91 dont la sortie traverse un amplificateur décaleur de niveau 92, alimenté par la tension Vp, avant d'attaquer les grilles des transistors 90G et 90D. Cette structure permet de tirer les noeuds BL et NBL à la masse avant chaque opération de lecture. La génération des signaux de commande de la structure de la figure 9 est à la portée de l'homme du métier à partir des indications fonctionnelles données ci-dessus. La figure 10 illustre, par une vue partielle très schématique en perspective, un mode de réalisation d'une résistance en silicium polycristallin du type des résistances de programmation Rpl et Rp2 selon l'invention. Une telle résistance (désignée par 31 en figure 10) est constituée d'une piste (dite aussi barreau) en silicium polycristallin obtenue par gravure d'une couche déposée sur un substrat 32 isolant. Le substrat 32 est indifféremment directement constitué du substrat du circuit intégré ou est constitué d'une couche isolante formant un substrat isolant ou équivalent pour la résistance 31. La résistance 31 est connectée, par ses deux extrémités, à des pistes conductrices (par exemple, métalliques) 33 et 34 destinées à raccorder le barreau résistif

aux autres éléments du circuit intégré. La représentation schématique de la figure 4 ne fait pas référence aux différentes couches isolantes et conductrices constituant généralement le circuit intégré. Pour simplifier, on s'est contenté de repré- senter le barreau résistif 31 posé sur le substrat isolant 32 et en contact, par les extrémités de sa face supérieure, avec les deux pistes métalliques 33 et 34. En pratique, les liaisons de l'élément résistif 31 aux autres composants du circuit intégré sont obtenues par des pistes plus larges en silicium poly- cristallin partant des extrémités du barreau 31 dans l'alignement de celui-ci. En d'autres termes, l'élément résistif 31 est généralement formé en rendant un tronçon d'une piste en silicium polycristallin plus étroit que le reste de la piste. La résistance R de l'élément 31 est donnée par la formule suivante : R = p(L/s), où p désigne la résistivitë du matériau (silicium polycristallin le cas échéant dopé) constituant la piste dans laquelle est gravé l'élément 31, où L désigne la longueur de l'élément 31, et où s désigne sa section, c'est-à-dire sa largeur 1 par son épaisseur e. La rësistivité p de l'élément 31 dépend, entre autres, du dopage éventuel du silicium polycristallin le constituant. Le plus souvent, lors de la réalisation d'un circuit intégré, on prévoit les résistances en faisant référence à une notion dite de résistance par carreau Q (square résistance) . Cette résistance par carreau se définit comme étant la résistivité du matériau divisée par 1 'épaisseur avec laquelle il est déposé. En reprenant la relation ci-dessus donnant la résistance d'un élément 31, la résistance est donc donnée par la relation : R = RQ * L/l. Le quotient L/l correspond à ce que l'on appelle le nombre de carreaux (square number) constituant l'élément résistif 31. Cela représente, vu de dessus, le nombre de

carreaux de dimension donnée fonction de la technologie, mis côte à côte pour former l'élément 31. La valeur de la résistance en silicium polycristallin est donc définie, à la fabrication, d'après les paramètres ci- dessus, conduisant à des résistivités et résistances dites nominales. Généralement, l'épaisseur e du silicium polycristallin est fixée par d'autres paramètres de fabrication du circuit intégré. Par exemple, cette épaisseur est fixée par l'épaisseur souhaitée pour les grilles des transistors MOS du circuit intégré. Une caractéristique de la présente invention est d'imposer temporairement, dans une résistance en silicium polycristallin (Rpl ou Rp2) dont on souhaite diminuer irréversiblement la valeur, un courant de programmation ou de contrainte, supérieur à un courant pour lequel la résistance passe par une valeur maximale, ce courant étant au-delà de la plage de courants de fonctionnement normal (en lecture) de cette résistance. En d'autres termes, on diminue la résistivité du silicium polycristallin dans la plage de courants de fonc- tionnement, de façon stable et irréversible, en imposant temporairement dans l'élément résistif correspondant la circulation d'un courant au-delà de la plage de courants de fonctionnement. Une autre caractéristique de 1 ' invention est que le courant servant à diminuer la valeur de la résistance est, à la différence d'un élément fusible, non destructif pour l'élément en silicium polycristallin. La figure 11 illustre, par un réseau de courbes donnant la résistance d'un élément en silicium polycristallin du type de celui représenté en figure 10 en fonction du courant le traversant, un mode de mise en oeuvre de la présente invention pour programmer une des résistances de la cellule mémoire. On suppose que le silicium polycristallin ayant servi à la fabrication de l'élément résistif 31 (Rpl ou Rp2) présente une résistivité nominale conférant à l'élément 31, pour les dimensions 1, L et e données, une valeur de résistance Rn0m-

Cette valeur nominale (d'origine) de la résistance correspond à la valeur prise de façon stable par l'élément résistif 31 dans la plage de courants de fonctionnement du système, c'est-à-dire généralement pour des courants inférieurs à 100 μA. Selon l'invention, pour diminuer la valeur de la résistance et passer de façon irréversible et stable, par exemple, à une valeur RI inférieure à Rnom'on applique aux bornes de l'élément résistif 31 un courant (par exemple II), dit de contrainte, supérieur à un courant Im pour lequel la valeur de la résistance R de l'élément 31 est maximale sans toutefois être infinie. Comme l'illustre la figure 11, une fois que ce courant II a été appliqué à l'élément résistif 31, on obtient, dans la plage Al de courants de fonctionnement du circuit intégré, une résistance stable de valeur RI. En fait, l'allure Snom de la résistance en fonction du courant est stable pour des courants relativement faibles (inférieurs à 100 μA) . Cette allure se met à croître pour des courants sensiblement supérieurs de l'ordre de quelques milliampères, voire plus (plage A2) . C'est dans cette plage de courants que l'allure Snom passe par un maximum pour la valeur Im. La résistance décroît ensuite progressivement. En figure 11, on a illustré une troisième plage A3 de courants correspondant à la plage généralement utilisée pour réaliser des fusibles. Il s'agit de courants de 1 ' ordre du dixième d' ampère où la résistance se met à croître brusquement jusqu'à devenir infinie. Par conséquent, on peut considérer que 1 'invention utilise la plage intermédiaire A2 de courants entre la plage de fonctionnement Al et la plage destructrice A3, pour diminuer de façon irréversible la valeur de la résistance ou plus précisément de la résistivité de l'élément en silicium polycristallin. En effet, une fois passé le maximum de l'allure Snom de la résistivité en fonction du courant, la valeur prise par la résistance dans la plage de courants de fonctionnement se trouve inférieure à la valeur Rnom. La nouvelle valeur, par exemple RI, dépend de la valeur la plus élevée du courant (ici, II) qui a

été appliqué pendant la phase de diminution irréversible. On notera en effet que la diminution irréversible opérée par l'invention s'effectue dans une phase spécifique de programmation, hors du fonctionnement normal en lecture (plage Al) du circuit intégré, c'est-à-dire hors du fonctionnement normal de la résistance. Le cas échéant, une fois que la valeur de la résistance en silicium polycristallin a été abaissée vers une valeur inférieure (par exemple RI en figure 11) , on peut encore procéder à une diminution irréversible de cette valeur. Il suffit pour cela de dépasser le courant maximum II de la nouvelle allure SI de la résistance en fonction du courant. Par exemple, on peut accroître la valeur du courant jusqu'à atteindre une valeur 12. Quand le courant est alors de nouveau diminué, on obtient une valeur R2 pour la résistance dans sa plage de fonctionnement normal. La valeur R2 est inférieure à la valeur RI et, bien sûr, à la valeur Rn0m-Ω^ns l'application aux cellules mémoires des figures précédentes, cela peut permettre d'inverser la programmation un nombre de fois limité. On voit que toutes les allures de la résistance en fonction du courant se rejoignent sur la pente de décroissance de la valeur de la résistance, après être passé par le maximum de l'allure. Ainsi, pour un élément résistif donné (p, L, s), les courants II, 12, etc. qui doivent être atteints, pour passer à une valeur de résistance inférieure, sont indépendants de la valeur de la résistance (Rnom, RI, R2) à partir de laquelle on provoque la diminution. Ce qui a été exprimé ci-dessus comme valeur de résistance correspond en fait à une diminution de la résistivité du silicium polycristallin constituant l'élément résistif. Les inventeurs considèrent que l'on assiste à une modification stable de la structure cristalline du silicium polycristallin et que l'on assiste, en quelque sorte, à un fluage du matériau, la structure cristalline finale obtenue dépendant du courant maximum atteint. En fait, le courant de contrainte provoque une

élévation de température de 1 ' élément en silicium, ce qui entraîne un fluage de celui-ci. Bien sûr, on veillera à ne pas dépasser la plage de courants de paramétrage A2 (de l'ordre de quelques milliampères) afin de ne pas risquer de détruire la résistance en silicium polycristallin. Cette précaution ne posera en pratique pas de problème dans la mesure où l'utilisation du silicium polycristallin pour constituer un fusible requiert des courants nettement plus élevés (de l'ordre du dixième d'ampère) qui ne sont pas disponibles une fois le circuit fabriqué. La réalisation pratique d'une résistance en silicium polycristallin selon l'invention ne diffère pas de la réalisation d'une résistance classique. Partant d'un substrat isolant, on dépose une couche de silicium polycristallin que l'on grave en fonction des dimensions souhaitées pour la résistance. Comme l'épaisseur de silicium polycristallin déposée est généralement fixée par la technologie, les deux dimensions que 1 ' on peut régler sont la largeur et la longueur. Généralement, on redépose un isolant sur le barreau de silicium polycristallin ainsi obtenu. Dans le cas d'une interconnexion en ligne, on aura modifié la largeur 1 par rapport aux pistes d'accès plus larges pour être fortement conductrices. Dans le cas d'un accès aux extrémités du barreau par le dessus comme cela est illustré en figure 10, on réalisera des vias dans l'isolant sur-jacent (non représenté) du barreau de silicium polycristallin pour connecter des pistes métalliques 33 et 34 de contact . En pratique, pour disposer de la capacité de réglage de résistance la plus importante avec un courant de contrainte minimum, on cherchera à utiliser une épaisseur minimale et une largeur minimale pour les éléments résistifs. Dans ce cas, seule la longueur L conditionne la valeur nominale de la résistance une fois la structure du silicium polycristallin fixée. Le dopage éventuel du silicium polycristallin, quel que soit son type, n'entrave pas la mise en oeuvre de l'invention. La seule

différence liée au dopage est la résistivité nominale avant contrainte et les résistivités obtenues pour des courants de contraintes donnés. En d'autres termes, pour un élément de dimensions données, cela conditionne le point de départ de la valeur de la résistance, et par voie de conséquence, les valeurs de résistance obtenues pour des courants de contrainte donnés. Pour passer de la valeur nominale à une valeur de résistance ou résistivité inférieure, ou pour passer d'une valeur donnée (inférieure à la valeur nominale) à une valeur encore inférieure, on peut selon l'invention utiliser plusieurs méthodes . Selon un premier mode de mise en oeuvre, on fait croître progressivement (pas à pas) le courant dans la résistance. Après chaque application d'un courant supérieur, on revient dans la plage de courants de fonctionnement et on mesure la valeur de la résistance. Tant que le point Im de courant n'est pas atteint, cette valeur de résistance restera à la valeur Rnom. Dès que le point Im en courant est dépassé, on change de courbe (allure S) et la valeur mesurée lorsque l'on repasse sur les courants de fonctionnement devient une valeur inférieure à la valeur Rnom. Si cette nouvelle valeur convient, on en reste là. Dans le cas contraire, on réapplique des courants supérieurs pour dépasser la nouvelle valeur maximale de l'allure courante. Dans ce cas, il n'est pas nécessaire de repartir des courants minimaux comme lorsque l'on démarre de la résistance nominale. En effet, la valeur du courant pour laquelle la résistance va de nouveau diminuer est forcément supérieure à la valeur du courant de contrainte II appliqué pour passer sur 1 'allure courante. La détermination du pas à appliquer est à la portée de l'homme du métier et n'est pas critique en ce qu'elle conditionne essentiellement le nombre de diminutions possibles. Plus le pas est élevé, plus les sauts entre les valeurs seront importants. Selon un deuxième mode de mise en oeuvre, on prédé- termine, par exemple par mesures, les différents courants à

appliquer pour passer des différentes valeurs de résistance à des valeurs inférieures. Cette prédétermination tient compte bien entendu de la nature du silicium polycristallin utilisé ainsi que préférentiellement de la résistance par carreau c'est- à-dire de la résistivité du matériau et de l'épaisseur dans laquelle il est déposé. En effet, comme les allures illustrées par la figure 11 peuvent également être lues comme allure de la résistance par carreau, on est en mesure de transposer les valeurs calculées aux différentes résistances d'un circuit intégré définies par les largeurs et longueurs des tronçons résistifs. Selon ce deuxième mode de mise en oeuvre, on est alors en mesure de prédéterminer la valeur du courant de contrainte à appliquer à l'élément résistif pour diminuer, de façon irréversible et stable, sa valeur. Les deux modes de mise en oeuvre ci-dessus sont combinables . Selon 1 ' invention, la diminution irréversible de la résistance ou résistivité peut être effectuée après fabrication lorsque le circuit est dans son environnement fonctionnel. En d'autres termes, le circuit 7 de commande et les transistors de programmation décrits en relation avec les figures précédentes peuvent être intégrés avec la ou les cellules mémoires. Le changement de courbes, c'est-à-dire la diminution de la valeur de résistance en fonctionnement normal est quasi immédiate dès que le courant de contrainte correspondant est appliqué. Par quasi-immédiat, on entend une durée de quelques dizaines voir centaines de microsecondes qui suffisent pour appliquer la contrainte correspondante au barreau de silicium polycristallin et diminuer la valeur de sa résistance. Cette valeur empirique dépend de la taille (physique) du barreau. On pourra choisir une durée de quelques millisecondes par sécurité. De plus, on peut considérer que, une fois la durée minimale atteinte, toute durée supplémentaire d'application du courant de contrainte ne modifie pas, au moins au premier ordre, la résistance atteinte. En outre, même si dans une application

particulière on considère ne pas pouvoir négliger 1 ' influence de la durée d'application de la contrainte, les deux modes préférés de mise en oeuvre (prédéterminer des valeurs de contraintes en durée et en intensité, ou progression pas à pas jusqu'à la valeur souhaitée) sont parfaitement compatibles avec la prise en compte de la durée d'application de la contrainte. A titre d'exemple particulier de mise en oeuvre, on a réalisé une résistance en silicium polycristallin dopée N+ ayant une section de 0,225 micromètre carré (1 = 0,9 μm, e = 0,25 μm) et une longueur L de 45 micromètres. Avec le silicium polycristallin utilisé et le dopage correspondant, la résistance nominale était d'environ 6300 Ohms. Cela correspond à une résistance par carreau d'environ 126 Ohms (50 carreaux) . En appliquant à cette résistance un courant supérieur à trois milliamperes, on a provoqué une diminution de sa valeur, stable pour un fonctionnement sous des courants allant jusqu'à 500 microampères. Avec un courant de 3,1 milliamperes, la valeur de la résistance a été abaissée à environ 4500 Ohms. En appliquant à la résistance un courant de 4 milliamperes, on a diminué la valeur de la résistance jusqu'environ 3000 Ohms. Les valeurs obtenues de résistances ont été les mêmes pour des durées de contraintes allant de 100 microsecondes à plus de 100 secondes. Selon un exemple de mise en oeuvre particulier de l'invention, le courant de contrainte est compris entre 1 et 10 milliamperes. Toujours selon un exemple de mise en oeuvre particulier, la concentration en dopant du silicium polycristallin est comprise entre 1.10 et 1.10 atomes par centimètre cube. A titre d'exemple particulier, on a réalisé des résistances en silicium polycristallin ayant les caractéristi ues nominales suivantes. Bien entendu, les exemples ci-dessus ainsi que les ordres de grandeurs donnés de courants et de résistances pour les différentes plages concernent les technologies actuelles. Les courants des plages Al, A2 et A3 pourront être différents (inférieurs) pour des technologies plus avancées et peuvent être transposés à des densités de courant. Le principe de l'invention n'en est pas modifié. On a toujours trois plages et on utilise la plage intermédiaire pour forcer la diminution de résistivité. La tension de programmation Vp peut être une tension variable selon que les niveaux de courant de programmation sont prédéterminés ou sont inconnus et doivent être obtenus par une augmentation par paliers. Selon une variante de réalisation, le courant de programmation forcé dans la résistance Rpl ou Rp2 est fixé par la commande (tension de grille) du transistor de programmation correspondant, la tension Vp étant alors fixe. Un avantage de la présente invention est qu'une cellule mémoire à programmation unique est ainsi réalisable dans la même technologie que les transistors MOS classiques et sans étape supplémentaire.

Un autre avantage d'une cellule mémoire selon 1 ' invention par rapport à une cellule EPROM est u'elle est insensible aux ultraviolets. Le stockage d'un code binaire dans un circuit intégré au moyen de cellule mémoire à programmation unique selon l'invention s'effectue, de préférence, avec une programmation disponible sur le circuit intégré fini c'est-à-dire dans son environnement applicatif. Cela est rendu possible grâce aux courants relativement faibles nécessaires pour programmer les résistances des cellules mémoires. Toutefois, cela n'exclut pas une programmation lors de la fabrication. Dans ce cas, l'interrupteur K et le circuit de commande en programmation sont omis. La possibilité de programmer la cellule mémoire dans son environnement applicatif est particulièrement avantageux et constitue donc un mode de réalisation préféré de l'invention. Un autre avantage de l'invention est que la modification irréversible de la valeur de la résistance programmée n'est pas destructrice et ne risque donc pas d'endommager d'autres parties du circuit. Cela permet notamment de prévoir une diminution de la valeur de la résistance après fabrication, et même au cours de sa vie dans son circuit applicatif. Bien entendu, pour le stockage d'un mot de plusieurs bits, on prévoit autant de cellules mémoires que le mot comporte de bits. Le circuit de commande en programmation peut alors être commun. En particulier, un même signal peut sélectionner la tension d'alimentation de toutes les cellules mémoires lors d'une phase de programmation. Des signaux de commande des transistors MOS de programmation ou de sélection doivent toutefois permettre de différencier des états 0 et 1 selon les différentes cellules. La réalisation d'un circuit de commande est à la portée de l'homme du métier à partir des indications fonctionnelles données ci-dessus. Initialement, les résistances Rpl et Rp2 étant identiques, 1 ' état de lecture avant programmation est indéterminé.

Cela n'est toutefois pas gênant pour l'utilisation d'une mémoire à programmation unique. La mise en oeuvre de 1 ' invention permet en fait de programmer plusieurs fois une même cellule mémoire sans toutefois permettre un nombre infini de programmations. En effet, si lors de la première programmation on ne force pas une résistance stable trop faible, on peut encore inverser la programmation en diminuant la valeur de la résistance programmable de l'autre branche à un niveau encore inférieure. La figure 12 représente, de façon très schématique et sous forme de blocs, un exemple de circuit d'exploitation d'un réseau de cellules mémoires 10 à programmation unique selon l'invention. Dans cet exemple, on suppose la présence de n cellules mémoires du type de celle illustrée par les figures 1, 2, 3, 4 ou 9. Une unité centrale de traitement 11 (CPU) reçoit un signal de configuration de la mémoire, soit en programmation (PG) , soit en utilisation (USE) . Pour une programmation, on utilise par exemple un générateur aléatoire 12 (RNG) fournissant n bits au réseau de cellules mémoires 10. En d'autres termes, le générateur aléatoire 12 fournit le code binaire devant être inscrit par programmation des différentes cellules selon l'invention. En utilisation, l'unité centrale 11 déclenche une lecture (READ) du circuit 10. Le circuit 10 fournit alors un mot binaire ID, par exemple, d'identification de la puce de circuit intégré contenant les cellules mémoires. Dans une telle application de stockage d'un identifiant d'une puce de circuit intégré, le recours à des cellules mémoires à programmation unique selon 1 ' invention présente de nombreux avantages . Un premier avantage est l'auto-génération à l'inté- rieur de la puce de circuit intégré de son identifiant, ce qui évite tout risque de fuite par intervention humaine. Un autre avantage est que le caractère aléatoire du mot d'identification stocké dépend complètement du générateur aléatoire 12 et non plus, comme dans certaines applications classiques, d'un réseau de paramètres physiques.

Un autre avantage de 1 ' invention est que le code stocké ne dépend plus, dans son contenu, d'un code logiciel quelconque. On améliore ainsi la sécurité du système contre des piratages éventuels. Un autre avantage de l'invention est que le nombre de cycles d'extraction n'est pas limité. Pour la programmation d'une mémoire selon l'invention, on pourra dissocier plusieurs phases distinctes dans la vie du produit. Par exemple, on prévoit une première zone (première série de résistances) programmables à l'issue de la fabrication pour contenir un code "fabricant". Le reste de la mémoire est laissé disponible pour être programmé (en une ou plusieurs fois) par l'utilisateur (final ou non) . Un autre exemple d'application de la présente invention concerne le blocage d'un circuit intégré suite à la détection d'une tentative de fraude. Des processus de détection de tentatives de fraude sont parfaitement connus. Ils servent à identifier qu'une puce de circuit intégré (par exemple, du type carte à puce prépayée ou non) a subi une attaque pour, soit utiliser les unités prépayées, soit découvrir une clé secrète de la puce. Dans un tel cas, on souhaite invalider le fonctionnement ultérieur de la puce pour éviter que la fraude porte ses fruits . Par la mise en oeuvre de 1 ' invention, il est possible de mémoriser une quantité secrète au moyen d'une mémoire à programmation unique propre à l'invention. Si au cours de la vie du circuit intégré, on détecte une tentative de fraude justifiant l'invalidation de la puce, on provoque automatiquement la programmation d'une ou plusieurs cellules mémoires dans un état inverse. En inversant même un seul bit de la quantité secrète, le système ne pourra plus authentifier la puce correctement, ce qui conduit à un blocage complet et irréversible de la puce. Selon un autre exemple d'application, on utilise une cellule mémoire à programmation unique de 1 ' invention pour verrouiller une puce de circuit intégré dans un mode de

fonctionnement particulier, par exemple, suite à un nombre d'utilisations limité, ou imposer un sens de progression d'un compteur. On notera que l'invention est aisément transposable d'une technologie à une autre. Bien entendu, la présente invention est susceptible de diverses variantes et modifications qui apparaîtront à 1 'homme de l'art. En particulier, la réalisation pratique des résistances de programmation en silicium polycristallin est à la portée de l'homme du métier à partir des indications fonctionnelles données ci-dessus. En outre, l'invention s'applique aussi bien à une lecture en parallèle de plusieurs cellules, qu'à une lecture série. L'adaptation du circuit de commande est à la portée de l'homme du métier.

The invention relates to a memory cell with a binary value consisting of two parallel branches. Each of said branches comprises: at least one polycrystalline silicon programming resistor (Rpl, Rp2), which is connected between a first supply terminal (1) and a point or terminal for the differential reading (4, 6) of the memory cell state; and at least one first switch (MNP1, MNP2) which, during programming, connects one of said read terminals to a second supply terminal (2). REVENDICATIONS 1. Cellule mémoire d'une valeur binaire, caractérisée en ce qu'elle comporte : deux branches parallèles comprenant chacune au moins une résistance de programmation (RPl, RP2 ; RPli, RP2i) en silicium polycristallin connectée entre une première borne (1 ; 2) d'alimentation et un point ou borne de lecture différentielle (4, 6) de l'état de la cellule ; et au moins un premier interrupteur (MNP1, MNP2 ; MPP1, MPP2) reliant, lors d'une programmation, une desdites bornes de lecture à une deuxième borne (2 ; 87) d'alimentation. 2. Cellule mémoire selon la revendication 1, dans laquelle chaque branche comporte un premier interrupteur (MNP1, MNP2 ; MPI, MP2) reliant, lors d'une programmation, la borne de lecture de la branche à ladite deuxième borne (2 ; 87) d'alimentation. 3. Cellule mémoire d'une valeur binaire, caractérisée en ce qu'elle comporte : deux branches parallèles comprenant chacune, en série entre deux bornes (1, 2) d'application d'une tension d'alimentation, une résistance de programmation (RPl, RP2) en silicium polycristallin et une résistance fixe (Rfl, Rf2) , les résistances fixes des deux branches étant, de préférence, identiques ; un amplificateur différentiel (5) dont les entrées respectives sont reliées aux points milieux entre les résistances de chaque branche constituant des point de lecture différentielle de l'état de la cellule, la sortie de 1 ' amplificateur fournissant la valeur binaire stockée dans la cellule ; et au moins un premier interrupteur (MNP1, MNP2 ; MPP1, MPP2) court-circuitant, lors d'une programmation, une desdites résistances fixes. 4. Cellule mémoire d'une valeur binaire, caractérisée en ce qu'elle comporte :