SEMICONDUCTOR STACKING STRUCTURE, AND METHOD AND APPARATUS FOR SEPARATING NITRIDE SEMICONDUCTOR LAYER USING SAME

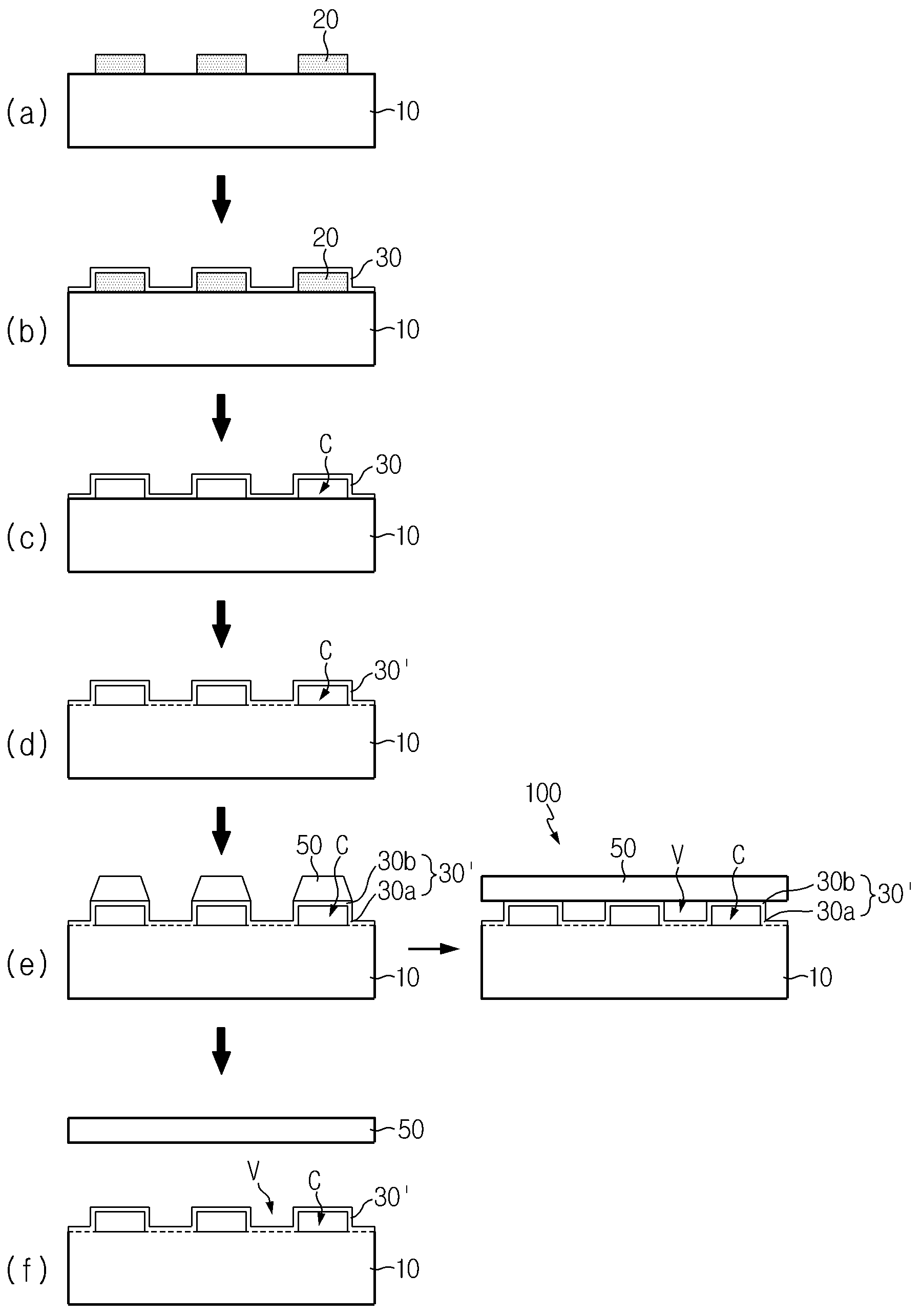

본 발명은 질화갈륨(GaN) 또는 갈륨과 다른 금속의 혼합 질화물로 된 반도체층 및 그 형성방법에 관한 것이다. 본 발명은 또한 이러한 층을 포함하는 전자 또는 광전자 소자(opto-electronic device), 질화물 반도체 기판 및 그 제조방법에 관한 것이다. 본 발명의 기술분야는 기판 위에 결정결함이 적은 고품질의 질화물 반도체층을 형성하기 위한 반도체 적층 구조 및 그 형성방법으로 넓게 정의될 수 있다. 주기율표 상의 Ⅲ족 내지 Ⅴ족 원소들의 질화물 반도체는 전자 및 광전자 소자 분야에서 중요한 위치를 점유하고 있으며, 이러한 분야는 앞으로 더욱 중요해질 것이다. 질화물 반도체의 응용분야는 실제적으로 레이저 다이오드(LD)에서부터 고주파수 및 고온에서 작동할 수 있는 트랜지스터에 이르기까지의 넓은 영역을 커버한다. 그리고, 자외선 광검출기, 탄성 표면파 소자 및 발광 다이오드(LED)를 포함한다. 예를 들어, 질화갈륨은 청색 LED 또는 고온 트랜지스터의 응용에 적합한 물질로 알려져 있지만, 이에 한정되지 않는 마이크로파 전자 소자용으로 폭넓게 연구되고 있다. 또한, 여기에서 쓰인 바와 같이, 질화갈륨은 질화알루미늄갈륨(AlGaN), 질화인듐갈륨(InGaN) 및 질화알루미늄인듐갈륨(AlInGaN)과 같은 질화갈륨계 합금을 포함하는 것으로 넓게 쓰일 수도 있다. 질화갈륨과 같은 질화물 반도체를 이용하는 소자들에서, 질화물 반도체층의 성장을 위해 가장 빈번히 사용되는 기판은 사파이어, 실리콘 카바이드(SiC), 실리콘과 같은 “이종” 기판이다. 그런데, 이들 이종 기판 물질은 질화물과의 격자상수 불일치와 열팽창계수의 차이가 있기 때문에, 이종 기판에 성장시킨 질화물 반도체층은 전위(dislocation) 등의 결정결함을 다량으로 포함하고 있다. 이러한 결함은 LED 등 질화물 반도체 소자의 성능을 떨어뜨리는 주요인으로 작용한다. 사파이어 기판은 질화갈륨보다 열팽창계수가 크기 때문에 질화갈륨을 고온에서 성장시킨 후 냉각시키면 질화갈륨 에피층에 압축 응력이 걸린다. 실리콘 기판은 질화갈륨보다 열팽창계수가 작기 때문에 질화갈륨을 고온에서 성장시킨 후 냉각시키면 질화갈륨 에피층에 인장 응력이 걸린다. 이 때문에 기판의 휘어짐 현상이 나타나고, 기판 휘어짐을 억제하기 위해서 기판의 두께도 커져야 하는 문제점이 있다. 두꺼운 기판을 사용하는 것은 표면적인 현상을 감소하는 역할을 할 뿐, 박막의 응력 자체를 감소하는 기술이 아니다. 박막의 응력 자체를 감소시킬 수 있다면 얇은 기판을 사용할 수 있게 되어 유리하다. 또한, LED 제작 후 칩 분리를 위해서 기판을 100 ㎛ 정도 남기고 갈아내야 하는 실상을 볼 때 얇은 기판의 사용이 가능해진다면 LED 생산적 측면에서 큰 이득을 얻을 수 있다. 필요에 따라서는 이종 기판 상에 형성된 질화물 반도체층을 이종 기판으로부터 분리시켜야 할 경우가 있는데, 종래 기술로는 레이저 리프트 오프(laser lift off)가 제안되어 있다. 그러나, 레이저 리프트 오프법을 사용하는 경우에도, 사파이어 기판과 질화물 반도체간에 열팽창계수 차이 등의 원인으로 기판의 휘어짐이 발생하거나, 레이저를 이용해 질화물 반도체층을 녹여서 떼어내는 방식이므로 국부 영역에서 높은 열로 인해 공정 중에 열응력을 유발하는 부작용이 있다. 레이저 리프트 오프법은 질화물 반도체의 열적 및 기계적 변형과 분해를 수반한다. 레이저 빔에 의한 충격에 의해 질화물 반도체층에 크랙 등의 결함이 발생하기 쉽고, 질화물 반도체층이 손상될 수 있으며, 나아가 질화물 반도체층이 깨지기 쉬워 공정이 불안정하다. 따라서, 고신뢰성의 기판 분리방법이나 고품질의 질화물 반도체 기판 또는 질화물 반도체 소자를 얻을 수 있는 방법이 요구된다. 본 발명이 해결하려는 과제는 질화물 반도체층 성장시 질화물 반도체층이 받는 응력을 감소시키고 고품질의 질화물 반도체층을 형성할 수 있을 뿐만 아니라 레이저 리프트 오프를 할 필요없이 기판과의 분리가 쉬운 반도체 적층 구조, 이를 이용한 질화물 반도체층 분리방법 및 장치를 제공하는 것이다. 상기의 과제를 해결하기 위하여, 본 발명에 따른 반도체 적층 구조는 질화물 반도체와 이종인 단결정 기판; 상기 기판과의 사이에 빈 공간(cavity)이 정의되도록 상기 기판과 접촉하는 다리부 및 상기 다리부로부터 연장되어 상기 기판과 평행한 상면부를 포함하고 상기 기판과 같은 결정 구조로 적어도 일부 결정화된 무기물 박막; 및 상기 빈 공간 위의 상기 결정화된 무기물 박막 상에서부터 성장된 질화물 반도체층을 포함한다. 특히 상기 빈 공간은 서로 분리된 복수개의 빈 공간이고 상기 질화물 반도체층의 측면 성장 속도가 빠른 방향과 수직인 방향으로 연장된 라인 타입 패턴일 수 있다. 상기 질화물 반도체층은 합체되거나 합체되지 않을 수 있다. 상기 질화물 반도체층은 수평 방향으로 연속적이거나 불연속적일 수 있다. 상기 질화물 반도체층은 2층 이상의 막이 될 수 있다. 이러한 2층 이상의 막 사이에 상기와 같은 빈 공간을 정의하는 무기물 박막이 더 형성될 수도 있다. 본 발명에 따른 질화물 반도체층 분리방법에서는 질화물 반도체와 이종인 단결정 기판 상에 희생층 패턴을 형성한 다음, 상기 희생층 패턴 상에 무기물 박막을 형성한다. 상기 기판과 무기물 박막으로 정의되는 빈 공간이 형성되도록, 상기 무기물 박막이 형성된 상기 기판으로부터 상기 희생층 패턴을 제거한다. 이후, 상기 기판과 같은 결정 구조로 상기 무기물 박막을 적어도 일부 결정화시키고, 상기 빈 공간 위의 상기 결정화된 무기물 박막 상에서부터 질화물 반도체층을 성장시킨다. 그리고 나서, 상기 기판과 상기 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 수행한다. 상기 질화물 반도체층을 성장시키는 단계에서는 상기 질화물 반도체층을 서로 분리된 복수개의 질화물 반도체층으로 형성할 수 있다. 상기 희생층 패턴은 다양한 방법으로 형성할 수 있다. 상기 기판 상에 감광막을 도포한 후 사진식각 방법으로 형성하거나, 상기 기판 상에 나노임프린트용 수지를 도포한 후 나노임프린트 방법으로 형성할 수 있다. 대신에 상기 기판 상에 유기물 나노입자를 붙여서 형성할 수도 있다. 상기 무기물 박막을 형성하는 단계는 상기 희생층 패턴이 변형되지 않는 온도 한도 내에서 수행하는 것이 바람직하다. 상기 빈 공간은 상기 희생층 패턴이 제거되어 없어진 자리이다. 따라서, 상기 빈 공간은 상기 희생층 패턴의 모양과 크기 및 2 차원적인 배열을 그대로 따른다. 그러므로 상기 빈 공간이 제어된 모양과 크기 및 2 차원적인 배열을 갖게 하려면 상기 희생층 패턴의 모양과 크기 및 2 차원적인 배열을 정해야 한다. 본 발명에 따른 다른 질화물 반도체층 분리방법에서는 본 발명에 따른 반도체 적층 구조를 이용해 그 안의 기판과 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 수행하는 것이다. 본 발명에 따른 또 다른 질화물 반도체층 분리방법에서는 본 발명에 따르지 않더라도 기판과 질화물 반도체층 사이에 빈 공간을 포함하는 계면층이 포함된 다른 반도체 적층 구조를 이용해 그 안의 기판과 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 수행하는 것이다. 이러한 방법을 이용해 기판으로부터 질화물 반도체층을 분리하면 수직형 또는 수평형 LED, 임의의 기판에 전사 혹은 이전된 LED 또는 자유 기립(free-standing)의 질화물 반도체 기판을 제조할 수 있다. 본 발명에 따른 질화물 반도체층 분리방법에서, 상기 기계적으로 분리시키는 단계는, 상기 기판과 질화물 반도체층에 수직 방향 힘을 주어 분리하는 방법, 수평 방향의 힘을 주어 분리하는 방법, 상대적인 원운동의 힘을 주어 분리하는 방법, 및 그 조합의 방법으로 수행할 수 있다. 특히 상기 기판과 질화물 반도체층에 수직 방향 힘을 주어 분리하는 방법에 의할 경우, 상기 기판과 질화물 반도체층이 수직 방향으로 압축되는 두께 또는 압력을 감지하여 종말점 검출(end point detect)하는 것이 바람직하다. 본 발명에 따른 질화물 반도체층 분리방법은 상기 기판과 질화물 반도체층 분리 후, 상기 분리된 질화물 반도체층을 다른 기판으로 전사하거나 패키징하는 단계를 더 포함할 수도 있다. 본 발명에 따른 질화물 반도체층 분리장치는 본 발명에 따른 반도체 적층 구조 또는 본 발명에 따르지 않더라도 기판과 질화물 반도체층 사이에 빈 공간을 포함하는 계면층이 포함된 다른 반도체 적층 구조에서 상기 기판과 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 수행하는 것이다. 이러한 장치는 상기 반도체 적층 구조의 기판과 질화물 반도체층에 각각 적용되는 치구로서 한 쌍의 판상 분리부재를 포함할 수 있다. 상기 분리부재와 상기 반도체 적층 구조 사이는 일시적인 접착이 되는 것일 수 있다. 상기 일시적인 접착은 접착층, 접착 코팅, 접착테이프, 정전기적인 힘 또는 진공에 의한 힘 중 어느 하나일 수 있다. 상기 장치는 상기 반도체 적층 구조에 외력을 인가하는 구동부, 및 상기 구동부를 제어하는 제어부를 포함할 수 있다. 상기 구동부는 상기 기판과 질화물 반도체층에 상대적인 압축, 인장, 전단, 비틀음 및 그 조합의 외력을 인가할 수 있다. 본 발명에 따른 분리장치는 상기 반도체 적층 구조의 기판과 질화물 반도체층에 각각 적용되는 치구로서 한 쌍의 판상 분리부재를 적어도 어느 한쪽에는 상기 반도체 적층 구조와 일시적 접착을 한 상태에서 상기 외력을 인가하는 것일 수 있다. 상기 분리부재 중 어느 한쪽은 고정하고 다른 한쪽을 나머지에 대해 수직 방향, 수평 방향 또는 회전 외력을 인가하는 것일 수 있다. 특히, 상기 분리부재 중 어느 한쪽은 고정하고 다른 한쪽을 나머지에 대해 수직 방향으로 구동시켜 압축력을 제공하고, 무기물 박막 또는 계면층 파괴로 상기 질화물 반도체층과 기판이 분리된 직후에 압축력을 해제하는 것이 바람직하다. 이 때, 상기 제어부는 상기 질화물 반도체층과 기판이 분리되는 종말점 검출을 통해 상기 구동부를 제어하여 상기 분리부재의 상대적 이동을 멈추거나 서로에 대해 이격시킬 수 있다. 상기 종말점 검출을 위한 분리감지부를 더 포함할 수 있다. 상기 분리감지부는 분리부재 사이의 거리 측정 또는 압력 모니터링 방법에 의한 것일 수 있다. 본 발명에 따른 분리장치는 상기 분리된 질화물 반도체층을 다른 기판으로 전사하거나 패키징하기 위해 운반하는 장치를 더 포함할 수도 있다. 본 발명에 따른 반도체 적층 구조, 이를 이용한 질화물 반도체층 분리방법 및 장치를 이용하면 자외선 광검출기, 탄성 표면파 소자, LED, LD, 마이크로파 전자 소자 등을 제조할 수 있으며 그 소자를 이용한 모듈, 시스템 등으로 확장할 수 있다. 뿐만 아니라 자유 기립의 질화물 반도체 기판을 제조할 수도 있다. 기타 실시예의 구체적 사항들은 상세한 설명 및 도면들에 포함되어 있다. 본 발명에 따르면, 질화물 반도체층은 빈 공간 위의 무기물 박막 상에서부터 성장한다. 무기물 박막은 그 위에서 성장하는 질화물 반도체층과 응력을 나누어서 해소할 수 있어, 본 발명에 따르면 질화물 반도체층이 결함 밀도가 작은 고품질로 성장이 된다. 따라서, 결함 밀도가 작은 고품질의 질화물 반도체층을 형성할 수 있고 질화물 반도체 결정결함 밀도 감소로 내부양자효율을 증대시킬 수 있다. 기판과 질화물 반도체층 사이의 열팽창계수 차이로 인해 질화물 반도체층에 응력이 발생되더라도 국부적인 응력 이완이 되고 이로 인한 기판 휘어짐 현상이 감소될 수 있다. 기판과 질화물 반도체층의 열팽창계수가 달라도 빈 공간이 질화물 반도체층에 의해 압축이 되거나 신장이 될 수 있으므로, 질화물 반도체층에 걸리는 응력은 감소된다. 이에 따라, 대면적 기판에서도 상대적으로 얇은 기판을 사용하는 것이 가능해진다. 특히, 희생층 패턴 형성시 사진식각 또는 나노임프린트와 같은 제어된 방법으로 형성하기 때문에 빈 공간이 불규칙적이거나 무작위로 형성되는 것이 아니라 제어된 방법으로 형성되므로 재현성이 좋고 소자 균일도가 우수하다. 이와 같은 결과로, 우수한 물성을 갖는 질화물 반도체 에피층을 성장시킬 수 있으므로, 고효율, 고신뢰성을 가지는 광전자 소자를 구현할 수 있다. 빈 공간, 그리고 질화물 반도체층을 형성하면서 만들 수 있는 보이드(void)로 인해 기판과 질화물 반도체층 사이는 물리적으로 분리하기 쉬운 상태가 된다. 레이저와 같은 큰 에너지를 가하지 않고도 작은 물리적 힘이나 충격에 의해 질화물 반도체층과 기판 사이를 기계적으로 분리시킬 수 있다. 따라서, 레이저 리프트 오프를 사용하지 않더라도 기판으로부터 질화물 반도체층을 분리하는 것이 용이해져, 수직형 LED 또는 자유 기립의 질화물 반도체 기판 제조가 용이해진다. 특히 본 발명에 따른 분리방법 및 장치에 의하면 레이저를 이용하지 않고 기판과 질화물 반도체층 사이를 기계적인 힘으로 분리를 하므로, 레이저를 이용하는 방법에 비하여 시간을 단축시키고 공정 비용을 감소시킬 수 있으며, 생산 효율을 높일 수 있다. 본 발명은 기계적인 분리 방법으로 기판과 질화물 반도체층 사이를 분리하는 방법 및 장치에 관한 새로운 구성을 제안한다. 쉽게 파괴가 가능한 인위적인 나노구조인, 빈 공간을 정의하는 무기물 박막을 기판과 질화물 반도체층 사이에 형성함으로써, 고가의 레이저 장치가 필요없고 또한 레이저에 의한 열화 현상없이 기판과 질화물 반도체층 사이를 분리할 수 있다. 빈 공간을 정의하는 무기물 박막 구조, 2차원 배열 및 질화물 반도체층 성장 조건 등을 조절하면 연속적 또는 불연속적으로 질화물 반도체층을 성장시킬 수 있어, LED의 성능을 향상시킬 뿐 아니라 생산단가를 낮출 수 있다. 도 1은 본 발명에 따른 반도체 적층 구조 및 그 형성방법을 설명하기 위해 도시한 도면이다. 도 2는 본 발명에 따른 반도체 적층 구조 및 그 형성방법에서 희생층 패턴의 2 차원적인 배열을 보이기 위한 도면이다. 도 3은 본 발명에 따른 반도체 적층 구조에서 빈 공간의 다양한 단면을 도시한다. 도 4는 본 발명에 따른 반도체 적층 구조 형성방법에서 다양한 희생층 패턴, 그로 인한 무기물 박막의 상면부 모양을 설명하기 위한 도면이다. 도 5는 본 발명에 따른 반도체 적층 구조에서 계면층 부분에 질화물 반도체층 일부가 포함된 경우를 도시한다. 도 6은 본 발명에 따른 반도체 적층 구조에서 질화물 반도체층의 상면 모양을 설명하기 위한 도면이다. 도 7은 본 발명에 따른 질화물 반도체층 분리장치에 포함되는 한 쌍의 판상 분리부재를 도시한다. 도 8은 본 발명에 따른 질화물 반도체층 분리장치에 포함되는 분리부재의 다른 예를 도시한다. 도 9는 본 발명에 따른 질화물 반도체층 분리장치의 개략도이다. 도 10은 본 발명에 따른 질화물 반도체층 분리장치를 이용한 압축 상태로 질화물 반도체층과 기판을 분리하는 경우를 도시한다. 도 11은 본 발명에 따른 질화물 반도체층 분리장치를 이용한 인장 상태 질화물 반도체층과 기판을 분리하는 경우를 도시한다. 도 12는 본 발명에 따른 질화물 반도체층 분리장치를 이용한 전단 상태로 질화물 반도체층과 기판을 분리하는 경우를 도시한다. 도 13은 본 발명에 따른 질화물 반도체층 분리장치를 이용한 비틀음 상태로 질화물 반도체층과 기판을 분리하는 경우를 도시한다. 도 14 및 도 15는 본 발명에 따른 실험예를 설명하기 위한 SEM 사진들이다. 이하 첨부된 도면들을 참조하여 본 발명을 더욱 상세히 설명하고자 한다. 다음에 설명되는 실시예들은 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 아래에서 상술되는 실시예들에 한정되는 것은 아니다. 본 발명의 실시예들은 당 업계에서 평균적인 지식을 가진 자에게 본 발명을 보다 완전하게 설명하기 위해서 제공되는 것이다. 따라서, 도면에서의 요소의 형상 등은 보다 명확한 설명을 강조하기 위해서 과장되어진 것이며, 도면 상에서 동일한 부호로 표시된 요소는 동일한 요소를 의미한다. 본 발명자들은 이종 기판 위에 빈 공간을 형성한 후 질화물 반도체층을 성장시킴으로써, 빈 공간을 찌그러뜨려 질화물 반도체층의 응력을 해소하는 다양한 연구 결과들을 제시해 왔다. 본 출원에서는 본 발명자들이 제안한 방법에 따라 형성한 반도체 적층 구조에서 질화물 반도체층과 기판을 분리하여 수직 LED 또는 수평형 LED, 임의의 기판에 전사 혹은 이전된 LED 또는 자유 기립의 질화물 반도체 또는 질화물 반도체 기판을 제조하는 방법 및 그러한 방법을 수행하기 위하여 질화물 반도체층을 기판과 분리하는 방법 및 장치에 대하여 더 연구한 결과에 따른 것이다. 도 1은 본 발명에 따른 반도체 적층 구조 및 그 형성방법을 설명하기 위해 도시한 도면이다. 도 1의 (a)를 참조하면, 먼저 기판(10) 상에 희생층 패턴(20)을 형성한다. 희생층 패턴(20)의 두께(d)는 0.01 ~ 10 ㎛이고 희생층 패턴(20)의 폭(w)은 0.01 ~ 10 ㎛으로 할 수 있다. 희생층 패턴(20)의 두께(d)와 폭(w)은 최종적으로 형성하려는 빈 공간을 고려하여 결정하도록 한다. 도 1의 (a)를 참조하면 희생층 패턴(20)은 기판(10) 전체에 같은 패턴으로 균일하게 형성되어 있다. 그러나 희생층 패턴(20)은 기판(10)에 국부적으로 다른 패턴으로 형성될 수도 있다. 도 2는 희생층 패턴(20)의 2 차원적인 배열을 보여주는 평면도로서 하나의 칩을 구성하는 기판의 일부를 보여준다. 기판(10)에 형성하는 희생층 패턴(20)은 라인 앤드 스페이스 타입(line and space type)으로서 기판(10) 상에서 y축 방향 혹은 x축 방향으로 신장하는 모양을 가질 수 있으며 도 2에서는 희생층 패턴(20)이 y축 방향으로 신장하는 경우를 예로 들었다. 500 nm의 라인 앤드 스페이스를 가정할 경우 가로 x 세로가 1mm x 1mm 크기의 칩에는 대략 1000개의 희생층 패턴(20)이 들어가게 된다. 희생층 패턴(20)을 이렇게 일 방향으로 신장하는 모양으로 형성할 경우 이로부터 형성하는 LED는 어느 한 방향으로의 광 특성이 제어가 되어 예컨대 편광 방향성을 조절하는 것이 가능해진다. 특히 희생층 패턴(20)은 후속적으로 형성하는 질화물 반도체층의 측면 성장 속도가 빠른 방향과 수직인 방향으로 연장된 라인 타입 패턴으로 형성하는 것이 바람직하다. 예를 들어 도 2에서는 x축 방향 질화물 측면 성장 속도가 빠른 경우가 된다. 기판(10)이 사파이어인 경우에 질화물의 측면 성장 속도가 빠른 방향은 <1-100>이므로 희생층 패턴(20)은 그에 수직인 <11-20> 방향을 따라 연장하는 라인 패턴으로 형성한다. 이렇게 하는 이유는 기판(10) 상에서부터 시작되는 ELO(Epitaxial Lateral Overgrowth)를 최대한 조장하면서 질화물 반도체층을 성장시키기 위함이다. 라인 타입의 희생층 패턴(20)은 기판(10) 전체에 걸쳐 형성될 수도 있지만 패턴과 패턴 사이가 이격되어 있는 섬(island) 형태도 가능하다. 섬 형태의 경우 기판(10) 전체에 걸쳐 형성되는 경우보다 보잉(bowing) 등을 방지하는 면에서 바람직할 수 있다. 희생층 패턴(20) 사이의 간격이 더욱 좁아지는 경우에는 측면 성장을 할 길이가 줄어들므로 측면 성장이 빠른 방향에 수직으로 라인 타입 패턴을 정렬할 필요는 없어진다. 이와 같은 희생층 패턴(20)은 사진식각 방법(photo lithography), 나노임프린트(nano-imprint) 방법, 유기물 나노입자 부착과 같은 다양한 방법을 통해 수행할 수 있다. 이와 같이 본 발명에 따르면 희생층 패턴(20)을 형성하는 방법이 비교적 간단하며, 기존에 PSS(patterned sapphire substrate)와 같은 기술에서 기판을 에칭하는 경우에 비하면 기판이 훼손되는 정도가 상대적으로 작고 공정을 단순화할 수 있다. 이렇게 다양한 희생층 패턴(20)이 형성되는 기판(10)은 사파이어, 실리콘, SiC, GaAs 기판 등 질화물 반도체층의 이종 에피층 성장에 이용되는 모든 이종 단결정 기판이 이용될 수 있으며, 본 실시예에서는 사파이어 기판인 것이 바람직하다. 도 1의 (a)에서와 같이 희생층 패턴(20)을 형성한 다음에는, 도 1의 (b)를 참조하여 희생층 패턴(20) 상에 무기물 박막(30)을 형성한다. 무기물 박막(30)은 후속적으로 기판(10)과의 빈 공간을 정의하는 것으로, 무기물 박막(30)을 형성할 때에는 희생층 패턴(20)이 변형되지 않는 온도 한도 내에서 수행하는 것이 바람직하다. 무기물 박막(30)은 희생층 패턴(20)이 제거된 후 구조물이 본래의 형상이 안정적으로 유지될 수 있는 두께로 한다. 무기물 박막(30)을 형성하기 위한 공정은 원자층 증착(Atomic Layer Deposition : ALD), 습식 합성(wet synthesis), 금속 박막 형성 후 산화공정(metal deposition and oxidation), 스퍼터링 등 다양한 방법이 가능하다. 구조적으로 안정된 빈 공간이 기판(10) 위에 존재하기 위해서는 무기물 박막(30) 형성시에 무기물 박막(30)의 일부가 기판(10)과 직접 접촉하는 것이 유리하다. 무기물 박막(30)은 실리카(SiO2), 알루미나(Al2O3), 티타니아(TiO2), 지르코니아(ZrO2), 이트리아(Y2O3)-지르코니아, 산화구리(CuO, Cu2O) 및 산화탄탈륨(Ta2O5), 질화알루미늄(AlN), 질화실리콘(Si3N4) 등 산화물이나 질화물 중 적어도 어느 하나일 수 있으며, 본 실시예에서는 알루미나인 것이 바람직하다. 이러한 무기물 박막(30)의 조성, 강도 및 두께 중 적어도 어느 하나를 조절하면 후속적으로 이를 이용한 구조 상에 형성되는 질화물 반도체층에 걸리는 응력을 조절할 수 있다. 무기물 박막(30)은 도시한 바와 같이 희생층 패턴(20)을 덮으면서 기판(10) 위로 전면적으로 형성된다. 바람직한 실시예에서, 알루미나는 ALD와 같은 증착 방법으로 기판(10)과 희생층 패턴(20)의 모양을 따라 균일한 두께로 형성할 수 있다. 증착 방법 대신에 습식 용액을 이용한 습식 합성 방법도 가능하다. 습식 용액을 기판(10)과 희생층 패턴(20)의 모양을 따라 균일하게 코팅한 후 가열, 건조 혹은 화학 반응을 통해 알루미나를 합성할 수 있다. 예를 들어 알루미늄 클로라이드(AlCl3)와 같은 알루미늄 전구체 분말을 테트라클로로에틸렌(C2Cl4)과 같은 용매에 혼합한 후 희생층 패턴(20)이 형성된 기판(10)에 적용하여 코팅하고 산소 분위기에서 가열하여 반응시키면 알루미나 박막을 입힐 수 있다. 혹은 금속 Al 박막을 스퍼터링 등의 방법으로 증착한 후에 산화 공정을 수행하여 알루미나를 형성하기도 한다. 이러한 알루미나는 비정질 또는 미세한 입자의 다결정으로 이루어진 상태로 형성된다. 무기물 박막(30) 형성 후에는 도 1의 (c)에서와 같이 기판(10)으로부터 희생층 패턴(20)을 선택적으로 제거하도록 한다. 희생층 패턴(20)은 감광막, 나노임프린트용 수지 혹은 유기물 나노입자와 같은 폴리머이므로 이를 쉽게 제거하는 방법은 가열이다. 자연발화점이 보통 600℃ 부근인 감광막은 열에 의해서 쉽게 제거될 수 있다. 그리고 산화 방식으로 더욱 쉽게 태워 제거하기 위해서는 산소를 포함하는 가스와의 화학 반응을 추가할 수 있다. 산소 분위기에서 고온으로 가열하면 흔히 애싱(ashing)이라고 부르는 열분해 공정에 의해 폴리머 성분을 쉽게 제거할 수 있는 것이다. 예컨대 산소 분위기에서의 열처리로 제거한다. 산소 분위기의 열처리가 적절하지 않은 경우, 예를 들어 기판(100)이 실리콘 기판이어서 산화물 생성이 우려되는 경우라면 유기 용매를 이용한 습식 제거를 이용할 수도 있다. 희생층 패턴(20)을 제거하고 나면, 도 1의 (c)에 도시한 바와 같이 기판(10)과 무기물 박막(30)으로 정의되는 빈 공간(C)을 형성할 수 있다. 본 실시예에서는 서로 분리된 복수개의 빈 공간(C)이 형성되지만, 처음에 형성하는 희생층 패턴(20) 모양에 따라 빈 공간의 모양이 달라질 수 있다. 빈 공간은 희생층 패턴이 반전된 형상을 갖는다. 바로 형성된 상태(as-deposited)의 무기물 박막(30)은 보통 비정질이거나 매우 작은 입자로 이루어진 다결정을 갖는 것이 보통이다. 희생층 패턴(20)을 제거함으로써 빈 공간(C)을 형성한 후에는 비정질 혹은 다결정 무기물 박막(30)을 치밀화하고 결정화할 수 있도록, 열처리를 진행하는 것이 바람직하다. 희생층 패턴(20) 제거 열처리와 무기물 박막(30) 열처리는 단계적으로 온도를 올려 진행하거나 연속적인 공정으로 진행할 수 있다. 기판(10)이 사파이어 기판이고 무기물 박막(30)이 알루미나인 경우처럼 무기물 박막(30)이 기판(10)과 조성이 같은 물질인 경우에, 예를 들어 1000℃ 부근으로 가열을 하면 열처리에 의해 무기물 박막(30)은 도 1의 (d)에서와 같이 기판(10)과 같은 결정 구조로 결정화된 무기물 박막(30')이 된다. 이에 따라 결정화된 무기물 박막(30')과 기판(10) 사이의 계면(도면에서는 점선으로 표시)은 사라지게 된다. 그 이유는 고온 열처리 동안 기판(10)과 직접 접촉하고 무기물 박막(30) 부분에서 고체상 에피성장(solid phase epitaxy)이 일어나서 기판(10)의 결정 방향을 따라 결정화가 일어나기 때문이다. 고체상 에피택시는 기판(10)과 무기물 박막(30) 사이의 계면에서부터 시작되어 무기물 박막(30)이 비정질로 이루어진 경우에는 최종적으로 결정화된 무기물 박막(30')은 다결정이 되거나, 미세한 다결정은 그 크기가 더 커지거나 가장 바람직한 경우에는 기판(10)과 같은 단결정으로 바뀌게 된다. 이러한 결정화는 무기물 박막(30)의 적어도 일부, 특히 전체에 걸쳐 일어나도록 함이 바람직하며, 빈 공간(C) 위의 결정화된 무기물 박막(30') 부분은 추후 질화물 반도체 에피층 성장시 씨앗 부분으로 작용을 하게 되므로 빈 공간(C) 위의 무기물 박막(30') 부분은 반드시 결정화가 되어 있어야 한다. 다음으로 도 1의 (e)에서와 같이 결정화된 무기물 박막(30') 위로 질화물 반도체층(50)을 더 형성한다. 질화물 반도체층(50)은 적절한 버퍼층을 포함하여 다층 구조로 형성될 수 있다. 질화물 반도체층(50)은 GaN, InN, AlN 또는 이들의 조합인 GaxAlyInzN(0<x,y,z<1) 등의 모든 질화물 반도체 물질을 포함한다. 질화물 반도체층(50) 물질 종류에 따라 밴드갭 조절이 되어 자외선, 가시광선, 적외선 영역의 빛을 방출하도록 할 수 있다. 이 때, 질화물 반도체층(50)은 기판(10) 상에서부터 성장하는 것이 아니라 빈 공간(C) 위의 결정화된 무기물 박막(30') 부분에서부터 씨앗이 성장한다(도 1의 (e) 좌측 그림). 증착 온도, 기체의 압력, 유량 등을 조절함으로써 질화물 반도체층(50)이 빈 공간(C) 위의 결정화된 무기물 박막(30')에서 성장하도록 할 수 있다. 성장 조건에 따라 그곳에서부터 성장된 부분들이 합체되면서 박막을 이루게 되고 빈 공간(C) 사이의 영역에 보이드(V)를 형성할 수 있다(도 1의 (e) 우측 그림). 실시예에 따라서는, 질화물 반도체층(50)이 합체되기 전에 성장을 종료할 수 있다. 즉, 에피층 성장 시간 조절에 따라 질화물 반도체층(50)은 서로 분리된 복수개의 질화물 반도체층으로 형성된다. 실시예에 따라서는, 보이드(V)가 형성되지 않을 수도 있다. 합체가 되는 경우라도 빈 공간(C) 사이의 거리를 조절함으로써 일부는 합체되고 일부는 합체되지 않도록 한다면 질화물 반도체층은 수평 방향으로 연속적이거나 불연속적으로 형성될 수가 있다. 무기물 박막(30')과 빈 공간(C)과 선택적인(optional) 보이드(V)를 포함하는 부분을 본 명세서에서는 "계면층"이라고 부르기로 한다. 이러한 계면층의 구성 조절에 따라서도 질화물 반도체층(50)은 서로 분리된 복수개의 질화물 반도체층으로 형성될 수 있다. 만약 질화물 반도체층(50)이 빈 공간(C) 사이의 기판(10) 상에서부터 성장한다면 이 때에는 ELO 방법으로 기판(10) 상에서부터 막이 자라나와 빈 공간(C) 위에서 횡방향으로 과도 성장하여 합체하게 될 것이다. 그러나 본 발명에서는 질화물 반도체층(50)이 기판(10)에서부터가 아니라 빈 공간(C) 위의 결정화된 무기물 박막(30') 부분에서부터 성장하는 것이므로 ELO 방법과는 전혀 다른 방식으로 질화물 반도체층(50)이 형성된다. 본 발명에 따라 결정화된 무기물 박막(30')은 그 위에서 성장하는 질화물 반도체층(50)과 응력을 나누어서 해소할 수 있기에 compliant layer의 역할을 할 수 있게 되고, 전위를 발생시킬 수 있는 응력이 해소되면서 성장하기 때문에 결함 밀도가 작은 고품질로 성장이 된다. 기판과 박막의 물리적 차이에 의한 응력은 계면에서 탄성에너지로 변환되어 전위를 생성하는 구동력(driving force)이 된다. 보통의 경우는 기판의 두께가 박막에 비해 상당히 두껍기 때문에 변형이 어렵고, 대신 박막에 전위가 생성되면서 응력이 해소된다. 이 때, 임계 두께(critical thickness)라는 일정 두께 이상의 박막이 성장될 때 계면에서의 탄성에너지가 전위의 생성에너지보다 커져서 전위가 발생하기 시작한다. 하지만 본 발명의 경우에는 무기물 박막(30')이 질화물 반도체층(50)보다 얇은 경우에는 임계 두께가 더욱 크기 때문에 질화물 반도체층(50)의 전위 발생이 저하된다. 이와 같이 무기물 박막(30')이 질화물 반도체층(50)보다 충분히 얇다면 보통의 경우의 기판과 박막의 역할이 바뀌었다고 볼 수 있고, 질화물 반도체층(50)은 전위가 적게 발생하는 상태로 성장하게 된다. 따라서, 결함 밀도가 작은 고품질의 질화물 반도체층(50)을 형성할 수 있고 질화물 반도체 결정결함 밀도가 감소하기 때문에 LED로 제조시 내부양자효율을 증대시킬 수 있다. 이와 같은 방법으로 형성한 본 발명에 따른 반도체 적층 구조(100)는 도 1의 (e) 우측 그림에서 보는 바와 같이, 질화물 반도체와 이종인 단결정 기판(10)과 결정화된 무기물 박막(30')을 포함한다. 기판(10)과 무기물 박막(30') 사이는 서로 분리된 복수개의 빈 공간(C)이 제어된 모양과 크기 및 2 차원적인 배열을 갖게 정의되어 있다. 반도체 적층 구조(100)는 또한 빈 공간(C) 위의 결정화된 무기물 박막(30') 상에서부터 성장하여 합체되면서 빈 공간(C) 사이의 영역에 보이드(V)를 형성하는 질화물 반도체층(50)을 포함한다. 무기물 박막(30')은 기판(10)과 접촉하는 다리부(30a) 및 다리부(30a)로부터 연장되어 기판(10)과 평행한 상면부(30b)를 포함한다. 빈 공간(C)은 형성방법 중에 희생층 패턴(20)이 제거되어 없어진 자리이다. 따라서, 빈 공간(C)은 희생층 패턴(20)의 모양과 크기 및 2 차원적인 배열을 그대로 따른다. 그러므로 빈 공간(C)이 제어된 모양과 크기 및 2 차원적인 배열을 갖게 하려면 희생층 패턴(20)의 모양과 크기 및 2 차원적인 배열을 정해야 한다. 본 실시예에서, 빈 공간(C)은 희생층 패턴(20)의 설계에 따라 기판(10) 전체에 같은 패턴으로 균일하게 정의되어 있다. 그러나, 빈 공간은 희생층 패턴의 설계에 따라 기판에 국부적으로 다른 패턴으로 정의되어 있을 수 있다. 빈 공간(C)이 존재하므로 기판(10)과 그 위에 형성하는 질화물 반도체층(50) 사이의 열팽창계수 차이가 있다면 빈 공간(C)이 면 방향으로 늘어나거나 압축되는 형태로 국부적인 변형을 일으켜 응력 에너지를 소모시킬 수 있다. 이에 따라 질화물 반도체층(50)에 걸리는 열응력을 감소시킬 수 있고, 따라서 기판(10) 휘어짐 현상을 줄일 수 있다. 이에 따라, 기판(10)이 대면적이라도 상대적으로 얇은 두께를 사용하는 것이 가능해진다. 특히, 이러한 빈 공간(C)은 희생층 패턴의 모양, 크기, 2차원 배열 등을 조절하여 제어할 수 있기 때문에 이러한 반도체 적층 구조(100)로부터 제조되는 LED의 광학적 특성, 예컨대 방출 패턴을 조절할 수 있다. 그리고, 희생층 패턴(20) 형성시 사진식각 또는 나노임프린트와 같은 제어된 방법으로 형성하기 때문에 빈 공간(C)이 불규칙적이거나 무작위로 형성되는 것이 아니라 제어된 방법으로 형성되므로 재현성이 좋고 소자 균일도가 우수하다. 이와 같은 결과로, 우수한 물성을 갖는 질화물 반도체층(50)을 에피택셜 성장시킬 수 있으므로, 고효율, 고신뢰성을 가지는 광전자 소자를 구현할 수 있다. 또한, 광 추출 효율 증가에 따른 고출력 LD 및 LED가 구현될 수 있다. 본 발명에 따른 반도체 적층 구조는 기판(10)과 질화물 반도체층(50)이 이러한 계면층을 사이에 두고 연결되어 있게 된다. 이러한 계면층은 빈 공간(C)과 선택적인 보이드(V)로 인해 기판(10)과 질화물 반도체층(50) 사이가 어느 정도 물리적으로 분리되어 있는 것이므로 응력 발생은 더욱 억제된 상태이고, 질화물 반도체층(50) 성장 후 본 발명에 따른 분리방법 및 장치에 의해 도 1의 (f)와 같이 질화물 반도체층(50)과 기판(10) 사이를 분리시킬 수 있다. 일반적인 종래 기술에 따라 질화물 반도체층을 기판 위에 성장하게 되면, 질화물 반도체층과 기판은 원자 수준의 접합을 하기 때문에 질화물 반도체층을 기판에서 분리하기 위해서는 레이저 리프트 오프와 같은 특수한 공정이 필요하다. 그러나, 본 발명에서는 계면층에 멤브레인 또는 브릿지(bridge)와 같은 무기물 박막(30')이 존재하므로 레이저 리프트 오프를 사용하지 않더라도 작은 기계적 힘으로 무기물 박막(30')을 붕괴시키거나 무기물 박막(30')과 기판(10) 계면을 분리하여 기판(10)으로부터 질화물 반도체층(50)을 분리하는 것이 용이해진다. 인장 혹은 압축 등의 작은 기계적인 힘으로도 분리가 되므로, 질화물 반도체층(50)이 휘어지거나 크랙이 발생하거나 깨지는 일이 없이 분리할 수 있다. 따라서, 기판(10)과 질화물 반도체층(50)의 분리가 필요한 응용 분야, 예컨대 수직형 LED 또는 수평형 LED, 임의의 기판에 이전된 LED 제조에 매우 유리하고 기판(10)을 재활용하기 쉽다. 뿐만 아니라 질화물 반도체층(50)을 후막으로 형성하여 기판(10)과 분리하게 되면 또는 자유 기립의 질화물 반도체 기판으로도 활용할 수 있으므로 우수한 질화물 반도체 성장을 위한 동종 기판으로서의 질화물 반도체 기판 제조가 용이해진다. 계면층의 모양은 희생층 패턴(20)의 모양에 따라 다양한 구성이 가능하다. 도 1에 도시한 예에서는 기판(10)에 수직인 단면이 직사각형인 희생층 패턴(20)을 형성하여, 무기물 박막(30')에 의해 정의되는 빈 공간(C)도 단면이 직사각형을 가진다. 빈 공간(C)의 단면은 도 3에 다양한 예로 도시하는 바와 같이, (a) 정사각형, 또는 (b) 상면보다 하면이 넓은 사다리꼴 모양 또는 반대로 (c) 상면보다 하면이 좁은 사다리꼴 모양일 수도 있다. 이러한 예들에서, 무기물 박막(30')은 기판과 접촉하는 다리부 및 다리부로부터 연장되어 기판과 평행한 상면부를 가지고, 다리부는 기판과 수직이거나 소정의 기울기를 가진다. 그러나, 상면부가 반드시 기판과 평행해야 하는 것은 아니다. 상면부가 convex 또는 concave와 같은 곡면을 가질 수도 있고, 빈 공간 단면이 삼각형인 경우처럼 상면부가 없을 수도 있다. 다리부 또한 반드시 직선 형태를 가져야 하는 것은 아니가. 다리부도 convex 또는 concave와 같은 곡면을 가질 수도 있고, 직선형이지만 기판과의 기울기가 변할 수도 있다. 그리고, 도 2에 도시한 예에서 희생층 패턴(20)은 라인 앤드 스페이스 타입이지만, 도 4에 다양한 예로 도시하는 바와 같이, 희생층 패턴은 다양한 모양을 가질 수 있다. 도 4는 본 발명에 따른 반도체 적층 구조 형성방법에서 다양한 희생층 패턴, 그로 인한 무기물 박막의 상면부 모양을 설명하기 위한 도면이다. 먼저 (a)를 참조하면, 기판 위에서 보았을 때 가로, 세로 길이가 "a"로 동일한 정사각형 모양의 패턴이 x, y 피치 "b"로 균일하게 형성되어 있다. (b)는 가로, 세로 길이가 "a"로 동일한 정사각형 모양의 패턴이 x, y 피치 "b"로 형성된 하나의 그룹(G1)이 x, y 피치 "c"로 균일하게 형성되어 있다. (c)는 가로, 세로 길이가 "a"와 "a'"로 다른 직사각형 모양의 패턴이 x 피치는 "b'"로, y 피치는 "d"로 형성되어 있다. b'와 d는 같거나 다를 수 있다. (d)는 가로, 세로 길이가 "a"와 "a'"로 다른 직사각형 모양의 패턴이 x 피치는 "b'"로, y 피치는 "d"로 형성된 하나의 그룹(G2)이 x, y 피치 "c'"로 균일하게 형성되어 있다. b'와 d는 같거나 다를 수 있다. 도 5는 본 발명에 따른 반도체 적층 구조에서 계면층 부분에 질화물 반도체층 일부가 포함된 경우를 도시한다. 실시예에 따라서는, 도 1을 참조하여 설명한 (e) 단계에서 질화물 반도체층(50)을 형성하는 동안 빈 공간(C) 사이의 무기물 박막(30') 부분에서도 질화물 반도체층(50')이 형성될 수 있다. 이 질화물 반도체층(50')이 성장해서 무기물 박막(30') 상면으로 넘어가기 전에 무기물 박막(30') 상면에서 성장한 질화물 반도체층(50)이 합체되는 경우, 도 5에 도시한 바와 같이, 빈 공간(C) 사이에는 질화물 반도체층(50')이 일부 채워지고 그 윗부분은 질화물 반도체층(50)과의 사이에 보이드(V)를 형성하게 된다. 도 6은 본 발명에 따른 반도체 적층 구조에서 질화물 반도체층의 상면 모양을 설명하기 위한 도면이다. 실시예에 따라서는, 질화물 반도체층(50)이 합체되기 전에 도 1을 참조하여 설명한 (e) 단계에서 성장을 종료할 수 있다. 그러면 질화물 반도체층(50)은 서로 분리된 복수개의 질화물 반도체층으로 형성된다. 도 6의 (a)는 예컨대 도 4의 (a)와 같은 희생층 패턴(20)을 이용하면서 질화물 반도체층(50)이 합체되기 전에 성장을 종료한 경우라고 할 수 있다. 정사각형 모양의 질화물 반도체층을 복수개 얻을 수 있다. 도 6의 (b)는 예컨대 도 4의 (c)와 같은 희생층 패턴(20)을 이용하면서 질화물 반도체층(50)이 합체되기 전에 성장을 종료한 경우라고 할 수 있다. 직사각형 모양의 질화물 반도체층을 복수개 얻을 수 있다. 원하는 소자 활용 용도에 따라, 예컨대 LCD BLU(Back Light Unit)에서와 같이 직사각형 모양의 LED 칩이 필요한 경우 등, 희생층 패턴(20) 모양을 달리 하면 빈 공간(C)의 모양이 달라지고 그 위에 씨앗층 역할을 하는 무기물 박막(30') 모양이 달라져 그 위에 형성되는 질화물 반도체층(50) 모양이 달라지는 구성을 이용할 수 있는 것이다. 이와 같이 질화물 반도체층(50)은 서로 분리된 복수개의 질화물 반도체층으로 형성이 될 수 있고, 질화물 반도체층(50) 제조시 LED 구성에 필요한 활성층을 포함하는 다층구조로 형성을 하면, 서로 분리된 복수개의 질화물 반도체층(50)은 이미 칩 단위로 제조가 되어 분리가 된 형태이므로, 본 발명에 따른 질화물 반도체층 분리방법에 의해 기판(10)으로부터 분리시 기존에 칩 단위 제조에 필요한 다이싱(dicing)과 같은 소자 개별화 공정없이 바로 패키지 공정에 투입될 수 있는 장점이 있다. 다음, 본 발명에 따른 질화물 반도체층 분리방법 및 장치에 대해 보다 상세히 설명한다. 본 발명에 따른 질화물 반도체층 분리방법은 본 발명에 따른 반도체 적층 구조(100), 또는 본 발명에서와 같이 빈 공간을 포함하는 계면층이 기판과 질화물 반도체층 사이에 형성되어 있는 다른 반도체 적층 구조의 상면과 하면에 수직 방향 힘을 주어 분리하는 제1의 방법과, 수평 방향의 힘을 주어 분리하는 제2의 방법, 상대적인 원운동의 힘을 주어 분리하는 제3의 방법이 가능하다. 제1의 방법은 압축 상태와 인장 상태의 두 가지가 가능하다. 먼저 압축 상태는 상면과 하면을 눌러서 무기물 박막 또는 계면층을 파괴시킴으로써 수행하는 방법이다. 인장 상태는 상면과 하면을 멀어지게 잡아떼어 무기물 박막 또는 계면층을 파괴시킴으로써 수행하는 방법이다. 제2의 방법은, 상면과 하면을 서로에 대해 상대적으로 수평 방향 이동시키는 전단력에 의해 무기물 박막 또는 계면층을 파괴시킴으로써 수행하는 전단 상태의 방법이다. 제3의 방법은 상면과 하면을 서로에 대해 비틀어 상대적으로 수평 원 운동시켜 무기물 박막 또는 계면층을 파괴시킴으로써 수행하는 비틀음 상태의 방법이다. 이러한 제1 내지 제3의 방법을 조합해서 수행하는 것도 가능하다. 레이저 조사와 같은 방법을 이용하지 않고 이러한 기계적인 힘으로 분리할 수 있는 이유는 본 발명에 따른 반도체 적층 구조(100)나 다른 반도체 적층 구조에서 빈 공간(C)과 선택적인 보이드(V)를 포함하는 계면층 때문이다. 본 발명에 따른 질화물 반도체층 분리장치는 이러한 분리방법을 구현하는 데에 적합하다. 이하에서는 본 발명에 따른 반도체 적층 구조(100)를 이용하여 기판(10)과 질화물 반도체층(50)을 분리하는 경우를 예로 들어 도시하지만, 반도체 적층 구조(100)와 다른 구조라도 빈 공간을 포함하는 계면층이 기판과 질화물 반도체층 사이에 형성되어 있는 반도체 적층 구조라면 본 발명에 따른 분리방법 및 장치를 이용해 기계적으로 분리할 수 있다. 도 7에 도시한 바와 같이 본 발명에 따른 분리장치는 반도체 적층 구조(100)의 상면과 하면에 각각 적용되는 치구로서 한 쌍의 판상 분리부재(210, 220)를 포함한다. 제1 분리부재(210)는 반도체 적층 구조의 하면, 즉 기판(10)측에 놓인다. 제2 분리부재(220)는 반도체 적층 구조의 상면, 즉 질화물 반도체층(50)측에 놓인다. 제1 분리부재(210)와 기판(10) 사이는 일시적인 접착이 될 수 있다. 마찬가지로, 제2 분리부재(220)와 질화물 반도체층(50) 사이도 일시적인 접착이 될 수 있다. 접착없이 단순히 접촉하는 것일 수도 있다. 본 명세서에서 일시적이라 함은, 분리 단계가 수행되는 동안에는 존재하다가 나중에 제거된다는 것을 의미한다. 일시적인 접착은 접착층, 접착 코팅, 접착테이프, 정전기적인 힘, 진공에 의한 힘 등 다양한 방법이 될 수 있다. 한 쌍의 분리부재(210, 220)는 반도체 적층 구조(100)를 다 덮을 수 있도록 반도체 적층 구조(100)보다 크거나 반도체 적층 구조(100)를 다 덮지 않게 작을 수도 있다. 도 8은 본 발명에 따른 질화물 반도체층 분리장치에 포함되는 분리부재(210, 220)의 다른 예를 도시한다. 분리부재(210, 220)는 대체로 판상이지만 그 안에 반도체 적층 구조(100)가 안착할 안착홈(S)이 형성된 것일 수도 있다. 그리고 안착홈(S)을 통하여 반도체 적층 구조(100)를 흡착하기 위한 진공력을 제공할 수 있도록 진공 공급홀이 더 형성되어 있을 수도 있다. 안착홈(S)의 크기는 반도체 적층 구조(100)의 크기와 동일하게 구비할 수 있지만 반도체 적층 구조(100)의 크기보다 상대적으로 크게 형성할 수 있다. 이 경우, 안착홈(S)은 반도체 적층 구조의 크기 및 형상에 관계없이 다양한 반도체 적층 구조를 안착시킬 수 있다. 진공 공급홀은 안착홈을 관통하여 형성되며, 관통된 홀을 통해 진공을 공급한다. 따라서, 안착홈(S)에 안착된 반도체 적층 구조(100)를 흡착하여 움직이지 않도록 고정시킨다. 이를 위해, 진공 공급홀은 진공 펌프와 연결된 진공 공급 라인과 연결되어 진공 펌프로부터 공급하는 진공을 제공한다. 또한, 진공 공급홀은 다양한 패턴으로 형성될 수 있지만, 반도체 적층 구조(100)의 전면을 골고루 흡착하기 위해 또는 반도체 적층 구조(100)의 크기에 상관없이 다양한 크기의 반도체 적층 구조를 흡착하기 위해 방사형 패턴으로 형성될 수 있다. 안착홈(S)은 분리부재(210, 220) 중 어느 하나에만 형성될 수도 있다. 한 쌍의 분리부재(210, 220)는 그 사이에 반도체 적층 구조(100)를 지지한 채 도 9에서와 같이 외력을 인가하는 구동부(230)와 제어부(240)가 포함된 분리장치(200)에 도입이 될 수 있다. 이 때에는 분리부재(210, 220)가 반도체 적층 구조(100)를 잘 지지할 수 있도록 일시적인 접착층이 그들 사이에 개재될 수 있다. 다른 방법으로, 제1 분리부재(210)가 분리장치(200)에 먼저 도입된 후 반도체 적층 구조(100)가 그 위에 놓이고 제2 분리부재(220)가 도입되는 순으로 순차 도입될 수도 있다. 도입되는 분리부재(210, 220)를 지지하거나 잡기 위하여 분리장치(200)는 적절한 베이스 부재와 홀딩 부재를 더 포함할 수 있다. 대신에 한 쌍의 분리부재(210, 220)는 분리장치(200)의 일부로서 구성될 수도 있다. 이 때에는 제1 분리부재(210) 위에 반도체 적층 구조(100)를 놓고, 제2 분리부재(220)를 반도체 적층 구조(100)측으로 이동시켜 분리부재(210, 220)에 의해 반도체 적층 구조(100)가 지지되게 한다거나, 제2 분리부재(220)는 반도체 적층 구조(100)와 이격시켜 놓고 제1 분리부재(210)가 반도체 적층 구조(100)를 지지하게 하는 식으로 분리 단계 대기 상태가 된다. 전류 온/오프(on/off)에 따라 흡/탈착이 쉽도록 분리부재(210, 220)가 반도체 적층 구조(100)를 지지하는 데에는 정전기적인 힘, 진공에 의한 힘이 바람직할 수 있고, 이를 위하여 분리장치(200)는 정전하 발생장치, 진공 펌프 등 다양한 구성요소를 더 포함할 수 있다. 분리장치(200)는 기판(10)과 질화물 반도체층(50)간의 기계적 분리를 위하여, 한 쌍의 분리부재(210, 220)에 대한 상대적인 압축, 인장, 전단, 비틀음 상태 중 적어도 어느 하나, 또는 이들의 조합을 구현할 수 있다. 분리부재(210, 220)의 상대적인 움직임에 의해 이러한 상태들이 구현되므로 분리부재(210, 220) 중 어느 하나는 고정하고 다른 하나에 구동부(230)에 의한 외력을 인가할 수 있다. 바람직하게는 하측에 놓이는 분리부재가 고정이 되는 것이 안정적인 측면에서 선호될 수 있다. 본 실시예에서 하측에 놓이는 분리부재는 기판(10)과 접하는 제1 분리부재(210)인 경우를 예로 들어 설명하지만, 질화물 반도체층(50)과 접하는 제2 분리부재(220)가 하측에 놓일 수도 있다. 먼저 제1의 방법을 구현하기 위해, 구동부(230)는 서로 대향하여 배치된 분리부재(210, 220) 중 상측에 놓이는 제2 분리부재(220)를 수직 방향으로 구동시키는 구동수단을 구비한다. 구동수단은 예를 들어 에어 실린더, 공압, 전기 모터 또는 유압 모터이고, 기판(10)과 질화물 반도체층(50)이 분리될 때까지 제2 분리부재(220)를 수직 방향(상하 방향)으로 구동시킨다. 제1의 방법 중 압축 상태를 구현하기 위해, 구동부(230)는 하방으로 제2 분리부재(220)를 구동시켜 압축력을 제공한다. 도 10의 (a)는 압축 상태에 의해 질화물 반도체층(50)과 기판(10)을 분리하는 경우를 도시한다. 도 10의 (b)는 무기물 박막(30')을 파괴시킴으로써 질화물 반도체층(50)과 기판(10)이 분리된 경우를 도시한다. 이 때 무기물 박막(30')의 파괴로 질화물 반도체층(50)과 기판(10)이 분리된 직후에는 제2 분리부재(220)가 아래로 눌려지는 힘이 해제되어야 질화물 반도체층(50)의 파손을 막을 수 있다. 파괴된 무기물 박막(30')의 일부는 질화물 반도체층(50)에 붙어 있을 수 있다. 따라서, 압축 상태 구현의 경우에는 종말점 검출(end point detect)이 필요하고, 제어부(240)는 종말점 검출시 구동부(230)를 제어하여 제2 분리부재(220)의 이동을 그 상태에서 멈추거나 상방으로 이격시킨다. 종말점 검출은 다음과 같은 방법 및 장치 구현이 가능하다. 분리장치(200)에 추가로 포함시킬 수 있는 분리감지부(250)에서는 여러 가지 방법으로 질화물 반도체층(50)과 기판(10)의 분리 정도를 감지할 수 있다. 특히 분리부재(210, 220) 사이의 거리(압축 두께로 환산될 수 있음)를 측정함으로써 질화물 반도체층(50)과 기판(10)의 분리 정도를 감지할 수 있다. 분리감지부(250)는 분리부재(210, 220) 사이의 거리를 측정할 수 있는 위치라면 어느 곳에라도 부착 가능하다. 분리감지부(250)로는 레이저 센서, 정전용량 센서, 엔코더 등과 같이 서로 이격된 두 물체간의 거리를 실시간으로 측정할 수 있는 것이라면 그 종류에 제한이 없이 사용될 수 있다. 분리부재(210, 220) 사이에 반도체 적층 구조(100)가 끼워져 있는 초기상태를 시작점으로 보고, 무기물 박막(30')이 형성된 부분, 즉 계면층의 두께 이하로 제2 분리부재(220)가 하방 이동하면 질화물 반도체층(50)과 기판(10)이 분리된 것으로 판단할 때를 분리점이라고 한다면, 제어부(240)는 분리부재(210, 220)가 분리점 위치로 이동할 때까지는 제2 분리부재(220)에 일정한 압력을 가하거나 가하는 가압력을 서서히 증가시키고, 분리점 위치에 도달한 이후에는 가압력을 완전히 해제하거나 제2 분리부재(220)를 상방으로 들어 올릴 수 있도록 구동부(230)를 제어함으로써 제2 분리부재(220)의 구동을 조절한다. 이와 같이, 분리감지부(250)와 제어부(240)를 이용하면 질화물 반도체층(50)과 기판(10) 분리 정도에 따라 가압 압력을 조절할 수 있고, 압축 상태에서 과한 압력이 가해져 질화물 반도체층(50)이 손상되는 것을 방지할 수 있다. 분리감지부(250)는 압력 모니터링 방법에 의해서도 구현될 수 있다. 이것은 무기물 박막(30')이 압축력을 견디는 동안에는 서서히 증가하는 압력이 감지되다가 압축력에 의해 무기물 박막(30')이 파괴되는 순간에 급격한 압력 변화가 발생하는 원리를 이용한다. 이 방법을 구현하려면 무기물 박막(30')에 걸리는 압력을 모니터링할 수 있도록 분리감지부(250)를 구성한다. 바람직하기로는 이 때의 분리감지부(250)는 로드셀(load cell) 구성을 취한다. 로드셀은 분리부재(210, 220) 중 어느 하나에 장착하거나, 분리부재(210, 220) 중 어느 하나를 로드셀 자체로 구현하는 것에 의할 수도 있다. 로드셀은 가해지는 압축력에 따른 압력 변화를 모니터링하는 장치로서 로드셀을 통해 압력이 해제되거나 급격히 변화되는 순간을 질화물 반도체층(50)과 기판(10)이 분리된 것으로 분리점으로 판단하고, 분리점 위치에 도달한 이후에는 가압력을 완전히 해제하거나 제2 분리부재(220)를 상방으로 들어 올릴 수 있도록 구동부(230)를 제어함으로써 제2 분리부재(220)의 구동을 조절한다. 다음, 제1의 방법 중 인장 상태를 구현하기 위해, 분리부재(210, 220)에 반도체 적층 구조(100)가 확실히 고정된 상태에서 구동부(230)는 상방으로 제2 분리부재(220)를 구동시켜 인장력을 제공한다. 도 11의 (a)는 본 발명에 따른 질화물 반도체층 분리장치를 이용해 인장 상태에 의해 질화물 반도체층(50)과 기판(10)을 분리하는 경우를 도시한다. 인장 상태는 분리부재(210, 220)를 서로 멀어지게 잡아떼어 무기물 박막(30')을 파괴시킴으로써 수행하는 방법이다. 인장력은 질화물 반도체층(50)과 기판(10)이 분리될 때까지, 다시 말해 분리부재(210, 220)간이 분리 시작 전보다 이격될 때까지 인가될 수 있다. 이 때 종말점 검출은 필수적인 구성은 아니다. 도 11의 (b)는 인장 상태에 의해 질화물 반도체층(50)과 기판(10)이 분리된 경우를 도시한다. 이 때 무기물 박막(30')은 부분적으로 질화물 반도체층(50)에 딸려 오거나 기판(10)에 남을 수 있다. 다음, 제2의 방법인 전단 상태를 구현하기 위해, 구동부(230)는 제1 분리부재(210)에 대하여 제2 분리부재(220)를 수평 방향으로 밀어서 전단력을 제공한다. 도 12의 (a)는 본 발명에 따른 질화물 반도체층 분리장치를 이용해 전단 상태에 의해 질화물 반도체층(50)과 기판(10)을 분리하는 경우를 도시한다. 전단력은 무기물 박막(30')을 파괴시킴으로써 질화물 반도체층(50)과 기판(10)이 분리될 때까지, 다시 말해 분리부재(210, 220)간의 상대적인 수평 이동이 발생될 때까지 인가될 수 있다. 이 때에도 종말점 검출은 필수적인 구성은 아니다. 도 12의 (b)는 전단 상태에 의해 질화물 반도체층(50)과 기판(10)이 분리된 경우를 도시한다. 이 때 무기물 박막(30')은 부분적으로 질화물 반도체층(50)에 딸려 오거나 기판(10)에 남을 수 있다. 다음, 제3의 방법인 비틀음 상태를 구현하기 위해, 구동부(230)는 제1 분리부재(210)에 대하여 제2 분리부재(220)를 비트는 힘 또는 제2 분리부재(220)에 수직인 축을 중심으로 하는 회전력을 제공한다. 도 13의 (a)는 본 발명에 따른 질화물 반도체층 분리장치를 이용해 비틀음 상태에 의해 질화물 반도체층(50)과 기판(10)을 분리하는 경우를 도시한다. 회전력은 무기물 박막(30')을 파괴시킴으로써 질화물 반도체층(50)과 기판(10)이 분리될 때까지, 다시 말해 분리부재(210, 220)간의 상대적인 원운동이 가능할 때까지 인가될 수 있다. 이 때도 종말점 검출은 필수적인 구성은 아니다. 도 13의 (b)는 비틀음 상태에 의해 질화물 반도체층(50)과 기판(10)이 분리된 경우를 도시한다. 이 때 무기물 박막(30')은 부분적으로 질화물 반도체층(50)에 딸려 오거나 기판(10)에 남을 수 있다. 이러한 분리방법과 장치(200)에 의해 분리된 질화물 반도체층(50)은 딸려온 무기물 박막(30') 일부 혹은 파편을 제거하기 위한 소정 공정을 거친 후, 아니면 이러한 공정없이 다른 기판으로 전사되어 소자 형태로 가공이 될 수 있고, 도 6을 참조하여 설명한 바와 같이 이미 칩 단위로 제조가 되어 분리가 된 경우라면 다이싱과 같은 공정없이 바로 패키지 공정에 투입될 수도 있다. 기판(10)으로부터 분리된 질화물 반도체층(50)을 다른 기판으로 옮기거나 다른 공정에 투입될 수 있도록 하기 위하여, 분리장치(200)는 분리된 질화물 반도체층을 다음 목적지로 운반하는 장치(미도시), 그리고 질화물 반도체층(50)에 딸려온 무기물 박막(30') 일부 혹은 파편을 제거하기 위한 장치(미도시)를 더 포함할 수도 있다. 본 실시예에서 제2 분리부재(220)측에 질화물 반도체층(50)이 일시적 접착하는 상태이므로 하방을 향하여 있는 제2 분리부재(220)를 반전시킨 후 일시적 접착을 해제하고 질화물 반도체층(50)을 다음 목적지로 운반하기 위해 분리장치(200)는 제2 분리부재(220)를 반전할 수 있는 장치 구성을 가질 수도 있다. 질화물 반도체층(50)이 일시적 접착된 제2 분리부재(220)측을 분리장치(200) 하측에 구성하는 경우에는 이러한 반전 장치 구성은 필요하지 않을 수도 있다. 분리하고 남은 기판(10)은 다른 질화물 반도체층 성장을 위해 재활용될 수 있다. 반도체 적층 구조(100) 및 분리된 기판(10)과 질화물 반도체층(50)의 운반은 이송 암(arm) 등을 포함하는 이송 기구에 의해 이루어질 수 있다. 이와 같은 분리방법 및 장치에 따르면, 레이저와 같은 고밀도 고출력 에너지를 사용할 필요없이 작은 기계적인 힘에 의해 기판과 질화물 반도체층을 분리할 수 있다. 공정 과정 및 장치 구성이 단순하고 공정 시간이 짧다. 이 장치는 진공이나 특정 가스 분위기를 만들지 않으므로 밀폐된 챔버 공간을 필요로 하지 않아 경제적이다. 이미 성장된 질화물 반도체층에 영향을 주지 않으면서 경제적으로 기판과 분리할 수 있는 방법과 장치이므로 질화물 반도체층 분리가 필요한 수직형, 수평형, 또는 임의의 기판에 이전된 LED 제조 또는 질화물 반도체 기판 제조와 같은 분야에 활용도가 높다. 질화물 반도체층을 분리하면 소자 구동시 발생하는 열을 손쉽게 제거할 수 있으며, 기판이 존재할 경우 기판 내부에 갇혀서 빠져나오지 못하는 빛을 밖으로 빼낼 수 있는 장점이 있고, 질화물 반도체 성장을 위한 동종 기판으로 활용할 가치가 있다. 다음, 본 발명에 따른 실험 결과를 설명함으로써 본 발명을 보다 상세히 설명한다. 실험 과정은 다음과 같다. 도 1을 참조하여 설명한 바와 같이 사파이어 기판 위에 라인 앤드 스페이스 타입 PR 패턴을 형성한 후 110℃에서 ALD에 의해 알루미나 박막을 형성하였다. 그런 다음, 공기 중에서 열처리를 실시함으로써 PR 패턴을 제거해 빈 공간을 형성하고 알루미나 박막은 결정화를 시켰다. 도 14의 (a)는 이러한 방법으로 사파이어 기판 위에 형성된 빈 공간과 알루미나 박막을 보여주는 SEM 사진이다. 다음으로 알루미나 박막 위에 GaN층을 성장시켰다. 성장 온도, 기체 유량, 압력 조절을 통하여 빈 공간 위 알루미나 박막에서부터 선택적으로 GaN층을 성장시켜 도 14의 (b)에 도시한 바와 같은 GaN층을 얻었다. 도 14의 (b)에서 볼 수 있는 바와 같이 GaN층은 기판 부분이 아닌 빈 공간 부분에서 선택적으로 성장하였고 빈 공간 사이는 도 5에 도시한 것과 같이 일부 GaN층이 형성되고 보이드도 형성되었다. 다음으로, 본 발명에서 제시하는 바와 같은 기계적인 분리를 통해 GaN층과 사파이어 기판을 분리하였다. 도 15의 (a)는 분리 후 GaN층을 촬영한 SEM 사진이고 (b)는 기판을 촬영한 SEM 사진이다. 도 15에 제시한 바와 같이 기계적인 분리를 통해 GaN층과 사파이어 기판을 성공적으로 분리할 수 있다. 이상에서 본 발명의 바람직한 실시예에 대해 도시하고 설명하였으나, 본 발명은 상술한 특정의 바람직한 실시예에 한정되지 아니하며, 청구범위에서 청구하는 본 발명의 요지를 벗어남이 없이 당해 발명이 속하는 기술분야에서 통상의 지식을 가진 자라면 누구든지 다양한 변형 실시가 가능한 것은 물론이고, 그와 같은 변경은 청구범위 기재의 범위 내에 있게 된다. A semiconductor stacking structure according to the present invention comprises: a monocrystalline substrate which is disparate from a nitride semiconductor; an inorganic thin film which is formed on a substrate to define a cavity between the inorganic thin film and the substrate, wherein at least a portion of the inorganic thin film is crystallized with a crystal structure that is the same as the substrate; and a nitride semiconductor layer which is grown from a crystallized inorganic thin film above the cavity. The method and apparatus for separating a nitride semiconductor layer according the present invention mechanically separate between the substrate and the nitride semiconductor layer. The mechanical separation can be performed by a method of separation of applying a vertical force to the substrate and the nitride semiconductor layer, a method of separation of applying a horizontal force, a method of separation of applying a force of a relative circular motion, and a combination thereof. 질화물 반도체와 이종인 단결정 기판; 상기 기판과의 사이에 빈 공간(cavity)이 정의되도록 상기 기판 상에 형성되고 상기 기판과 같은 결정 구조로 적어도 일부 결정화된 무기물 박막; 및 상기 빈 공간 위의 상기 결정화된 무기물 박막 상에서부터 성장된 질화물 반도체층을 포함하는 반도체 적층 구조. 제1항에 있어서, 상기 질화물 반도체층은 합체되어 있거나 합체되어 있지 않은 것을 특징으로 하는 반도체 적층 구조. 제1항에 있어서, 상기 질화물 반도체층은 수평 방향으로 연속적이거나 불연속적인 것을 특징으로 하는 반도체 적층 구조. 제1항에 있어서, 상기 질화물 반도체층은 상기 빈 공간 사이의 영역에 보이드(void)를 형성하는 것을 특징으로 하는 반도체 적층 구조. 제1항에 있어서, 상기 무기물 박막은 기판과 접촉하는 다리부 및 다리부로부터 연장된 상면부를 포함하는 것을 특징으로 하는 반도체 적층 구조. 제5항에 있어서, 상기 상면부는 상기 기판과 평행한 면 또는 곡면을 가지고, 상기 다리부는 상기 기판과 수직이거나 소정의 기울기를 가지거나 곡면을 가지는 것을 특징으로 하는 반도체 적층 구조. 제1항에 있어서, 상기 질화물 반도체층은 서로 분리된 복수개의 질화물 반도체층으로 형성되는 것을 특징으로 하는 반도체 적층 구조. 질화물 반도체와 이종인 단결정 기판 상에 희생층 패턴을 형성하는 단계; 상기 희생층 패턴 상에 무기물 박막을 형성하는 단계; 상기 기판과 무기물 박막으로 정의되는 빈 공간(cavity)이 형성되도록, 상기 무기물 박막이 형성된 상기 기판으로부터 상기 희생층 패턴을 제거하는 단계; 상기 기판과 같은 결정 구조로 상기 무기물 박막을 적어도 일부 결정화시키는 단계; 및 상기 빈 공간 위의 상기 결정화된 무기물 박막 상에서부터 질화물 반도체층을 성장시키는 단계를 포함하여 반도체 적층 구조를 형성한 후, 상기 기판과 상기 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 포함하는 질화물 반도체층 분리방법. 제1항 기재의 반도체 적층 구조에서 기판과 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 포함하는 질화물 반도체층 분리방법. 제8항에 있어서, 상기 질화물 반도체층을 성장시키는 단계에서 상기 질화물 반도체층은 서로 분리된 복수개의 질화물 반도체층으로 형성하는 것을 특징으로 하는 질화물 반도체층 분리방법. 제8항 또는 제9항에 있어서, 상기 기계적으로 분리시키는 단계는, 상기 기판과 질화물 반도체층에 수직 방향 힘을 주어 분리하는 방법, 수평 방향의 힘을 주어 분리하는 방법, 상대적인 원운동의 힘을 주어 분리하는 방법, 및 그 조합의 방법으로 수행하는 것을 특징으로 하는 질화물 반도체층 분리방법. 제11항에 있어서, 상기 기판과 질화물 반도체층이 수직 방향으로 압축되는 두께 또는 압력을 감지하여 종말점 검출하는 것을 특징으로 하는 질화물 반도체층 분리방법. 제11항에 있어서, 상기 기판과 질화물 반도체층 분리 후, 상기 분리된 질화물 반도체층을 다른 기판으로 전사하거나 패키징하는 단계를 더 포함하는 질화물 반도체층 분리방법. 제1항 기재의 반도체 적층 구조 또는 기판과 질화물 반도체층 사이에 빈 공간을 포함하는 계면층이 포함된 다른 반도체 적층 구조에서 상기 기판과 질화물 반도체층 사이를 기계적으로 분리시키는 단계를 수행하는 질화물 반도체층 분리장치. 제14항에 있어서, 상기 반도체 적층 구조의 기판과 질화물 반도체층에 각각 적용되는 치구로서 한 쌍의 판상 분리부재를 포함하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제15항에 있어서, 상기 분리부재와 상기 반도체 적층 구조 사이는 일시적인 접착이 되는 것을 특징으로 하는 질화물 반도체층 분리장치. 제16항에 있어서, 상기 일시적인 접착은 접착층, 접착 코팅, 접착테이프, 정전기적인 힘 또는 진공에 의한 힘 중 어느 하나인 것을 특징으로 하는 질화물 반도체층 분리장치. 제15항에 있어서, 상기 분리부재 중 적어도 어느 하나에는 안착홈이 형성되고, 상기 안착홈을 통하여 상기 반도체 적층 구조를 흡착하기 위한 진공력을 제공할 수 있도록 진공 공급홀이 더 형성되어 있는 것을 특징으로 하는 질화물 반도체층 분리장치. 제14항에 있어서, 상기 반도체 적층 구조에 외력을 인가하는 구동부; 및 상기 구동부를 제어하는 제어부를 포함하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제19항에 있어서, 상기 구동부는 상기 기판과 질화물 반도체층에 상대적인 압축, 인장, 전단, 비틀음 및 그 조합의 외력을 인가하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제20항에 있어서, 상기 반도체 적층 구조의 기판과 질화물 반도체층에 각각 적용되는 치구로서 한 쌍의 판상 분리부재를 적어도 어느 한쪽에는 상기 반도체 적층 구조와 일시적 접착을 한 상태에서 상기 외력을 인가하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제21항에 있어서, 상기 분리부재 중 어느 한쪽은 고정하고 다른 한쪽을 나머지에 대해 수직 방향, 수평 방향 또는 회전 외력을 인가하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제21항에 있어서, 상기 분리부재 중 어느 한쪽은 고정하고 다른 한쪽을 나머지에 대해 수직 방향으로 구동시켜 압축력을 제공하고, 무기물 박막 또는 계면층 파괴로 상기 질화물 반도체층과 기판이 분리된 직후에 압축력을 해제하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제23항에 있어서, 상기 제어부는 상기 질화물 반도체층과 기판이 분리되는 종말점 검출을 통해 상기 구동부를 제어하여 상기 분리부재의 상대적 이동을 멈추거나 서로에 대해 이격시키는 것을 특징으로 하는 질화물 반도체층 분리장치. 제24항에 있어서, 상기 종말점 검출을 위한 분리감지부를 더 포함하는 것을 특징으로 하는 질화물 반도체층 분리장치. 제25항에 있어서, 상기 분리감지부는 분리부재 사이의 거리 측정 또는 압력 모니터링 방법에 의한 것을 특징으로 하는 질화물 반도체층 분리장치. 제14항에 있어서, 상기 분리된 질화물 반도체층을 다른 기판으로 전사하거나 패키징하기 위해 운반하는 장치를 더 포함하는 것을 특징으로 하는 질화물 반도체층 분리장치.