HIGH-SPEED DIGITAL LOGIC CIRCUIT FOR SAR_ADC, AND SAMPLING ADJUSTMENT METHOD

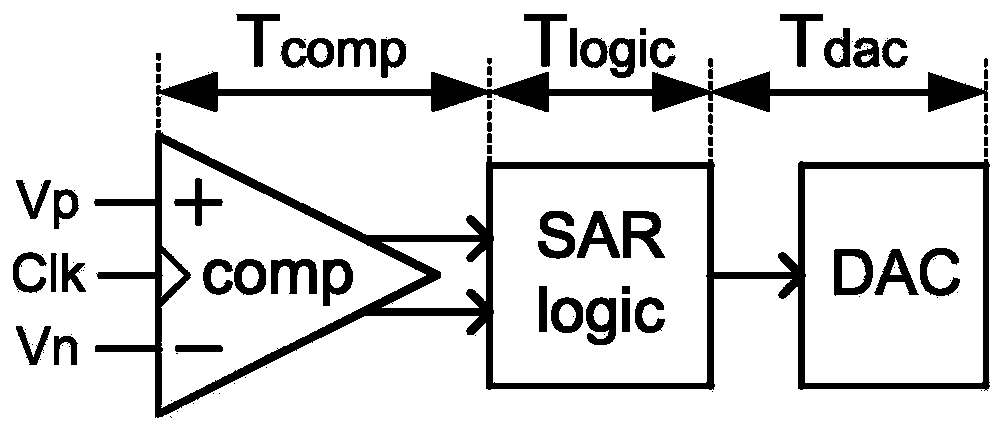

本发明属于模拟或数模混合集成电路技术领域,涉及一种高速SAR_ADC数字逻辑电路;具体为一种用于SAR_ADC的高速数字逻辑电路及采样调节方法。 近年来,随着模数转换器性能指标的进一步提高,特别是随着集成电路工艺技术的不断发展,对高速异步逐次逼近型模数转换器的研究也越来越深入。随着集成电路制造工艺的不断演进,高增益运算放大器的设计变得越来越困难,由于不需要运算放大器,SAR结构ADC具有天然的低功耗优势,特别是在纳米级工艺节点下,SAR结构ADC的速度又得到了巨大的提升。因此,高速SAR结构ADC成为目前模数转换器的研究热点。传统的SAR结构ADC中,由于采用异步逻辑,每一次逐次逼近过程中,比较器完成比较器之后,给出触发信号触发数字逻辑,数字逻辑通过获取比较器的比较结果,控制电容阵列中的开关切换,从而使得电容阵列中,电荷守恒极板的电压进行逐次逼近。但传统结构中,比较器的比较过程和数字逻辑电路的工作过程是串行进行的,延迟较大。因此,传统结构不利于高速SAR结构ADC的实现。 传统SAR结构ADC环路延迟示意图如图1所示,其中Tcomp表示比较器的比较延迟,Treset表示比较器的复位延迟,Tlogic表示数字逻辑延迟,Tdac表示DAC建立延迟。由图1可知,传统的SAR结构ADC数字逻辑电路中,一个逐次逼近周期的延迟可以近似表示为Tcomp+Tlogic+Tdac,以10位SAR结构ADC为例进行说明,总的延迟为10(Tcomp+Tlogic+Tdac)。

总体而言,上述3个延迟时间大致相同,如果可以减小其中一个环节的延迟时间,总的延迟时间可以大大减小,这对于提高SAR结构ADC的整体速度非常重要。由电路知识可知,比较器的复位延迟Treset和比较起的比较延迟Tcomp大致相同,而如图1所示,比较器的复位延迟(Tlogic+Tdac)明显长于比较器的比较延迟Tcomp,比较器的复位延迟并不需要这么长的时间,而是比较器必须等待Tlogic+Tdac的延迟之后,才能进行下一次比较。

针对上述问题,现有技术提出了并行SAR logic技术,SAR结构ADC环路延迟示意图如图2所示。比较器comp和SAR logic被信号Clk同时触发,通过合理设置比较器comp和SAR logic的延迟,使得比较器的延迟Tcomp和SAR logic的延迟Tlogic大致相当。每次比较周期中,比较器comp的有效输出信号为Dp/Dn,SAR logic输出的逻辑窗口logic window。在每一次比较周期中,对应的逻辑窗口捕获相应的比较器有效输出结果Dp/Dn,然后电容阵列开始建立。通过这种并行SAR logic技术,使得比较器comp和SAR logic同时被触发,通过合理设置比较器comp和SAR logic的延迟,使得比较器的有效输出结果Dp/Dn能够被SAR logic输出的逻辑窗口logic window捕获,从而触发电容阵列的建立,通过上述技术,使得整个SAR_ADC的延迟时间变为Tcomp+Tdac,从而大幅度降低了SAR_ADC的延迟时间,明显提升了SAR_ADC的转换速度。

实际工作中,为了能够快速捕获比较器comp的有效输出信号Dp/Dn,SAR logic输出的逻辑窗口logic window的延迟会稍微小于比较器comp的比较延迟,从而使得只要比较 器的有效比较结果一旦输出,就会立刻被逻辑窗口logic window捕获。 上述结构的缺点是,当SAR logic输出逻辑窗口logic window后,而比较器还没有输出有效比较器结果时,逻辑窗口logic window会捕获一个无效的比较结果,使得电容阵列开始建立时,向一个错误的方向建立(improper settling of DAC),当比较器comp输出有效的比较结果后,电容阵列才会转而向一个正确的方向建立,这种现象会降低电容阵列的建立精度,从而影响整个SAR_ADC的精度。另一方面,随着SAR_ADC工作速度的提高,产生一个高速逻辑窗口logic window变得越来越困难,通过逻辑窗口对比较器的有效结果进行捕获的设计目的不能得到完全的体现。同时,异步SAR logic结构还存在一个问题,随着输入信号、电源电压,温度和工艺角等因素的变化,SAR_ADC完成整个逐次逼近过程所需要的时间是变化的,为了保证SAR_ADC完成整个逐次逼近过程后再对输入信号进行采样,SAR_ADC的采样必须满足最慢转换时间,这就使得在大多数情况下,SAR_ADC完成整个逐次逼近过程后,需要等待一段时间采样进行采样,这会造成时间的浪费,限制了SAR_ADC的转换速度。 由于需要满足SAR_ADC的采样必须满足最慢转换时间,采样时间被明显压缩,从而降低了SAR_ADC的采样精度。为了获得更高的采样精度,在设计中,必须通过增加采样开关尺寸、减小DAC面积或者降低SAR_ADC转换速度等方法,上述方法会明显增加设计成本或者引入其他非理想因素,增加了电路的设计难度。 发明内容 基于上述分析,本发明提出了一种用于SARADC的高速数字逻辑及采样调节方法。仍然采用并行数字逻辑原理,比较器的比较过程和数字逻辑模块同时开始工作,通过延迟匹配,使得这两个延迟基本相同,数字逻辑模块的输出信号依次捕获比较器的比较结果,以此明显降低SAR结构ADC一次完整工作过程的延迟,提高SAR结构ADC的工作速度。 本发明的一种用于SAR_ADC的高速数字逻辑电路,所述电路包括并行的比较器和逻辑控制单元,以及电容阵列DAC;比较器和逻辑控制单元被时钟信号Clk同时触发;比较器输出有效比较结果Dp/Dn,逻辑控制单元输出相应的上升沿信号C<i>,通过设置延迟匹配,使得逻辑控制单元输出的上升沿信号C<i>略晚于比较器输出有效比较结果Dp/Dn,从而使得Dp/Dn被对应的上升沿信号C<i>捕获,从而建立电容阵列;i=0,1,…,N-1,N表示SAR_ADC的位数。 进一步的,所述逻辑控制单元包括或门和串联的N+1个D触发器,所述D触发器包括与门、上拉PMOS管、传输门和多个反相器;数据信号D<i>从数据输入端进入传输门并发送至第一反相器,复位信号R<i>从复位信号输入端对第一反相器输出的信号进行反向处理,经过第二反相器的数据输出端输出数据信号Q<i>;将复位信号R<i>与时钟输入端CP端的时钟信号Clk中CP<i>经过与门从第三反相器的输出。 进一步的,当复位信号输入端输入的复位信号R<i>为0时,D触发器的数据输出端Q<i>被复位为0;当复位信号输入端的复位信号R<i>为1,且时钟信号输入端的时钟信号CP<i>为1时,D触发器的数据输出端的输出数据信号Q<i>被刷新为其数据输入端的输入信号D<i>。D触发器的复位信号R<i>为0时,比较器的时钟信号CP<i>不能为1。 进一步的,所述复位信号输入端是通过内部采样控制信号Clks_in的反相信号 Clks_inn进行控制;所述内部采样控制信号Clks_in包括通过将第N+1个D触发器的输出信号和外部采样控制信号输入或门,或门的输出信号即为内部采样控制信号Clks_in。 在本发明的高速逻辑数字电路下,本发明还提出了一种用于该SAR_ADC的高速数字逻辑电路的采样调节方法,所述方法包括当N次逐次逼近过程完成后,外部采样控制信号Clks仍然为0,第N+1个D触发器产生的输出信号变为1,使得或门的输出信号变为1,从而SAR_ADC立即进入采样状态,同时,前N个D触发器被复位;当外部采样控制信号Clks由0变为1之后,第N+1个D触发器的被复位,其输出信号变为0,或门的输出信号仍然保持为1,使得SAR_ADC仍然处于采样状态,直到外部采样控制信号变为0,采样状态结束,SAR_ADC进入逐次逼近状态。 本发明的有益效果: 和传统并行SAR logic技术相比,本发明中,通过SAR logic分别输出的数字信号上升沿来捕获比较器的有效输出结果Dp/Dn;消除了传统并行数字逻辑采用数字逻辑窗口来捕获比较器有效输出结果Dp/Dn所带来的电容阵列错误建立的缺点;同时,数字信号上升沿来捕获比较器的有效输出结果Dp/Dn,和产生逻辑窗口相比,能够更适用于高速情况。 另一方面,本发明采用采样调节技术,和传统技术相比,在采用异步逻辑的情况下,可以最大程度上增加SAR_ADC的采用时间,在不引入额外复杂电路的情况下,提高了SAR_ADC的采样精度。 图1为传统SAR_ADC延迟示意图; 图2为采用并行SAR logic技术的延迟示意图; 图3为本发明所采用的并行SAR logic示意图; 图4为两种并行SAR logic结构DAC建立对比图(a)现有技术(b)本技术; 图5为本发明SAR_ADC的SAR logic原理图; 图6为本发明采用的工作时序图; 图7为三种结构逐次逼近过程平均延迟对比图; 图8为采样信号线性度对比图。 为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。 实施例1 本实施例以10位SAR结构ADC为例进行说明,即N=10;本发明所采用的并行SAR logic示意图如图3所示。比较器comp和逻辑控制单元SAR logic被信号Clk同时触发,经过一个延迟之后,比较器输出有效比较结果Dp/Dn,SAR logic输出相应的上升沿信号C<i>(i=0,1,…,9),通过设置合适的延迟,使得SAR logic输出的上升沿信号C<i>(i=0,1,…,9)稍微晚于比较器输出有效比较结果Dp/Dn,从而使得Dp/Dn被对应的上升沿信号C<i>(i=0,1,…,9)捕获。 本发明中,由于上升沿信号C<i>(i=0,1,…,9)晚于比较器输出有效比较结果Dp/Dn,从而不会造成电容阵列的错误建立,提高了电容阵列的建立精度。两种并行SAR logic结构DAC建立对比图如图4所示,传统并行SAR logic结构DAC建立图如图4(a)所示,从图4(a)中可以看出,在逻辑窗口logic window的上升沿和比较器有效比较的有效结果Dp/Dn之间,电容阵列DAC会出现一个错误的建立过程(improper settling of DAC),当比较器输出有效结果之后,电容阵列DAC开始正常建立,上述过程会降低电容阵列的建立精度或者增加DAC的建立时间。 本发明所示并行SAR logic结构DAC建立如图4(b)所示,由于SAR logic输出的上升沿信号C<i>(i=0,1,…,9)延迟时间稍大于Dp/Dn,电容阵列DAC会进行正常建立。 本发明SAR logic原理图和工作时序图分别如图5和图6所示。图5中,所述逻辑控制单元包括或门和串联的N+1个D触发器,对于D触发器DFF,D端为DFF的数据输入端,CP端的DFF的时钟输入端,R端为DFF的复位信号输入端,Q端的DFF的数据输出端。 当复位信号输入端R的输入信号为0时,DFF的数据输出端Q被复位为1。当复位端R的输入信号为1,且时钟信号输入端CP的输入信号为1时,DFF的数据输出端Q的输出数据被刷新为DFF的数据输入端D的输入信号。 其中,信号Clks为外部采样控制信号,信号Clks_in为内部采样控制信号,信号Clks_inn和Clksn分别为Clks_in和Clksn的反相信号。第11个D触发器的输出信号CO和外部采样控制信号Clks输入或门OR,或门OR的输出信号即是内部采样控制信号Clks_in。 作为一种可实现方式,如图5所示,本发明中D触发器DFF由反相器INV、与门AND、上拉PMOS管MP和传输门TN构成。数据信号D<i>从数据输入端进入传输门并发送至第一反相器,复位信号R<i>从复位信号输入端对第一反相器输出的信号进行反向处理,经过第二反相器的数据输出端输出数据信号Q<i>;将复位信号R<i>与时钟输入端CP端的时钟信号Clk中CP<i>经过与门从第三反相器的输出。 图6中,比较器和SAR logic被信号Clk同时触发,比较器的有效输出信号为Dp/Dn,SAR logic的输出信号为C<i>(i=0,1,…,9)。 通过延迟匹配,即设置电路延迟(一个比较器时钟周期的10%-20%),使得SAR logic输出信号C<i>(i=0,1,…,9)的上升沿稍晚于比较器的有效输出结果Dp/Dn,那么,比较器的有效输出结果Dp/Dn就能够被SAR logic的输出信号C<i>(i=0,1,…,9)依次捕获。 通过本方案,能够明显降低传统并行SAR logic技术中的电容阵列建立误差,提高SAR_ADC的精度。由于传统结构采用数字逻辑窗口对比较器的有效输出结果Dp/Dn进行捕获,随着SAR_ADC转换速度的不断提高,产生高速逻辑窗口的难度越来越大,通过本发明所提出的逻辑上升沿C<i>(i=0,1,…,9)对比较器的输出结果进行捕获,可以有效避免产生高速逻辑窗口所带来的设计难度。 另一方面,对于SAR_ADC而言,随着温度、电源电压和工艺角等不同参数的变化,完成逐次逼近所需要的时间有所差异,而采样过程必须在逐次逼近过程完成之后才能进行,这就使得在设计电路的时候,必须在逐次逼近过程完成之后,经过一定的时间等待,才能开始下一次采样过程呢。而在不同的温度、电源电压和工艺角情况下,等待时间是不同的,在设计中,这个等待时间必须设计为各种情况下最长的那个等待时间,从满足所有情况的要求。这就使得在某些情况下,出现了时间的浪费。 实施例2 本发明还提出了采样时间调节方法,即用于SAR_ADC的高速数字逻辑电路的采样调节方法,当10次逐次逼近过程完成后,此时外部采样控制信号Clks仍然为0,第11个D触发器产生的输出信号CO变为1,使得或门OR的输出为Clks_in变为1,从而SAR_ADC立即进入采样状态,同时,前10个D触发器被复位。当外部采样控制信号Clks由0变为1之后,第11个D触发器的被复位,其输出信号CO变为0,由于此时外部采样控制信号Clks为1,或门OR的输出信号Clks_in仍然保持为1,使得SAR_ADC仍然处于采样状态,直到外部采样控制信号Clks变为0,采样状态结束,SAR_ADC进入逐次逼近状态。 由以上描述可知,SAR_ADC总的采样时间Tsample由固定时间TClks和可变时间Tvar构成,其中TClks由外部采样控制信号Clks决定,这是一个固定值;而Tvar由内部转换时间决定,这个时间随着温度、电源电压和工艺角的变化而变化。通过本发明,可以使得在温度、电源电压和工艺角变化的情况下,逐次逼近过程一旦完成,SAR_ADC立即开始采样,和传统SAR_ADC的固定采样时间相比,最大程度延长了采样时间,提高了SAR_ADC的性能。

实施例3 为了进一步验证本发明的上述优点,在65nmCMOS工艺下,对上述结构进行了仔细的设计,电源电压取1.2V。采用上述三种结构(包括传统异步SAR logic、传统并行异步SAR logic以及本发明提出的SAR logic)分别设计一个10位100MHz采样率SAR_ADC,通过仿真结果,将上述三种结构的转换时间和采样时间进行对比。将三种结构的外部采样时间都设置为1ns,三种结构逐次逼近过程平均延迟对比图如图7所示,由图7可知,和传统异步SAR logic相比,本发明在速度上至少提升了37.5%,和并行异步SAR logic相比,由于并行异步SARlogic需要更长的延迟来恢复DAC的错误建立,本发明在速度上至少提升了17%。由于传统异步SAR logic和并行SAR logic结构的采样时间相同,所以,只对并行SAR logic结构和本发明所示SAR logic结构的采样效果进行对比。将采样时间设置为0.5ns情况下,并行SAR logic结构和本发明所示SAR logic结构的采样信号线性度对比如图8所示,由于采样时间从1ns压缩到了0.5ns,对于并行SAR logic结构而言,采样时间就只有0.5ns,而对于本发明所示SAR logic结构而言,由于图5中的可变采样时间Tvar可以增加SAR_ADC的采样时间,从而增加了SAR_ADC的采样精度。因此由图8可知,采用本技术之后,随着输入信号幅度的变化,采样所得到的信号的无杂散动态范围(SFDR)平均提高了6dB。

以上所举实施例,对本发明的目的、技术方案和优点进行了进一步的详细说明,所应理解的是,以上所举实施例仅为本发明的优选实施方式而已,并不用以限制本发明,凡在本发明的精神和原则之内对本发明所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。 A high-speed digital logic circuit for a SAR_ADC, and a sampling adjustment method. The digital logic circuit comprises: a comparator and a logic control unit operating in parallel with each other; and a capacitor array DAC. The comparator and the logic control unit are simultaneously triggered by a clock signal, such that the comparator outputs a valid comparison result Dp/Dn, and the logic control unit outputs a corresponding rising edge signal, wherein delays are matched so as to allow the rising edge signal to be outputted slightly later than the Dp/Dn outputted by the comparator, and the Dp/Dn is then captured by the corresponding rising edge signal, thereby creating a capacitor array. The circuit and the sampling adjustment method help remedy a defect in conventional parallel-mode digital logic, in which a digital logic window captures an invalid output result of the comparator, which results in an improper settling of a capacitor array. Moreover, the invention can maximize sampling times of SAR_ADCs when asynchronous logic is employed. 一种用于SAR_ADC的高速数字逻辑电路,所述电路包括并行的比较器和逻辑控制单元,以及电容阵列DAC;其特征在于,比较器和逻辑控制单元被时钟信号Clk同时触发;比较器输出有效比较结果Dp/Dn,逻辑控制单元输出相应的上升沿信号C<i>,通过设置延迟匹配,使得逻辑控制单元输出的上升沿信号C<i>略晚于比较器输出有效比较结果Dp/Dn,从而使得Dp/Dn被对应的上升沿信号C<i>捕获,从而建立电容阵列;i=0,1,…,N-1,N表示SAR_ADC的位数。 根据权利要求1所述的一种用于SAR_ADC的高速数字逻辑电路,其特征在于,所述逻辑控制单元包括或门和串联的N+1个D触发器,所述D触发器包括与门、上拉PMOS管、传输门和多个反相器;数据信号D<i>从数据输入端进入传输门并发送至第一反相器,复位信号R<i>从复位信号输入端对第一反相器输出的信号进行反向处理,经过第二反相器的数据输出端输出数据信号Q<i>;将复位信号R<i>与时钟输入端CP端的时钟信号Clk中CP<i>经过与门从第三反相器的输出。 根据权利要求2所述的一种用于SAR_ADC的高速数字逻辑电路,其特征在于,当复位信号输入端输入的复位信号R<i>和时钟信号CP<i>都为0时,D触发器的数据输出端Q<i>被复位为0;当复位信号输入端的复位信号R<i>为1,且时钟信号输入端的时钟信号CP<i>为1时,D触发器的数据输出端的输出数据信号Q<i>被刷新为其数据输入端的输入信号D<i>;D触发器的复位信号R<i>为1,时钟信号CP<i>为0时,D触发器的数据输出端Q<i>保持上一个状态的值;D触发器的复位信号R<i>为0时,比较器的时钟信号CP<i>不能为1。 根据权利要求2或3所述的一种用于SAR_ADC的高速数字逻辑电路,其特征在于,所述复位信号输入端是通过内部采样控制信号Clks_in的反相信号Clks_inn进行控制;所述内部采样控制信号Clks_in包括通过将第N+1个D触发器的输出信号和外部采样控制信号输入或门,或门的输出信号即为内部采样控制信号Clks_in。 一种用于权利要求1~4任一所述的SAR_ADC的高速数字逻辑电路的采样调节方法,其特征在于,所述方法包括当N次逐次逼近过程完成后,外部采样控制信号Clks仍然为0,第N+1个D触发器产生的输出信号变为1,使得或门的输出信号变为1,从而SAR_ADC立即进入采样状态,同时,前N个D触发器被复位;当外部采样控制信号Clks由0变为1之后,第N+1个D触发器的被复位,其输出信号变为0,或门的输出信号仍然保持为1,使得SAR_ADC仍然处于采样状态,直到外部采样控制信号变为0,采样状态结束,SAR_ADC进入逐次逼近状态。技术领域

背景技术

附图说明

具体实施方式