CIRCUIT CHIP COMPRISING A SPECIFIC CONNECTION AREA CONFIGURATION

Schaltungschip mit spezifischer Anschlußflächenanordnung Beschreibung Die vorliegende Erfindung bezieht sich allgemein auf Schaltungschips und die Anordnung von zumindest zwei Anschlußflächen auf denselben und insbesondere auf ultradünne Schaltungschips, die zum Aufbau von flachen Chipkarten oder elektronischen Etiketten geeignet sind. Durch die Entwicklung der kontaktbehafteten und der kontaktlosen Chipkarten hat sich ein völlig neuer und schnell wachsender Markt für elektronische Mikro-Systeme ergeben. Integrierte Schaltungen werden nicht mehr lediglich in Großgeräte oder auch Handsysteme eingebaut, sondern sozusagen "nackt" in Chipkarten. Am Ende dieser Entwicklung steht die sogenannte Wegwerfelektronik, deren erster Vertreter die Telephonkarte war. Eine Wegwerfelektronik erfordert preisgünstige Chips bzw. Mikromodule in ökologisch akzeptablen Trägern. Darüberhinaus sind zunehmend flachere Module erforderlich, insbesondere im Falle elektronischer Etiketten, bei denen ein kontaktloses Modul, das aus einer integrierten Schaltung, d.h. einem Schaltungschip, und einer Antennenspule besteht, zwischen zwei Papieren eingebettet wird. Ein solches elektronisches Etikett setzt eine besonders flache Bauform des kontaktlosen Moduls mit einem möglichst geringen Dickenauftrag voraus, um papiertechnische Vorgänge, wie z.B. Bedrucken, Laminieren, usw., nicht zu beeinträchtigen. Neben Papieren können zur Herstellung elektronischer Etiketten auch andere dünne, flexible Substrate, wie z.B. Polymerfolien, verwendet werden. Der Anwendungsbereich für elektronische Etiketten reicht von der Warenkennzeichnung über Tickets bis hin zu Sicherheitspapieren und darüberhinaus bis in die Domäne der heutigen Chipkarten.

An die Kontaktierungstechnologie für solche dünnen Chips ist eine Reihe von speziellen Anforderungen zu stellen. Diese beziehen sich auf einen geringen Preis, einen geringen Materialeinsatz, eine leichte Kontaktierbarkeit und vor allem eine geringe Bauhöhe. Letztere ist essentiell, wenn alle Vorteile der Dünnchip-Technologie genutzt werden sollen. Im Gegensatz zu Einzel- und vor allem auch Leistungs-Bauelementen werden integrierte Schaltungen in aller Regel durch planar in einer Ebene, nämlich der Nutzoberfläche des Halbleiters liegende Kontakte, mit der peripheren Beschaltung verbunden. Diese periphere Beschaltung ist im einfachsten Fall durch die Kontaktstifte eines Gehäuses gebildet. Im Falle von speziellen Montagetechniken, beispielsweise der Chip-On-Board-Technologie, ist diese periphere Beschaltung beispielsweise durch Leiterbahnen auf einem Substrat, das im wesentlichen einer üblichen kupferkaschierten Leiterplatte entspricht, gebildet. Hinsichtlich derzeit gängiger Kontak- tierungstechniken sei beispielsweise auf den Artikel "Packa- ging-Trends: High-Tech im Kleinstformat" H. Reichl u. a., Bauelemente, IC-Packaging, Elektronik 12/1998, verwiesen. Beschrieben werden dort insbesondere Flip-Chip-Bondtechniken, bei denen die Montage des Chips und die Kontaktierung gleichzeitig erfolgt. Ferner ist dort die Möglichkeit einer Dünnfilmverdrahtung beschrieben. Die Verwendung eines derartigen Flip-Chip-Verfahrens für kontaktlose Chipkarten ist auch in der DE-A-19639902 beschrieben. In der DE-C-4430812 ist ein Verfahren zum Herstellen eines ionensensitiven Feldeffekttransistors mit einem Rückseitenkontakt beschrieben. Dort ist ein Verfahren beschrieben, um frei wählbare vertikale Kontakte zwischen der Bauelementebene und der Rückseitenmetallisierung zu realisieren. Die Kontaktierung der Bauelementebene erfolgt dann ausschließlich von der Rückseite her, so daß sich die Metallisierung lediglich auf der von der Probenflüssigkeit entfernten Seite befindet, wodurch die Kurzschlußsicherheit erhöht wird.

Sämtliche bekannte Kontaktierungsverfahren sind bei der Fertigung ultraflacher Chipkartenmodule oder elektronischer Etiketten nachteilig, da zum einen exakte Justageverfahren erforderlich sind, und zum anderen die erzeugten Kontaktierungen eine weitere Verringerung der Dicke von derartigen Modulen verhindern. Die planare Kontaktanordnung herkömmlicher integrierter Schaltungen ist in deren planartechnischer Herstellung begründet. Diese beruht auf dem einseitigen Zugriff auf die Oberfläche und deren Strukturierung mittels lithographischer Verfahren. Übliche integrierte Schaltungen weisen in aller Regel von einigen 10 bei Speichern bis zu mehreren 100 Anschlüssen bei komplexen Logikbausteinen auf, die als sogenannte Anschluß-Pads meist am Rande der integrierten Schaltungen angeordnet sind. Typische Anschlußflächenabmessungen liegen im Bereich von 70 μm, um die Anforderungen an die Justiergenauigkeit bei einem Testen und bei der Kontaktierung in erträglichen Grenzen zu halten. Bei für eine Wegwerfelektronik geeigneten Schaltungschips stellen sich weitgehend andere Anforderungen. Beispielsweise besitzen integrierte Schaltungen für Transpondermodule als einzige periphere Beschaltung eine großflächige Induktivität, d.h. eine Antennenspule und/oder eine Kapazität, d.h. einen Dipol. Die Dicke dieser externen Anschlußelemente liegt typischerweise bei einigen Mikrometern. Mittels der externen Anschlußelemente bezieht die integrierte Schaltung ihre Betriebsenergie aus einem externen Hochfrequenzfeld und tauscht Daten mit diesem Hochfrequenzfeld aus. Im einfachsten Fall erfolgt dieser Datenaustausch durch eine Daten- speicher-programmierte Dämpfung des Antennenkreises. Der Antennenkreis bildet zusammen mit einem integrierten Kondensator und einem Widerstand, der durch einen Transistor, der öffnet und schließt und damit den Schwingkreis dämpft, einen Resonanzkreis. Folglich benötigt eine solche integrierte Schaltung für einen Einsatz in einem Transpondermodul lediglich zwei externe Anschlüsse. Hierbei stellen sich kaum

Probleme hinsichtlich einer Erwärmung, da die in der integrierten Schaltung umgesetzte Energie dem Strahlungsfeld des Schreib-Lesegeräts entstammt, entsprechend dem Raumwinkel relativ gering ist und zudem nur über kurze Zeit anliegt. Seit langem wird die Rückseite herkömmlicher Schaltungschips mit metallischen Belägen versehen, um zum einen definierte Potentialverhältnisse und einen Ohmschen Kontakt zu erreichen, und um zu anderen diverse Lötverfahren einsetzen zu können. Für diese Metallisierung kommt eine Vielzahl von Metallen in Frage, die nach ihren Eigenschaften ausgewählt und kombiniert werden. Diese Eigenschaften sind beispielsweise die Bildung eines niedrigschmelzenden Eutektikums, das Legierungsverhalten, das Benetzungsverhalten, das Korrosionsverhalten, das Verhalten als Diffusionsbarriere sowie die mechanische Belastbarkeit. Typische bekannte Schichtaufbauten bestehen aus Kombinationen von Ti, TiN, W, Ni, AI, Au, Cr. Überdies besteht die übliche Funktion eines Rückseitenkontakts bei konventionell gehäusten Chips darin, eine mechanisch und vor allem auch thermisch gut leitende Verbindung mit dem Gehäuse herzustellen. Die Aufgabe der vorliegenden Erfindung besteht darin, einen Schaltungschip mit einer spezifischen Anschlußflächenanordnung zu schaffen, der die einfache und kostengünstige Fertigung ultraflacher Chipkarten oder elektronischer Etiketten ermöglicht. Diese Aufgabe wird durch einen Schaltungschip gemäß Anspruch 1 gelöst. Die vorliegende Erfindung schafft einen Schaltungschip, der aus einem halbleitenden Substrat mit einer Vorderseite und einer Rückseite besteht, wobei in der Vorderseite des halbleitenden Substrats eine integrierte Schaltung mit einer

Mehrzahl von Bauelementen definiert ist. Die integrierte Schaltung besitzt zwei zur Signaleinkopplung oder Signalauskopplung dienende und ohne Beeinträchtigung der Funktion der integrierten Schaltung vertauschbare Anschlüsse. Der Schaltungschip weist lediglich zwei Anschlußflächen auf, von denen eine auf der Vorderseite des halbleitenden Substrats und eine auf der Rückseite desselben angeordnet ist, wobei jede der Anschlußflächen mit einem der vertauschbaren Anschlüsse verbunden ist. Gemäß der vorliegenden Erfindung weist die integrierte Schaltung zwei zur Signaleinkopplung oder Signalauskopplung dienende und ohne Beeinträchtigung der Funktion der integrierten Schaltung vertauschbare Anschlüsse auf, wobei einer derselben mit der auf der Vorderseite angeordneten Anschlußfläche verbunden ist, während der andere derselben mit der auf der Rückseite angeordneten Anschlußfläche verbunden ist. Die beiden Anschlußflächen sind somit als elektrisch gleichwertig anzusehen. Bei der Verwendung des erfindungsgemäßen Schaltungschips für ein Transpondermodul besitzt derselbe somit lediglich zwei Anschlußflächen, von denen einer auf der Vorderseite angeordnet ist und dieselbe im wesentlichen bedeckt, während der andere auf der Rückseite angeordnet ist und dieselbe im wesentlichen bedeckt. Wie oben angegeben, werden die metallischen Kontakte vorzugsweise großflächig ausgeführt, wobei sie maximal die gesamte Chipfläche einnehmen. Dadurch ergibt sich eine sehr einfache und damit unpräzise Justage und Kontaktierung mit geringem Übergangswiderstand. Ein geringer Übergangswiderstand ist erforderlich, um die im Resonanzfall relativ hohen Ströme im Schwingkreis zu leiten. Diese bestimmen die Spulengüte, die im Sinne einer engbandigen Resonanz möglichst hoch sein sollte. Die erfindungsgemäße Anordnung der Anschlußflächen ermöglicht beispielsweise beim Einsatz des Schaltungschips in einem Transpondermodul eine möglichst flache Verbindung der

Anschlußflächen mit den peripheren Komponenten, wobei, wie oben angegeben, bei einem Transpondermodul im Regelfall zwei Anschlüsse genügen, um sowohl die Energieversorgung als auch den bidirektionalen Datenfluß sicherzustellen. Somit ist ein extrem flaches Transpondermodul mit einer Gesamtdicke im Bereich von 10 μm realisierbar. Dadurch ist der Einbau in oder zwischen dünne Substrate möglich. Insbesondere ermöglicht der erfindungsgemäße Aufbau des Schaltungschips ein sehr massearmes Mikromodul, was eine Rolle bei den Materialkosten und insbesondere bei der Entsorgung im Falle einer Wegwerfelektronik spielt. Bei der geringen Dicke des Schaltungschips, typischerweise im Bereich von 10 μm, kann ein Kontakt durch eine Anzahl von Verfahren auf die Rückseite des Schaltungschips geführt werden. Überdies liefert das Vorsehen einer Anschlußfläche auf der Vorderseite und einer Anschlußfläche auf der Rückseite des Schaltungschips eine Maximie- rung der durch die Anschlußflächen besetzten Fläche, so daß der Bondprozeß sowohl vereinfacht als auch beschleunigt durchgeführt werden kann. Bei bevorzugten Ausführungsbeispielen der vorliegenden Erfindung werden die beiden Kontakte elektrisch gleichwertig ausgebildet, so daß die Einbau-Orientierung hinsichtlich der Ausrichtung der Oberseite bzw. der Unterseite beliebig ist. Weiterhin können großflächige Metallisierungen auf der Vorderseite bzw. der Rückseite weitere Aufgaben übernehmen, beispielsweise als Lichtschutz, als Abschirmung, als Potentialausgleich, als Korrosionsschutz, als Ansatzfläche für eine magnetische oder elektrostatische Handhabung, usw.. Überdies wird durch die auf unterschiedlichen Hauptoberflächen liegenden Anschlußflächen die Gefahr von Kurzschlüssen durch ineinander fließende Leitkleber und dergleichen beseitigt. Somit eignet sich der erfindungsgemäße Schaltungschip insbesondere zum Einbau in ein Isolationssubstrat, derart, daß beide Hauptoberflächen des Chips im wesentlichen bündig mit

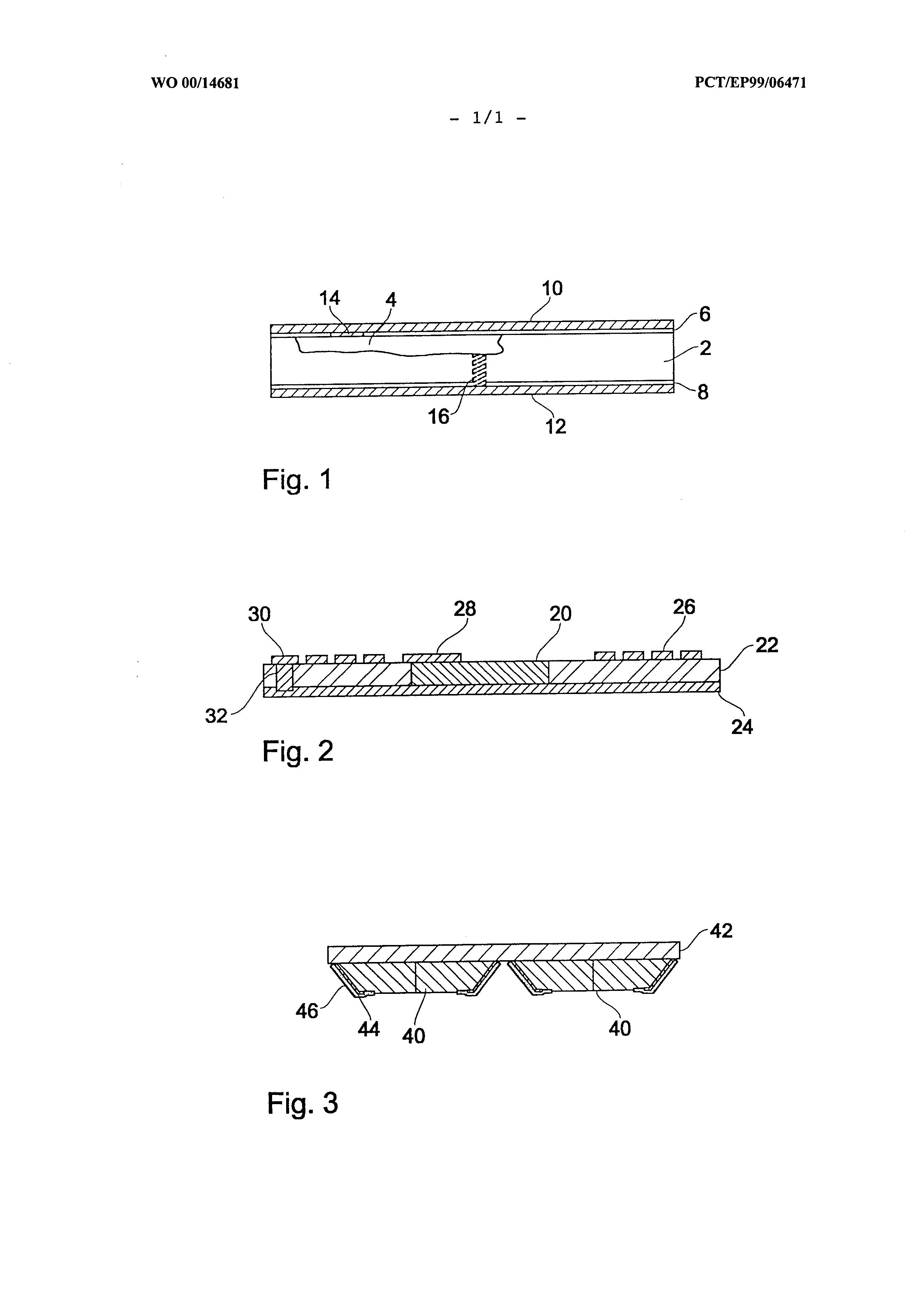

den Hauptoberflächen des Isolationssubstrats sind. Vorzugsweise kann auf der Unterseite des Isolationssubstrats eine ganzflächige Metallisierung vorgesehen sein, wodurch eine Kontaktierung des auf der Unterseite des Schaltungschips vorgesehenen Anschlußfläche realisiert wird. Die Kontaktierung der auf der Oberseite des Schaltungschips angeordneten Anschlußfläche kann mittels einer strukturierten Metallisierung, die auf diese Oberfläche des Isolationssubstrates und des Schaltungschips aufgebracht wird, erfolgen. Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend bezugnehmend auf die beiliegenden Zeichnungen näher erläutert. Es zeigen: Fig. 1 schematisch eine Querschnittansicht eines erfindungsgemäßen Schaltungschips; Fig. 2 eine schematische Querschnittansicht eines Trans- pondermoduls , das einen erfindungsgemäßen Schaltungschip enthält; und Fig. 3 eine schematische Darstellung zur Veranschaulichung, wie eine Metallisierung auf die Rückseite des Schaltungschips geführt werden kann. In Fig. 1 ist schematisch ein einfaches Ausführungsbeispiel eines erfindungsgemäßen Schaltungschips dargestellt. In der Nutzseite eines halbleitenden Substrats 2 ist eine integrierte Schaltung 4 mit einer Mehrzahl von Bauelementen gebildet. Das halbleitende Substrat 2 weist beispielsweise eine Dicke von 10 μm auf. Auf die Oberseite und der Unterseite des halbleitenden Substrats 2 sind jeweils dünne Passivie- rungsschichten 6 und 8 aufgebracht. Auf diesen Passivie- rungsschichten 6 und 8 ist jeweils eine Metallschicht 10 und 12 einer Dicke von typischerweise 0,5 μm vorgesehen. Die Metallschicht 10 ist über eine leitfähige Verbindung 14 mit der integrierten Schaltung in dem halbleitenden Substrat 2 verbunden. Ebenso ist die Metallschicht 12 auf eine belie-

bige geeignete Art und Weise mit der integrierten Schaltung 4 verbunden, wie schematisch durch eine gestrichelt dargestellte Verbindung 16 gezeigt ist. Die Metallschichten 10 und 12 sind vorzugsweise mit zwei zur Signaleinkopplung oder Signalauskopplung dienenden Anschlüssen der integrierten Schaltung verbunden, die ohne Beeinträchtigung der integrierten Schaltung vertauschbar sind, so daß der Schaltungschip in einer beliebigen Ausrichtung mittels der Anschlußflächen 10 und 12 extern kontaktiert werden kann. Die Pas- sivierungsschichten 6 und 8 dienen zur Isolation des Halbleitersubstrats 2 von den Anschlußflächen, die durch die Metallschichten 10 und 12 gebildet sind. Dabei ist anzumerken, daß die Passivierungsschicht 8 nicht notwendigerweise vorhanden ist, wie nachfolgend ausführlicher erläutert wird. Die Metallschichten 10 und 12 können aus einem beliebigen Metall nach Vorgabe der Halbleitertechnik bestehen und mittels der dort verwendeten Verfahren hergestellt werden. Beispielhafte Metalle sind AI, W, Cr, Ti, TiN, Cu oder Au, sowie Legierungen und Korabinationen derselben. Die in Fig. 1 schematisch bei 16 dargestellte leitfähige Verbindung kann auf unterschiedliche Arten realisiert sein. Beispielsweise kann dieselbe durch eine Durchkontaktierung bis zu einem geeignet dotieren Bereich der integrierten Schaltung implementiert sein. Alternativ kann diese leitfähige Verbindung über auf zumindest einer Seitenfläche des halbleitenden Substrats 2 vorgesehene leitfähige Strukturen realisiert sein, wobei dann auf der Nutzseite des Halbleitersubstrats zwei mehrlagige Metallisierungen vorgesehen sein können, die zur Verbindung der auf der Seitenfläche des Halbleitersubstrats vorgesehenen leitfähigen Strukturen mit einem entsprechenden Anschlußbereich der integrierten Schaltung dienen. Eine Durchkontaktierung zur leitfähigen Verbindung der Metallschicht 12 kann ebenfalls bis zu einer Metallisierungsebene einer Mehrzahl von Metallisierungsebenen auf der Nutz-

seite des halbleitenden Substrats 2 durchgeführt werden. Dazu wird oder werden zunächst ein oder mehrere Kontaktlöcher geätzt, deren Tiefe der späteren Chipdicke entspricht. Soll eine galvanische Trennung zwischen dem halbleitenden Substrat 2 und der Rückseitenmetallisierung 12 erfolgen, wird nachfolgend Plasmaoxid isotrop in dem Kontaktloch zur seitlichen Isolation abgeschieden. Dieses Oxid wird nachfolgend am Boden des Lochs anisotrop geätzt, woraufhin das Loch mit einem Metall aufgefüllt wird, vorzugsweise Wolfram. Im Anschluß daran wird das halbleitende Substrat vorzugsweise noch im Waferverbund gedünnt, bis das halbleitende Substrat die gewünschte Dicke hat und der Kontaktstift freigelegt ist. Im Anschluß daran wird die Rückseite mit einem der oben genannten Metalle metallisiert. Dieses Verfahren ist speziell für extrem dünne Chips geeignet, während sich dicke Chips aufgrund des begrenzten, ätztechnisch zu erreichenden Aspektverhältnisses für dieses Verfahren weniger eignen. Eine weitere Möglichkeit besteht darin, vollständig auf eine zusätzliche galvanische Trennung zwischen der Rückseitenmetallisierung 12 und dem halbleitenden Substrat 2 zu verzichten. In diesem Fall ist die Passivierungsschicht 8 auf der Rückseite des halbleitenden Substrats 2 überflüssig. Somit ist die Rückseitenmetallisierung 12 direkt mit dem Substrat verbunden, wobei darauf geachtet werden muß, das ein ausreichend guter Ohmscher Kontakt zwischen der Metallisierungsschicht 12 und dem halbleitenden Substrat hergestellt wird. Um einen solchen guten Ohmschen Kontakt zu realisieren muß eine Prozessierung an dünnen und mechanisch nicht mehr frei handhabbaren Wafern erfolgen, wobei diese Prozessierung möglicherweise Temperaturschritte bis zu 450°C implizieren kann, die von dünnen Wafern und insbesondere den darin enthaltenen Bauelementen nicht ohne weiteres toleriert werden. Als Verfahren zur Erzielung guter Ohmscher Kontakte auf der Rückseite gedünnter Wafer kommen eine Ionenimplantation verbunden mit einem Kurzzeit-Ausheilverfahren (RTP (RTP = rapid thermal processing), z.B. per Laser) in Frage. Derartige mehr oder weniger transiente Verfahren können auch an einem,

etwa mittels organischen Klebern auf einem Handlingwafer befestigten Dünnchip-Wafer vorteilhaft angewandt werden. Nach dieser Prozessierung wird dann die Rückseitenmetallisierung aufgebracht. Ist, wie oben beschrieben, die Rückseitenmetallisierung 12 direkt mit dem halbleitenden Substrat 2 verbunden, muß selbstverständlich eine geeignete Isolierung des Halbleitersubstrats 2 von der integrierten Schaltung 4 gegeben sein. Eine solche Isolierung kann zweckmäßigerweise durch sperrende Diodenstrecken zu den üblicherweise verwendeten CMOS-Wan- nen der integrierten Schaltung realisiert werden. Alternativ könnte eine leitfähige Verbindung der Rückseitenmetallisierung 12 zu der integrierten Schaltung 4 durch das Vorsehen geeignet dotierter leitfähiger Bereiche realisiert werden. In Fig. 2 ist ein Transpondermodul dargestellt, das einen erfindungsgemäßen Schaltungschip enthält. Der Schaltungschip 20 ist dabei in eine Ausnehmung eines Isolationssubstrats 22 derart eingebracht, daß beide Hauptoberflächen des Schaltungschips 20 im wesentlichen bündig zu den Hauptoberflächen des Isolationssubstrats 22 sind. Auf der Rückseite des Isolationssubstrats 22 ist vorzugsweise ganzflächig eine Metallisierungsschicht 24 vorgesehen. Auf der Vorderseite des Isolationssubstrats 22 sowie auf Teilen des Schaltungschips 20 ist eine strukturierte Metallisierung 26 vorgesehen, die eine Antenneneinrichtung in der Form einer Spule definiert. Ein Anschlußende 28 der Spule ist leitfähig mit dem Vorderseitenkontakt (in Fig. 2 nicht dargestellt) des Schaltungschips 20 verbunden. Ein zweites Anschlußende 30 der strukturierten Metallisierung 26 ist über eine Durchkontaktierung 32 durch das Isolationssubstrat 22 mit der auf der Rückseite des Isolationssubstrats 22 vorgesehenen Metallisierungsschicht 24 verbunden. Die Metallisierungsschicht 24 kontaktiert die Rückseitenanschlußflache (in Fig. 2 nicht dargestellt) des Schaltungschips 20, so daß diese Rückseitenan-

schlußfläche über die Metallisierungsschicht 24 sowie die Durchkontaktierung 32 mit dem zweiten Anschlußende 30 der strukturierten Metallisierungsschicht verbunden ist. Es ist somit offensichtlich, daß der Schaltungschip gemäß der vorliegenden Erfindung eine überaus einfache Kontaktierung ermöglicht und überdies die Erstellung eines flachen Transpon- dermoduls einer Dicke zwischen 10 und 50 μm, möglicherweise darunter bis zu 5 μm, ermöglicht. Die Kontaktierung zwischen dem Anschlußende 28 der strukturierten Metallisierung 26 und die Kontaktierung zwischen der Metallisierungsschicht 24 und dem Schaltungschip 20 können mittels beliebiger bekannter Kontaktierungsverfahren durchgeführt werden. Fig. 3 zeigt eine schematische Darstellung, wie bei der Herstellung der Schaltungschips bereits eine leitfähige Struktur auf den Rändern eines Schaltungschips durchgeführt werden kann, um eine leitfähige Verbindung zur Rückseite herzustellen. In Fig. 3 sind zwei Halbleiterchips 40 dargestellt, die auf einen Hilfsträger 42 aufgebracht sind. Die integrierten Schaltungen sind dabei bei den in Fig. 3 gezeigten Chips 40 in den oberen Bereichen derselben gebildet. Die Vereinzelung der Chips erfolgt mittels eines anisotropen KOH-Ätzens, wodurch die dargestellten 54-Grad-Kanten bewirkt werden. Auf diese abgeschrägten Kanten kann nun vorteilhaft optional zunächst eine Isolation 44 und nachfolgend eine Metallisierung 46 aufgebracht werden, um die angesprochene leitfähige Verbindung zur Rückseite des Schaltungschips herzustellen. Ein Transpondermodul, wie es beispielsweise in Fig. 2 dargestellt ist, kann beispielsweise folgende Kenngrößen besitzen: Frequenz 13 MHz, L = 4 nH, C = 30 pF, Schwingkreisgüte > 20. Die Spulenfläche kann ca. 2 bis 100 Quadratzentimeter betragen. Wie bereits ausgeführt wurde, soll die Dicke des Moduls in einem Bereich von 10 μm liegen. Diese geringe Dicke ermöglicht ausreichend geringe Widerstandswerte auch bei den in der CMOS-Technik üblichen Substratdotierungen von 1014 cm-3, was zu einem spezifischen Widerstand von 1 bis 10

Ohmcm führt. Dieser Serienwiderstand des Substrats geht bei einer direkten Kontaktierung der Rückseitenanschlußflache durch dasselbe in den Schwingkreiswiderstand ein und muß möglichst niedrig sein, um eine ausreichende Spulengüte zu gewährleisten. Der Schaltungschip gemäß der vorliegenden Erfindung weist ein halbleitendes Substrat aus, das vorzugsweise aus monokristallinem oder polykristallinem Silizium besteht. Jedoch kann das halbleitende Substrat auch durch andere Halbleiter bzw. Verbindungshalbleiter, z.B. Galliumarsenid, gebildet sein. Ferner kann das halbleitende Substrat durch halbleitende Polymere realisiert sein.

Patentansprüche Schaltungschip aus einem halbleitenden Substrat (2) mit einer Vorderseite und einer Rückseite, wobei in der Vorderseite des halbleitenden Substrats (2) eine integrierte Schaltung (4) mit einer Mehrzahl von Bauelementen definiert ist, wobei die integrierte Schaltung (4) zwei zur Signaleinkopplung oder Signalauskopplung dienende und ohne Beeinträchtigung der Funktion der integrierten Schaltung (4) vertauschbare Anschlüsse aufweist, wobei der Schaltungschip lediglich zwei Anschlußflächen (10, 12) aufweist, von denen eine (10) auf der Vorderseite des halbleitenden Substrats (2) und eine (12) auf der Rückseite desselben angeordnet ist, wobei jede der Anschlußflächen mit einem der vertauschbaren Anschlüsse verbunden ist. Schaltungschip nach Anspruch 1, bei dem die Anschlußflächen (10, 12) jeweils großflächig, die Vorderseite und die Rückseite im wesentlichen bedeckend, angeordnet sind. Schaltungschip gemäß Anspruch 1 oder 2, bei dem die zumindest eine Anschlußfläche (12) auf der Rückseite über eine Durchkontaktierung durch den Schaltungschip mit einem Anschluß der integrierten Schaltung verbunden ist. Schaltungschip gemäß Anspruch 1 oder 2, bei dem die Anschlußfläche (12) auf der Rückseite über auf zumindest einer Seitenfläche des halbleitenden Substrats (2) vorgesehene leitfähige Strukturen mit einem Anschluß der integrierten Schaltung (4) verbunden ist.

5. Schaltungschip gemäß Anspruch 1 oder 2, bei dem die Anschlußfläche (12) auf der Rückseite direkt mit dem Substrat leitfähig verbunden ist. 6. Schaltungschip gemäß einem der Ansprüche 1 bis 5, bei dem die Anschlußflächen aus einer Metallschicht bestehen, die aus AI, W, Cr, Ti, TiN, Cu, Ni, Au oder Legierungen derselben gebildet ist. 7. Schaltungschip gemäß einem der Ansprüche 1 bis 6, bei dem das halbleitenden Substrat (2) ein ultradünnes Halbleitersubstrat mit einer Dicke von weniger als 50 μm ist.