SOLID-STATE IMAGING ELEMENT AND ELECTRONIC DEVICE

本技術は、固体撮像素子、および電子装置に関し、特に、フォトダイオードからのオーバーフローを安定的に行うことができるようにした固体撮像素子、および電子装置に関する。

デジタルスチルカメラやデジタルビデオカメラなどに搭載する固体撮像素子としてCMOS(Complementary Metal Oxide Semiconductor)イメージセンサが知られている。CMOSイメージセンサ(以下、CISと称する)においては、画素毎に形成されているPD(Photodiode)による光電変換によって入射光に応じた電荷が発生され、発生された電荷が転送トランジスタを介してFD(Floating Diffusion)に転送され、FDにおいて電荷が電気信号(画素信号)に変換されて読み出される。

また、従来、CISのQs(飽和電荷量)を向上させたり、縦方向に複数のPDを積層させた縦方向分光CISを形成したりすることなどを目的として、PDをSi(シリコン)基板の深部(裏面側)に形成する構成が提案されている。PDにて発生、蓄積された電荷の読み出しは、例えば、Si基板に対して垂直方向(縦方向)に設けられた縦型トランジスタを介してSi基板の表面側に設けられたFDに転送される。

上述したような構成の場合、PDとFDの距離が長く、また、PDにて電荷蓄積中は縦型トランジスタが低電圧に固定されているので、オーバーフローの設計が困難である。そのため、Si基板の裏面側にオーバーフロードレイン(以下、OFDと称する)を設ける構造が提案されている(例えば、特許文献1)。

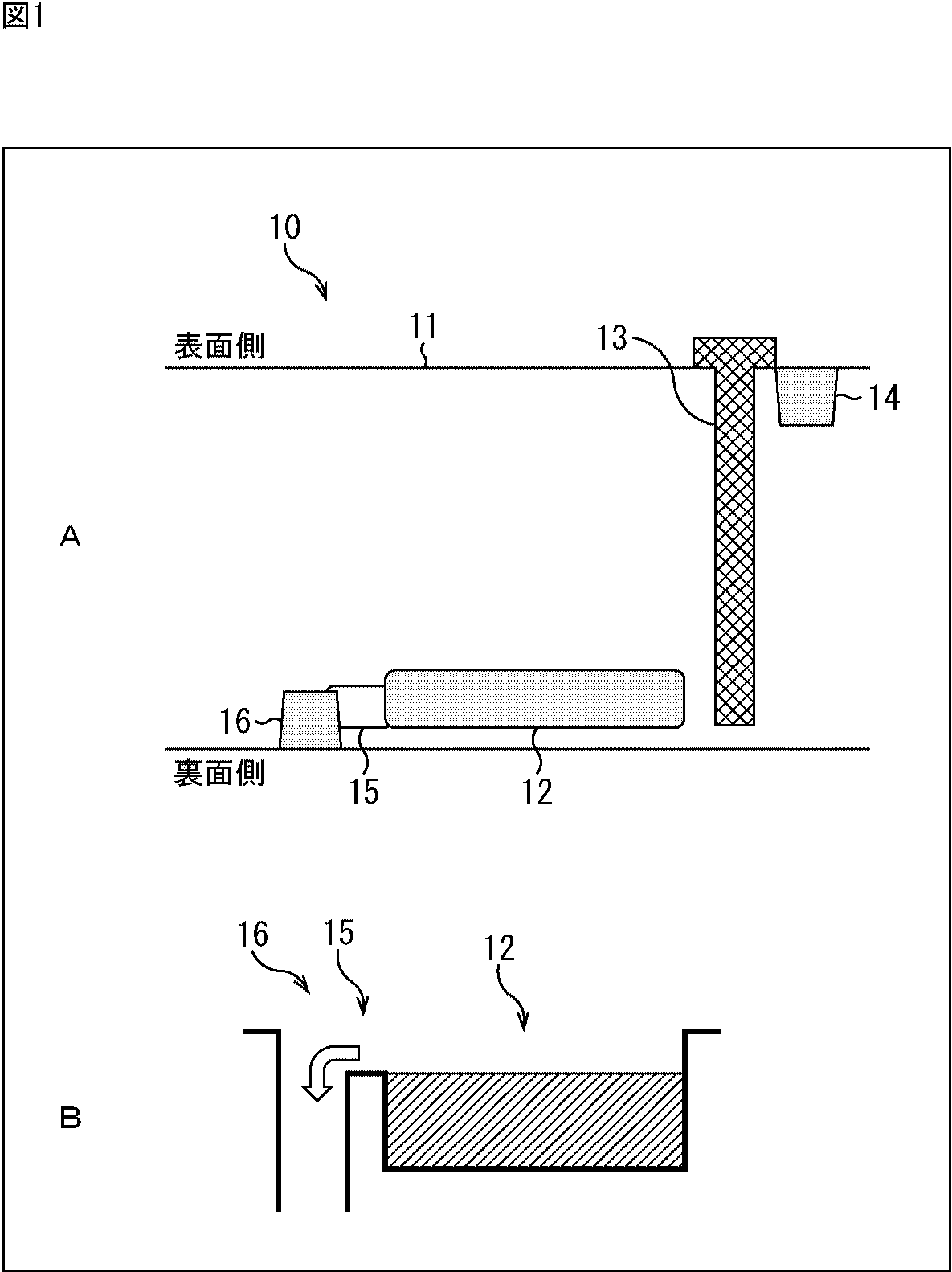

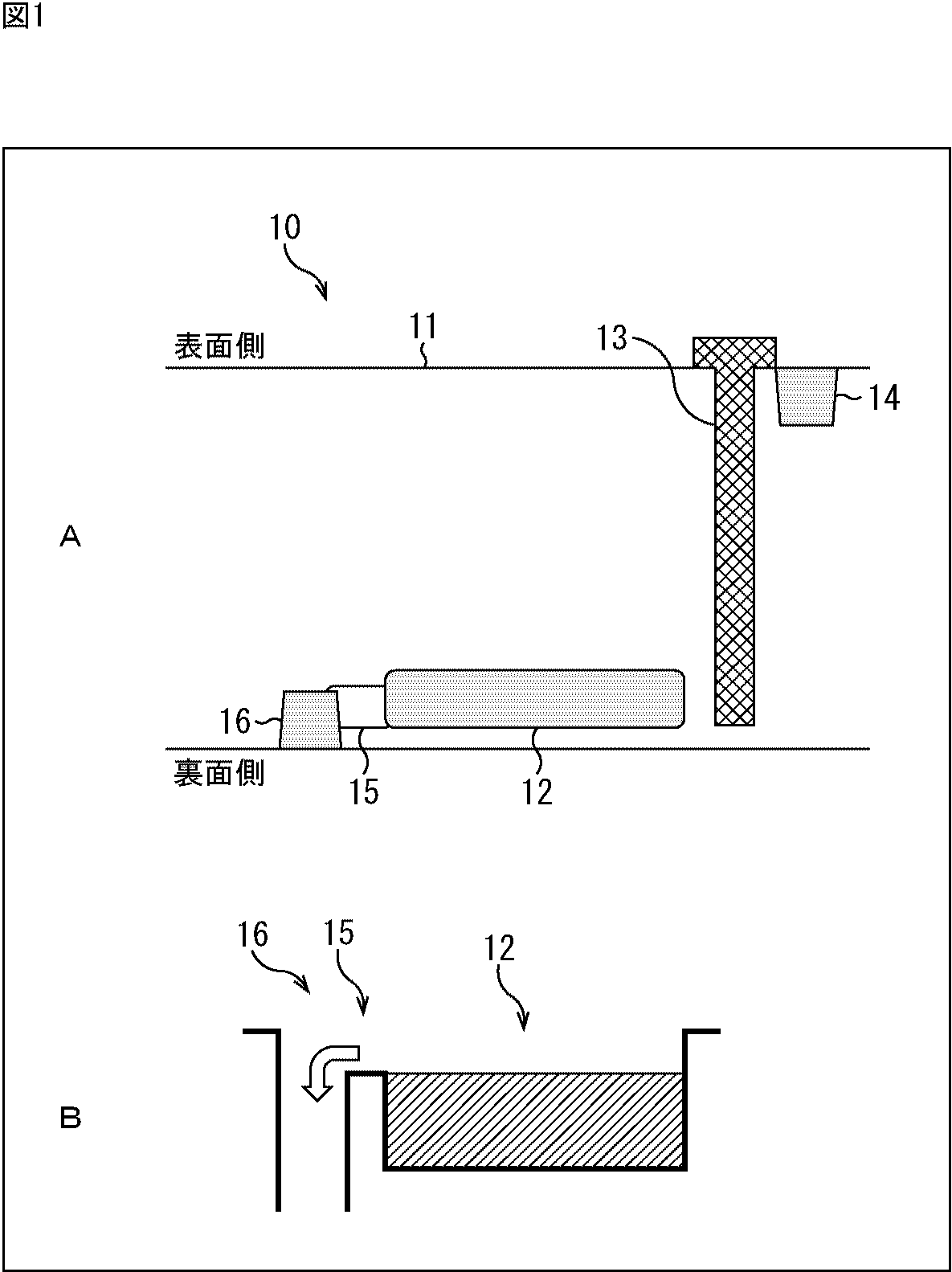

図1は、Si基板の裏面側にPDとOFDを設けたCMOSイメージセンサの構成の一例を示している。なお、同図Aは断面図、同図Bは該CISの各部のポテンシャルを示している。

このCIS10は、Si基板11の裏面側(深部)にPD12が形成され、表面側にFD14が形成されている。また、Si基板11に対して垂直方向(縦方向)に縦型トランジスタ13が形成されている。さらに、Si基板11の裏面側(深部)には、電位障壁部15を介してPD12に繋がるOFD16が形成されている。OFD16は電源電圧に設定される、高濃度の拡散層からなる。

PD12、電位障壁部15、およびOFD16のポテンシャルの高さは同図Bに示される通りであり、PD12にて発生、蓄積された電荷が飽和した場合、飽和した電荷は電位障壁部15を超えてOFD16に排出されることになる。

図1のAに示された構成の場合、PD12、電位障壁部15、およびOFD16のポテンシャルの高さは理論的には図1のBに示されたものとなる。しかしながら、OFD16が高濃度の拡散層であり、OFD16と電位障壁部15の距離が近いことから、PD12、電位障壁部15、およびOFD16を形成するに際し、これらの配置がずれたり、それぞれの不純物濃度がばらついたりすると、電位障壁部15のポテンシャルの高さが大きく変化し易くなる。その場合、Qsが低下したり、隣接画素との混色が発生したりすることが起こり得る。

本技術は、このような状況に鑑みてなされたものであり、PDからのオーバーフローを安定的に行えるようにして、Qsの低下や混色の発生を抑止できるようにするものである。

本技術の第1の側面である固体撮像素子は、入射光に応じて電荷を発生、保持する電荷保持部と、前記電荷保持部で飽和した前記電荷が排出されるOFD部と、前記電荷保持部から前記OFD部に流れ出る前記電荷の障壁となる電位障壁部とを半導体基板内の受光面側に備え、前記OFD部は、同じ型の不純物の濃度が異なる低濃度OFD部および高濃度OFD部から成り、前記高濃度OFD部と前記電位障壁部は、間隔を開けて形成されている。

前記電荷保持部と前記低濃度OFD部とは、同じ型の不純物の濃度が等しいようにすることができる。

本技術の第1の側面である固体撮像素子は、前記半導体基板の前記受光面とは反対の面から形成され、前記高濃度OFD部に接する第1の縦型トランジスタをさらに備えることができる。

前記第1の縦型トランジスタと前記電位障壁部は、間隔を開けて形成されているようにすることができる。

本技術の第1の側面である固体撮像素子は、前記半導体基板に形成される画素トランジスタと前記電荷保持部との間に、前記第1の縦型トランジスタから横方向に延伸されているドレイン層をさらに備えることができる。

前記ドレイン層は、前記電荷保持部と同じ型の不純物の拡散層から形成されているようにすることができる。

本技術の第1の側面である固体撮像素子は、前記半導体基板のウェル領域のうち、所定の画素トランジスタの下部領域と、その他の領域とを電気的に分離する、前記第1の縦型トランジスタから横方向に延伸されているウェル分離層をさらに備えることができる。

前記ウェル分離層によって電気的に分離された、前記所定の画素トランジスタの前記下部領域の電位は、前記その他の領域の電位よりも低くすることができる。

前記所定の画素トランジスタは、AMPトランジスタおよびSELトランジスタとすることができる。

前記所定の画素トランジスタとしての前記AMPトランジスタの入力電圧となるRST電位は、前記AMPトランジスタのドレイン電圧よりも低くすることができる。

前記所定の画素トランジスタは、RSTトランジスタとすることができる。

本技術の第1の側面である固体撮像素子は、前記半導体基板の前記受光面とは反対の面から形成され、前記電荷保持部から前記電荷を読み出す第2の縦型トランジスタをさらに備えることができる。

前記高濃度OFD部には、前記電荷保持部に電荷が蓄積したときに前記電荷保持部に生じる電圧よりも高い電圧が印可されているようにすることができる。

前記高濃度OFD部には、前記半導体基板の前記受光面とは反対の面から前記半導体基板を貫く貫通電極を介して供給される、前記電荷保持部に電荷が蓄積したときに前記電荷保持部に生じる電圧よりも高い電圧が印可されているようにすることができる。

前記貫通電極は、複数の画素毎に設けられ、前記複数の画素により共有されるようにすることができる。

本技術の第1の側面である固体撮像素子は、前記電位障壁部のポテンシャルを制御する制御部をさらに備えることができる。

前記高濃度OFD部は、前記複数の画素により共有されるようにすることができる。

前記電荷保持部は、前記半導体基板内に複数層積層されているようにすることができる。

本技術の第1の側面である固体撮像素子は、前記半導体基板の前記受光面の外側に形成された光電変換膜をさらに備えることができる。

本技術の第2の側面である電子装置は、固体撮像素子が搭載された電子装置において、前記固体撮像素子は、入射光に応じて電荷を発生、保持する電荷保持部と、前記電荷保持部で飽和した前記電荷が排出されるOFD部と、前記電荷保持部から前記OFD部に流れ出る前記電荷の障壁となる電位障壁部とを半導体基板内の受光面側に備え、前記OFD部は、同じ型の不純物の濃度が異なる低濃度OFD部および高濃度OFD部から成り、前記高濃度OFD部と前記電位障壁部は、間隔を開けて形成されている。

本技術の第1の側面によれば、電荷保持部からのオーバーフローを安定的に行い、Qsの低下や混色の発生を抑止することが可能となる。

本技術の第2の側面によれば、固体撮像素子のQsの低下や混色の発生を抑止することが可能となる。

以下、本技術を実施するための最良の形態(以下、実施の形態と称する)について、図面を参照しながら詳細に説明する。

<本技術の実施の形態である固体撮像素子の第1の構成例>

この固体撮像素子30の第1の構成例は、Si基板11の裏面近傍に形成されたPD(電荷保持部)31を有し、裏面側から照射される光に応じて画素信号を出力する、いわゆる裏面照射型CISである。

固体撮像素子30の第1の構成例には、Si基板11に対して垂直方向(縦方向)に縦型トランジスタ13が形成されており、表面側にFD14が形成されており、PD31にて変換、蓄積された電荷は、縦型トランジスタ13を介してFD14に転送される。

PD31は、例えば、Si基板11のP型ウェルに形成されたN+領域(N型の不純物濃度1E16乃至1E18/cm3)であり、Si基板11の裏面に接触しないように、その裏面から所定の間隔を隔てたSi基板11の内部に形成されている。

また、固体撮像素子30には、PD31の横方向に隣接して形成されたN-領域(P型の不純物濃度1E16乃至1E18/cm3)からなる電位障壁部32、および、電位障壁部32の横方向に隣接して形成されたPD31と同じ濃度のN+領域(N型の不純物濃度1E16乃至1E18/cm3)からなる低濃度OFD33が形成されている。電位障壁部32のポテンシャル制御については、図12を参照して後述する。

さらに、固体撮像素子30には、低濃度OFD33と重複し、電位障壁部32から間隔を開けた位置に、Si基板11の裏面側に接触するように、低濃度OFD33よりも高濃度のN+領域(N型の不純物濃度1E18乃至1E20/cm3)からなる高濃度OFD34が形成されている。高濃度OFD34は、PD31に電荷が蓄積したときのPD31に生じる電位よりも高い電圧に固定される(詳細は図9乃至図11を参照して後述する)。

図3は、固体撮像素子30の第1の構成例におけるPD31周辺のポテンシャルを示している。同図に示されるように、PD31において電荷の蓄積時間中に飽和した電荷は、電位障壁部32を超えて低濃度OFD33に流れ、さらに、高濃度OFD34に排出される。

<固体撮像素子30の第1の構成例の製造方法>

始めに、同図Aに示されるように、Si薄膜(SOI)41にN型のイオンを注入することにより、PD(電荷保持部)31および低濃度OFD33を形成する。ただし、PD31と低濃度OFD33は同一素材から成り、この段階において両者は区別されず一体的に形成される。次に、同図Bに示されるように、PD31と低濃度OFD33の間にP型のイオンを注入することにより、電位障壁部32を形成する。電位障壁部32が形成されたことにより、PD31と低濃度OFD33が区別される。

次に、同図Cに示されるように、Si薄膜41と低濃度OFDに重なるようにN型のイオンを注入することにより、高濃度OFD34を形成する。このとき、高濃度OFD34を、低濃度OFD33と重複し、電位障壁部32から間隔を開けた位置に、Si薄膜41の裏面側に接触するように形成する。なお、電位障壁部32よりも先に高濃度OFD34を形成し、高濃度OFD34を形成した後に電位障壁部32を形成するようにしてもよい。

最後に、同図Dに示されるように、Si薄膜41からSiをエピタキシャル成長させることによってSi部42を形成し、Si部42に縦型トランジスタ13やFD14などを形成する。なお、PD31とSi薄膜41の裏面の間にP型のイオンを注入してもよい。

以上のようにして生成された固体撮像素子30の第1の構成例においては、PD31で発生された電荷を読み出す場合、該電荷は縦型トランジスタ13を介してFD14に転送される。また、PD31で発生された電荷が飽和した場合、飽和した電荷は電位障壁部32を超えて、低濃度OFD33に流れて高濃度OFD34に排出される。

このように、固体撮像素子30の第1の構成例では、電荷を読み出すときと、飽和した電荷を排出するときの経路が異なるので、例えば、PD31から電荷を読み出すときの経路を利用して電荷の排出も行う構成と比較して、より安定的に電荷を排出させることができる。

また、固体撮像素子30の第1の構成例では、高濃度OFD34が直に電位障壁部32に接することなく形成されているので、高濃度OFD34が電位障壁部32のポテンシャルの高さに対して影響を及ぼすことを抑止できる。よって、Qsの低下や、隣接画素との混色の発生を抑止することができる。

<本技術の実施の形態である固体撮像素子の第2の構成例>

この固体撮像素子30の第2の構成例は、第1の構成例と同様に裏面照射型CISであり、第1の構成例における高濃度OFD34を削除し、その代わりに縦型トランジスタ(VG)51およびOFD52を設けたものである。

縦型トランジスタ51は、低濃度OFD33に接し、かつ、電位障壁部32に接しない位置にSi基板11に対して垂直方向(縦方向)に形成される。縦型トランジスタ51はPD31に電荷が蓄積したときのPD31に生じる電位よりも高い電圧に固定される。OFD52は、Si基板11の表面側に形成される。

図6は、固体撮像素子30第2の構成例におけるPD31周辺のポテンシャルを示している。

同図に示されるように、PD31において電荷の蓄積時間中に飽和した電荷は電位障壁部32を超えて低濃度OFD33に流れ、さらに、縦型トランジスタ51を介してOFD52に排出される。

<固体撮像素子30の第2の構成例の製造方法>

始めに、同図Aに示されるように、Si薄膜(SOI)41にN型のイオンを注入することにより、PD(電荷保持部)31および低濃度OFD33を形成する。ただし、PD31と低濃度OFD33は同一素材から成り、この段階において両者は区別されず一体的に形成される。次に、同図Bに示されるように、PD31と低濃度OFD33の間にP型のイオンを注入することにより、電位障壁部32を形成する。電位障壁部32が形成されたことにより、PD31と低濃度OFD33が区別される。

最後に、同図Cに示されるように、Si薄膜41からSiをエピタキシャル成長させることによってSi部42を形成し、Si部42に縦型トランジスタ51およびOFD52の他、縦型トランジスタ13やFD14などを形成する。なお、PD31とSi薄膜41の裏面の間にP型のイオンを注入してもよい。

以上のように、固体撮像素子30の第2の構成例は、第1の構成例に比較して少ない工程で製造することができる。

生成された固体撮像素子30の第2の構成例においては、PD31で発生された電荷を読み出す場合、該画素が縦型トランジスタ13を介してFD14に転送される。また、PD31で発生した電荷が飽和した場合、飽和した電荷が電位障壁部32を超え、低濃度OFD33に流れて縦型トランジスタ51を介してOFD52に排出される。

このように、固体撮像素子30の第2の構成例では、電荷を読み出すときと、飽和した電荷を排出するときの経路が異なるので、例えば、PD31から電荷を読み出すときの経路を利用して電荷の排出も行う構成と比較して、より安定的に電荷を排出させることができる。

また、固体撮像素子30の第2の構成例では、縦型トランジスタ51が直に電位障壁部32に接することなく形成されているので、縦型トランジスタ51に印可されている電圧が電位障壁部32のポテンシャルの高さに対して影響を及ぼすことを抑止できる。よって、Qsの低下や、隣接画素との混色の発生を抑止することができる。

<本技術の実施の形態である固体撮像素子の第3の構成例>

この固体撮像素子30の第3の構成例は、第1の構成例に、第2の構成例の縦型トランジスタ51およびOFD52を追加したものである。縦型トランジスタ51は、高濃度OFD34に接続されている。

固体撮像素子30の第3の構成例においては、PD31で発生された電荷を読み出す場合、該電荷が縦型トランジスタ13を介してFD14に転送される。また、PD31で発生された電荷が飽和した場合、飽和した電荷が電位障壁部32を超えて低濃度OFD33に流れ、高濃度OFD34に排出されるか、または縦型トランジスタ51を介してOFD52に排出される。

このように、固体撮像素子30の第3の構成例では、電荷を読み出すときと、飽和した電荷を排出するときの経路が異なるので、例えば、PD31から電荷を読み出すときの経路を利用して電荷の排出も行う構成と比較して、より安定的に電荷を排出させることができる。

また、固体撮像素子30の第3の構成例では、高濃度OFD34や縦型トランジスタ51が直に電位障壁部32に接することなく形成されているので、これらが電位障壁部32のポテンシャルの高さに対して影響を及ぼすことを抑止できる。よって、Qsの低下や、隣接画素との混色の発生を抑止することができる。

<高濃度OFD34の電位固定方法>

図9は、画素毎に貫通電極を設けた場合の構成例である。この場合、高電圧の電源71と高濃度OFD34は、配線72、貫通電極73、および配線74を介して接続されて、高濃度OFD34が高電圧に固定される。

図10および図11は、複数の画素で貫通電極を共有する場合の構成例であり、図10は断面図を、図11は上面図を示している。この場合、画素毎に貫通電極73を設ける場合に比較して、各画素が占める面積を貫通電極73の分だけ削減することができる。

<電位障壁部32のポテンシャル制御>

<本技術の実施の形態である固体撮像素子の第1の構成例の変形例>

隣接する複数の画素で高濃度OFD34を共有することにより、画素毎に高濃度OFD34を設ける場合に比較して、各画素で高濃度OFD34が占める面積を削減することができる。

図15は、固体撮像素子の第1の構成例の他の変形例(第2の変形例)として、Si基板11内にPD91を追加積層した構成例の断面図を示している。

同図に示されるように、Si基板11内に複数のPD(画素保持部31とPD91)が形成されている場合、裏面側に近い方のPD31では主に短波長側の光を光電変換し、遠い方のPD91では主に長波長側の光を光電変換するようにする。複数のPDによって異なる波長の光に応じて光電変換することにより分光が可能となる。また、複数のPDの出力を組み合わせれば、Qsの拡大が可能となる。なお、Si基板11内にPDを3層以上形成するようにしてもよい。

図16は、固体撮像素子の第1の構成例のさらに他の変形例(第3の変形例)として、図15の第2の変形例に、Si基板11の裏面から離れた外側にさらに有機光電変換膜などの光電変換膜92を追加した構成例の断面図を示している。

同図に示されるように、光電変換膜92を設けた場合、光電変換膜92により光電変換された成分を出力として取り出すことができ、かつ、光電変換膜92を透過した光をPD31,91それぞれにより光電変換することができる。複数のPD31,91と光電変換膜92によって異なる波長の光に応じて光電変換すれば、分光が可能となる。

<本技術の実施の形態である固体撮像素子の第2の構成例の変形例>

この第4の変形例は、図5の第2の構成例に対して、Si基板11の表面から離れた外側に有機光電変換膜などの光電変換膜101を追加するとともに、Si基板11の表面内側には、光電変換膜101が発生した電荷を蓄積するためのFD103が追加されている。

さらに、光電変換膜101の暗電流対策として、FD103には、RSTトランジスタ104を介してGND端子105が接続されている。なお、GND端子105の電圧は、0Vに限られるものではなく、VDDよりも低い電圧であればよい。他の構成例や変形例においても同様とする。

またさらに、FD103およびGND端子105と電荷保持部31との間には、横方向に伸びるN型拡散層からなるドレイン層106が形成されており、縦型トランジスタ51に接続されている。

第4の変形例においては、電源に接続されている縦型トランジスタ51からの電力によってN型拡散層のドレイン層106を常時オンとすることにより、ドレイン層106がFD103やGND端子105の画素トランジスタ、P型ウェルコンタクト107などから漏れる電荷を回収するためのドレインとして機能する。したがって、電荷保持部31の暗電流の悪化を抑止することができる。また、電力が供給されている縦型トランジスタ51には、ドレイン層106と同様に、漏れる電荷を回収するためのドレインとして作用が期待できる。縦型トランジスタ51によるドレインとしても作用が効果的である場合、ドレイン層106を省略してもよい。

なお、上述した第4の変形例は、図8に示された第3の構成例に適用することもできる。

<本技術の実施の形態である固体撮像素子の第2の構成例の他の変形例>

この第5の変形例は、図5の第2の構成例に対して、Si基板11の表面から離れた外側に有機光電変換膜などの光電変換膜101を追加するとともに、Si基板11の表面内側には、光電変換膜101が発生した電荷を蓄積するためのFD103が追加されている。

さらに、光電変換膜101の暗電流対策として、FD103には、RSTトランジスタ104を介してGND端子105が接続されている。

そして、第5の変形例では、ここまでに説明された構成例や変形例で省略されていた、AMPトランジスタ112およびSELトランジスタ113が図示されている。

この第5の変形例は、AMPトランジスタ112およびSELトランジスタ113を間に挟んでSi基板11内に絶縁部111,114が形成されている。

また、AMPトランジスタ112およびSELトランジスタ113の下方には、横方向に伸びるN型拡散層からなるウェル分離層115が形成されている。ウェル分離層115は、縦型トランジスタ51から横方向に延伸されており、絶縁部111,114とも接している。

このような構造により、ウェル領域のうち、AMPトランジスタ112およびSELトランジスタ113の下方領域は、その他の領域(FD103をリセットするRSTトランジスタ104)などが形成されている領域)から電気的に分離されたことになり、両領域の電位は異なるものとなる。第5の変形例の場合、AMPトランジスタ112およびSELトランジスタ113の下方領域は、その他のウェル領域よりも電位が低くなる。

これにより、FD103のリセット電位をAMPトランジスタ112の入力電圧に拘わりなく任意に設定できるので、AMPトランジスタ112の動作点に起因したランダムノイズや駆動能力(gm)などの撮像特性の劣化を抑止することができる。

なお、AMPトランジスタ112およびSELトランジスタ113の下方領域と、RSTトランジスタ104などが形成されている領域の電位を異なるものとすることによって得られる上記効果についてのみ着目した場合、ウェル分離層115は縦型トランジスタ51に接続していなくてもよい。その場合、以下に説明する図19乃至図22に示す構成例が考えられる。

すなわち、図19に示される構成例は、Drainに接続されているN型領域121から、AMPトランジスタ112およびSELトランジスタ113の下方にウェル分離層115を延伸したものである。この場合も、AMPトランジスタ112およびSELトランジスタ113の下方領域は、その他のウェル領域よりも電位が低くなり、上述した効果を得ることができる。

図20に示される構成例は、Drainに接続されているN型領域121から、RSTトランジスタ104の下方にウェル分離層115を延伸することにより、ウェル領域のうち、RSTトランジスタ104の下方領域は、その他の領域(AMPトランジスタ112およびSELトランジスタ113などが形成されている領域)から電気的に分離されたことになり、両領域の電位は異なるものとなる。この場合、RSTトランジスタ104の下方領域は、その他のウェル領域よりも電位が高くなり、上述した効果を得ることができる。

なお、図18の示された第5の変形例を図20に構成例と同様に変形し、縦型トランジスタ51から延伸したウェル分離層115によって、RSTトランジスタ104の下方領域と、その他の領域(AMPトランジスタ112およびSELトランジスタ113などが形成されている領域)とを電気的に分離してもよい。

図21に示される構成例は、図20に示された構成例における各半導体の導電性を反転させたものである。この場合、RSTトランジスタ104の下方領域の電位は、その他のウェル領域よりも低くなり、上述した効果を得ることができる。

図22に示される構成例は、AMPトランジスタ112およびSELトランジスタ113をPMOSにより形成して、その下部をN型のウェル領域によって形成している。これにより、ウェル分離層115を形成することなく、AMPトランジスタ112およびSELトランジスタ113の下方領域と、RSTトランジスタ104などが形成されているその他の領域を電気的に分離して、両領域の電位を異なるものとしている。この場合、AMPトランジスタ112およびSELトランジスタ113の下方領域は、その他のウェル領域よりも電位が高くなり、上述した効果を得ることができる。

<本技術の実施の形態である固体撮像素子の第2の構成例のさらに他の変形例>

この第6の変形例においては、電源に接続されている縦型トランジスタ51からの電力によってドレイン層106を常時オンとすることにより、ドレイン層106がFD103およびGND端子105から漏れる電荷を回収するためのドレインとして機能する。したがって、電荷保持部31の暗電流の悪化を抑止することができる。

また、ウェル分離層115が、ウェル領域のうち、AMPトランジスタ112およびSELトランジスタ113の下方領域と、その他の領域を電気的に分離し、両領域の電位が異なるものとなる。これにより、FD103のリセット電位をAMPトランジスタ112の入力電圧に拘わりなく任意に設定できるので、AMPトランジスタ112の動作点に起因したランダムノイズや駆動能力(gm)などの撮像特性の劣化を抑止することができる。

なお、上述した第6の変形例は、図8に示された第3の構成例に適用することもできる。

次に、図25は、図23に示された第6の変形例における縦型トランジスタ51を複数の画素で共有する場合の構成例の上面図を示している。この場合、画素毎に縦型トランジスタ51を設ける場合に比較して、各画素が占める面積を縮小することができる。

<固体撮像素子30の使用例>

固体撮像素子30は、例えば、以下のように、可視光や、赤外光、紫外光、X線等の光をセンシングする様々なケースに使用することができる。

・ディジタルカメラや、カメラ機能付きの携帯機器等の、鑑賞の用に供される画像を撮影する装置

なお、本技術の実施の形態は、上述した実施の形態に限定されるものではなく、本技術の要旨を逸脱しない範囲において種々の変更が可能である。

本技術は以下のような構成も取ることができる。

30 固体撮像素子, 31 電荷保持部, 32 電位障壁部, 33 低濃度OFD, 34 高濃度OFD, 51 縦型トランジスタ, 52 OFD, 71 電源, 73 貫通電極, 81 ゲート電極, 82 縦型トランジスタ, 91 PD, 92 光電変換膜,101 光電変換膜, 106 ドレイン層, 115 ウェル分離層

This technology pertains to: a solid-state imaging element capable of stably performing overflow from a PD, and preventing the occurrence of Qs decline and color mixing; and an electronic device. A solid-state imaging element according to one embodiment of this technology is equipped, on the light-receiving surface side inside a semiconductor substrate, with a charge-maintaining part for producing and maintaining a charge according to incident light, an OFD section from which the charge saturated by the charge-maintaining part is discharged, and a potential barrier for forming a barrier for the charge flowing from the charge-maintaining part to the OFD section. Therein, the OFD section comprises a low-concentration OFD section and a high-concentration OFD section which have different concentrations of the same type of impurity, and the high-concentration OFD section and the potential barrier are formed with an interval interposed therebetween. This technology is applicable to CMOS image sensors, for example.

入射光に応じて電荷を発生、保持する電荷保持部と、

前記電荷保持部と前記低濃度OFD部とは、同じ型の不純物の濃度が等しい

前記半導体基板の前記受光面とは反対の面から形成され、前記高濃度OFD部に接する第1の縦型トランジスタをさらに備える

前記第1の縦型トランジスタと前記電位障壁部は、間隔を開けて形成されている

前記半導体基板に形成される画素トランジスタと前記電荷保持部との間に、前記第1の縦型トランジスタから横方向に延伸されているドレイン層をさらに備える

前記ドレイン層は、前記電荷保持部と同じ型の不純物の拡散層から形成されている

前記半導体基板のウェル領域のうち、所定の画素トランジスタの下部領域と、その他の領域とを電気的に分離する、前記第1の縦型トランジスタから横方向に延伸されているウェル分離層をさらに備える

前記ウェル分離層によって電気的に分離された、前記所定の画素トランジスタの前記下部領域の電位は、前記その他の領域の電位よりも低い

前記所定の画素トランジスタは、AMPトランジスタおよびSELトランジスタである

前記所定の画素トランジスタとしての前記AMPトランジスタの入力電圧となるRST電位は、前記AMPトランジスタのドレイン電圧よりも低い

前記所定の画素トランジスタは、RSTトランジスタである

前記半導体基板の前記受光面とは反対の面から形成され、前記電荷保持部から前記電荷を読み出す第2の縦型トランジスタをさらに備える

前記高濃度OFD部には、前記電荷保持部に電荷が蓄積したときに前記電荷保持部に生じる電圧よりも高い電圧が印可されている

前記高濃度OFD部には、前記半導体基板の前記受光面とは反対の面から前記半導体基板を貫く貫通電極を介して供給される、前記電荷保持部に電荷が蓄積したときに前記電荷保持部に生じる電圧よりも高い電圧が印可されている

前記貫通電極は、複数の画素毎に設けられ、前記複数の画素により共有される

前記電位障壁部のポテンシャルを制御する制御部をさらに備える

前記高濃度OFD部は、前記複数の画素により共有される

前記電荷保持部は、前記半導体基板内に複数層積層されている

前記半導体基板の前記受光面の外側に形成された光電変換膜を

固体撮像素子が搭載された電子装置において、

図2は、本技術の実施の形態である固体撮像素子の第1の構成例を示すブロック断面図である。なお、図2は、1画素分を図示しており、図1に示された従来のCISと共通する構成要素については同一の符号を付しているので、その説明は適宜省略する。

次に、固体撮像素子30の第1の構成例の製造方法を説明する。図4は、固体撮像素子30の第1の構成例の製造過程を示している。

図5は、本技術の実施の形態である固体撮像素子の第2の構成例を示すブロック断面図である。なお、図5は、1画素分を図示しており、図2に示された第1の構成例と共通する構成要素については同一の符号を付しているので、その説明は適宜省略する。

次に、固体撮像素子30の第2の構成例の製造方法を説明する。図7は、固体撮像素子30の第2の構成例の製造過程を示している。

図8は、本技術の実施の形態である固体撮像素子の第3の構成例を示すブロック断面図である。なお、図8は、1画素分を図示しており、図2に示された第1の構成例または第図5に示された第2の構成例と共通する構成要素については同一の符号を付しているので、その説明は適宜省略する。

上述したように、PD31から飽和した電荷の排出先である高濃度OFD34は、PD31に電荷が蓄積しているときのPD31に生じる電位よりも高い電圧に固定する必要がある。そこで、高濃度OFD34の電極がSi基板11の裏面側に存在する場合、Si基板11に貫通電極を設けて表面側の電源と高濃度OFD34とを電気的に接続すればよい。

次に、図12は、電位障壁部32のポテンシャルを制御するための構成例を示している。同図Aは、Si基板11の裏面側にゲート電極81を設けて電位障壁部32と接続した構成例である。この場合、ゲート電極81から所定の電圧を印可することにより、電位障壁部32のポテンシャルを制御することができる。同図Bは、Si基板11の表面側から縦型トランジスタ82を設けた電位障壁部32と接続した構成例である。この場合、縦型トランジスタ82から所定の電圧を印可することにより、電位障壁部32のポテンシャルを制御することができる。

次に、図13および図14は、図2に示された固体撮像素子の第1の構成例の変形例(第1の変形例)として、高濃度OFD34を複数の画素で共有する場合の構成例であり、図13は断面図を、図14は上面図を示している。なお、図14のAおよび図14のBは、高濃度OFD34を2画素で共有する場合の例を示し、図14のCは、高濃度OFD34を4画素で共有する場合の例を示している。

次に、図17は、図5に示された固体撮像素子の第2の構成例の変形例(第4の変形例)を示している。

次に、図18は、図5に示された固体撮像素子の第2の構成例の他の変形例(第5の変形例)である。

次に、図23は、図5に示された固体撮像素子の第2の構成例のさらに他の変形例(第6の変形例)である。具体的には、図17に示された第4の変形例と、図18に示された第5の変形例を組み合わせたものである。図24は、図23に示された第6の変形例の上面図である。

図26は、本技術の実施の形態である固体撮像素子30の使用例を示している。

・自動停止等の安全運転や、運転者の状態の認識等のために、自動車の前方や後方、周囲、車内等を撮影する車載用センサ、走行車両や道路を監視する監視カメラ、車両間等の測距を行う測距センサ等の、交通の用に供される装置

・ユーザのジェスチャを撮影して、そのジェスチャに従った機器操作を行うために、TVや、冷蔵庫、エアーコンディショナ等の家電に供される装置

・内視鏡や、赤外光の受光による血管撮影を行う装置等の、医療やヘルスケアの用に供される装置

・防犯用途の監視カメラや、人物認証用途のカメラ等の、セキュリティの用に供される装置

・肌を撮影する肌測定器や、頭皮を撮影するマイクロスコープ等の、美容の用に供される装置

・スポーツ用途等向けのアクションカメラやウェアラブルカメラ等の、スポーツの用に供される装置

・畑や作物の状態を監視するためのカメラ等の、農業の用に供される装置

(1)

入射光に応じて電荷を発生、保持する電荷保持部と、

前記電荷保持部で飽和した前記電荷が排出されるOFD部と、

前記電荷保持部から前記OFD部に流れ出る前記電荷の障壁となる電位障壁部と

を半導体基板内の受光面側に備え、

前記OFD部は、同じ型の不純物の濃度が異なる低濃度OFD部および高濃度OFD部から成り、

前記高濃度OFD部と前記電位障壁部は、間隔を開けて形成されている

固体撮像素子。

(2)

前記電荷保持部と前記低濃度OFD部とは、同じ型の不純物の濃度が等しい

前記(1)に記載の固体撮像素子。

(3)

前記半導体基板の前記受光面とは反対の面から形成され、前記高濃度OFD部に接する第1の縦型トランジスタをさらに備える

前記(1)または(2)に記載の固体撮像素子。

(4)

前記第1の縦型トランジスタと前記電位障壁部は、間隔を開けて形成されている

前記(3)に記載の固体撮像素子。

(5)

前記半導体基板に形成される画素トランジスタと前記電荷保持部との間に、前記第1の縦型トランジスタから横方向に延伸されているドレイン層をさらに備える

前記(3)に記載の固体撮像素子。

(6)

前記ドレイン層は、前記電荷保持部と同じ型の不純物の拡散層から形成されている

前記(5)に記載の固体撮像素子。

(7)

前記半導体基板のウェル領域のうち、所定の画素トランジスタの下部領域と、その他の領域とを電気的に分離する、前記第1の縦型トランジスタから横方向に延伸されているウェル分離層をさらに備える

前記(3)から(6)のいずれかに記載の固体撮像素子。

(8)

前記ウェル分離層によって電気的に分離された、前記所定の画素トランジスタの前記下部領域の電位は、前記その他の領域の電位よりも低い

前記(7)に記載の固体撮像素子。

(9)

前記所定の画素トランジスタは、AMPトランジスタおよびSELトランジスタである

前記(7)または(8)に記載の固体撮像素子。

(10)

前記所定の画素トランジスタとしての前記AMPトランジスタの入力電圧となるRST電位は、前記AMPトランジスタのドレイン電圧よりも低い

前記(9)に記載の固体撮像素子。

(11)

前記所定の画素トランジスタは、RSTトランジスタである

前記(7)に記載の固体撮像素子。

(12)

前記半導体基板の前記受光面とは反対の面から形成され、前記電荷保持部から前記電荷を読み出す第2の縦型トランジスタをさらに備える

前記(1)から(11)のいずれかに記載の固体撮像素子。

(13)

前記高濃度OFD部には、前記電荷保持部に電荷が蓄積したときに前記電荷保持部に生じる電圧よりも高い電圧が印可されている

前記(1)から(12)のいずれかに記載の固体撮像素子。

(14)

前記高濃度OFD部には、前記半導体基板の前記受光面とは反対の面から前記半導体基板を貫く貫通電極を介して供給される、前記電荷保持部に電荷が蓄積したときに前記電荷保持部に生じる電圧よりも高い電圧が印可されている

前記(1)から(13)のいずれかに記載の固体撮像素子。

(15)

前記貫通電極は、複数の画素毎に設けられ、前記複数の画素により共有される

前記(14)に記載の固体撮像素子。

(16)

前記電位障壁部のポテンシャルを制御する制御部をさらに備える

前記(1)から(15)のいずれかに記載の固体撮像素子。

(17)

前記高濃度OFD部は、前記複数の画素により共有される

前記(1)から(16)のいずれかに記載の固体撮像素子。

(18)

前記電荷保持部は、前記半導体基板内に複数層積層されている

前記(1)から(17)のいずれかに記載の固体撮像素子。

(19)

前記半導体基板の前記受光面の外側に形成された光電変換膜を

さらに備える前記(1)から(18)のいずれかに記載の固体撮像素子。

(20)

固体撮像素子が搭載された電子装置において、

前記固体撮像素子は、

入射光に応じて電荷を発生、保持する電荷保持部と、

前記電荷保持部で飽和した前記電荷が排出されるOFD部と、

前記電荷保持部から前記OFD部に流れ出る前記電荷の障壁となる電位障壁部と

を半導体基板内の受光面側に備え、

前記OFD部は、同じ型の不純物の濃度が異なる低濃度OFD部および高濃度OFD部から成り、

前記高濃度OFD部と前記電位障壁部は、間隔を開けて形成されている

電子装置。

前記電荷保持部で飽和した前記電荷が排出されるOFD部と、

前記電荷保持部から前記OFD部に流れ出る前記電荷の障壁となる電位障壁部と

を半導体基板内の受光面側に備え、

前記OFD部は、同じ型の不純物の濃度が異なる低濃度OFD部および高濃度OFD部から成り、

前記高濃度OFD部と前記電位障壁部は、間隔を開けて形成されている

固体撮像素子。

請求項1に記載の固体撮像素子。

請求項2に記載の固体撮像素子。

請求項3に記載の固体撮像素子。

請求項3に記載の固体撮像素子。

請求項5に記載の固体撮像素子。

請求項3に記載の固体撮像素子。

請求項7に記載の固体撮像素子。

請求項7に記載の固体撮像素子。

請求項9に記載の固体撮像素子。

請求項7に記載の固体撮像素子。

請求項2に記載の固体撮像素子。

請求項2に記載の固体撮像素子。

請求項13に記載の固体撮像素子。

請求項14に記載の固体撮像素子。

請求項2に記載の固体撮像素子。

請求項2に記載の固体撮像素子。

請求項2に記載の固体撮像素子。

さらに備える請求項2に記載の固体撮像素子。

前記固体撮像素子は、

入射光に応じて電荷を発生、保持する電荷保持部と、

前記電荷保持部で飽和した前記電荷が排出されるOFD部と、

前記電荷保持部から前記OFD部に流れ出る前記電荷の障壁となる電位障壁部と

を半導体基板内の受光面側に備え、

前記OFD部は、同じ型の不純物の濃度が異なる低濃度OFD部および高濃度OFD部から成り、

前記高濃度OFD部と前記電位障壁部は、間隔を開けて形成されている

電子装置。