STORAGE DEVICE

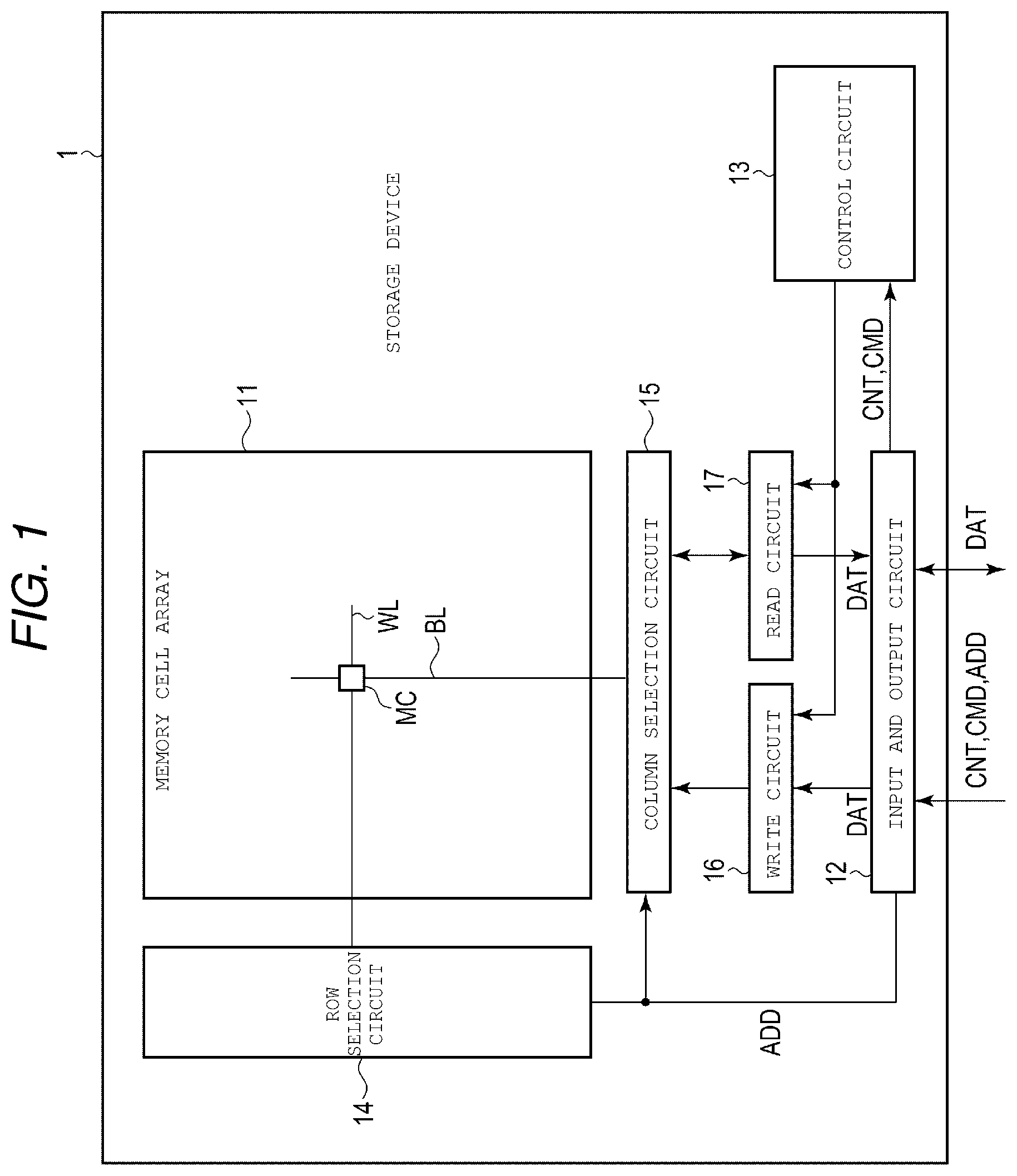

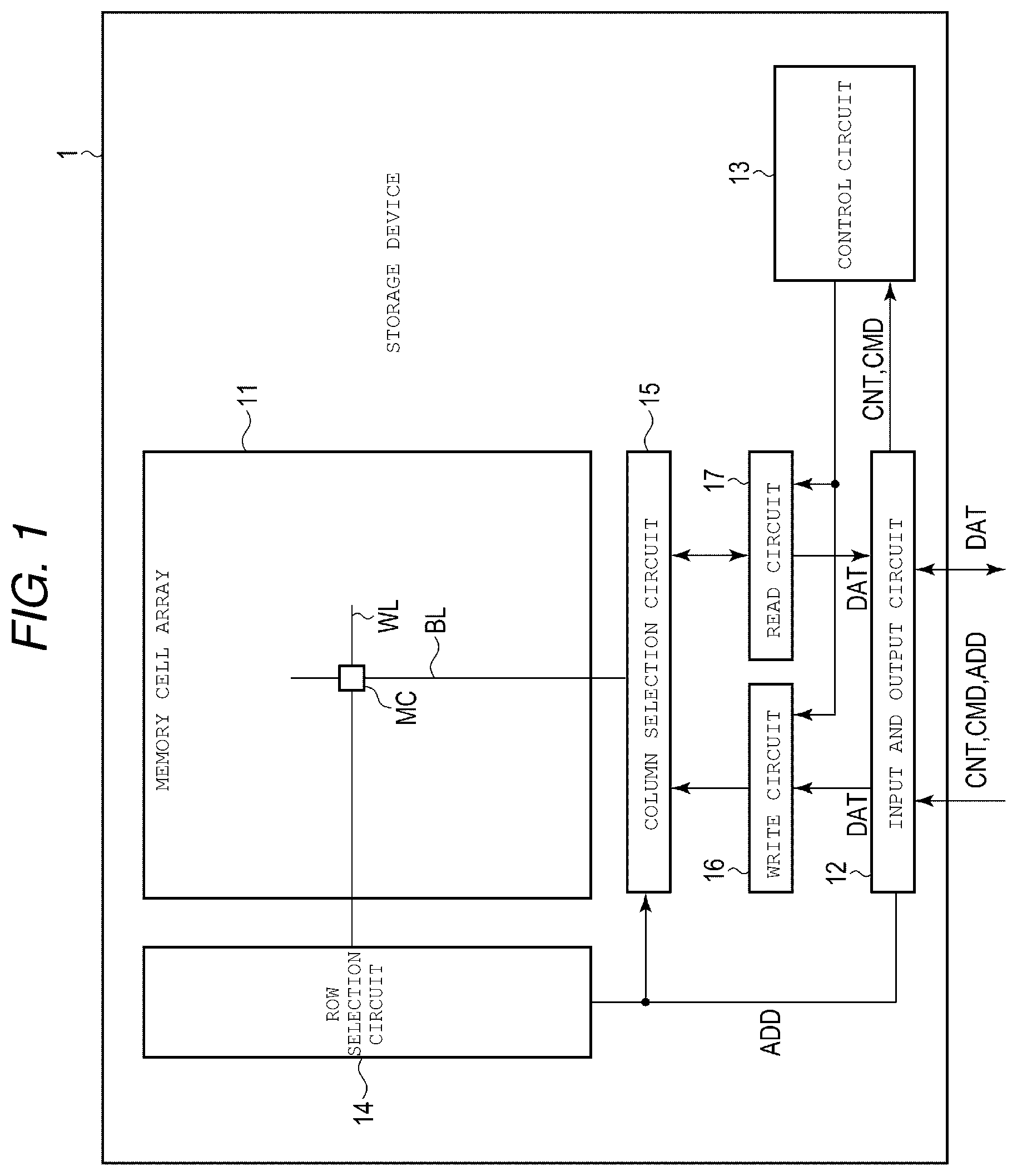

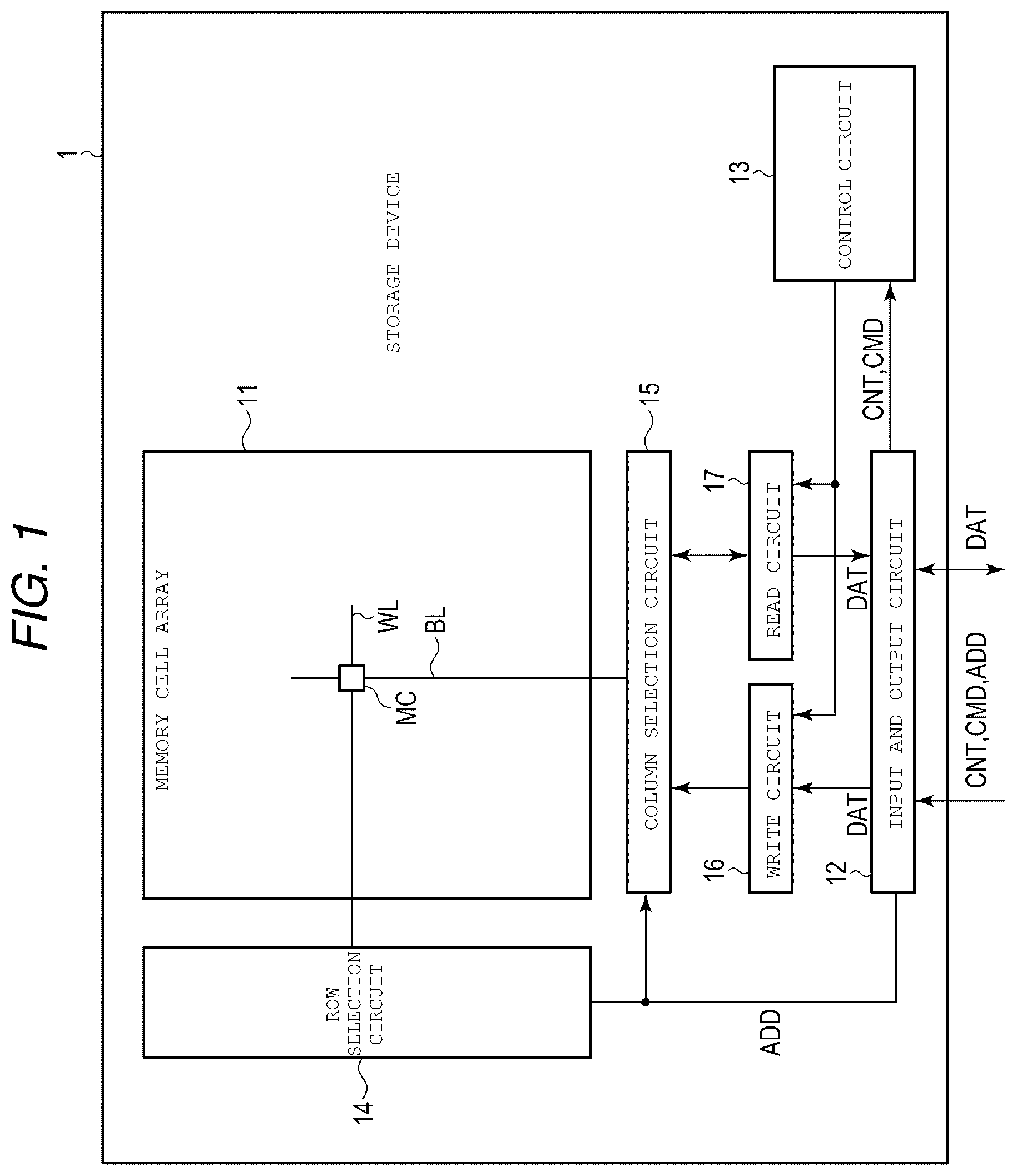

This application is based upon and claims the benefit of priority from Japanese Patent Application No. 2018-173092, filed Sep. 14, 2018, the entire contents of which are incorporated herein by reference. Embodiments described herein relate generally to a storage device. A storage device that stores data using a switchable resistor of an element is known. Embodiments provide a high-performance storage device. In general, according to one embodiment, a storage device, includes a first conductor extending along a first direction, a plurality of first variable-resistance elements on the first conductor, a second conductor on the plurality of first variable-resistance elements, the second conductor extending along a second direction, a plurality of second variable-resistance elements on the second conductor, and a third conductor on the plurality of second variable-resistance elements, the third conductor extending along the first direction. A first switching element is connected between the second conductor and a corresponding one of the first variable-resistance elements. A second switching element is connected between the third conductor and a corresponding one of second variable-resistance elements. Hereinafter, example embodiments will be described with reference to the drawings. In the following description, the same reference numerals will be given to those elements having substantially the same function and configuration, and repeated description for each example may be omitted. The drawings are schematic, and the depicted relationships between element thicknesses and/or other dimensions, the ratios between depicted element dimensions may be different from the actual ratio in actual devices. Furthermore, the descriptions of aspects and/or elements of any one embodiment are also applicable as descriptions of any other embodiment as long as such description is not expressly or obviously excluded from said other embodiments. In the specification and claims, a case where a first element is “connected” to a second element includes a case in which the first element is directly or indirectly connected to the second element via a conductive element interposed therebetween. The memory cell array 11 includes a plurality of memory cells MC, a plurality of word lines WL, and a plurality of bit lines BL. The memory cells MC can store data in a nonvolatile manner. Each memory cell MC is connected to one word line WL and one bit line BL. Each word line WL is associated with a row. Each bit line BL is associated with a column. By selecting one row and selecting one or more columns, one or a plurality of memory cells MC are specified/selected. The input and output circuit 12 receives a plurality of various control signals CNT, various commands CMD, address signals ADD, and data DAT (write data), from a memory controller or the like, and sends data DAT (read data) to the memory controller or the like. The row selection circuit 14 receives the address signal ADD from the input and output circuit 12 and brings one word line WL that corresponds to the row based on the received address signal ADD into a selected state. The column selection circuit 15 receives the address signal ADD from the input and output circuit 12 and brings the plurality of bit lines BL that correspond to the column based on the received address signal ADD into a selected state. The control circuit 13 receives the control signal CNT and the command CMD from the input and output circuit 12. The control circuit 13 controls other elements of the storage device 1, in particular, the write circuit 16 and the read circuit 17, based on the details of the control instructed by the control signal CNT and the details of the command CMD. Specifically, the control circuit 13 controls the write circuit 16 during the writing of data to the memory cell array 11. The control during the data writing includes supply of a voltage used for the data writing to the write circuit 16. Further, the control circuit 13 controls the read circuit 17 during the reading of the data from the memory cell array 11. The control during the data reading includes supply of a voltage used for the data reading to the read circuit 17. The write circuit 16 receives the write data DAT from the input and output circuit 12 and supplies the voltage used for the data writing to the column selection circuit 15 based on the control of the control circuit 13 and the write data DAT. The read circuit 17 includes a sense amplifier, and reads the data held in the memory cell MC based on the control of the control circuit 13. The read data is supplied to the input and output circuit 12 as the read data DAT. Each memory cell MC has a node N1 and a node N2, is connected to one word line WL at node N1, and is connected to one bit line BL at node N2. More specifically, the memory cell MCa includes a memory cell MCa <β, γ> for all combinations of the cases where β is equal to or greater than 0 and equal to or less than M and all cases where γ is equal to or greater than 0 and equal to or less than N, and the memory cell MCa <β, γ> connects the word line WLa <β> and the bit line BL<γ> to each other. Similarly, the memory cell MCb includes a memory cell MCb <β, γ> for all combinations of the cases where β is equal to or greater than 0 and equal to or less than M and all cases where γ is equal to or greater than 0 and equal to or less than N, and the memory cell MCb <β, γ> connects the word line WLb <β> and the bit line BL<γ> to each other. Each memory cell MC includes one variable-resistance element VR and one switching element SEL. More specifically, the memory cell MCa <β, γ> includes the variable-resistance element VRa <β, γ> and the switching element SELa <β, γ> for all combinations of the cases where β is equal to or greater than 0 and equal to or less than M and all cases where γ is equal to or greater than 0 and equal to or less than N. The memory cell MCb <β, γ> includes the variable-resistance element <β, γ> and the switching element SELb <β, γ> for all combinations of the cases where β is equal to or greater than 0 and equal to or less than M and all cases where γ is equal to or greater than 0 and equal to or less than N. In each memory cell MC, the variable-resistance element VR and the switching element SEL are connected to each other in series. In each memory cell MC, the variable-resistance element VR may be connected to the node N1 and the switching element SEL may be connected to the node N2 (type A), or the switching element SEL may be connected to the node N1 and the variable-resistance element VR may be connected to the node N2 (type B). However, it is possible to switch the type corresponding to memory cells MCa and MCb labels in each embodiment. The variable-resistance element VR can switch between a low resistance state and a high resistance state. The variable-resistance element VR can hold one bit of data by using the two different resistance states. The switching element SEL has two terminals, and when a voltage less than a first threshold voltage is applied between the two terminals in the first direction, the switching element SEL is in a high resistance state (off state). On the other hand, when a voltage equal to or greater than the first threshold voltage is applied between the two terminals in the first direction, the switching element SEL is in a low resistance state, for example, in an electrically conductive state (on state). The switching element SEL further has the same switching function based on the magnitude of the voltage applied in a second direction opposite to the first direction. By switching on or off the switching element SEL, it is possible to control the supply of the current to the variable-resistance element VR connected to the switching element SEL, that is, the selection or non-selection of the variable-resistance element VR. Furthermore, a z axis is orthogonal to the xy plane. As shown in A plurality of conductors 22 are provided above (the z axis direction) of the conductor 21. The conductors 22 extend along the x axis and are arranged along the y axis at equal intervals, for examples. Each of the conductors 22 function respectively as a word line WLb. The spacing intervals between the conductors 22 are equal to the spacing intervals between the conductors 21, for example. A variable-resistance element 23 is provided between each of the conductors 21 and each of the conductors 22. Each of the variable-resistance elements 23 are connected to only one conductor 21 and only one conductor 22. The variable-resistance elements 23 are arranged in a matrix along the x axis and the y axis. The variable-resistance elements 23 arranged along the x axis are arranged at equal intervals, and the variable-resistance elements 23 arranged along the y axis are arranged at equal intervals. For example, the spacing interval (the distance between the two adjacent centers) of the variable-resistance elements 23 is D. Here, D may be the smallest interval manufacturable based, for example, on limitations in the process of manufacturing the storage device 1. Each of the variable-resistance elements 23 has a substantially circular shape on the xy plane. The variable-resistance element 23 can function as the variable-resistance element VRb and includes a plurality of layers stacked along the z axis. Each of the plurality of layers is either a conductor, an insulator, or a ferromagnetic body. Further, the details of the variable-resistance element 23 will be described later. A plurality of conductors 32 are provided below the z axis of the conductor 21. The conductor 32 extends along the x axis and arranged along the y axis, for example, arranged along the y axis at equal intervals. Each of the conductors 32 functions as one word line WLa. The intervals of the conductors 32 are equal to the intervals of the conductors 21, for example. Each of the conductors 32 has, for example, substantially the same planar shape on the xy plane as that of a conductor 22 and is disposed directly below the z axis of a corresponding conductor 22. One variable-resistance element 33 is provided between each of the conductors 21 and each of the conductors 32. Each of the variable-resistance elements 33 can be respectively connected electrically to only one conductor 21 and only one conductor 32. Each of the variable-resistance elements 33 has substantially the same shape as that of a variable-resistance element 23, is disposed directly below the z axis of the corresponding variable-resistance element 23, can function as the variable-resistance element VRa, and includes a plurality of layers stacked along the z axis. Each of the plurality of layers is either a conductor, an insulator, or a ferromagnetic body. Further, the details of the variable-resistance element 33 will be described below. As shown in A plurality of switching elements 34 are provided on one layer above the layer on which the variable-resistance element 33 is disposed. The switching elements 34 extend along the y axis and are arranged along the x axis. Each of the switching elements 34 is connected to the upper surface of each of the plurality of variable-resistance elements 33 arranged along the y axis, on a bottom surface. The switching element 34 functions as the switching element SELa. The switching element 34 is, for example, a switching element between the two terminals (e.g., single-pole, single throw switch), the first terminal of the two corresponds to one of the upper surface or the bottom surface of the switching element 34, and the second terminal of the two corresponds to the other one of the upper surface or the bottom surface of the switching element 34. When a voltage less than the first threshold voltage is applied across the switching element 34, the switching element 34 is in a “high resistance” state. When a voltage equal to or greater than the first threshold voltage is applied across the switching element 34, the switching element 34 is in a “low resistance” state. The switching element 34 may operate with any polarity of applied voltage. The switching element 34 may contain at least one type of chalcogen element selected from the group consisting of Te, Se, and S. Otherwise, the switching element 34 may contain a chalcogenide that is a compound containing the chalcogen element. The switching element 34 may further contain at least one type of element selected from the group consisting of B, Al, Ga, In, C, Si, Ge, Sn, As, P, and Sb. In the second embodiment and any of the embodiments thereafter, the switching element 34 may be the switching element between the two terminals as described here. The switching element 34 may include a further layer, for example, conductor, on one or both of the upper surface and the bottom surface. Each of the variable-resistance elements 33 and an upper part of the variable-resistance element 33 of the switching element 34 configure one memory cell MCa. In other words, as shown in The description returns to The plurality of variable-resistance elements 23 are provided on a layer one layer above a layer on which the conductor 21 is disposed. The plurality of variable-resistance elements 23 arranged along the y axis are disposed on the upper surface of one conductor 21. A plurality of switching elements 24 are provided on a layer one layer above a layer on which the variable-resistance element 23 is disposed. The switching elements 24 extend along the x axis and are arranged along the y axis. Each of the switching elements 24 is connected to the upper surface of each of the plurality of variable-resistance elements 23 arranged along the x axis, on a bottom surface. The switching element 24 functions as the switching element SELb. The switching element 24 is, for example, a switching element between the two terminals, the first terminal of the two corresponds to one of the upper surface or the bottom surface of the switching element 24, and the second terminal of the two corresponds to the other one of the upper surface or the bottom surface of the switching element 24. When a voltage less than a second threshold voltage is applied between the two terminals of the switching element 24, the switching element 24 is in a “high resistance” state. When a voltage equal to or greater than the second threshold voltage is applied between the two terminals of the switching element 24, the switching element 24 is in a “low resistance” state. The switching element 24 may operate with any polarity of voltage. The switching element 24 may contain at least one chalcogen element selected from the group consisting of Te, Se, and S. Otherwise, the switching element 24 may contain a chalcogenide that is a compound containing the chalcogen element. The switching element 24 may further contain at least one type of element selected from the group consisting of B, Al, Ga, In, C, Si, Ge, Sn, As, P, and Sb. In the second embodiment and any of the embodiments thereafter, the switching element 24 may be the switching element between the two terminals as described here. The switching element 24 may include a further layer, for example, conductor, on one or both of the upper surface and the bottom surface. Each of the variable-resistance elements 23 and an upper part of the variable-resistance element 23 of the switching element 24 configure one memory cell MCb. In other words, based on the same principle as described for the switching element 34 with reference to A plurality of conductors 22 are provided on a layer one layer above a layer on which the switching element 24 is disposed. Each of the conductors 22 is disposed on the upper surface of one switching element 24 and has, for example, substantially the same planar shape as the planar shape of one switching element 24. In the region above the board 31, an insulator 37 is provided in a region other than a region where the conductor 32, the variable-resistance element 33, the switching element 34, the conductor 21, the variable-resistance element 23, the switching element 24, and the conductor 22 are disposed. According to the structure of the memory cell array 11 of the first embodiment, the memory cell MCa is the type A (refer to The variable-resistance elements 23 and 33 are based on MTJ elements, and the variable-resistance elements 23 and 33 include a ferromagnetic body 41, an insulating non-magnetic body 42, and a ferromagnetic body 43. The ferromagnetic body 41 is disposed at the lowermost part of the variable-resistance element 23, the non-magnetic body 42 is disposed on the upper surface of the ferromagnetic body 41, and the ferromagnetic body 43 is disposed on the upper surface of the non-magnetic body 42. In the ferromagnetic body 41, in a normal operation by the storage device 1, the direction of magnetization is invariable, while the direction of magnetization of the ferromagnetic body 43 is variable. The ferromagnetic bodies 41 and 43 have, for example, easy magnetization axes along the direction passing through interfaces of the ferromagnetic body 41, the non-magnetic body 42, and the ferromagnetic body 43. The ferromagnetic body 41, the non-magnetic body 42, and the ferromagnetic body 43 together show a magnetic resistor effect. Specifically, when the directions of magnetization of the ferromagnetic bodies 41 and 43 are parallel to each other, the variable-resistance elements 23 and 33 exhibit the minimum resistor value. On the other hand, when the directions of magnetization of the ferromagnetic bodies 41 and 43 are parallel to each other, the variable-resistance elements 23 and 33 exhibit the maximum resistor value. States corresponding to the two different resistor values can be assigned to different binary data values, respectively. When a write current IWAPhaving a certain magnitude flows from the ferromagnetic body 43 toward the ferromagnetic body 41, the direction of magnetization of the ferromagnetic body 41 becomes antiparallel to the direction of magnetization of the ferromagnetic body 43. On the other hand, when the write current IWAp having a certain magnitude flows from the ferromagnetic body 41 toward the ferromagnetic body 43, the direction of magnetization of the ferromagnetic body 41 becomes parallel to the direction of magnetization of the ferromagnetic body 43. Each of the variable-resistance elements 23 and 33 may further include the ferromagnetic bodies and (or) additional conductors. The variable-resistance elements 23 and 33 may have a structure as depicted in As shown in The region between the conductors 32 is filled by a part of the insulator 37. A stacked body for forming the variable-resistance element 33 is deposited on the upper surface of the conductor 32 and the insulator 37 therebetween. The stacked body includes a plurality of layers corresponding to those in the variable-resistance element 33. According to the example of A mask material 50 is deposited on the upper surface of the stacked body used to form the variable-resistance element 33. The mask material 50 remains above the region where the variable-resistance element 33 is to be formed, and is open at the other part thereof. The variable-resistance element 33 is formed by etching the stacked body by ion beam etching (IBE) using the mask material 50. As shown in As shown in As shown in As shown in Next, the region between the variable-resistance elements 23 is fill by a part of the insulator 37. A layer 24A is deposited on the upper surface of the variable-resistance element 23 and the insulator 37 therebetween, and a conductor 22A is deposited on the upper surface of the layer 24A. The layer 24A includes the same material as that of the switching element 24 and the conductor 22A contains the same material as that of the conductor 22. A mask material 52 is formed on the upper surface of the conductor 22A. The mask material 52 remains above the region where the switching element 24 and the conductor 22 are to be formed, and are open at the other part thereof. As shown in As shown in According to the first embodiment, as described below, it is possible to prevent deterioration of characteristics caused by patterning and to provide a storage device 1 having switching elements 24 and 34 that can be easily patterned. The memory cell array 11 with the circuit shown in As shown in However, the IBE of the layer 134A may deteriorate the characteristics of the switching element 134. Furthermore, the IBE in the step of According to the first embodiment, the switching elements 34 extend along the y axis so as to be connected to the plurality of variable-resistance elements 33 arranged along the y axis, and unlike the structure of On the other hand, similar to the structure in Similarly, the switching elements 24 extend along the x axis so as to be connected to the plurality of variable-resistance elements 23 arranged along the x axis, and unlike the structure in A second embodiment is different from the first embodiment in the structure of the memory cell array 11. More specifically, the second embodiment is different from the first embodiment in the position and shape on the z axis of the switching element 24. Hereinafter, points different from those of the first embodiment will be mainly described. As shown in The switching elements 24 extend along the y axis and are arranged along the x axis. Each of the switching elements 24 is disposed on the upper surface of one conductor 21. Each of the bottom surfaces of the plurality of variable-resistance elements 23 arranged along the y axis are connected to the upper surface of one switching element 24. According to the structure of the memory cell array 11 of the second embodiment, both the memory cells MCa and MCb are the type A (refer to A mask material 56 is formed on the upper surface of the conductor 24A. The mask material 56 remains above the region where the stacked body of the switching element 34, the conductor 21, and the switching element 24 are to be formed. The material layers for switching element 345, the conductor 21, the conductor 22, and the switching element 24 are partly removed by etching, such as RIE, through the mask material 56. As a result of etching, the switching element 34 is formed, the conductor 21 is formed, and the switching element 24 is formed. As shown in According to the second embodiment, similar to the first embodiment, the switching elements 34 extend along the y axis and are disposed between the layer on which the conductor 21 is disposed and the layer on which the variable-resistance element 33 is disposed. Accordingly, similar to the first embodiment, deterioration of the characteristics of the switching element 34 can be prevented, which would otherwise occur when the switching element 34 is patterned by IBE. Further, according to the second embodiment, the switching elements 24 extend along the y axis so as to be connected to the plurality of variable-resistance elements 23 arranged along the y axis, and unlike the structure in A third embodiment is different from the first embodiment in the structure of the memory cell array 11. More specifically, the third embodiment is different from the first embodiment in the position and shape on the z axis of the switching element 34. Hereinafter, points different from those of the first embodiment will be mainly described. As shown in The switching elements 34 extend along the x axis and are arranged along the y axis. Each of the switching elements 34 is disposed on the upper surface of one conductor 32. Each of the bottom surfaces of the plurality of variable-resistance elements 33 arranged along the x axis are connected to the upper surface of one switching element 34. According to the structure of the memory cell array 11 of the third embodiment, both the memory cells MCa and MCb are the type B (refer to Next, the mask material 57 is removed and the region between the stacked bodies of the conductor 32 and the switching element 34 is filled by a part of the insulator 37. Next, as shown in According to the third embodiment, similar to the first embodiment, the switching elements 24 extend along the x axis and are disposed between the layer on which the conductor 22 is disposed and the layer on which the variable-resistance element 23 is disposed. Accordingly, similar to the first embodiment, deterioration of the characteristics of the switching element 24 can be prevented, which would otherwise occur when the switching element 24 is patterned by IBE. Further, according to the third embodiment, the switching elements 34 extend along the x axis so as to be connected to the plurality of variable-resistance elements 33 arranged along the x axis, and unlike the structure in A fourth embodiment is different from the first embodiment in the structure of the memory cell array 11. More specifically, the fourth embodiment is different from the first embodiment in the shape of the switching element 24. Hereinafter, points different from those of the first embodiment will be mainly described. As shown in The switching elements 34 spread along the xy plane, spread exceeding a region of at least a set of two or more variable-resistance elements 33 arranged along the x axis and two or more variable-resistance elements 33 arranged along the y axis, and are connected to each of the upper surfaces of the plurality of variable-resistance elements 33 arranged along the xy plane. Similarly, the switching elements 24 spread along the xy plane, spread exceeding a region of at least a set of two or more variable-resistance elements 23 arranged along the x axis and two or more variable-resistance elements 23 arranged along the y axis, and are connected to each of the upper surfaces of the plurality of variable-resistance elements 23 arranged along the xy plane. According to the structure of the memory cell array 11 of the fourth embodiment, the memory cell MCa is the type A (refer to As shown in According to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane, and the switching elements 34 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. In other words, the switching elements 24 and 34 do not go through the process of separating the switching elements 24 and 34 from each other, and accordingly, it is possible to prevent deterioration of the characteristics of the switching elements 24 and 34, which can occur when performing the patterning by the etching (for example, IBE) for the separation. On the other hand, as described with reference to A fifth embodiment is different from the first embodiment in the structure of the memory cell array 11. More specifically, the fifth embodiment is different from the first embodiment in the shape of the switching element 34 and the position and shape on the z axis of the switching element 24. Hereinafter, points different from those of the first embodiment will be mainly described. As shown in Similar to the fourth embodiment, the switching elements 34 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. Further, similar to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane. According to the structure of the memory cell array 11 of the fifth embodiment, both the memory cells MCa and MCb are the type A (refer to The memory cell array 11 of the fifth embodiment can be formed by the following steps. Similar to the fourth embodiment, the steps in The mask material 59 is removed, the region between the variable-resistance elements 23 is filled by a part of the insulator 37, the conductor 22 is formed on the upper surface of the variable-resistance element 23, and the region between the conductors 22 is filled by a part of the insulator 37. As a result, the structure shown in According to the fifth embodiment, the switching elements 24 spread along the xy plane similar to the fourth embodiment and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane, and the switching elements 34 spread along the xy plane similar to the fourth embodiment and are connected to the upper surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. Accordingly, while the circuit in A sixth embodiment is different from the first embodiment in the structure of the memory cell array 11. More specifically, the sixth embodiment is different from the first embodiment in the position and shape of the switching element 34 and the shape of the switching element 24 along the z axis. Hereinafter, points different from those of the first embodiment will be mainly described. As shown in Similar to the fourth embodiment, the switching elements 34 spread along the xy plane and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. Further, similar to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane. According to the structure of the memory cell array 11 of the third embodiment, both the memory cells MCa and MCb are the type B (refer to The mask material 50 is removed and the region between the variable-resistance elements 33 is filled by a part of the insulator 37. Next, the conductor 21, the variable-resistance element 23, the switching element 24, and the conductor 22 are formed by steps similar to those described with reference to According to the sixth embodiment, the switching elements 24 spread along the xy plane similar to the fourth embodiment and are connected to the upper surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane, and the switching elements 34 spread along the xy plane similar to the fourth embodiment and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. Accordingly, while the circuit in A seventh embodiment is different from the first embodiment in the structure of the memory cell array 11. More specifically, in the seventh embodiment, in the arrangement on the xy plane of the variable-resistance elements 23 and 33, the shape of the conductor 22 and the conductor 32 and the arrangement on the xy plane, and the arrangement on the xy plane of the switching elements 24 and 34, are different from those of the first embodiment. Hereinafter, points different from those of the first embodiment will be mainly described. The distance between each of the variable-resistance elements 23 and the variable-resistance element 23 closest to the row next to the row to which the variable-resistance element 23 belongs is, for example, D. Accordingly, the pitch of the variable-resistance elements 23 arranged along the y axis and the pitch of the variable-resistance elements 23 arranged along the x axis are both √2×D. Each of the conductors 21 overlaps with the plurality of variable-resistance elements 23 arranged along the y axis on the xy plane, and extends along the plurality of variable-resistance elements 23 arranged along the y axis as will be described in detail later. Each of the conductors 22 overlaps with two rows of the variable-resistance elements 23 arranged along the y axis on the xy plane and extends along the two rows of the variable-resistance element 23 arranged along the y axis. Each of the conductors 32 overlaps with the plurality of variable-resistance elements 23 arranged along the y axis on the xy plane, and extends along the plurality of variable-resistance elements 23 arranged along the y axis as will be described in detail later. Each of the conductors 32 has, for example, substantially the same planar shape as that of one conductor 22 and is disposed directly below the z axis of the corresponding conductor 22. As shown in The two rows of the variable-resistance elements 33 arranged along the y axis are connected to the upper surface of each of the conductors 32. Each of the switching elements 34 is connected to the upper surfaces of each of the plurality of variable-resistance elements 33 in one row arranged along the y axis, is disposed below one conductor 21 on the z axis, and for example, has substantially the same planar shape as the planar shape of one corresponding conductor 21. Each of the conductors 21 is connected to the variable-resistance elements 23 in one row arranged along the y axis, on the upper surface. Each of the switching elements 24 is connected to the upper surfaces of each of the two rows of the variable-resistance elements 23 arranged along the y axis, is disposed below one conductor 22 on the z axis, and for example, has substantially the same planar shape as the planar shape of one corresponding conductor 22. According to the structure of the memory cell array 11 of the seventh embodiment, the memory cell MCa is the type A (refer to The structure in According to the seventh embodiment, similar to the first embodiment, the switching elements 34 extend along the y axis and are disposed between the layer on which the conductor 21 is disposed and the layer on which the variable-resistance element 33 is disposed, and the switching elements 24 extend along the x axis and are disposed between the layer on which the conductor 22 is disposed and the layer on which the variable-resistance element 23 is disposed. Accordingly, the same advantage as those in the first embodiment can be obtained. Further, according to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, in the seventh embodiment, it is possible to include more variable-resistance elements 23 and 33 than in the first embodiment per unit surface area, and it is possible to have a higher degree of integration degree than in the first embodiment. Furthermore, due to the arrangement in a zigzag manner, each of the conductors 22 can have a wider flat planar shape over the two rows of the variable-resistance elements 23 arranged along the y axis, and each of the conductors 32 can have a wider planar shape below the two rows of the variable-resistance elements 33 arranged along the y axis. Accordingly, the widths of the planes of the conductor 22 and the conductor 32 can be greater than the minimum pitch D of the variable-resistance elements 23 and 33. Therefore, the conductor 22 and the conductor 32 can be formed more easily than a case where the pitch of the variable-resistance elements 23 and 33 on the x axis and on the y axis is the minimum pitch D. An eighth embodiment is similar to the seventh embodiment and the second embodiment in the structure of the memory cell array 11 and relates to the combination of the seventh embodiment and the second embodiment. Hereinafter, points different from those of the seventh embodiment will be mainly described. As shown in Each of the switching elements 24 is disposed on the upper surface of one conductor 21 and has, for example, substantially the same planar shape as the planar shape of one corresponding conductor 21, and is connected to the bottom surfaces of each of the variable-resistance elements 33 in one row arranged along the y axis. According to the structure of the memory cell array 11 of the eighth embodiment, both the memory cells MCa and MCb are the type A (refer to The structure in Specifically, the patterning is changed such that the shapes and (or) arrangement of the conductor 32, the variable-resistance element 33, the switching element 34, the conductor 21, the switching element 24, the variable-resistance element 23, and the conductor 22 are as shown in According to the eighth embodiment, similar to the second embodiment, the switching elements 24 extend along the y axis and are disposed between the layer on which the variable-resistance element 23 is disposed and the layer on which the conductor 21 is disposed, and the switching elements 34 extend along the y axis and are disposed between the layer on which the conductor 21 is disposed and the layer on which the variable-resistance element 33 is disposed. Accordingly, the same advantages as those in the second embodiment, that is, the same advantages as those in the first embodiment, can be obtained. Further, according to the eighth embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. A ninth embodiment is similar to the seventh embodiment and the third embodiment in the structure of the memory cell array 11 and relates to the combination of the seventh embodiment and the third embodiment. Hereinafter, points different from those of the seventh embodiment will be mainly described. As shown in Each of the switching elements 34 is disposed on the upper surface of one conductor 32 and has, for example, substantially the same planar shape as the planar shape of one corresponding conductor 32, and is connected to the bottom surfaces of each of two rows of the variable-resistance elements 33 arranged along the y axis. According to the structure of the memory cell array 11 of the ninth embodiment, both the memory cells MCa and MCb are the type B (refer to The structure in According to the ninth embodiment, similar to the third embodiment, the switching elements 24 extend along the x axis and are disposed between the layer on which the conductor 22 is disposed and the layer on which the variable-resistance element 23 is disposed, and the switching elements 34 extend along the x axis and are disposed between the layer on which the variable-resistance element 33 is disposed and the layer on which the conductor 32 is disposed. Accordingly, the same advantages as those in the third embodiment, that is, the same advantages as those in the first embodiment, can be obtained. Further, according to the ninth embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. A tenth embodiment is similar to the seventh embodiment in the structure of the memory cell array 11. As shown in Each of the switching elements 34 is disposed on the upper surface of one conductor 32 and has, for example, substantially the same planar shape as the planar shape of one corresponding conductor 32, and is connected to the bottom surfaces of each of two rows of the variable-resistance elements 33 arranged along the y axis. Each of the switching elements 24 is disposed on the upper surface of one conductor 21 and has, for example, substantially the same planar shape as the planar shape of one corresponding conductor 21, and is connected to the bottom surfaces of each of the variable-resistance elements 33 in one row arranged along the y axis. According to the structure of the memory cell array 11 of the tenth embodiment, the memory cell MCa is the type B (refer to The structure in According to the tenth embodiment, similar to the second embodiment, the switching elements 24 extend along the y axis and are disposed between the layer on which the variable-resistance element 23 is disposed and the layer on which the conductor 21 is disposed, and similar to the third embodiment, the switching elements 34 extend along the x axis and are disposed between the layer on which the variable-resistance element 33 is disposed and the layer on which the conductor 32 is disposed. Accordingly, the same advantage as those in the first embodiment can be obtained. Further, according to the tenth embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. An eleventh embodiment is different from the seventh embodiment in the structure of the memory cell array 11. More specifically, the eleventh embodiment is different from the seventh embodiment in the shape of the switching element 24 and the shape of the switching element 34. Hereinafter, points different from those of the seventh embodiment will be mainly described. As shown in Further, similar to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane. Further, similar to the fourth embodiment, the switching elements 34 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. According to the structure of the memory cell array 11 of the eleventh embodiment, the memory cell MCa is the type A (refer to The structure in Specifically, the patterning is changed such that the shapes and (or) arrangement of the conductor 32, the variable-resistance element 33, the conductor 21, the variable-resistance element 23, and the conductor 22 are as shown in According to the eleventh embodiment, similar to the fourth embodiment, the switching elements 24 and 34 spread along the xy plane. Therefore, the same advantage as those in the fourth embodiment can be obtained. Further, according to the eleventh embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. A twelfth embodiment is different from the seventh embodiment in the structure of the memory cell array 11. More specifically, the twelfth embodiment is different from the seventh embodiment in the shape of the switching element 34 and the position and shape on the z axis of the switching element 24. Hereinafter, points different from those of the seventh embodiment will be mainly described. As shown in Similar to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane. Further, similar to the fourth embodiment, the switching elements 34 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. According to the structure of the memory cell array 11 of the twelfth embodiment, both the memory cells MCa and MCb are the type A (refer to The structure in According to the twelfth embodiment, similar to the fourth embodiment, the switching elements 24 and 34 spread along the xy plane. Therefore, the same advantage as those in the fourth embodiment can be obtained. Further, according to the twelfth embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. A thirteenth embodiment is different from the seventh embodiment in the structure of the memory cell array 11. More specifically, the thirteenth embodiment is different from the seventh embodiment in the position and shape on the z axis of the switching element 24 and the position and shape on the z axis of the switching element 34. Hereinafter, points different from those of the seventh embodiment will be mainly described. As shown in Similar to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the upper surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane. Further, similar to the fourth embodiment, the switching elements 34 spread along the xy plane and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. According to the structure of the memory cell array 11 of the thirteenth embodiment, both the memory cells MCa and MCb are the type B (refer to The structure in According to the thirteenth embodiment, similar to the fourth embodiment, the switching elements 24 and 34 spread along the xy plane. Therefore, the same advantage as those in the fourth embodiment can be obtained. Further, according to the thirteenth embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. A fourteenth embodiment is similar to the seventh embodiment in the structure of the memory cell array 11. As shown in Similar to the fourth embodiment, the switching elements 24 spread along the xy plane and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 23 arranged along the xy plane. Further, similar to the fourth embodiment, the switching elements 34 spread along the xy plane and are connected to the bottom surfaces of each of the plurality of variable-resistance elements 33 arranged along the xy plane. According to the structure of the memory cell array 11 of the fourteenth embodiment, the memory cell MCa is the type B (refer to The structure in According to the fourteenth embodiment, similar to the fourth embodiment, the switching elements 24 and 34 spread along the xy plane. Therefore, the same advantage as those in the fourth embodiment can be obtained. Further, according to the fourteenth embodiment, similar to the seventh embodiment, the variable-resistance elements 23 and 33 are arranged in a zigzag manner on a plane. Therefore, the same advantage as those in the seventh embodiment can be obtained. In the seventh to twelfth embodiments, the conductor 22 extends over the two rows of the variable-resistance elements 23 arranged along the y axis, the conductor 32 extends below the two rows of the variable-resistance elements 33 arranged along the y axis, and the conductor 21 extends along the one row of the variable-resistance elements 23 and 33 arranged along the y axis. Instead, the conductor 21 may extend below the two rows of the variable-resistance elements 23 arranged along the x axis and over the two rows of the variable-resistance elements 33 arranged along the x axis, the conductor 22 may extend over the one row of the variable-resistance elements 23 along the x axis, and the conductor 32 may extend below the one row of the variable-resistance elements 33 along the x axis. The variable-resistance element VR may include phase-change elements, ferroelectric elements, or other elements. The phase-change element is used in a phase-change random access memory (PCRAM), contains chalcogenide and the like, and changes to a crystalline state or an amorphous state due to heat generated by the write current, and accordingly, a different resistor value is indicated. The variable-resistance element VR may include elements used for resistive RAM (ReRAM) including metal oxides or perovskite oxides. In a case of the variable-resistance element VR, the resistor value of the variable-resistance element VR changes by the application of different widths (pulse application period) of the write pulse, the different amplitudes (current value and voltage value), and different polarities (applying direction) of the write pulse. While certain embodiments have been described, these embodiments have been presented by way of example only, and are not intended to limit the scope of the inventions. Indeed, the novel embodiments described herein may be embodied in a variety of other forms; furthermore, various omissions, substitutions and changes in the form of the embodiments described herein may be made without departing from the spirit of the inventions. The accompanying claims and their equivalents are intended to cover such forms or modifications as would fall within the scope and spirit of the inventions. According to one embodiment, a storage device includes a first conductor extending along a first direction, first variable-resistance elements on the first conductor, and a second conductor on the first variable-resistance elements and extending along a second direction. A plurality of second variable-resistance elements is on the second conductor. A third conductor is on the plurality of second variable-resistance elements. The third conductor extends along the first direction. A first switching element is connected between the second conductor and a corresponding one of the first variable-resistance elements. A second switching element is connected between the third conductor and a corresponding one of second variable-resistance elements. 1. A storage device, comprising:

a first conductor extending along a first direction; a plurality of first variable-resistance elements on the first conductor; a second conductor on the plurality of first variable-resistance elements, the second conductor extending along a second direction; a plurality of second variable-resistance elements on the second conductor; a third conductor on the plurality of second variable-resistance elements, the third conductor extending along the first direction; a first switching element connected between the second conductor and a corresponding one of the first variable-resistance elements; and a second switching element connected between the third conductor and a corresponding one of second variable-resistance elements. 2. The storage device according to 3. The storage device according to 4. The storage device according to 5. The storage device according to 6. The storage device according to the plurality of first variable-resistance elements is arranged in a first plane parallel to the first direction and the second direction, the plurality of second variable-resistance elements is arranged in a second plane parallel to the first direction and the second direction, the second plane spaced from the first plane in a third direction orthogonal to the first and second planes, the first switching element is connected to first variable-resistance elements adjacent to each other along the second direction, and the second switching element is connected to second variable-resistance elements adjacent to each other along the first direction. 7. The storage device according to the first switching element is connected to an upper surface of at least two first variable-resistance elements adjacent to each other in the second direction, a bottom surface of the second conductor is connected to the first switching element, the second switching element is connected an upper surface of at least two second variable-resistance elements, and a bottom surface of the third conductor is connected to the second switching element. 8. The storage device according to the first switching element is connected an upper surface of at least two of first variable-resistance elements, a bottom surface of the second conductor is connected to the first switching element, an upper surface of the second conductor is connected to the second switching element, and a bottom surface of at least two second variable-resistance elements is connected to the second switching element. 9. The storage device according to the first switching element is connected to an upper surface of the first conductor and a bottom surface of at least two of first variable-resistance elements, and the second switching element is connected to an upper surface of at least two second variable-resistance elements and a bottom surface of the third conductor. 10. The storage device according to the plurality of first variable-resistance elements are arranged in a matrix pattern along the first direction and the second direction, and the plurality of second variable-resistance elements are arranged in a matrix pattern along the first direction and the second direction. 11. The storage device according to the plurality of first variable-resistance elements are in a zigzag pattern along at least one of the first and second directions, and the plurality of second variable-resistance elements are in a zigzag pattern along at least one of the first and second directions. 12. The storage device according to 13. A storage device, comprising:

a first conductor extending along a first direction; a plurality of first variable-resistance elements arranged in a zigzag pattern above the first conductor; a second conductor extending along a second direction above the plurality of first variable-resistance elements; a plurality of second variable-resistance elements arranged in a zigzag pattern above the second conductor; a third conductor extending along the first direction above the plurality of second variable-resistance elements; a first switching element connected to at least two of the plurality of first variable-resistance elements; and a second switching element connected to at least two of the plurality of second variable-resistance elements. 14. The storage device according to the plurality of first variable-resistance elements includes a first row of the first variable-resistance elements arranged along the first direction and a second row of the first variable-resistance elements arranged along the first direction, and coordinates along first axis for the first variable-resistance elements of the first row is offset from coordinates along the first direction for the first variable-resistance elements in the second row. 15. The storage device according to the plurality of first variable-resistance elements are arranged in a first plane parallel to the first direction and the second direction, the plurality of second variable-resistance elements are arranged in a second plane parallel to the first direction and the second direction, the second plane spaced from the first plane in a third direction orthogonal to the first and second planes, the first switching element is connected to first variable-resistance elements adjacent to each other in the zigzag pattern along the second direction, and the second switching element is connected to the second variable-resistance elements adjacent to each other in the zigzag pattern along the first direction. 16. The storage device according to the first switching element is connected to an upper surface of at least two of first variable-resistance elements, a bottom surface of the second conductor is connected to the first switching element, the second switching element is connected to an upper surface of at least two second variable-resistance elements, and a bottom surface of the third conductor is connected to the second switching element. 17. The storage device according to the first switching element is connected an upper surface of at least two first variable-resistance elements, a bottom surface of the second conductor is connected to the first switching element, the second switching element is connected to an upper surface of the second conductor, and the second switching element is connected to a bottom surface of at least two second variable-resistance elements. 18. The storage device according the first switching element is connected to an upper surface of the first conductor, the first switching element is connected to a bottom surface of at least two first variable-resistance elements, the second switching element is connected to an upper surface of at least two second variable-resistance elements, and the second switching element is connected to a bottom surface of the third conductor. 19. The storage device according to the first switching element is connected to an upper surface of the first conductor, the first switching element is connected to a bottom surface of at least two first variable-resistance elements, the second switching element is connected to an upper surface of the second conductor, and the second switching element is connected to a bottom surface of at least two second variable-resistance elements. 20. The storage device according to the first switching element permits a current to flow when a voltage having a magnitude greater than or equal to a first value is applied across the first switching element, and the second switching element permits a current to flow when a voltage having a magnitude greater than or equal to a second value is applied across the second switching element.CROSS-REFERENCE TO RELATED APPLICATION

FIELD

BACKGROUND

DESCRIPTION OF THE DRAWINGS

DETAILED DESCRIPTION

First Embodiment

Second Embodiment

Third Embodiment

Fourth Embodiment

Fifth Embodiment

Sixth Embodiment

Seventh Embodiment

Eighth Embodiment

Ninth Embodiment

Tenth Embodiment

Eleventh Embodiment

Twelfth Embodiment

Thirteenth Embodiment

Fourteenth Embodiment

Modification Example