MEMRISTOR AND METHOD FOR MANUFACTURING SAME

本发明属于半导体器件领域,具体来讲,涉及一种忆阻器及其制作方法。 突触可塑性是学习与记忆的重要分子基础,因此突触仿生和突触可塑性模拟被认为是实现高效类脑人工神经网络的第一步。忆阻器作为第四种基本电路元件,拥有独特的类神经突触非线性电学传输特性,它的出现和发展为实现这一目标提供了可能。突触和忆阻器有着十分相似的传输特性,单个忆阻器便可能模拟一个突触的基本功能;与传统使用的由多个晶体管和电容器相结合的互补金属氧化物半导体(CMOS)来模拟一个突触相比,忆阻器减少了很多能耗,也降低了集成电路的复杂性。 忆阻器是非线性、无源、双端电学器件,其具有或展现作为偏置历史的函数的瞬态电阻水平,其最大的特点为:它的电阻值非恒定,而是随着外加电压或电流的大小、极性而发生变化,并且这些变化具有非易失性,可以在很长一段时间内被保留下来。 传统的忆阻器通常是采用从上至下依次为顶电极、中间介质层、底电极的三明治结构,通常采用电子束蒸发、热蒸发、磁控溅射等真空气相沉积制备,通过调节两个金属电极层之间的电压来改变电阻,实现低阻态和高阻态,制备工艺较为复杂。目前忆阻器的研究主要基于氧化物材料的体系,其工作机理主要依赖离子、氧空位在电场作用下迁移和聚集。然而,基于离子、氧空位迁移的过程速度较慢,很难在顶电极和底电极之间形成导电丝,给低阻态的实现造成了阻碍,得不到很高的开关比,所需偏置电压很大造成功耗大,且受到热效应的影响而使得稳定性较差,随机性很大,难以控制,且很容易受到外界环境的影响,这些都限制了忆阻器的发展。 发明内容 为解决上述现有技术存在的问题,本发明提供了一种忆阻器及其制作方法,该忆阻器通过设置同一平面上的两部分电极功能层,并利用纳米线或纳米带实 现二者之间的电子导通,能够使该忆阻器在循环的正负电压下进行高电阻和低电阻切换,并且得到高HRS/LRS(高电阻值/低电阻值)值。 为了达到上述发明目的,本发明采用了如下的技术方案: 一种忆阻器,包括衬底以及设置在所述衬底上的间隔的第一电极功能层和第二电极功能层;其中,所述第一电极功能层和所述第二电极功能层之间通过纳米线或纳米带连接以实现电子导通。 可选地,所述第一电极功能层和所述第二电极功能层之间的最小宽度为50nm~50μm。 可选地,所述第一电极功能层远离所述衬底的顶面和所述第二电极功能层的远离所述衬底的顶面齐平,并且所述纳米线或纳米带的顶面不低于所述第一电极功能层及所述第二电极功能层的顶面。 可选地,所述第一电极功能层和所述第二电极功能层的厚度均为1nm~600nm;所述纳米线或纳米带的厚度为1nm~1000nm。 可选地,所述纳米线或纳米带的材料为Ge2Sb2-xBixTe5;其中,0≤x≤2。

可选地,所述第一电极功能层和所述第二电极功能层的材料均选自Ag、Cu、Al、Zn、Fe、Mg、Na、Sn中的任意一种。 可选地,所述忆阻器还包括设置在所述衬底和所述第一电极功能层之间的第一导电电极、以及设置在所述衬底和所述第二电极功能层之间的第二导电电极。 可选地,所述第一导电电极和所述第二导电电极的材料均选自Pt、Ni、Mn、Mo、Nb、Pd、Ru、RuO2、Ta、TaN、W、WN、Ti及钛的氧化物中的任意一种;和/或,所述第一导电电极和所述第二导电电极的厚度均为1nm~600nm。

可选地,所述忆阻器还包括设置在所述衬底和所述第一导电电极之间的第一电极吸附层、以及设置在所述衬底和所述第二导电电极之间的第二电极吸附层。 可选地,所述第一电极吸附层和所述第二电极吸附层的材料均选自Cr、Ti、Ni中的任意一种;和/或,所述第一电极吸附层和所述第二电极吸附层的 厚度均为0.1nm~100nm。 可选地,所述忆阻器还包括环绕设置于所述第一电极功能层和所述第二电极功能层周围的阻变层。 可选地,所述阻变层的材料为Ge2Sb2-xBixTe5;其中,0≤x≤2。

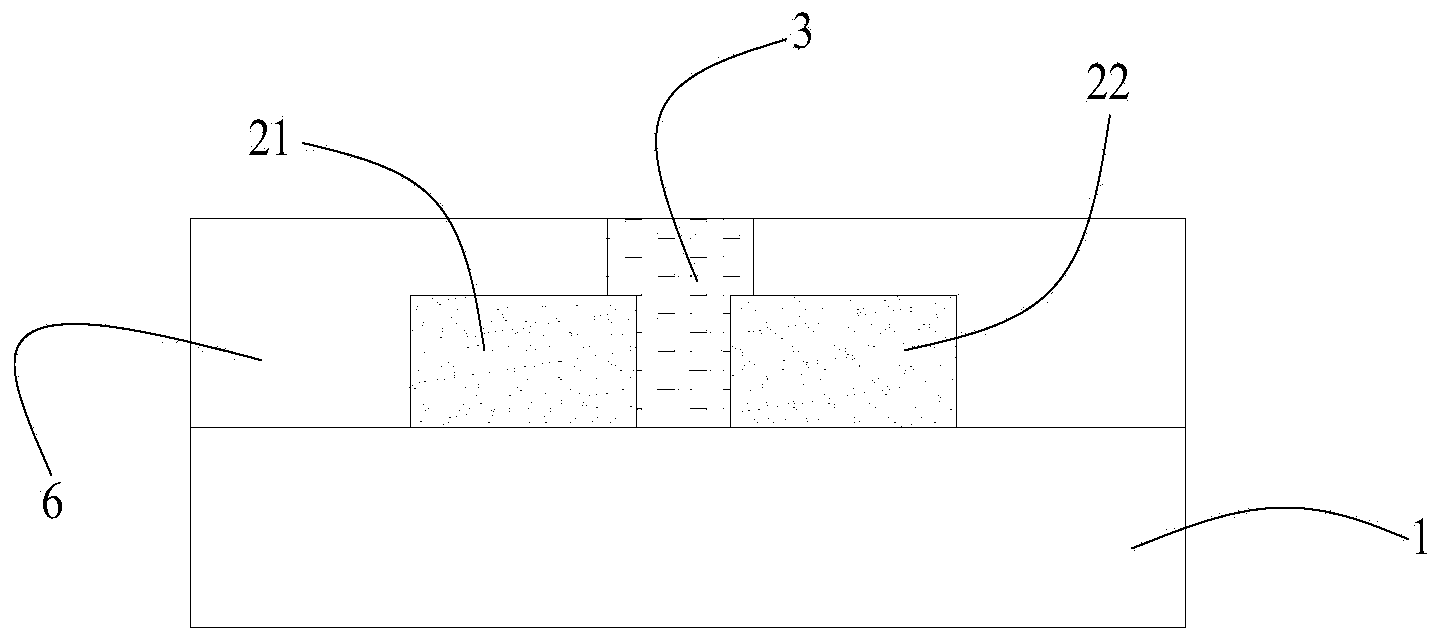

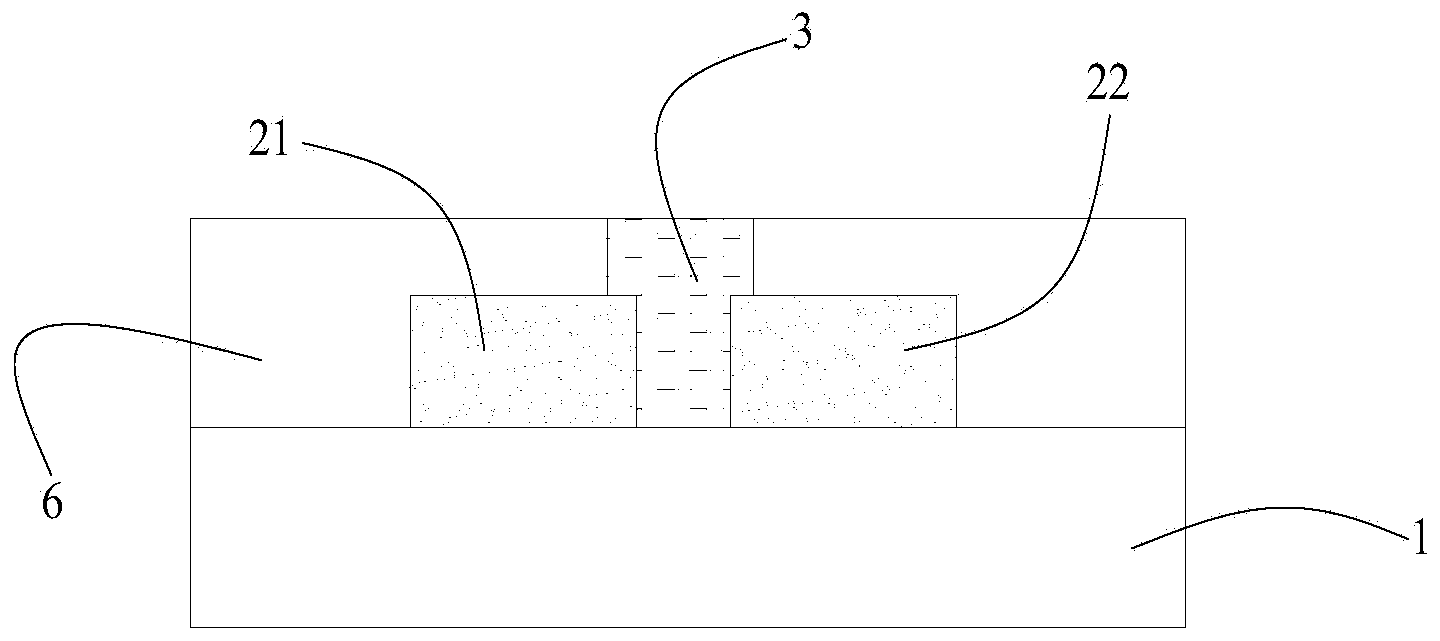

可选地,所述阻变层的远离所述衬底的顶面与所述纳米线或纳米带的顶面齐平。 本发明的另一目的还在于提供了一种如上任一所述的忆阻器的制作方法,其包括步骤: S1、在衬底上制作间隔的第一电极功能层和第二电极功能层; S2、至少在所述第一电极功能层和所述第二电极功能层之间沉积阻变材料,以形成阻变源层; S3、采用飞秒激光于所述第一电极功能层和所述第二电极功能层之间的阻变源层上进行划线,在所述第一电极功能层和所述第二电极功能层之间形成纳米线或纳米带;其中, 若要求所述忆阻器的开关比不低于1000,则去除非划线区域的阻变源层; 若要求所述忆阻器的开关比小于1000,则不去除或部分去除非划线区域的阻变源层。 本发明通过在衬底上的同一平面上设置两部分间隔的电极功能层,并利用纳米线或纳米带实现二者之间的电子导通,能够保证该忆阻器在循环的正负电压下进行高电阻和低电阻切换,并且得到高HRS/LRS(高电阻值/低电阻值)值。本发明的忆阻器改变了传统的“三明治结构”的忆阻器。本发明的具有全新结构的忆阻器的制作方法简化了工艺,也使器件的测试更为便利。 通过结合附图进行的以下描述,本发明的实施例的上述和其它方面、特点和优点将变得更加清楚,附图中: 图1是根据本发明的第一种忆阻器的剖面结构示意图; 图2是根据本发明的第二种忆阻器的剖面结构示意图; 图3是根据本发明的第三种忆阻器的剖面结构示意图; 图4-图6是根据本发明的第一种忆阻器的制作方法的工艺流程图; 图7-图8是根据本发明的第二种忆阻器的制作方法的局部工艺流程图; 图9-图11是根据本发明的第三种忆阻器的制作方法的局部工艺流程图; 图12是根据本发明的实施例1的忆阻器电流-电压特性曲线; 图13是根据本发明的实施例2的忆阻器电流-电压特性曲线。 以下,将参照附图来详细描述本发明的实施例。然而,可以以许多不同的形式来实施本发明,并且本发明不应该被解释为限制于这里阐述的具体实施例。相反,提供这些实施例是为了解释本发明的原理及其实际应用,从而使本领域的其他技术人员能够理解本发明的各种实施例和适合于特定预期应用的各种修改。在附图中,为了清楚起见,可以夸大元件的形状和尺寸,并且相同的标号将始终被用于表示相同或相似的元件。 将理解的是,尽管在这里可使用术语“第一”、“第二”等来描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件区分开来。 基于现有技术中忆阻器一般所具有的“三明治结构”,其将导致难以在顶电极和底电极之间形成导电丝,从而给低阻态的实现造成阻碍,得不到很高的开关比,所需偏置电压很大造成功耗大,且受到热效应的影响而使得稳定性较差,随机性很大,难以控制,且很容易受到外界环境的影响。为此,本发明提供了具体全新结构的忆阻器。 具体参阅图1,本发明提供了第一种结构的忆阻器,其包括衬底1以及设置在该衬底1上的间隔的第一电极功能层21和第二电极功能层22;其中,第一电极功能层21和第二电极功能层22之间通过纳米功能部3连接以实现电子导通。 在该忆阻器中,第一电极功能层21和第二电极功能层22的材料可具体选自Ag、Cu、Al、Zn、Fe、Mg、Na、Sn中的任意一种。 如此,该第一电极功能层21和第二电极功能层22内的金属离子能够更好地通过纳米功能部3形成导电通路,从而加快了该忆阻器低阻态的形成、并增强了器件循环稳定性,大大提高了电阻变化率(即开关比),提升了该忆阻器的性能。 根据第一电极功能层21及第二电极功能层22的具体材料选择,为了获得更好的导电效果,本发明还提供了第二种结构的忆阻器。 具体参阅图2,该第二种结构的忆阻器在与图1所示的第一种结构的忆阻器的基础上,还包括设置在衬底1和第一电极功能层21之间的第一导电电极41、以及设置在衬底1和第二电极功能层22之间的第二导电电极42。 可选择地,第一导电电极41和第二导电电极42的材料可具体选自Pt、Ni、Mn、Mo、Nb、Pd、Ru、RuO2、Ta、TaN、W、WN、Ti及钛的氧化物中的任意一种。

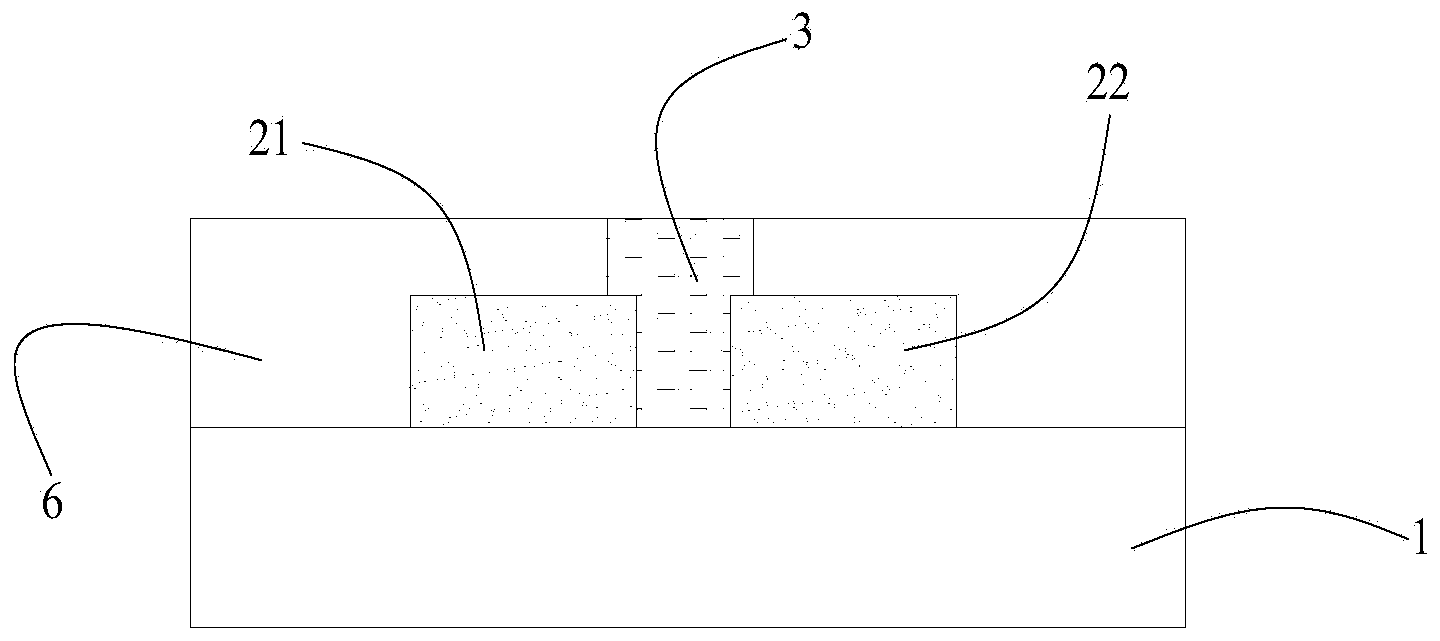

可选择地,控制第一导电电极41和第二导电电极42的厚度均为1nm~600nm即可。 进一步地,根据第一导电电极41和第二导电电极42的具体材料选择,为了防止二者与衬底1的附着力不够、易于脱落,本发明还提供了第三种结构的忆阻器。 具体参阅图3,该第三种结构的忆阻器在与图2所示的第二种结构的忆阻器的基础上,还包括设置在衬底1和第一导电电极41之间的第一电极吸附层51、以及设置在衬底1和第二导电电极42之间的第二电极吸附层52。 可选择地,第一电极吸附层51和第二电极吸附层52的材料可具体选自Cr、Ti、Ni中的任意一种。 可选择地,控制第一电极吸附层51和第二电极吸附层52的厚度均为0.1nm~100nm即可。 换句话说,本发明的忆阻器在衬底1上形成了相互分隔不连接的两部分导电功能层。该导电功能层具体为电极功能层21、22;或具体为依次叠层的导电电极41、42和电极功能层21、22,或具体为依次叠层的电极吸附层51、52,以及导电电极41、42和电极功能层21、22。 可选择地,在上述三种结构的忆阻器中,还包括环绕设置在电极功能层21、 22周围的阻变层6。 具体来讲,参阅图1-图3,本发明提供的上述三种不同结构的忆阻器中,纳米功能部3具体指纳米线或纳米带。 并且,上述电极功能层21、22无需限制具体的形状,但二者之间的最小宽度控制为50nm~50μm。这是因为,若二者之间距离太近,则易导致短路,但若二者之间距离太远,则在使用过程中需要施加较大的电压,影响器件性能。 进一步地,考虑该忆阻器的制作工艺的方便,电极功能层21、22同时制作,导电电极41、42同时制作,电极吸附层51、52同时制作;因此,第一电极功能层21的远离衬底1的顶面和第二电极功能层22的远离衬底1的顶面齐平,并且纳米功能部3的顶面不低于电极功能层21、22的顶面。 进一步地,控制电极功能层21、22的厚度均为1nm~600nm、纳米功能部3的厚度为1nm~1000nm即可。 在本发明的忆阻器中,纳米功能部3的材料为Ge2Sb2-xBixTe5(0≤x≤2)。

基于本发明的忆阻器的制作工艺的方便,优选阻变层6与用于形成纳米功能部3的部分同时制作,因此阻变层6的材料与纳米功能部3的材料也相同,为Ge2Sb2-xBixTe5(0≤x≤2)。由此,阻变层6的远离衬底1的顶面即与纳米功能部3的顶面齐平。

以下将参照附图对本发明的上述忆阻器的制作方法进行详细的描述。 本发明的上述第一种结构的忆阻器的制作方法包括下述步骤: 在步骤S1中,在衬底1上制作间隔的第一电极功能层21和第二电极功能层22;如图4所示。 优选对衬底1首先进行预处理,以保证其表面的清洁;然后再在其上方制作电极功能层21、22。 一般来讲,依次使用丙酮、乙醇和去离子水分别超声清洗该衬底1大约15min,再用氮气吹干其表面即可。 所述衬底1可以是玻璃,也可以是含二氧化硅层的硅片;本发明中不作具体限定。 电极功能层21、22的制作可以首先采用光刻胶及掩膜版进行图形化处理, 以形成用于制作电极功能层21、22的图形化区域,而该图形化区域的周边均还涂布有光刻胶;然后在图形化区域沉积,从而在衬底1上形成了电极功能层21、22;最后去除电极功能层21、22周边的光刻胶即可。 在步骤S2中,至少在第一电极功能层21和第二电极功能层22之间沉积阻变材料,以形成阻变源层6a;如图5所示。 具体来讲,在电极功能层21、22上沉积阻变材料,以在二者之间、优选环绕二者的阻变源层6a;并优选控制该阻变源层6a的顶面高于电极功能层21、22的顶面,以将二者完全覆盖。 在步骤S3中,采用飞秒激光于第一电极功能层21和第二电极功能层22之间的阻变源层6a上进行划线,在第一电极功能层21和第二电极功能层22之间形成纳米功能部3;如图6所示。 需要说明的是,当进行飞秒激光的划线之后,会形成划线区域和非划线区域;其中,划线区域即所述纳米功能部3,而针对非划线区域,则根据所要制作的忆阻器的开关比要求,来选择性地去除非划线区域的阻变源层。具体来讲,若要求忆阻器的开关比不低于1000,则去除非划线区域的阻变源层;而若要求忆阻器的开关比小于1000,则不去除或部分去除非划线区域的阻变源层。 如此,即通过飞秒激光的划线使得电极功能层21、22之间的阻变源层6a形成了一条或多条纳米线或纳米带的纳米功能部3,从而保证电极功能层21、22内的金属离子能够更好地通过纳米功能部3形成导电通路,从而加快了该忆阻器低阻态的形成、并增强了器件循环稳定性,大大提高了电阻变化率(即开关比),提升了该忆阻器的性能。与此同时,飞秒激光的划线操作还对阻变源层6a照射了紫外光,为阻变源层6a提供了能量,以获得更好的器件性能。 在上述步骤的基础上,为了制作本发明的上述第二种结构的忆阻器,其在步骤S1中,具体包括首先在衬底1上制作间隔的第一导电电极41和第二导电电极42;如图7所示。然后在第一导电电极41上制作第一电极功能层21,在第二导电电极42上制作第二电极功能层22;如图8所示。 进一步在上述步骤的基础上,为了制作本发明的上述第三种结构的忆阻器,其在步骤S1中,具体包括首先在衬底1上制作间隔的第一电极吸附层51和第二电极吸附层52;如图9所示。然后在第一电极吸附层51上制作第一导电电 极41,在第二电极吸附层52上制作第二导电电极42;如图10所示。最后在第一导电电极41上制作第一电极功能层21,在第二导电电极42上制作第二电极功能层22;如图11所示。 在上述第二种结构和第三种结构的忆阻器的制作方法中,其余步骤参照上述第一种结构的忆阻器的制备方法所述,可分别对应获得不同结构的忆阻器。 进一步地,上述步骤中所涉及的各结构层的源材料均与每一结构层的材料对应相同;如某忆阻器中第一电极功能层21的材料为Mg,即其第一电极功能层21的制作过程中,即沉积Mg即可。 以下将通过具体的实施例来说明本发明的上述忆阻器及其制作方法,但本发明并不限制于此;下述实施例仅是本发明所要求保护的忆阻器及其制作方法的具体示例。 实施例1 本实施例提供了一种如图3所示的忆阻器。 在本实施例的忆阻器中,衬底1的材料为尺寸规格为4英寸左右的单抛单氧化层的硅片。第一电极吸附层51和第二电极吸附层52均为5nm厚的铬薄膜;第一导电电极41和第二导电电极42均为50nm厚的金薄膜,第一电极功能层21和第二电极功能层22均为20nm厚的银薄膜;阻变层6和纳米功能部3均为100nm厚的Ge2Sb2Te5。

在本实施例的忆阻器中,其第一电极功能层21和第二电极功能层22之间的最窄间距为5μm。 以下具体描述本实施例的忆阻器的制作方法。 (1)提供一衬底1,并对该衬底1进行预处理;具体为依次使用丙酮、酒精和去离子水分别对衬底1进行约15min的超声清洗,并用氮气吹干。 (2)在衬底1上旋涂光刻胶NR9-1000p,于150℃下前烘3min,选择对称电极掩模板,利用光刻机紫外曝光40s,于100℃下后烘3min,然后于DPD-200中显影10s~15s,利用剥离工艺形成用于形成两部分导电功能层的图形化区域。 (3)首先,利用电子束蒸发工艺在图形化区域上制备5nm厚的铬薄膜作 为电极吸附层51、52;然后,利用热蒸发工艺在电极吸附层51、52上制备50nm厚的金薄膜作为导电电极41、42;再次,利用热蒸发工艺在导电电极41、42上制备20nm厚的银薄膜作为电极功能层21、22;本实施例中电子束蒸发的工作压强控制为5×10-3Pa;最后,利用丙酮浸泡15min以去除覆盖图形化区域外其他区域的光刻胶。

(4)采用磁控溅射的方法,在电极功能层21、22上沉积100nm厚的阻变材料Ge2Sb2Te5以作为阻变源层6a;具体来讲,以阻变材料Ge2Sb2Te5作为溅射靶材,以氩气作为溅射气氛、衬底温度为室温、溅射功率为40W、时间10min;在真空无氧气氛中室温条件下进行溅射处理即可。

(5)依据选定的对称电极掩膜版的尺寸,本实施例形成的电极功能层21、22之间的最短间隙为5μm;将其置于飞秒激光器下,用激光功率为0.47mW、扫描步长0.1μm的参数将电极功能层21、22之间的阻变源层6a划一条10μm的纳米线搭接在电极功能层21、22上,即获得本实施例中的忆阻器。 对本实施例的忆阻器的性能进行测试,具体来讲,将该忆阻器于手套箱中进行上述测试,其电流-电压特性曲线如图12所示。 从图12中可以看出,本实施例的忆阻器从-4V开始一直到3.8V,在有电压施加在该器件上时,其电阻呈现低阻态;而电压从3.8V开始,随着电压的减小其电阻骤增,并一直保持高阻态直到电压减到-4V。因此,本实施例的忆阻器具有高电阻变化率(开关比可达到8000)、高循环稳定性(开关比随着循环次数增加波动很小)和操作速度快等优异性能。 实施例2 在实施例2的描述中,与实施例1的相同之处在此不再赘述,只描述与实施例1的不同之处。实施例2与实施例1的不同之处在于,在实施例2的忆阻器中,第一导电电极41和第二导电电极42均为100nm厚的金薄膜,第一电极功能层21和第二电极功能层22均为50nm厚的铜薄膜;且第一电极功能层21和第二电极功能层22之间的最窄间距为10μm。 在本实施例的忆阻器的制作方法中,与实施例1中的制作方法的不同之处在于,在步骤(5)中,控制激光功率为0.62mW、扫描步长0.1μm的参数将电极功能层21、22之间的阻变源层6a划一条20μm的纳米线搭接在电极功能 层21、22上;其余参照实施例1中所述,即获得本实施例中的忆阻器。 对本实施例提供的忆阻器的性能进行测试。具体来讲,首先,将该忆阻器先浸泡于25%(wt%)的四甲基氢氧化铵溶液(TMAH)中50min,以去除纳米功能部3周围的其他阻变源层6a;然后在该忆阻器的远离衬底1的表面镀一层100nm的Al2O3作为隔离层,以防止其在测试过程中发生氧化;最后于手套箱中进行上述测试,其电流-电压特性曲线如图13所示。

从图13中可以看出,本实施例的忆阻器从-5.9V开始一直到5.8V,在有电压施加在器件上时,其电阻呈现低阻态;而电压从3.8V开始,随着电压的减小其电阻骤增,并一直保持高阻态直到电压减到-5.9V。因此,本实施例的忆阻器具有高电阻变化率(开关比可达到5000)、高循环稳定性(开关比随着循环次数增加波动很小)和操作速度快等优异性能。 虽然已经参照特定实施例示出并描述了本发明,但是本领域的技术人员将理解:在不脱离由权利要求及其等同物限定的本发明的精神和范围的情况下,可在此进行形式和细节上的各种变化。 A memristor and a method for manufacturing the same. The memristor comprises a substrate (1) and a first electrode functional layer (21) and a second electrode functional layer (22) disposed on the substrate and spaced apart from each other, wherein the first electrode functional layer and the second electrode functional layer are connected by means of a nanowire or nanoribbon so as to achieve electronic conduction. The present structure of the memristor is employed to change the conventional "sandwich structure" of memristors. In the present structure, two electrode functional layers spaced apart from each other are disposed on the same plane at a substrate, and achieve electronic conduction with each other by means of nanowires or nanoribbons, thereby ensuring that the memristor can be switched between high resistance and low resistance in positive and negative voltage cycles, and obtain a high resistance value (HRS) or a low resistance value (LRS). The method for manufacturing the memristor facilitates a simplified technique and easy testing. 一种忆阻器,其中,包括衬底以及设置在所述衬底上的间隔的第一电极功能层和第二电极功能层;其中,所述第一电极功能层和所述第二电极功能层之间通过纳米线或纳米带连接以实现电子导通。 根据权利要求1所述的忆阻器,其中,所述第一电极功能层和所述第二电极功能层之间的最小宽度为50nm~50μm。 根据权利要求1所述的忆阻器,其中,所述第一电极功能层和所述第二电极功能层的远离所述衬底的顶面齐平,并且所述纳米线或纳米带的顶面不低于所述第一电极功能层及所述第二电极功能层的顶面。 根据权利要求3所述的忆阻器,其中,所述第一电极功能层和所述第二电极功能层的厚度均为1nm~600nm;所述纳米线或纳米带的厚度为1nm~1000nm。 根据权利要求1所述的忆阻器,其中,所述纳米线或纳米带的材料为Ge2Sb2-xBixTe5;其中,0≤x≤2。

根据权利要求1所述的忆阻器,其中,所述第一电极功能层和所述第二电极功能层的材料均选自Ag、Cu、Al、Zn、Fe、Mg、Na、Sn中的任意一种。 根据权利要求6所述的忆阻器,其中,所述忆阻器还包括设置在所述衬底和所述第一电极功能层之间的第一导电电极、以及设置在所述衬底和所述第二电极功能层之间的第二导电电极。 根据权利要求7所述的忆阻器,其中,所述第一导电电极和所述第二导电电极的材料均选自Pt、Ni、Mn、Mo、Nb、Pd、Ru、RuO2、Ta、TaN、W、WN、Ti及钛的氧化物中的任意一种;所述第一导电电极和所述第二导电电极的厚度均为1nm~600nm。

根据权利要求7所述的忆阻器,其中,所述忆阻器还包括设置在所述衬底和所述第一导电电极之间的第一电极吸附层、以及设置在所述衬底和所述第二导电电极之间的第二电极吸附层。 根据权利要求9所述的忆阻器,其中,所述第一电极吸附层和所述第 二电极吸附层的材料均选自Cr、Ti、Ni中的任意一种;所述第一电极吸附层和所述第二电极吸附层的厚度均为0.1nm~100nm。 一种如权利要求1所述的忆阻器的制作方法,其中,包括步骤: S1、在衬底上制作间隔的第一电极功能层和第二电极功能层; S2、至少在所述第一电极功能层和所述第二电极功能层之间沉积阻变材料,以形成阻变源层; S3、采用飞秒激光于所述第一电极功能层和所述第二电极功能层之间的阻变源层上进行划线,在所述第一电极功能层和所述第二电极功能层之间形成纳米线或纳米带;其中, 若要求所述忆阻器的开关比不低于1000,则去除非划线区域的阻变源层; 若要求所述忆阻器的开关比小于1000,则不去除或部分去除非划线区域的阻变源层。 根据权利要求11所述的忆阻器的制作方法,其中,所述第一电极功能层和所述第二电极功能层之间的最小宽度为50nm~50μm。 根据权利要求11所述的忆阻器的制作方法,其中,所述第一电极功能层和所述第二电极功能层的远离所述衬底的顶面齐平,并且所述纳米线或纳米带的顶面不低于所述第一电极功能层及所述第二电极功能层的顶面。 根据权利要求13所述的忆阻器的制作方法,其中,所述第一电极功能层和所述第二电极功能层的厚度均为1nm~600nm;所述纳米线或纳米带的厚度为1nm~1000nm。 根据权利要求11所述的忆阻器的制作方法,其中,所述纳米线或纳米带的材料为Ge2Sb2-xBixTe5;其中,0≤x≤2。 根据权利要求11所述的忆阻器的制作方法,其中,所述第一电极功能层和所述第二电极功能层的材料均选自Ag、Cu、Al、Zn、Fe、Mg、Na、Sn中的任意一种。 根据权利要求16所述的忆阻器的制作方法,其中,所述忆阻器还包括设置在所述衬底和所述第一电极功能层之间的第一导电电极、以及设置在所述衬底和所述第二电极功能层之间的第二导电电极。 根据权利要求17所述的忆阻器的制作方法,其中,所述第一导电电极和所述第二导电电极的材料均选自Pt、Ni、Mn、Mo、Nb、Pd、Ru、RuO2、Ta、TaN、W、WN、Ti及钛的氧化物中的任意一种;所述第一导电电极和所述第二导电电极的厚度均为1nm~600nm。 根据权利要求17所述的忆阻器的制作方法,其中,所述忆阻器还包括设置在所述衬底和所述第一导电电极之间的第一电极吸附层、以及设置在所述衬底和所述第二导电电极之间的第二电极吸附层。 根据权利要求19所述的忆阻器的制作方法,其中,所述第一电极吸附层和所述第二电极吸附层的材料均选自Cr、Ti、Ni中的任意一种;所述第一电极吸附层和所述第二电极吸附层的厚度均为0.1nm~100nm。技术领域

背景技术

附图说明

具体实施方式