SEMICONDUCTOR STRUCTURE WITH IMPROVED METALLIZATION ADHESION AND METHOD FOR MANUFACTURING THE SAME

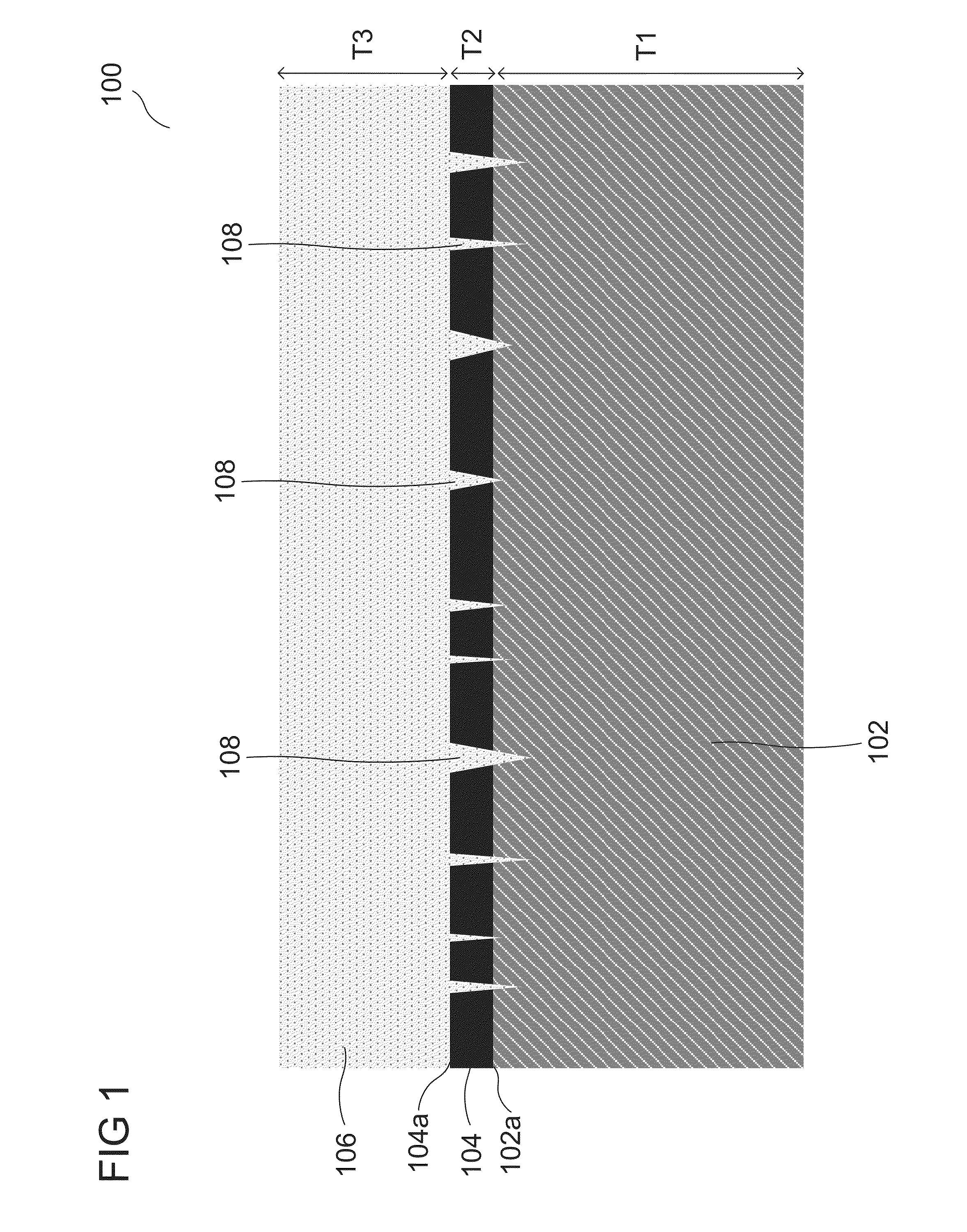

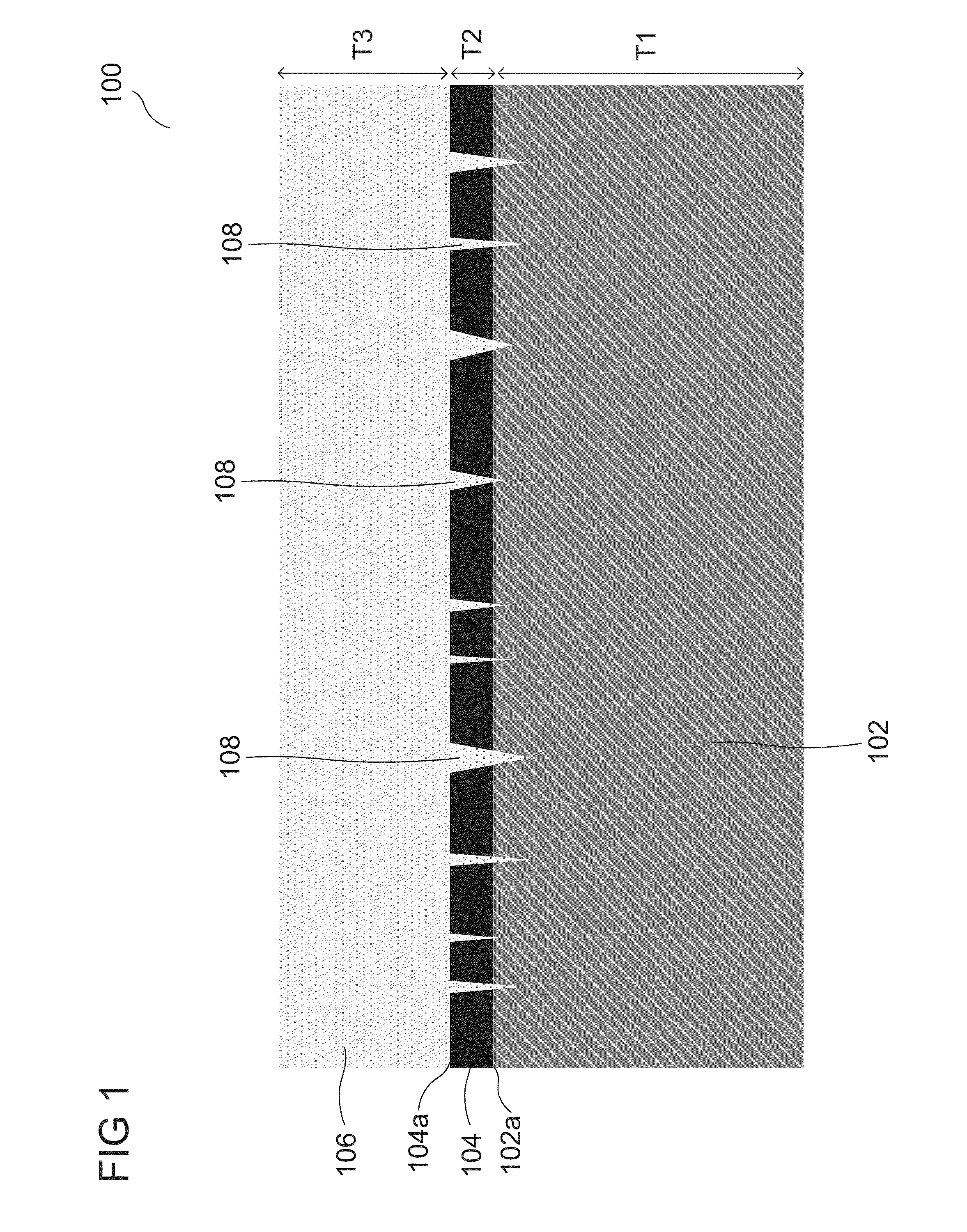

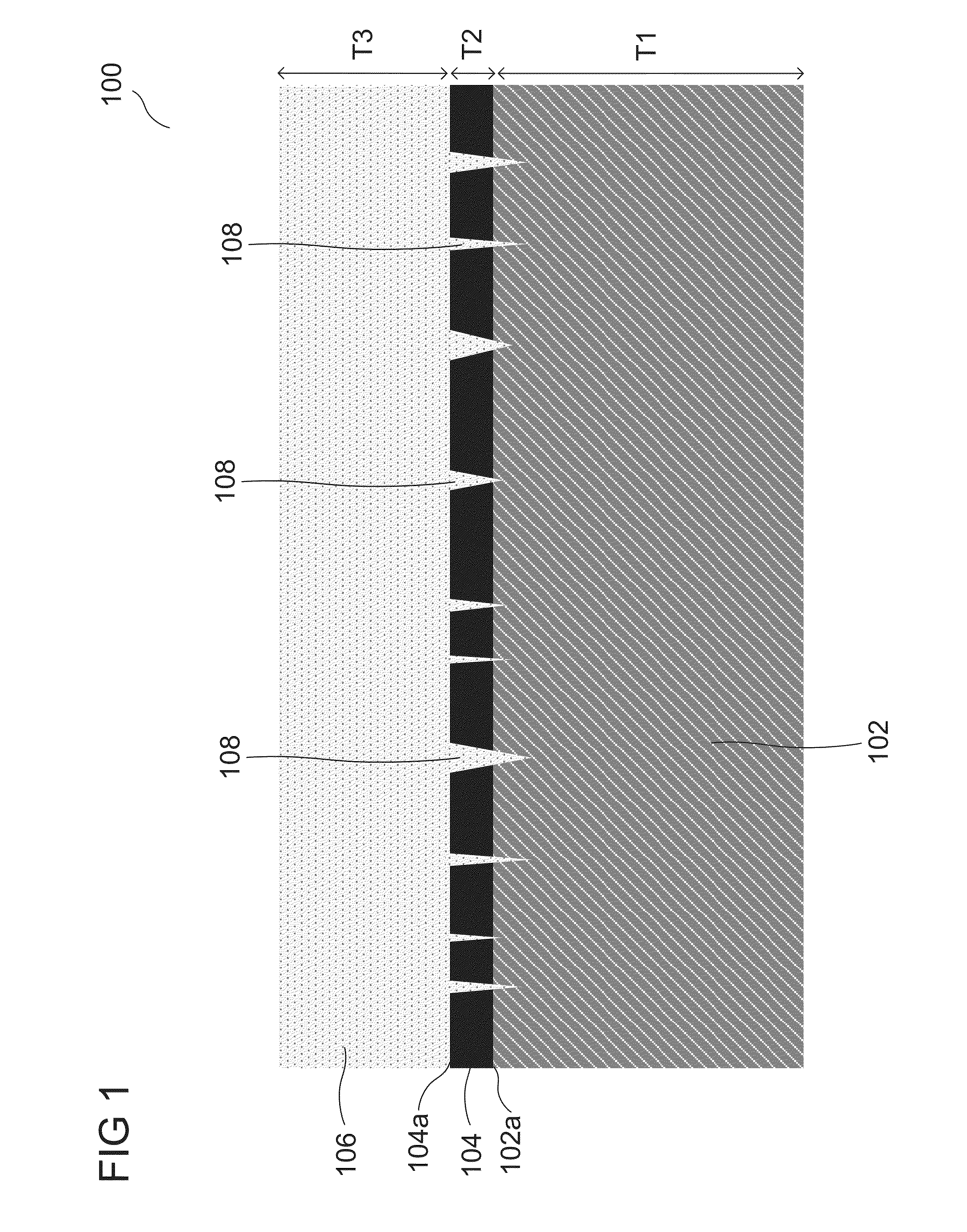

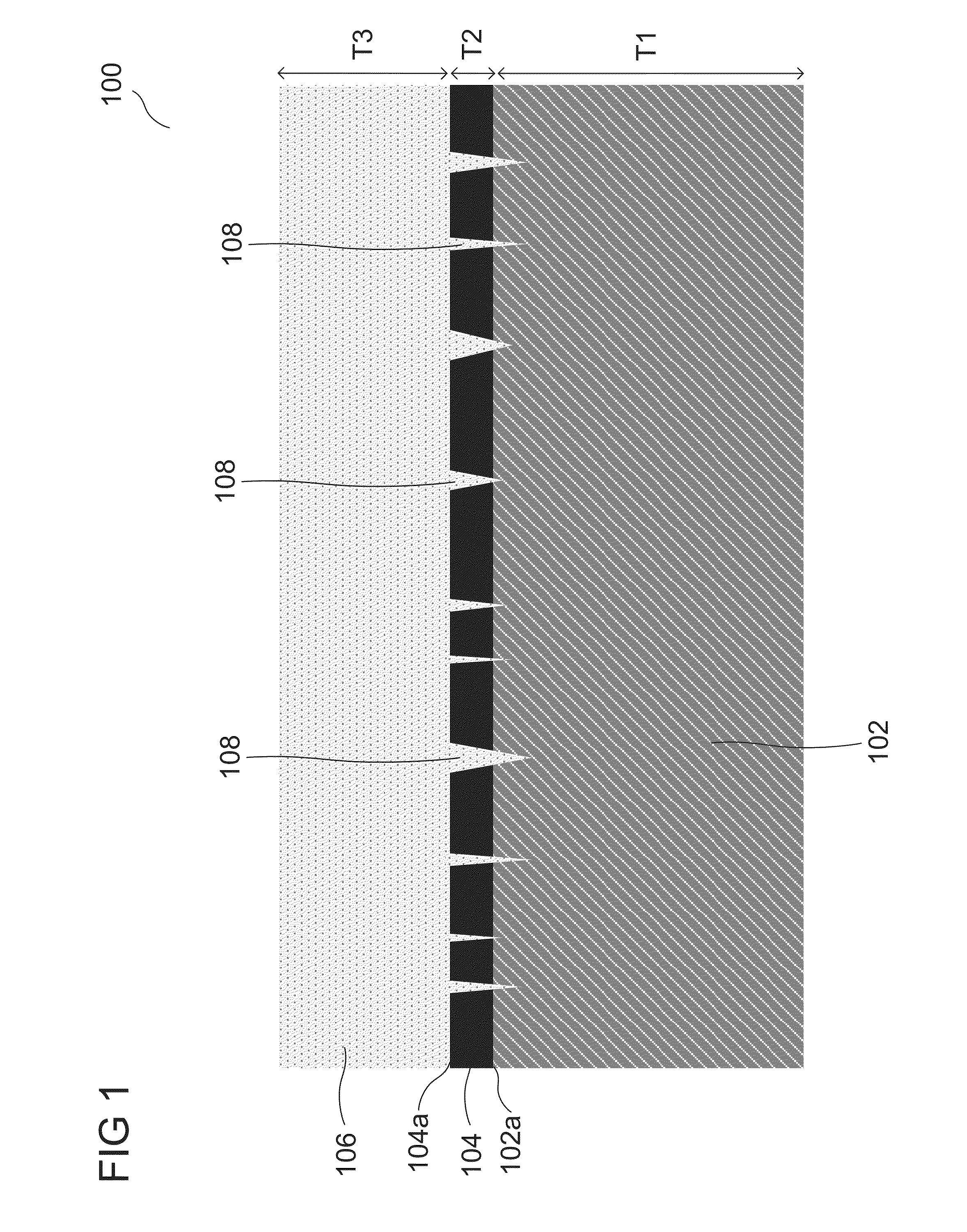

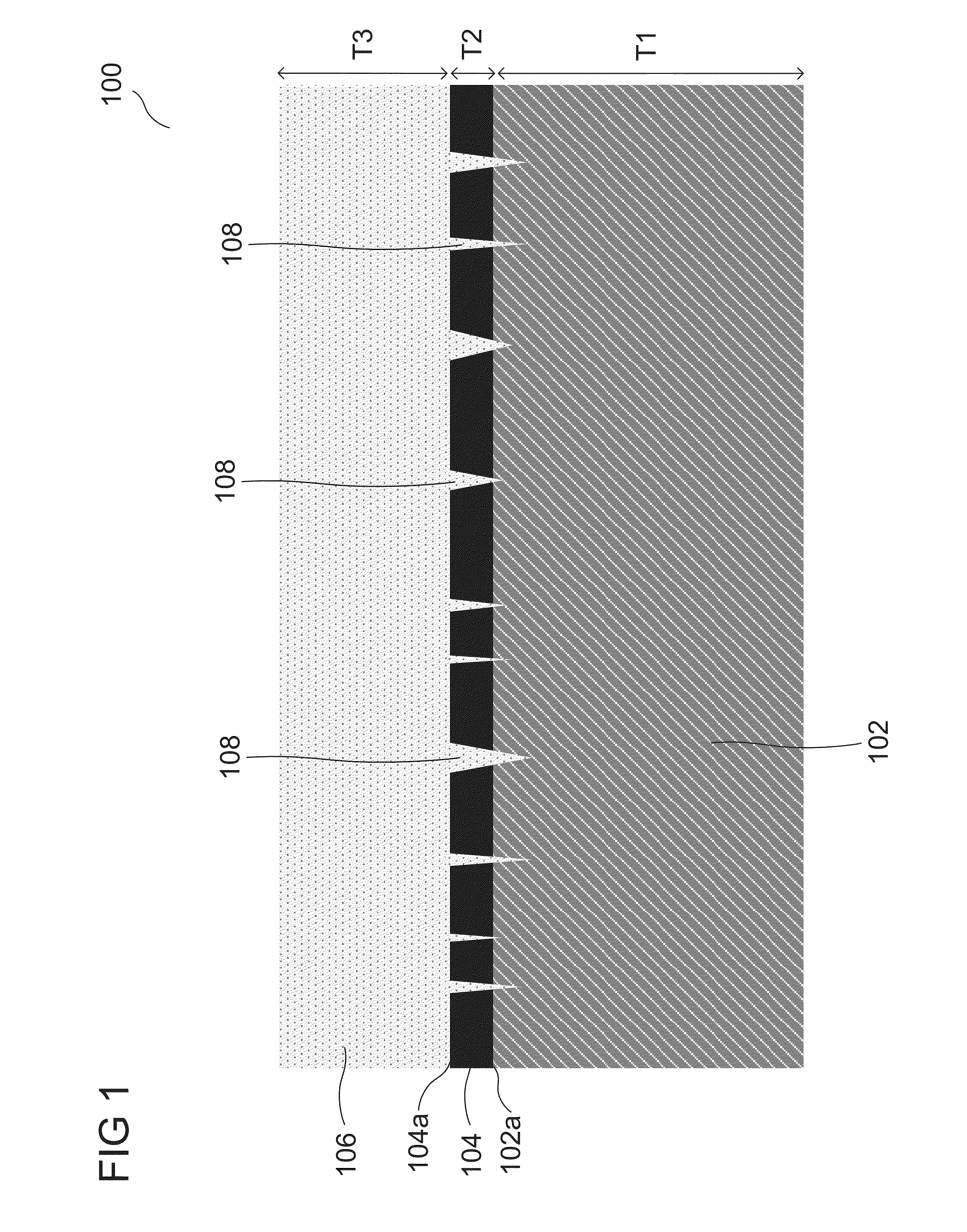

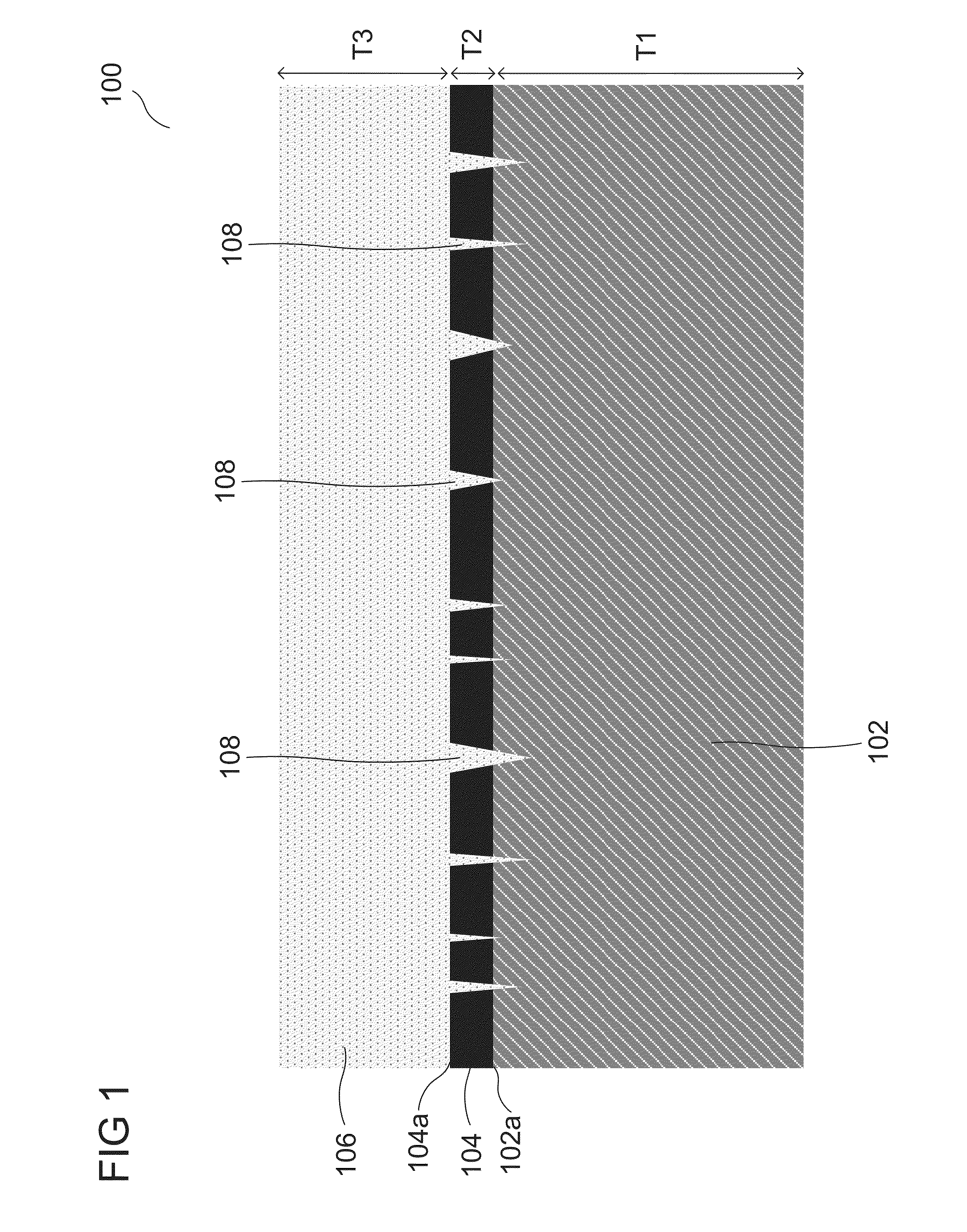

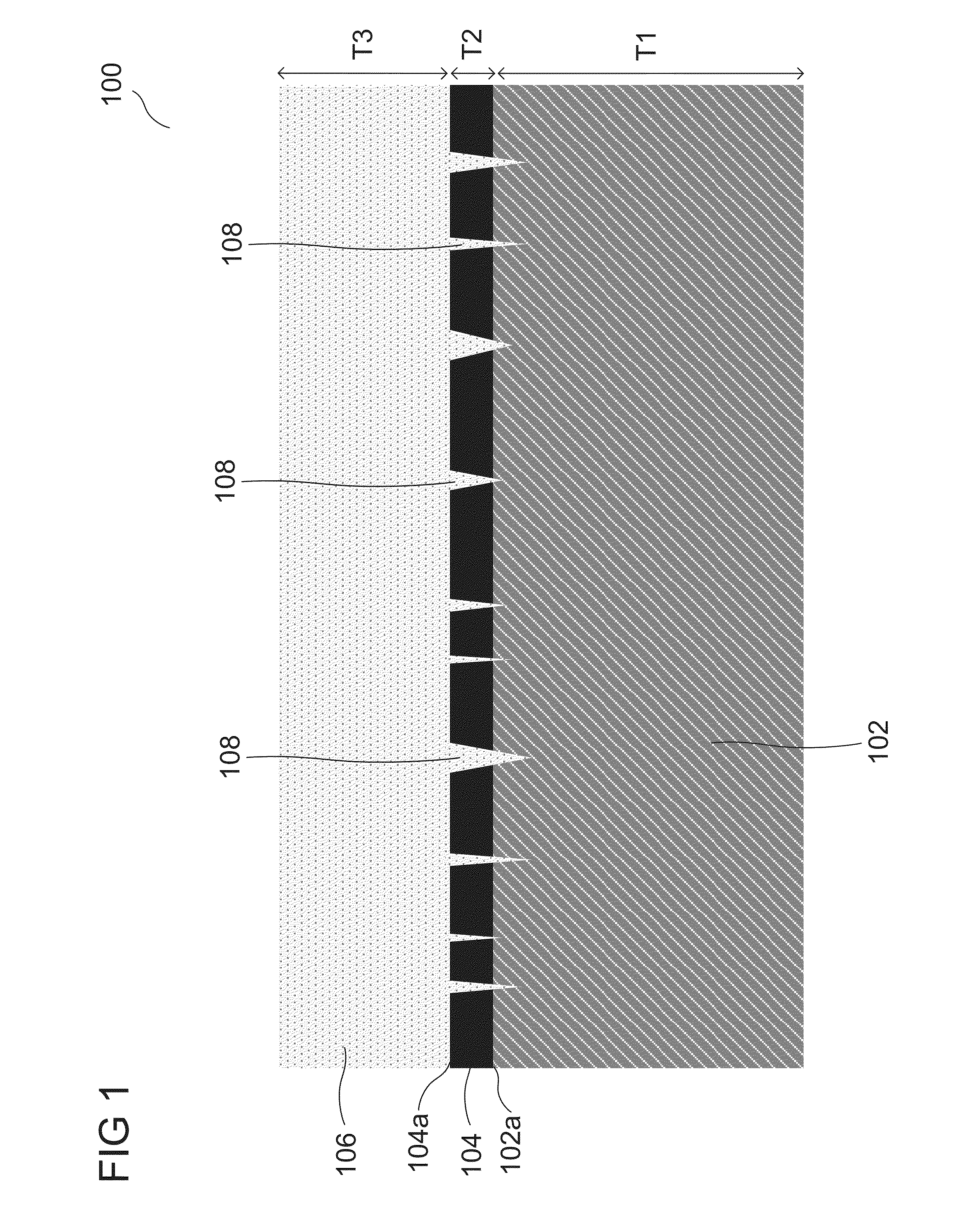

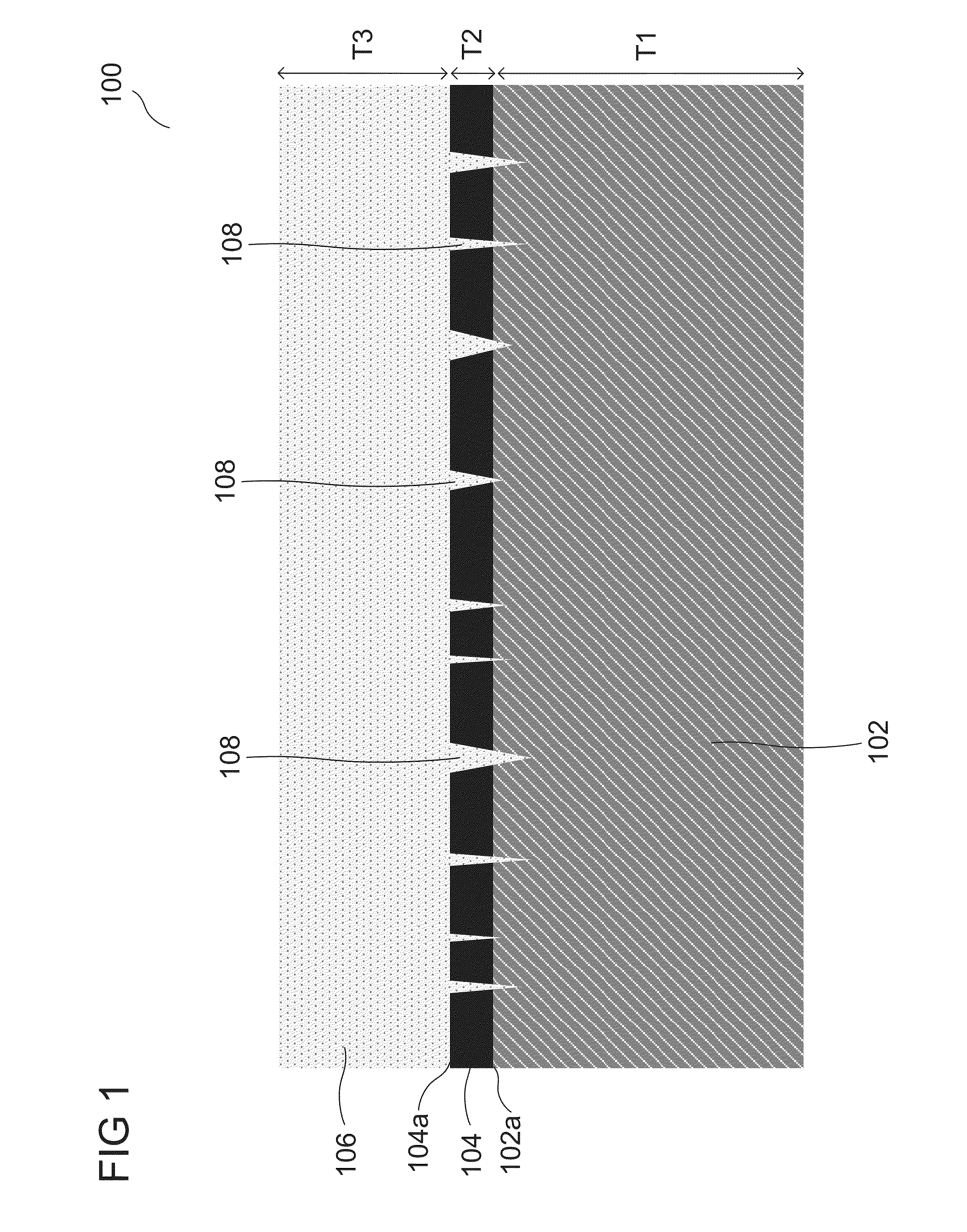

Various embodiments relate to a semiconductor structure with superior metallization adhesion compared to currently available technology and a method for manufacturing a semiconductor structure with superior metallization adhesion. Many semiconductor devices are constructed using a multi-layer stack structure wherein a metal or metallic material is adhered to a semiconductor material, silicon based power MOSFETs, for example. In the current technologies used to bond titanium to silicon, many current automated production techniques, e.g. mechanical sawing and vacuumed assisted chip pick up, may cause the backside metallization to “peel” off the semiconductor material. A currently available solution to prevent backside metallization peel off in silicon-titanium devices is to replace the titanium with another metal, such as an aluminum-copper-silicon composition. However, for many applications this solution may result in reduced device performance. In various embodiments, a semiconductor structure is provided. The semiconductor structure may include a substrate with a first layer formed on a first side of the substrate and a second layer formed over the first layer. In various embodiments, the second layer may include a plurality of substantially pointed structures which interpenetrate through the first layer and extend into the substrate. In the drawings, like reference characters generally refer to the same parts of the disclosure throughout the different views. The drawings are not necessarily to scale, emphasis instead generally being placed upon illustrating the principles of the disclosure. In the following description, various embodiments of the disclosure are described with reference to the following drawings, in which: The following detailed description refers to the accompanying drawings that show, by way of illustration, specific details and embodiments in which the disclosure may be practiced. The word “exemplary” is used herein to mean “serving as an example, instance, or illustration”. Any embodiment or design described herein as “exemplary” is not necessarily to be construed as preferred or advantageous over other embodiments or designs. The word “over” used with regards to a deposited material formed “over” a side or surface may be used herein to mean that the deposited material may be formed “directly on”, e.g. in direct contact with the implied side or surface. The word “over” used with regards to a deposited material formed “over” a side or surface may be used herein to mean that the deposited material may be formed “indirectly on” the implied side or surface with one or more additional layers being arranged between the implied side or surface and the deposited material. The term “carrier structure” as used herein should be understood to include various structures such as, e.g. a lead frame, a semiconductor substrate, such as a silicon substrate, a printed circuit board, and/or various flexible substrates. In various embodiments, a semiconductor device with improved backside metallization adhesion characteristics that can withstand modern automated manufacturing techniques is provided. According to various embodiments, as illustrated in In various embodiments, first conductive layer 104 may be formed of a conductive material such as a metallic material, a metalized material, a metal foil, an elemental metal, and/or a metal alloy. For example, the first conductive layer 104 may include or essentially consist of copper, nickel, tin, lead, silver, gold, aluminum, titanium, gallium, indium, boron, and various alloys of these metals such as e.g. cupronickel, nickel-aluminum, aluminum-copper-silicon, etc. In some embodiments, the first conductive layer 104 may be a multilayer substrate, e.g. a multilayer polymer, multilayer glass-ceramic, multilayer glass-ceramic copper, etc. Further, the first conductive layer 104 may include or essentially consist of other materials as may be desirable for a given application. According to various embodiments, the first conductive layer 104 may have a thickness, T2, in the range from about 20 nm to about 500 nm, e.g. in the range from about 20 nm to about 30 nm, e.g. in the range from about 30 nm to about 40 nm, e.g. in the range from about 40 nm to about 50 nm, e.g. in the range from about 50 nm to about 100 nm, e.g. in the range from about 100 nm to about 150 nm, e.g. in the range from about 150 nm to about 200 nm, e.g. in the range from about 200 nm to about 250 nm, e.g. in the range from about 250 nm to about 300 nm, e.g. in the range from about 300 nm to about 350 nm, e.g. in the range from about 350 nm to about 500 nm. According to various embodiments, the first conductive layer 104 may be deposited through various techniques, e.g. vapor deposition, an electrochemical process, and electroplating process, an electroless process, a chemical vapor deposition process, molecular beam epitaxy, spin coating, a sputter deposition, and/or various other techniques as may be desirable for a given application. In various embodiments, the first conductive layer 104 may be square or substantially square in shape. The first conductive layer 104 may be rectangular or substantially rectangular in shape. According to various embodiments, the first conductive layer 104 may be a circle or substantially circular in shape. The first conductive layer 104 may be an oval or substantially oval-like in shape. According to various embodiments, the first conductive layer 104 may be a triangle or substantially triangular in shape. The first conductive layer 104 may be a cross or substantially cross shaped. According to various embodiments, the first conductive layer 104 may be formed into any shape that may be desired for a given application. According to various embodiments, the second conductive layer 106 may have a thickness, T3, in the range from about 100 nm to about 5 μm, e.g. in the range from about 100 nm to about 200 nm, e.g. in the range from about 200 nm to about 300 nm, e.g. in the range from about 300 nm to about 500 nm, e.g. in the range from about 500 nm to about 1 μm, e.g. in the range from about 1 μm to about 5 μm. In some embodiments, the second conductive layer 106 may have a thickness T3 of at least about 100 nm, e.g. of at least 150 nm, e.g. of at least 200 nm, e.g. of at least 250 nm, e.g. of at least 300 nm. In at least one embodiment, the second conductive layer 106 may have a thickness T3 of less than or equal to about 2 μm, e.g. of less than or equal to 1.6 μm, e.g. of less than or equal to 1 μm, e.g. of less than or equal to 550 nm, e.g. of less than or equal to 500 nm. In various embodiments, the second conductive layer 106 may be square or substantially square in shape. The second conductive layer 106 may be rectangular or substantially rectangular in shape. According to various embodiments, the second conductive layer 106 may be a circle or substantially circular in shape. The second conductive layer 106 may be an oval or substantially oval-like in shape. According to various embodiments, the second conductive layer 106 may be a triangle or substantially triangular in shape. The second conductive layer 106 may be a cross or substantially cross shaped. According to various embodiments, the second conductive layer 106 may be formed into any shape that may be desired for a given application. The second conductive layer 106 may include or essentially consist of a conductive material, e.g. a metallic material, a metalized material, a metal foil, an elemental metal, and/or a metal alloy. For example, the second conductive layer 106 may include or essentially consist of copper, nickel, tin, lead, silver, gold, aluminum, titanium, gallium, indium, boron, and various alloys of these metals such as e.g. cupronickel, nickel-aluminum, aluminum-copper-silicon, etc. Further, the second conductive layer 106 may include or essentially consist of other materials as may be desirable for a given application. According to various embodiments, the second conductive layer 106 may be deposited through various techniques, e.g. vapor deposition, an electrochemical process, and electroplating process, an electroless process, a chemical vapor deposition process, molecular beam epitaxy, a lithography process, spin coating, a sputter deposition, and/or various other techniques as may be desirable for a given application. In various embodiments, the second conductive layer 106 may further include a plurality of spike-like structures 108. The spike-like structures 108 may at least partially permeate the first conductive layer 104. In other words, the spike-like structures 108 may extend from the second conductive layer 106 and partially penetrate the first conductive layer 104. The spike-like structures 108 may extend into and/or through a surface 104 According to an embodiment, as illustrated in According to various embodiments, the plurality of perforations 202 may be formed in through first conductive layer 104 using various techniques, e.g. laser drilling, various grinding techniques, deep reactive-ion etching, isotropic gas phase etching, vapor etching, wet etching, isotropic dry etching, plasma etching, various lithography techniques, etc. In various embodiments, each perforation 202 may be square or substantially square in shape. Each perforation 202 may be rectangular or substantially rectangular in shape. According to various embodiments, each perforation 202 may be a circle or substantially circular in shape. Each perforation 202 may be an oval or substantially oval-like in shape. According to various embodiments, each perforation 202 may be a triangle or substantially triangular in shape. Each perforation 202 may be a cross or substantially cross shaped. According to various embodiments, each perforation 202 may be formed into any shape that may be desired for a given application. In at least one embodiment, the distance, represented by reference numeral Si, across each perforation 202, may be in the range from about 0.5 μm to about 3.0 μm; e.g. in the range from about 0.5 μm to about 0.75 μm; e.g. in the range from about 0.75 μm to about 1.0 μm; e.g. in the range from about 1.0 μm to about 1.25 μm; e.g. in the range from about 1.25 μm to about 1.50 μm; e.g. in the range from about 1.50 μm to about 1.75 μm; e.g. in the range from about 1.75 μm to about 2.0 μm; e.g. in the range from about 2.0 μm to about 2.25 μm; e.g. in the range from about 2.25 μm to about 2.50 μm; e.g. in the range from about 2.50 μm to about 2.75 μm; e.g. in the range from about 2.75 μm to about 3.0 μm. According to various embodiments, the plurality of recesses 204 may be formed in the substrate 102 using various techniques, e.g. laser drilling, various grinding techniques, deep reactive-ion etching, isotropic gas phase etching, vapor etching, wet etching, isotropic dry etching, plasma etching, various lithography techniques, etc. In various embodiments, each recess 204 may be square or substantially square in shape. Each recess 204 may be rectangular or substantially rectangular in shape. According to various embodiments, each recess 204 may be a circle or substantially circular in shape. Each recess 204 may be an oval or substantially oval-like in shape. According to various embodiments, each recess 204 may be a triangle or substantially triangular in shape. Each recess 204 may be a cross or substantially cross shaped. According to various embodiments, each recess 204 may be formed into any shape that may be desired for a given application. In some embodiments, the plurality of recesses may not be necessary and/or may be excluded entirely from the semiconductor structure 100. According to an embodiment, as illustrated in According to various embodiments, the first conductive layer 104 may be implemented as a permeable bather layer. For example, a titanium layer which is sufficiently thin so that during an annealing process it becomes permeable to aluminum and/or silicon grains which may grow and/or be formed during the annealing. In an exemplary embodiment, the first conductive layer 104 may be implemented as a thin, permeable titanium bather layer. In an embodiment, this thin titanium bather layer may replace the titanium backside contact in a semiconductor diode. According to various embodiments, replacing the conventional titanium backside diode contact with a thinner, more permeable titanium layer may improve the adhesion of the backside metallization titanium to the silicon in the diode. In various embodiments, an aluminum based metal layer may be deposited over the permeable titanium layer and the diode may be subjected to various annealing processes similar to those described above. The annealing may cause various protrusions, growths, and/or spikes to form on the aluminum based metal layer. Many of these aluminum based spikes and/or protrusions may extend through the permeable titanium layer and penetrate into the silicon layer. This “spiking” may cause an increased and/or more robust adhesion between the titanium layer and the silicon in the diode. Various properties of the aluminum based spikes, e.g. length, thickness, extent of penetration into the silicon layer, etc., may be tailored and/or adjusted by altering the thickness of the permeable titanium layer. According to some embodiments, characteristics of the aluminum based spikes may be adjusted by changing the composition of aluminum based metal layer deposited over the permeable titanium layer. Further, in at least on embodiment, characteristics of the aluminum based spikes may be adjusted by regulating the so-called thermal budget of the annealing process. Additionally, in various embodiments, the characteristics of the aluminum based spikes may be adjusted so that the backside diode contact surface area occupied by the aluminum based spikes may only be a minor fraction of the total surface area of the backside diode contact. According to various embodiments, as illustrated in The substrate provided in method 400 may include or essentially consist of a semiconductor material such as germanium, silicon germanium, silicon carbide, gallium nitride, indium, indium gallium nitride, indium gallium arsenide, indium gallium zinc oxide, or other elemental and/or compound semiconductors, e.g. a III-V compound semiconductor such as e.g. gallium arsenide or indium phosphide, or a II-VI compound semiconductor or a ternary compound semiconductor or a quaternary compound semiconductor, as may be desired for a given application. The substrate of method 400 may include or may be composed of, for example, glass, and/or various polymers. The substrate of method 400 may be a silicon-on-insulator (SOI) structure. In some embodiments the substrate of method 400 may be a printed circuit board. According to various embodiments, the substrate of method 400 may be a flexible substrate, such as a flexible plastic substrate, e.g. a polyimide substrate. In various embodiments, the substrate of method 400 may be composed of or may include one or more of the following materials: a polyester film, a thermoset plastic, a metal, a metalized plastic, a metal foil, and a polymer. In various embodiments, the substrate of method 400 may be a flexible laminate structure. According to various embodiments, the substrate of method 400 may be a semiconductor substrate, such as a silicon substrate. The substrate of method 400 may include or essentially consist of other materials or combinations of material, for example various dielectrics, metals, and polymers as may be desirable for a given application. The first conductive layer of the method 400 may be formed of a metallic material, a metalized material, a metal foil, an elemental metal, and/or a metal alloy. For example, the first conductive layer of the method 400 may be composed of or may include copper, nickel, tin, lead, silver, gold, aluminum, titanium, gallium, indium, boron, and various alloys of these metals such as e.g. cupronickel, nickel-aluminum, aluminum-copper-silicon, etc. Further, the first conductive layer of method 400 may include or may be composed of other materials as may be desirable for a given application. The second conductive layer of the method 400 may be composed of or may include any of the materials listed above for the first conductive layer of the method 400. According to various embodiments, as illustrated in The following examples pertain to further embodiments. In Example 1, a semiconductor structure, which may include a substrate; a first conductive layer formed on a first side of the substrate; and a second conductive layer formed over the first conductive layer; the second conductive layer may include a plurality of substantially pointed structures which may interpenetrate through the first conductive layer and extend into the substrate. In Example 2, the semiconductor structure of Example 1, where the plurality of substantially pointed structures may increase an adhesion between the first conductive layer and the substrate. In Example 3, the semiconductor structure of Example 1 or 2, where the first conductive layer may have a thickness which is less than 25% of a thickness of the second conductive layer. In Example 4, the semiconductor structure of any one of Examples 1 to 3, where the first conductive layer may be implemented as a titanium layer. In Example 5, the semiconductor structure of any one of Examples 1 to 4, where the second conductive layer may be implemented as an aluminum-based layer. In Example 6, the semiconductor structure of any one of Examples 1 to 5, where the plurality of substantially pointed structures may occupy less than 10% of the surface area of a side of the first conductive layer which may be in contact with the first side of the substrate. In Example 7, a semiconductor structure, which may include a substrate; a first conductive layer formed over a first side of the substrate; a second conductive layer formed over the first conductive layer; a plurality of perforations in the first conductive layer; and a plurality of recesses in the substrate arranged to be coaxial with the plurality of perforations; where the second conductive layer may include a plurality of post-like structures which each extend through a perforation from said plurality and may be coupled to a surface of a recess from said plurality. In Example 8, the semiconductor structure of Example 7, where the plurality of post-like structures may increase an adhesion between the first conductive layer and the substrate. In Example 9, the semiconductor structure of Example 7 or 8, where the first conductive layer may be implemented as a titanium layer. In Example 10, the semiconductor structure of any one of Examples 7 to 9, where the second conductive layer may be implemented as an aluminum-based layer. In Example 11, the semiconductor structure of any one of Examples 7 to 10, where the plurality of post-like structures may occupy less than 10% of the surface area of a side of the first conductive layer which may be in contact with the first side of the substrate. In Example 12, a method of forming a semiconductor structure, which may include providing a substrate; depositing a first conductive layer on a first side of the substrate; depositing a second conductive layer over the first conductive layer; and shaping the second conductive layer to include a plurality of substantially pointed structures which may interpenetrate through the first conductive layer and extend into the substrate. In Example 13, the method of Example 12, where the plurality of substantially pointed structures may be formed through an annealing process. In Example 14, the method of Example 12 or 13, where the first conductive layer may have a thickness which is less than 25% of a thickness of the second conductive layer. In Example 15, the method of any one of Examples 12 to 14, where the plurality substantially pointed structures may be shaped to increase an adhesion between the first conductive layer and the substrate. In Example 16, a method of forming a semiconductor structure, which may include providing a substrate; forming a first conductive layer over a first side of the substrate; forming a second conductive layer over the first conductive layer; opening a plurality of perforations in the first conductive layer; and creating a plurality of recesses in the substrate and arranging said recesses to be coaxial with the plurality of perforations. In Example 17, the method of Example 16 may further include shaping the second conductive layer to include a plurality of post-like structures which each extend through a perforation from said plurality and are coupled to a surface of a recess from said plurality. In Example 18, the method of Example 16 or 17, where the first conductive layer may have a thickness which is less than 25% of a thickness of the second conductive layer. In Example 19, the method of any one of Examples 16 to 18, where the plurality of perforations and/or the plurality of recesses may be formed through one or more semiconductor device fabrication techniques. In Example 20, the method of any one of Examples 16 to 19, where the plurality post-like structures may be shaped to increase an adhesion between the first conductive layer and the substrate. A semiconductor structure is disclosed. The semiconductor structure may include a substrate, a first layer formed on a first side of the substrate and second layer formed over the first layer. The second layer may include a plurality of substantially pointed structures which interpenetrate through the first layer and extend into the substrate. A method for manufacturing a semiconductor structure is likewise disclosed. 1. A semiconductor structure, comprising:

a substrate; a first layer formed on a first side of the substrate; and a second layer formed over the first layer; the second layer comprising a plurality of substantially pointed structures which interpenetrate through the first layer and extend into the substrate. 2. The semiconductor structure of wherein the plurality of substantially pointed structures increases an adhesion between the first layer and the substrate. 3. The semiconductor structure of wherein the first layer has a thickness which is less than 25% of a thickness of the second layer. 4. The semiconductor structure of wherein the first layer comprises a titanium layer. 5. The semiconductor structure of wherein the second layer comprises an aluminum-based layer. 6. The semiconductor structure of wherein the plurality of substantially pointed structures occupy a fraction of the surface area of a side of the first layer which is in contact with the first side of the substrate. 7. A semiconductor structure, comprising:

a substrate; a first conductive layer formed over a first side of the substrate; a second conductive layer formed over the first conductive layer; a plurality of perforations in the first conductive layer; and a plurality of recesses in the substrate arranged to be coaxial with the plurality of perforations; wherein the second conductive layer comprises a plurality of post-like structures which each extend through a perforation from said plurality and are coupled to a surface of a recess from said plurality. 8. The semiconductor structure of wherein the plurality of post-like structures increase an adhesion between the first conductive layer and the substrate. 9. The semiconductor structure of wherein the first conductive layer comprises a titanium layer. 10. The semiconductor structure of wherein the second conductive layer comprises an aluminum-based layer. 11. The semiconductor structure of wherein the plurality of post-like structures occupy less than 10% of the surface area of a side of the first conductive layer which is in contact with the first side of the substrate. 12. A method of forming a semiconductor structure, the method comprising:

providing a substrate; depositing a first conductive layer on a first side of the substrate; depositing a second conductive layer over the first conductive layer; and shaping the second conductive layer to comprise a plurality of substantially pointed structures which interpenetrate through the first conductive layer and extend into the substrate. 13. The method of wherein the plurality of substantially pointed structures are formed through an annealing process. 14. The method of wherein the first conductive layer has a thickness which is less than 25% of a thickness of the second conductive layer. 15. The method of wherein the plurality substantially pointed structures are shaped to increase an adhesion between the first conductive layer and the substrate. 16. A method of forming a semiconductor structure, the method comprising:

providing a substrate; forming a first conductive layer over a first side of the substrate; forming a second conductive layer over the first conductive layer; opening a plurality of perforations in the first conductive layer; and creating a plurality of recesses in the substrate and arranging said recesses to be coaxial with the plurality of perforations. 17. The method of shaping the second conductive layer to comprise a plurality of post-like structures which each extend through a perforation from said plurality and are coupled to a surface of a recess from said plurality. 18. The method of wherein the first conductive layer has a thickness which is less than 25% of a thickness of the second conductive layer. 19. The method of wherein the plurality of perforations and/or the plurality of recesses are formed through one or more semiconductor device fabrication techniques. 20. The method of wherein the plurality post-like structures are shaped to increase an adhesion between the first conductive layer and the substrate.TECHNICAL FIELD

BACKGROUND

SUMMARY

BRIEF DESCRIPTION OF THE DRAWINGS

DESCRIPTION