CHIP PACKAGING METHOD AND CHIP PACKAGING STRUCTURE

本申请要求于2015年3月16日提交中国专利局、申请号为201510114089.9、发明名称为“芯片封装方法及芯片封装结构”的中国专利申请的优先权,其全部内容通过引用结合在本申请中。 本发明涉及半导体制造技术领域,尤其涉及一种芯片封装方法及芯片封装结构。 晶圆级芯片尺寸封装(Wafer Level Chip Size Packaging,WLCSP)技术是对晶圆进行封装测试后再切割得到单个成品芯片的技术,封装后的芯片尺寸与裸片完全一致。晶圆级芯片尺寸封装技术彻底颠覆了传统封装,例如陶瓷无引线芯片载具(Ceramic Leadless Chip Carrier)和有机无引线芯片载具(Organic Leadless Chip Carrier)等,顺应了市场对微电子产品日益轻、小、短、薄化和低价化的要求。经晶圆级芯片尺寸封装技术封装后的芯片尺寸能够达到高度微型化,芯片成本随着芯片尺寸的减小和晶圆尺寸的增加而显著降低。晶圆级芯片尺寸封装技术是可以将IC设计、晶圆制造、封装测试、基底制造整合为一体的技术,是当前封装领域的热点和未来的发展趋势。 扇出型晶圆级封装(Fan Out Wafer Level Packaging)技术是晶圆级封装技术中的一种。扇出型晶圆级封装的方法包括:在载体晶圆表面形成剥离薄膜;在剥离薄膜表面形成介质层;在所述介质层内形成再布线金属层以及金属电极;将芯片倒装至与所述金属电极电连接;在倒装所述芯片之后,在介质层和芯片表面形成塑封料层,所述塑封料层包围所述芯片,形成带有塑封料层的封装结构;将载体圆片和剥离膜与带有塑封料层的封装体分离,形成塑封圆片;植球回流,在暴露出的金属电极表面形成焊球凸点;单片切割,形成最终的扇

出芯片结构。 然而,现有的扇出晶圆级封装方法的封装质量、以及所形成的封装结构的集成度仍有待提高。 发明内容 本发明解决的问题是提供一种芯片封装方法及芯片封装结构,所形成的封装结构尺寸缩小,稳定性和可靠性提高。 为解决上述问题,本发明提供一种芯片封装方法,包括: 提供第一芯片,所述第一芯片包括相对的第一表面和第二表面,所述第一芯片的第一表面具有若干第一焊盘; 提供第二芯片,所述第二芯片包括相对的第三表面和第四表面,所述第二芯片的第三表面具有若干第二焊盘,且所述第二芯片的面积大于第一芯片的面积; 提供载板; 将所述第二芯片的第四表面与载板表面相结合; 将所述第一芯片的第二表面与所述第二芯片的第三表面相结合,所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外; 在所述载板表面形成封料层,所述封料层包覆所述第一芯片和第二芯片; 在所述封料层内形成第一导电结构和第二导电结构,所述第一导电结构与第一焊盘电连接,所述第二导电结构与第二焊盘电连接。 可选的,将所述第二芯片的第四表面与载板表面相结合的步骤包括:在所述载板表面形成胶合层;将所述第二芯片的第四表面固定于所述胶合层表面。 可选的,所述第一芯片的第二表面通过绝缘胶层与所述第二芯片的第三表面相结合。 可选的,所述封料层为感光干膜、非感光干膜或者塑封材料膜。

可选的,还包括:在所述封料层内形成若干分别暴露出若干第一焊盘的第一开口;在所述封料层内形成若干分别暴露出若干第二焊盘的第二开口。 可选的,所述第一导电结构和第二导电结构包括:位于所述第一开口的侧壁和底部表面、所述第二开口的侧壁和底部表面以及所述封料层的部分顶部表面的电互连层,所述电互连层填充满或不填充满所述第一开口或第二开口。 可选的,还包括:在所述封料层和电互连层表面形成阻焊层,所述阻焊层内具有若干第三开口,所述第三开口暴露出部分电互连层表面;在所述第三开口内形成凸块。 可选的,还包括:在形成所述封料层之后,去除所述载板,形成待处理衬底;对所述待处理衬底进行切割,形成若干独立的封装结构,所述封装结构包括相互结合的第一芯片和第二芯片、以及包覆所述第一芯片和第二芯片的封料层。 可选的,所述第一芯片的数量为一个或多个;所述第二芯片的数量为一个或多个。 可选的,当所述第一芯片的数量为多个时,若干第一芯片位于同一层或者多层重叠,且若干第一芯片分布于一个或多个第二芯片上;当所述第一芯片或第二芯片的数量为多个时,若干第一芯片或第二芯片的功能相同或不同。 相应的,本发明还提供一种采用上述任一项方法所形成的芯片封装结构,包括: 第一芯片,所述第一芯片包括相对的第一表面和第二表面,所述第一芯片的第一表面具有若干第一焊盘; 第二芯片,所述第二芯片包括相对的第三表面和第四表面,所述第二芯片的第三表面具有若干第二焊盘,且所述第二芯片的面积大于第一芯片的面积; 载板,所述第二芯片的第四表面与载板表面相结合; 所述第一芯片的第二表面与所述第二芯片的第三表面相结合,所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外;

位于所述载板表面的封料层,所述封料层包覆所述第一芯片和第二芯片; 位于所述封料层内的第一导电结构和第二导电结构,所述第一导电结构与第一焊盘电连接,所述第二导电结构与第二焊盘电连接。 与现有技术相比,本发明的技术方案具有以下优点: 本发明的方法中,提供第一芯片和第二芯片,且第一芯片的面积小于第二芯片的面积。由于所述第二芯片的第三表面具有第二焊盘,所述第一芯片的第一表面具有第一焊盘;将所述第二芯片的第四表面与载板表面相结合,能够暴露出所述第二焊盘;将所述第一芯片的第二表面与所述第二芯片的第三表面相结合,且所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外,则所述第一焊盘和第二焊盘均能够被暴露;因此,能够直接在所述载板上形成同时包覆第一芯片和第二芯片的封料层。 首先,所述第二芯片的第四表面与载板表面相结合,所述第一芯片的第二表面与第二芯片的第三表面相结合,使得第一芯片和第二芯片之间的结合更稳定,而且第一芯片和第二芯片之间的距离减小,有利于缩小封装结构的尺寸。 其次,由于所述封料层同时包覆第一芯片和第二芯片,因此降低了对第一芯片或第二芯片的厚度要求,所述第一芯片的厚度能够进一步减小,有利于使第一芯片和第二芯片的总厚度减小,则所形成的封装结构尺寸减小;此外,所述封料层的稳定性更佳,能够避免因形成多层封料层而发生的分层或开裂问题。 再次,在形成封料层之后,形成与第一焊盘电连接的第一导电结构、以及与第二焊盘电连接的第二导电结构,由于避免了多次形成多层导电结构的工艺步骤,使得第一导电结构和第二导电结构的形成工艺简单,而且避免了多层导电结构形成过程中的对位偏差问题;而且,由于对第一芯片和第二芯片的厚度要求减小,因此能够通过减小第一芯片的厚度,使塑封层到第二焊盘的距离减小,从而降低了形成第二导电结构的工艺难度,有利于降低第二导电结构与第二焊盘之间、以及第一导电结构与第一焊盘之间发生断路的概率,提高了所形成的封装结构的良率。

进一步,所述第二芯片的第四表面通过胶合层与载板表面相结合,所述第一芯片的第二表面通过绝缘胶层与所述第二芯片的第三表面相结合;不仅有利于使第一芯片与第二芯片的结合更稳定,还能够使第一芯片的第二表面到第二芯片的第三表面的距离减小,则有利于使所形成的封装结构的尺寸缩小。 本发明的结构中,由于所述第二芯片的第三表面具有第二焊盘,所述第一芯片的第一表面具有第一焊盘;所述第二芯片的第四表面与载板表面相结合,且所述第一芯片的第二表面与所述第二芯片的第三表面相结合,且所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外,则所述第一焊盘和第二焊盘均能够被暴露;因此,所述封料层能够直接包覆第一芯片和第二芯片。首先,所述第一芯片和第二芯片之间的结合更稳定,而且第一芯片和第二芯片之间的距离减小,有利于缩小封装结构的尺寸。其次,所述封料层同时包覆第一芯片和第二芯片,降低了对第一芯片或第二芯片的厚度要求,所述第一芯片或第二芯片的厚度能够减小;此外,所述封料层的稳定性更佳,能够避免因多层封料层而发生的分层或开裂问题。再次,所述封料层内具有与第一焊盘电连接的第一导电结构、以及与第二焊盘电连接的第二导电结构,由于避免了多层导电结构的对位偏差问题,有利于降低断路的发生概率,提高了封装结构的良率。 图1是本发明现有技术的扇出晶圆级封装结构; 图2是本发明现有技术的一种系统级扇出晶圆封装结构; 图3是本发明现有技术的另一种系统级扇出晶圆封装结构; 图4至图17是本发明实施例的一种芯片封装过程的剖面结构示意图; 图18至图19是本发明实施例的另一种芯片封装过程的剖面结构示意图。 如背景技术所述,现有的扇出晶圆级封装方法的封装质量、以及所形成的

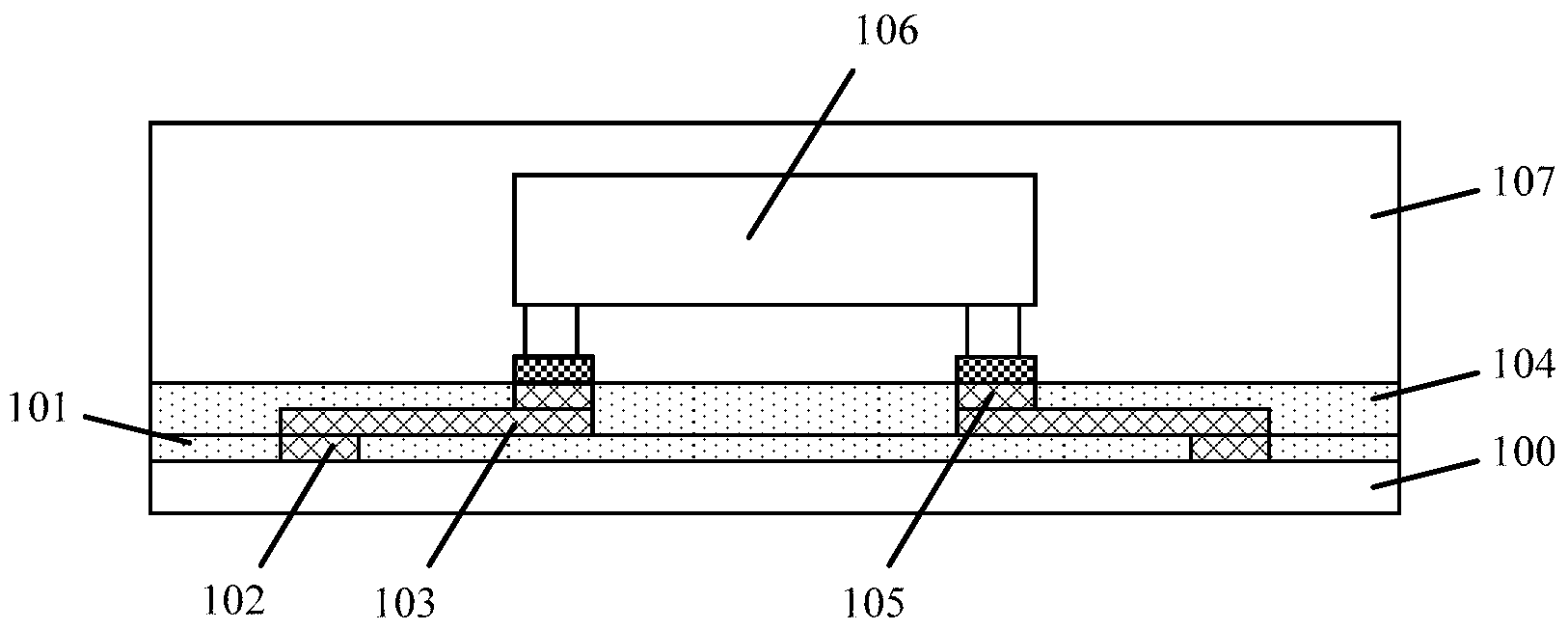

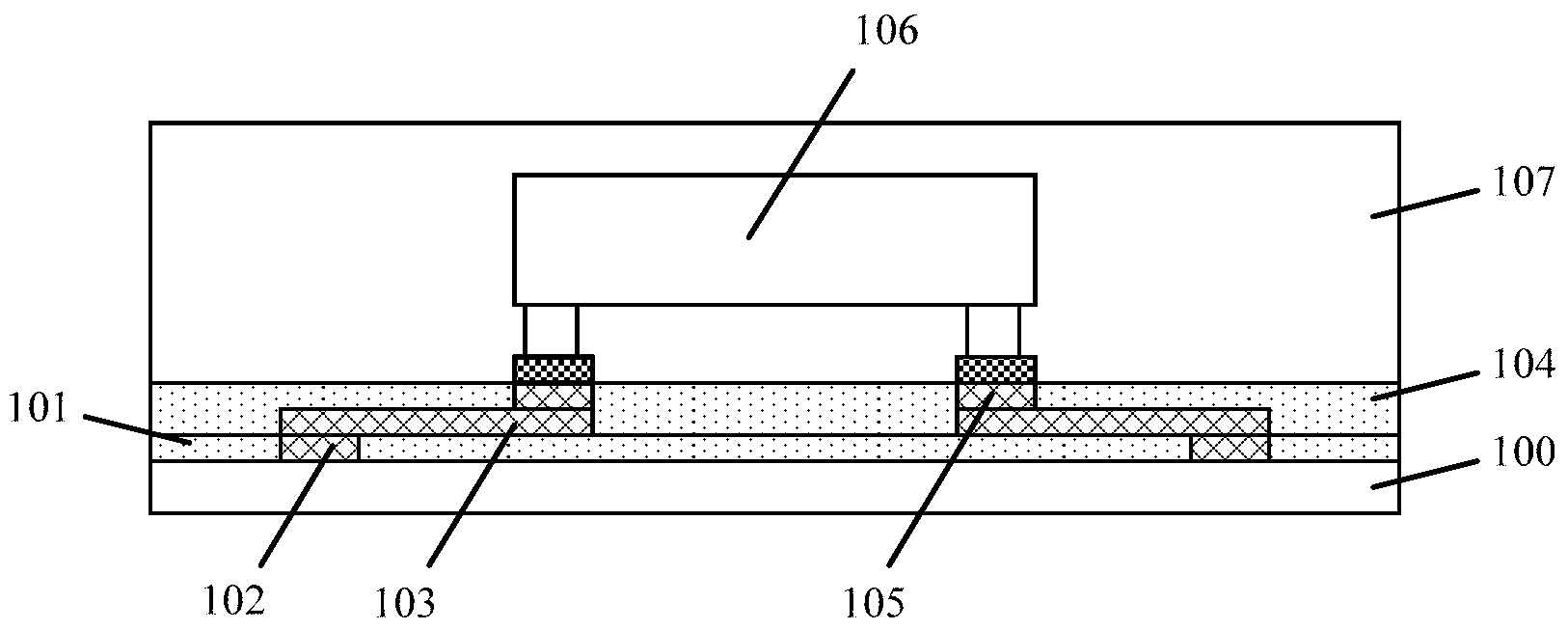

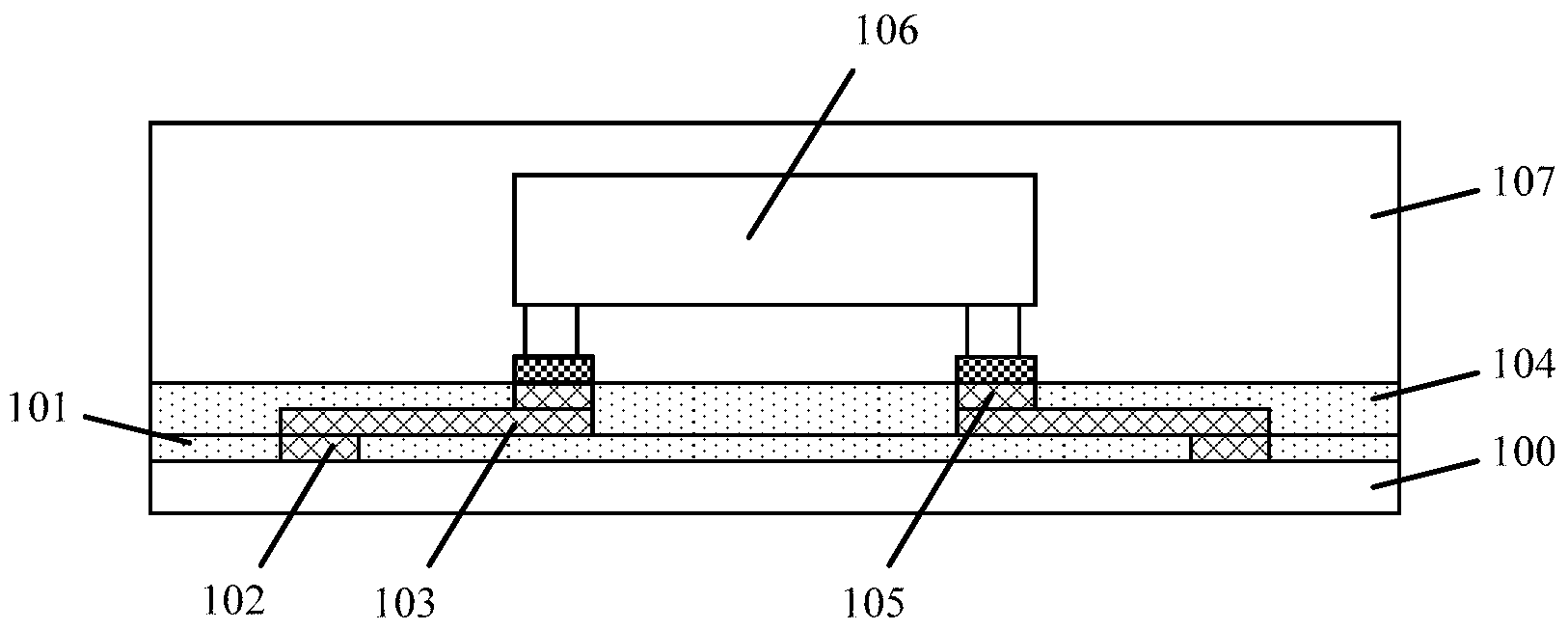

封装结构的集成度仍有待提高。 请参考图1,图1是现有技术中一种扇出晶圆级封装结构,包括:载板100;位于载板100表面的剥离膜和第一介质层101;位于第一介质层101内的第一开口;位于第一开口内的基板端金属电极102;位于所述第一介质层101表面的布线层103;位于布线层103、基板端金属电极102和第一介质层101表面的第二介质层104,所述第二介质层104内具有第二开口;位于第二开口内的芯片端金属电极105;将芯片106的功能面倒装于第二介质层104上,且芯片106与所述芯片端金属电极105电连接;位于第二介质层104表面的塑封层107,所述塑封层107包围所述芯片106,形成封装结构。 后续需要去除所述封装结构中的载板100,并在暴露出基板端金属电极102的表面形成焊球,所述焊球与基板端金属电极102电连接;对所述封装结构进行单片切割,形成扇出芯片封装结构。 在上述形成的扇出芯片封装结构中,所述芯片106为单一功能芯片,若需形成多功能的系统,则需将多个不同功能的扇出芯片封装结构进行集成,造成所形成的封装器件的尺寸较大,且制造成本较高。 为了满足半导体器件微小型化的需求,现有技术中另一种系统级扇出晶圆封装结构,请参考图2,包括:载板200;位于载板200表面的介质层201;位于介质层201内的电互连结构202;将有源芯片203和无源芯片204的功能面倒装于介质层201上,且所述有源芯片203和无源芯片204与所述电互连结构202电连接;所述介质层201表面具有塑封层205,所述塑封层205包围所述无源芯片204和有源芯片203。在后续去除所述载板200之后,在暴露出的电互连结构表面形成焊球,并对所形成的结构进行切割,以形成包括有源芯片203和无源芯片204的芯片封装结构。 在上述形成的封装结构中,由于所述有源芯片203和无源芯片204均倒装于载板200上,使得系统级封装结构的尺寸依旧较大,则所述扇出晶圆级封装结构的尺寸有待进一步缩小。 在另一现有技术中,还提出了一种扇出晶圆封装结构,请参考图3,包括:介质层300;位于介质层300内的再布线层301;将第一芯片组302的非功能

面固定于介质层300表面,所述第一芯片组302包括有源芯片和无源芯片;位于所述介质层300表面的第一塑封层303,所述第一塑封层303包围所述第一芯片组302;位于所述第一塑封层303表面和内部的第一电互连结构304,所述第一电互连结构304与所述再布线层301和第一芯片组302电连接;将第二芯片组305的非功能面固定于第一塑封层303和第一电互连结构304表面,所述第二芯片组305包括有源芯片和无源芯片;位于所述第一塑封层303和第一电互连结构304表面的第二塑封层306,所述第二塑封层306包围所述第二芯片组305;位于所述第二塑封层306表面和内部的第二电互连结构307,所述第二电互连结构307与所述第一电互连结构304和第二芯片组305电连接;将第三芯片组308的功能面倒装于第二塑封层306和第二电互连结构307上,所述第三芯片组308与第二电互连结构307电连接,且所述第三芯片组308包括有源芯片和无源芯片;位于所述第二塑封层306和第二电互连结构307表面的第三塑封层309,所述第三塑封层309包围所述第三芯片组308。 上述扇出晶圆封装结构虽然能够实现若干芯片组的重叠设置,然而,由于每形成一层芯片组,均需要形成一层塑封层包围所述芯片组,而且,每一层塑封层的表面和内部均需要形成电互连结构,以实现不同层电互连结构之间电连接,因此所述封装结构的制造工艺繁琐,而且成本较高。 其次,由于每层芯片组均需要由一层塑封层包围固定,为了满足塑封工艺的需求,每层芯片组的厚度不宜过薄,即每组芯片组中的无源芯片和有源芯片的厚度不宜过薄,否则将造成所形成的塑封层材料无法完全包围芯片组,甚至无法形成塑封层。因此,即使所述芯片组能够重叠设置,所形成的封装结构的厚度依旧较厚,则所形成的封装结构的空间占用率依旧较高,不利于器件的微小型化发展要求。 而且,由于每层芯片组和塑封层的厚度较厚,则用于形成所述导电插塞的通孔深度较深,使得形成所述通孔的工艺难度增大。此外,由于需要在每一层的塑封层表面和内部均形成电互连结构,使得所述电互连结构的对位难度提高,容易在不同层的电互连结构之间造成良率损失。 再次,由于每层芯片组均需要由一层塑封层包围固定,相邻两层塑封层之

间的结合稳定性较差,两层塑封层之间容易发生分层或开裂(peeling),则所形成的封装结构内部容易产生缺陷,封装结构的稳定性较差、可靠性较低。 为了解决上述问题,本发明提供一种芯片封装方法及芯片封装结构。在所述封装方法中,提供第一芯片和第二芯片,且第一芯片的面积小于第二芯片的面积。所述第二芯片的第三表面具有第二焊盘,所述第一芯片的第一表面具有第一焊盘;将所述第二芯片的第四表面与载板表面相结合,能够暴露出所述第二焊盘;将所述第一芯片的第二表面与所述第二芯片的第三表面相结合,且所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外,则所述第一焊盘和第二焊盘均能够被暴露;因此,能够直接在所述载板上形成同时包覆第一芯片和第二芯片的封料层。首先,所述第二芯片的第四表面与载板表面相结合,所述第一芯片的第二表面与第二芯片的第三表面相结合,使得第一芯片和第二芯片之间的结合更稳定,而且第一芯片和第二芯片之间的距离减小,有利于缩小封装结构的尺寸。此外,所述封料层的稳定性更佳,能够避免因形成多层封料层而发生的分层或开裂问题。再次,在形成封料层之后,形成与第一焊盘电连接的第一导电结构、以及与第二焊盘电连接的第二导电结构,由于避免了多次形成多层导电结构的工艺步骤,使得第一导电结构和第二导电结构的形成工艺简单,而且避免了多层导电结构形成过程中的对位偏差问题;而且,由于第一芯片的第一表面与第二芯片的第三表面之间的距离降低至最小,即使塑封层到第二焊盘的距离减小,从而降低了形成第二导电结构的工艺难度,有利于降低第二导电结构与第二焊盘之间、以及第一导电结构与第一焊盘之间发生断路的概率,提高了所形成的封装结构的良率。 为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。 图4至图17是本发明实施例提供的的一种芯片封装过程的剖面结构示意图。 请参考图4,提供第一芯片410,所述第一芯片410包括相对的第一表面411和第二表面412,所述第一芯片410的第一表面411具有若干第一焊盘413。 在本实施例中,所述第一芯片410的面积小于后续提供的第二芯片的面

积,所述第一芯片410与后续提供的第二芯片相结合。所述第一芯片410的第一表面具有第一焊盘413,所述第一芯片410的第一表面411为功能面,所述第一芯片410的第二表面412为非功能面,后续将所述第一芯片410的第二表面412与第二芯片相结合,能够暴露出所述第一芯片410的第一焊盘413,以便后续能够形成与所述第一焊盘413电连接的第一导电结构。 所述第一芯片410的形成步骤包括:提供第一衬底414(如图5所示),所述第一衬底414包括若干第一芯片区415;对所述第一衬底414进行减薄后切割,使若干第一芯片区415相互独立,形成第一芯片410。 所述第一衬底414包括硅衬底、硅锗衬底、碳化硅衬底、绝缘体上硅(SOI)衬底、绝缘体上锗(GOI)衬底硅衬底、硅锗衬底、碳化硅衬底、绝缘体上硅(SOI)衬底、绝缘体上锗(GOI)衬底;所述第一衬底414为整片的晶圆。 所述第一芯片区415用于形成所述第一芯片410;在本实施例中,所述第一芯片区415呈阵列排布。在本实施例中,相邻第一芯片区415之间还具有第一切割道区,通过在所述第一切割道区对所述第一衬底414进行切割,能够使若干第一芯片区415相互分离并独立,形成第一芯片410。 所述第一衬底414的第一芯片区415内形成有半导体器件、电互连所述半导体器件的电互连结构、以及电隔离所述半导体器件和电互连结构的绝缘层。所形成的第一芯片410可以包括集成电路芯片、传感器芯片或微机电系统(MEMS)芯片;所述集成电路芯片可以包括处理器芯片、存储器芯片或控制器芯片;所述传感器芯片可以包括图像传感器芯片,例如CCD图像传感器或CMOS图像传感器;所述传感器芯片还可以包括温度传感器芯片、压力传感器芯片、湿度传感器芯片或运动传感器芯片,本申请对比不做限定。 所述第一焊盘413位于第一芯片410的第一表面411。在本实施例中,所述第一焊盘413位于第一表面411的边缘区域内,以便后续在第一表面411结合第二芯片之后,能够在结合区域以外暴露出所述第一焊盘413。所述第一焊盘413的材料为导电材料,所述导电材料包括铜、钨、铝、银或金。所述第一焊盘413用于实现第一芯片410与其他芯片或电路的电连接,所述第一焊盘413能够与第一芯片410内所需的半导体器件或电互连结构电连接。在本实施

例中,所述第一焊盘413的表面突出于第一表面411。在其它实施例中,所述第一焊盘413的表面还能够与第一表面411齐平。 请参考图6,提供第二芯片420,所述第二芯片420包括相对的第三表面421和第四表面422,所述第二芯片420的第三表面421具有若干第二焊盘423,且所述第二芯片420的面积大于第一芯片410(如图4所示)的面积。 所述第二芯片420的第三表面421具有第二焊盘423,所述第二芯片420的第三表面421为功能面,所述第二芯片420的第四表面422为非功能面。在本实施例中,所述第二芯片420的面积大于第一芯片410(如图4所示),而且,所述第二焊盘423位于第二芯片420第三表面421的边缘区域内,当后续将所述第一芯片410(如图4所示)的第二表面412(如图4所示)与所述第二芯片420第三表面421的中心区域相结合之后,能够使第二焊盘423位于第一芯片410和第二芯片420的结合区域之外,从而能够暴露出所述第二焊盘423。 所述第二芯片420的形成步骤与第一芯片410的形成步骤相同,所述第二芯片420的尺寸与第一芯片410不同,所述第二芯片420的功能或类型与第一芯片410相同或不同。 所述第二焊盘423位于第二芯片420的第三表面421。所述第二焊盘423的材料为导电材料,所述导电材料包括铜、钨、铝、银或金。所述第二焊盘423用于实现第二芯片420与其他芯片或电路的电连接,所述第二焊盘423能够与第二芯片420内所需的半导体器件或电互连结构电连接。在本实施例中,所述第二焊盘423的表面突出于第三表面421。在其它实施例中,所述第二焊盘423的表面还能够与第二表面421齐平。 请参考图7,提供载板400;将所述第二芯片420的第四表面422与载板400表面相结合。 所述载板400为后续形成封装结构提供工作平台。在本实施例中,所形成的封装结构为扇出型系统级封装结构,在后续形成封料层之后,需要去除所述载板400,形成以封料层包围第一芯片410(如图4所示)和第二芯片的420的封装结构。

所述载板400包括玻璃基板、半导体基板或树脂基板。在本实施例中,所述载板400为硅晶圆或玻璃基板,所述硅晶圆或玻璃基板易剥离、抗腐蚀能力强,可以进行重复利用。 本实施例的载板400如图8所示,所述载板400包括若干器件区440;所述第二芯片420的第四表面422与所述载板400的器件区440表面相结合。相邻所述器件区440之间作为切割区,当后续去除载板400之后,能够在切割区对应的位置对所形成的封装结构进行切割,以形成单片芯片封装结构。 在本实施例中,所述第二芯片420通过胶合层401固定于载板400表面。将所述第二芯片420的第四表面422与载板400表面相结合的步骤包括:在所述载板400表面形成胶合层401;将所述第二芯片420的第四表面422固定于所述胶合层401表面。由于所述第二芯片420的第四表面422不具有第二焊盘423,在将第二芯片420的第四表面422结合于载板400表面之后,能够暴露出所述第二焊盘423。 其中,所述胶合层401的表面具有粘性,从而使载板400和第二芯片420相互固定;所述胶合层401的材料可以包括UV胶。所述UV胶经紫外线照射后粘性降低,以便后续将载板400从封装结构中剥离。 在其它实施例中,还能够通过在所述第二芯片420的第四表面422形成粘结层,再将所述第二芯片420的第四表面422通过所述粘结层固定于载板400表面。 请参考图9,将所述第一芯片410的第二表面412与所述第二芯片420的第三表面421相结合,所述若干第二焊盘423位于所述第一芯片410和第二芯片420的结合区域之外。 由于所述第一芯片410的面积小于所述第二芯片420的面积,因此,在将第一芯片410固定于第二芯片420的第三表面421之后,能够暴露出部分第二芯片420的第三表面421;而且,由于本实施例中的第二焊盘423位于第二芯片420第三表面421的边缘区域内,因此,在将所述第一芯片410固定于第三表面421的中心区域之后,能够使第二焊盘423位于结合区域之外,使得第二焊盘423能够被暴露。

由于所述第一芯片410的第一表面411具有第一焊盘413,在将第一芯片410的第二表面412固定于第二芯片420的第三表面421之后,能够暴露出所述第一焊盘413。 由于所述第一焊盘413和第二焊盘423均能够被暴露,因此后续能够直接形成包围所述第一芯片410和第二芯片420的封料层,而且能够同时形成电连接第一焊盘413的第一导电结构、以及电连接第二焊盘423的第二导电结构。 首先,由于无需分别形成包围第一芯片410和第二芯片420的封料层,不仅能够简化工艺,还能够防止相邻封料层之间发生分层或断裂,因此,后续形成的封料层固定和绝缘保护能力稳定,所形成的封装结构可靠性提高。 其次,所述第一芯片410或第二芯片420的厚度能够小于塑封工艺的要求,由此,能够使所形成的第一芯片410或第二芯片420的厚度相应减小,不仅有利于使所形成的封装结构的厚度减小,而且降低了后续形成第二导电结构时的刻蚀工艺的难度。当仅针对单独一颗芯片进行塑封时,每层的封料层都会有一个极值厚度,但是在本实施例中,第一芯片410和第二芯片420通过绝缘胶层进行贴合后,再一起进行塑封可以使整体封装尺寸更薄。 在本实施例中,所述第一芯片410的第二表面412通过绝缘胶层402与所述第二芯片420的第三表面421相结合。 其中,所述绝缘胶层402的表面具有粘性,从而使第一芯片410和第二芯片420相互固定;所述绝缘胶层402的材料包括绝缘硅胶、聚酰亚胺或BCB树脂。通过绝缘胶层将第二芯片420的第三表面421与第一芯片410的第二表面411相固定,能够使第三表面421到第二表面411的距离减小,有利于进一步缩小所形成封装结构的厚度尺寸。 在本实施例中,所述第一芯片410的数量为一个。在另一实施例中,所述第一芯片的数量为多个;当所述第一芯片的数量为多个时,若干第一芯片的功能相同或不同;当所述第一芯片的数量为多个时,若干第一芯片位于同一层或者为多层重叠结构;当所述第一芯片为多层重叠结构时,至少一层第一芯片的部分第一焊盘在相邻两层第一芯片的结合区域之外。

需要说明的是,在本实施例和附图中,仅以一个第一芯410片和一个第二芯片420为例对本发明的芯片封装方法和封装结构进行了说明。在其它实施例中,所述第一芯片410的数量可以为一个或多个,所述第二芯片420的数量也可以为一个或多个,当所述第一芯片或者第二芯片的数量为多个时,若干第一芯片410或第二芯片420为相同功能或者不同功能的芯片,例如,可以是存储器芯片、处理器芯片、图像传感器芯片或运动传感器芯片等。当第一芯片410为多个时,可以在一个第二芯片420的第三表面421上分布多个第一芯片410。 请参考图10,在所述载板400表面形成封料层403,所述封料层403包覆所述第一芯片410和第二芯片420。 在本实施例中,由于所述第二焊盘423和第一焊盘413均能够被暴露出,因此能够在相互固定第一芯片410和第二芯片420之后形成所述封料层403,由于避免了分别逐层形成包围第一芯片410和第二芯片420的封料层、以及在每一层封料层内部和表面形成一组电互连结构的步骤,从而能够使形成封装结构的工艺得以简化,而且有利于使所形成的封装结构的尺寸缩小;而且,能够避免因逐层形成封料层而发生的两层封料层之间分层或开裂等问题。 其次,所述封料层403厚度大于所述第一芯片410的第一表面411到第二芯片420的第四表面422的距离,即所述第一表面411到第四表面422的距离满足封料层403的形成工艺要求即可,而所述第一芯片410和第二芯片420的厚度能够相应减小,有利于缩小所形成的封装结构的厚度尺寸。 此外,后续在形成所述封料层403之后再同时形成电连接第一焊盘413的第一导电结构、以及电连接第二焊盘423的第二导电结构,不仅能够简化工艺步骤,而且能够避免因逐层形成的导电结构而发生的对位偏差等问题,防止导电结构之间发生断路,提高封装结构的良率。 所述封料层403可以包括感光干膜、非感光干膜或者塑封材料膜。在一实施例中,所述封料层403为感光干膜,所述封料层403的形成工艺为真空贴膜工艺。 在另一实施中,所述封料层403的材料为塑封材料,所述塑封材料包括环氧树脂、聚酰亚胺树脂、苯并环丁烯树脂、聚苯并恶唑树脂、聚对苯二甲酸丁

二酯、聚碳酸酯、聚对苯二甲酸乙二醇酯、聚乙烯、聚丙烯、聚烯烃、聚氨酯、聚烯烃、聚醚砜、聚酰胺、聚亚氨酯、乙烯-醋酸乙烯共聚物、聚乙烯醇或其他合适的聚合物材料。 所述封料层403的形成工艺包括注塑工艺(injection molding)、转塑工艺(transfer molding)或丝网印刷工艺。所述注塑工艺包括:提供模具;在所述模具中填充塑封材料,使所述塑封材料包覆所述第一芯片410和第二芯片420;对所述塑封材料进行升温固化,形成封料层403。 在其他实施例中,所述封料层403的材料也可以为其他绝缘材料,本申请对此不做限定。 在形成所述封料层403之后,在所述封料层403内形成第一导电结构和第二导电结构,所述第一导电结构与第一焊盘413电连接,所述第二导电结构与第二焊盘423电连接。以下将对所述第一导电结构和第二导电结构的形成步骤进行说明。 请参考图11,在所述封料层403内形成若干分别暴露出若干第一焊盘413的第一开口404;在所述封料层403内形成若干分别暴露出若干第二焊盘423的第二开口405。 所述第一开口404用于形成第一导电结构,所述第二开口405用于形成第二导电结构;所述第一导电结构用于与第一焊盘413电连接,所述第二导电结构用于与第二焊盘423电连接。在本实施例中,所述第一开口405和第二开口406同时形成。在其它实施例中,所述第一开口404和第二开口405还能够在不同步骤中形成,由于所述第一开口404的深度小于第二开口405的深度,因此,当采用刻蚀工艺形成所述第一开口404和第二开口405时,形成第一开口404的刻蚀深度小于形成第二开口405的刻蚀深度,则分别形成所述第一开口404和第二开口405时,能够减少对第一焊盘413的损伤。 在一实施例中,所述封料层403可以为感光干膜,形成所述第一开口404和第二开口405的工艺可以为光刻工艺,包括:采用紫外光照射所述感光干膜待形成第一开口404和第二开口405区域之外的区域,使感光干膜的材料发生聚合反应以形成稳定物质;采用显影工艺去除感光干膜未被紫外光照射的区

域,形成第一开口404和第二开口405。 在一实施例中,所述封料层403可以为非感光干膜或塑封材料,形成所述第一开口404和第二开口405的工艺可以为激光打孔工艺,包括:采用激光源对封料层403需要形成第一开口404和第二开口405的对应区域进行加热,使激光照射区域的封料层403发生气化,以形成第一开口404和第二开口405。所述激光源输出的激光脉冲宽度可以为1ns~200ns,脉冲频率可以为80kHz~200kHz,激光在聚焦点处的能量大于1E18W/cm2。由于采用激光打孔工艺无需形成掩膜层,能够简化工艺,并减少污染及副产物。 当所述封料层403为非感光干膜或塑封材料时,所述第一开口404和第二开口405的形成工艺还可以包括刻蚀工艺。所述第一开口404和第二开口405的形成步骤可以包括:在所述封料层403表面形成图形化层,所述图形化层暴露出需要形成第一开口404和第二开口405的对应区域;以所述图形化层为掩膜,刻蚀所述封料层403,直至暴露出第一焊盘413和第二焊盘423,形成所述第一开口404和第二开口405;在刻蚀所述封料层403之后,去除所述图形化层。 所述图形化层可以为图形化的光刻胶层,还可以为图形化的硬掩膜,所述硬掩膜的材料包括氧化硅、氮化硅、氮氧化硅中的一种或的多种。所述刻蚀封料层403的工艺可以为各向异性的干法刻蚀工艺。本实施例中,后续形成的第一导电结构和第二导电结构可以为导电插塞,所述第一开口404和第二开口405的侧壁垂直于载板400表面;所述各向异性的干法刻蚀工艺的刻蚀气体可以包括CH4、CHF3、CH3F中的一种或多种,偏置功率大于100瓦,偏置电压大于10伏。 在本实施例中,所述第一开口404和第二开口405的侧壁垂直于载板400表面。在另一实施例中,所述第一开口404和第二开口405的侧壁相对于所述载板400表面倾斜,且所述第一开口404和所述第二开口405的顶部尺寸大于底部尺寸,有利于后续在所述第一开口404和所述第二开口405内形成导电材料。 请参考图12,在所述第一开口404内形成填充满所述第一开口404(参考

图11)的第一导电插塞406;在所述第二开口405(参考图11)内形成填充满所述第二开口405的第二导电插塞407。 所述第一导电插塞406用于通过第一焊盘413与第一芯片410电连接;所述第二导电插塞407用于通过第二焊盘423与第二芯片420电连接。本实施例中,所述第一导电插塞407和第二导电插塞406同时形成,不仅能够简化工艺步骤,还能够降低工艺难度,避免发生对位偏差。 所述第一导电插塞406和第二导电插塞407的形成步骤包括:在所述第一开口404和所述第二开口405内形成导电膜,所述导电膜填充满所述第一开口404和第二开口405;对所述导电膜进行抛光,形成第一导电插塞406和第二导电插塞407。在本实施例中,所述抛光工艺进行至暴露出所述封料层403表面为止。在另一实施例中,所述抛光工艺在封料层403表面保留部分厚度的导电膜,且位于封料层403表面的导电膜为图形化的电互连层。 所述导电膜的形成工艺可以为物理气相沉积工艺,例如溅射工艺,或者为真空锡印刷工艺;所述导电膜的材料为金属,所述金属包括金、锡、铜、钨、铝、钛中的一种或多种组合。 请参考图13,在所述封料层403的部分表面、第一导电插塞406的顶部表面和第二导电插塞407的顶部表面形成电互连层408。 所述电互连层408与第一导电插塞406或第二导电插塞407电连接,用于在塑封层403表面实现再布线。 所述的电互连层408的形成步骤包括:在封料层403、第一导电插塞406和第二导电插塞407的顶部表面形成电互连膜;在所述电互连膜表面形成图形化层,所述图形化层暴露出部分所述电互连膜;以所述图形化层为掩膜,刻蚀所述电互连膜,直至暴露出封料层403表面为止,形成电互连层408;在刻蚀所述电互连膜之后,去除所述图形化层。 所述电互连膜的材料包括铜、钨、铝、钛、钽、氮化钛、氮化钽、银中的一种或多种;刻蚀所述电互连膜的工艺包括各向异性的干法刻蚀工艺或者湿法工艺;所述图形化层可以为图形化的光刻胶层,还可以为图形化的硬掩膜,所

述硬掩膜的材料包括氧化硅、氮化硅、氮氧化硅中的一种或的多种。 请参考图14,在所述封料层403和电互连层408表面形成阻焊层409,所述阻焊层409内具有若干第三开口430,所述第三开口430暴露出部分电互连层408表面。 所述阻焊层409用于保护所述电互连层408;所述阻焊层409内的第三开口430用于在后续工艺中用于形成凸块。 所述阻焊层409的形成步骤包括:在所述封料层403和电互连层408表面形成阻焊膜;对所述阻焊膜进行图形化,形成阻焊层409,且所述阻焊层409内具有第三开口430。 在一实施例中,所述阻焊层409的材料包括聚合物材料或无机绝缘材料;所述聚合物材料可以为绝缘树脂;所述无机绝缘材料包括氧化硅、氮化硅或氮氧化硅。对所述阻焊膜进行图形化的工艺包括:在阻焊膜表面形成图形化层的光刻胶层;以所述光刻胶层刻蚀所述阻焊膜。 在另一实施例中,阻焊层409的材料可以为光刻胶,所述第三开口430可以采用光刻工艺形成。 请参考图15,在所述第三开口430(如图14所示)内形成凸块431。 在一实施例中,所述凸块431可以为焊球,所述焊球的材料包括锡,所述焊球的形成步骤包括:在所述第三开口430底部的电互连层408表面印刷锡膏,再进行高温回流,在表面张力作用下,形成焊球。在另一实施例中,可以先在所述第三开口430底部的电互连层408表面印刷助焊剂和焊球颗粒,再高温回流形成焊球。在其它实施例中,还可以在所述电互连层408上电镀锡柱,再高温回流形成焊球。 在另一实施例中,所述凸块431还可以为铜柱、金柱、锡球、或者铜柱和锡球的结合体等。 请参考图16,在形成所述凸块431之后,去除所述载板400(如图15所示),形成待处理衬底432。

所形成的待处理衬底432包括第一芯片410、第二芯片420、第一导电结构、封料层403、第一导电插塞406和第二导电插塞407。 在本实施例中,由于所述载板400与封料层403和第二芯片420之间具有胶合层401,所述胶合层401的材料为UV胶,所述UV胶经紫外线照射后粘性降低,以便后续将载板400从封装结构中剥离。 请参考图17,对所述待处理衬底432进行切割,形成若干独立的封装结构433,所述封装结构433包括相互结合的第一芯片410和第二芯片420、以及包覆所述第一芯片410和第二芯片420的封料层403。 在本实施例中,所述载板400(如图16所示)的器件区440(如图8所示)之间具有切割区,对所述待处理衬底432进行切割的工艺包括:在所述器件区440对应的区域对所述待处理衬底432进行切割,形成若干独立的芯片封装结构。 综上,本实施例中,提供第一芯片和第二芯片,且第一芯片的面积小于第二芯片的面积。由于所述第二芯片的第三表面具有第二焊盘,所述第一芯片的第一表面具有第一焊盘;将所述第二芯片的第四表面与载板表面相结合,能够暴露出所述第一焊盘;将所述第一芯片的第二表面与所述第二芯片的第三表面相结合,且所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外,则所述第一焊盘和第二焊盘均能够被暴露;因此,能够直接在所述载板上形成同时包覆第一芯片和第二芯片的封料层。 首先,所述第二芯片的第四表面与载板表面相结合,所述第一芯片的第二表面与第二芯片的第三表面相结合,使得第一芯片和第二芯片之间的结合更稳定,而且第一芯片和第二芯片之间的距离减小,有利于缩小封装结构的尺寸。 其次,由于所述封料层同时包覆第一芯片和第二芯片,因此降低了对第一芯片或第二芯片的厚度要求,所述第一芯片或第二芯片的厚度能够减小,有利于使第一芯片和第二芯片的总厚度减小,则所形成的封装结构尺寸减小;此外,所述封料层的稳定性更佳,能够避免因形成多层封料层而发生的分层或开裂问题。

再次,在形成封料层之后,形成与第一焊盘电连接的第一导电结构、以及与第二焊盘电连接的第二导电结构,由于避免了多次形成多层导电结构的工艺步骤,使得第一导电结构和第二导电结构的形成工艺简单,而且避免了多层导电结构形成过程中的对位偏差问题;而且,由于对第一芯片和第二芯片的厚度要求减小,因此能够通过减小第一芯片的厚度,使塑封层到第二焊盘的距离减小,从而降低了形成第二导电结构的工艺难度,有利于降低第二导电结构与第二焊盘之间、以及第一导电结构与第一焊盘之间发生断路的概率,提高了所形成的封装结构的良率。 相应的,本发明还提供一种采用上述封装方法形成的芯片封装结构,请继续参考图15,包括: 第一芯片410,所述第一芯片410包括相对的第一表面411和第二表面412,所述第一芯片410的第一表面411具有若干第一焊盘413; 第二芯片420,所述第二芯片420包括相对的第三表面421和第四表面422,所述第二芯片420的第三表面421具有若干第二焊盘423,且所述第二芯片420的面积大于第一芯片410的面积; 载板400,所述第二芯片420的第四表面422通过胶合层401与载板400表面相结合; 所述第一芯片410的第二表面412与所述第二芯片420的第三表面421相结合,所述若干第二焊盘423位于所述第一芯片410和第二芯片420的结合区域之外; 位于所述载板400表面的封料层403,所述封料层403包覆所述第一芯片410和第二芯片420; 位于所述封料层403内的第一导电结构和第二导电结构,所述第一导电结构与第一焊盘413电连接,所述第二导电结构与第二焊盘423电连接。 以下将对上述结构进行详细说明。 本实施例第一导电结构和第二导电结构包括:所述封料层403内具有若干分别暴露出若干第一焊盘413的第一开口、以及若干分别暴露出若干第二焊盘

423的第二开口;位于所述第一开口内且填充满所述第一开口的第一导电插塞406;位于所述第二开口内且填充满所述第二开口的第二导电插塞407。 本实施例的封装结构还包括:位于所述封料层403的部分表面、第一导电插塞406的顶部表面和第二导电插塞407的顶部表面的电互连层408。 本实施例的封装结构还包括:位于所述封料层403和电互连层408表面的阻焊层409,所述阻焊层409内具有若干第三开口,所述第三开口暴露出部分电互连层408表面;位于所述第三开口内的凸块431。 在本实施例中,所述第一芯片410的数量为一个。在另一实施例中,所述第一芯片的数量为多个;当所述第一芯片的数量为多个时,若干第一芯片的功能相同或不同;当所述第一芯片的数量为多个时,若干第一芯片位于同一层或者为多层重叠结构;当所述第一芯片为多层重叠结构时,至少一层第一芯片的部分第一焊盘在相邻两层第一芯片的结合区域之外。 需要说明的是,在本实施例和附图中,仅以一个第一芯410片和一个第二芯片420为例对本发明的芯片封装方法和封装结构进行了说明。在其它实施例中,所述第一芯片410的数量可以为一个或多个,当所述第二芯片420的数量也可以为一个或多个,当所述第一芯片或者第二芯片的数量为多个时,若干第一芯片410或第二芯片420为相同功能或者不同功能的芯片,例如,存储器芯片、处理器芯片、图像传感器芯片或运动传感器芯片等。当第一芯片410为多个时,可以在一个第二芯片420的第三表面421上分布多个第一芯片410。 本实施例还提供一种封装结构,在图15的基础上,还包括:去除所述载板400并形成待处理衬底;对所述待处理衬底进行切割,形成若干独立的封装结构433,如图17所示;所述封装结构433包括相互结合的第一芯片410和第二芯片420、以及包覆所述第一芯片410和第二芯片420的封料层403。 综上,本实施例中,由于所述第二芯片的第三表面具有第二焊盘,所述第一芯片的第一表面具有第一焊盘;所述第二芯片的第四表面与载板表面相结合,且所述第一芯片的第二表面与所述第二芯片的第三表面相结合,且所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外,则所述第一焊盘和第二焊盘均能够被暴露;因此,所述封料层能够直接包覆第一芯片和第二芯片。

首先,所述第一芯片和第二芯片之间的结合更稳定,而且第一芯片和第二芯片之间的距离减小,有利于缩小封装结构的尺寸。其次,所述封料层同时包覆第一芯片和第二芯片,降低了对第一芯片或第二芯片的厚度要求,所述第一芯片或第二芯片的厚度能够减小;此外,所述封料层的稳定性更佳,能够避免因多层封料层而发生的分层或开裂问题。再次,所述封料层内具有与第一焊盘电连接的第一导电结构、以及与第二焊盘电连接的第二导电结构,由于避免了多层导电结构的对位偏差问题,有利于降低断路的发生概率,提高了封装结构的良率。 图18至图19是本发明实施例的另一种芯片封装过程的剖面结构示意图。 在图10的基础上,请继续参考图18,在所述封料层403内形成若干分别暴露出若干第一焊盘413的第一开口504;在所述封料层403内形成若干分别暴露出若干第二焊盘423的第二开口505;在所述第一开口504的侧壁和底部表面、所述第二开口505的侧壁和底部表面以及所述封料层403的部分顶部表面形成电互连层500,在第一开口504内形成第一导电结构,在第二开口505内形成第二导电结构。 在本实施例中,所述第一导电结构和第二导电结构的形成步骤还包括:在所述第一开口504的侧壁和底部表面、所述第二开口505的侧壁和底部表面以及所述封料层403的部分顶部表面形成电互连层500,在第一开口504内形成第一导电结构,在第二开口505内形成第二导电结构。 在本实施例中,所述第一开口504和第二开口505的侧壁相对于所述载板400表面倾斜,且所述第一开口504和所述第二开口505的顶部尺寸大于底部尺寸,有利于在所述第一开口504和所述第二开口505的侧壁和顶部表面形成图形化的电互连层500。所述第一开口504和第二开口505的形成步骤如前述实施例所述,在此不作赘述。 所述电互连层的形成步骤包括:在所述封料层403表面、第一开口504的侧壁和底部表面、以及第二开口505的侧壁和底部表面形成电互连膜;在所述电互连膜表面形成图形化层,所述图形化层暴露出部分电互连膜;以所述图形化层为掩膜,刻蚀所述电互连膜直至暴露出封料层403表面为止。

所述电互连膜的形成工艺为物理气相沉积工艺,例如溅射工艺。所述电互连层500的材料包括金、锡、铜、钨、铝、钛中的一种或多种组合。所述图形化层能够为图形化的光刻胶层或图形化的硬掩膜层。 请参考图19,在所述封料层403和电互连层500表面形成阻焊层501,所述阻焊层501内具有若干第三开口,所述第三开口暴露出部分位于封料层403表面的电互连层500;在所述第三开口内形成凸块503。 在本实施例中,所述阻焊层501还能够填充满所述第一开口504(如图18所示)和第二开口505(如图18所示)。 所述形成阻焊层501以及凸块503的步骤与前述实施例相同,在此不做赘述。 在形成凸块503之后,去除所述载板400,形成待处理衬底;沿切割线506对所述待处理衬底进行切割,形成若干独立的封装结构,所述封装结构包括相互结合的第一芯片410和第二芯片420、以及包覆所述第一芯片410和第二芯片420的封料层403。 相应的,本发明还提供一种采用上述封装方法形成的芯片封装结构,请继续参考图19,包括: 第一芯片410,所述第一芯片410包括相对的第一表面411和第二表面412,所述第一芯片410的第一表面411具有若干第一焊盘413; 第二芯片420,所述第二芯片420包括相对的第三表面421和第四表面422,所述第二芯片420的第三表面421具有若干第二焊盘423,且所述第二芯片420的面积大于第一芯片410的面积; 载板400,所述第二芯片420的第四表面422与载板400表面相结合; 所述第一芯片410的第二表面412与所述第二芯片420的第三表面421相结合,所述若干第二焊盘423位于所述第一芯片410和第二芯片420的结合区域之外; 位于所述载板400表面的封料层403,所述封料层403包覆所述第一芯片

410和第二芯片420; 位于所述封料层403内的第一导电结构和第二导电结构,所述第一导电结构与第一焊盘413电连接,所述第二导电结构与第二焊盘423电连接。 与前述实施例提供的封装结构相比,本实施例的封装结构区别在于:所述第一导电结构和第二导电结构包括:位于所述封料层403内的若干分别暴露出若干第一焊盘413的第一开口;位于所述封料层403内的若干分别暴露出若干第二焊盘423的第二开口;位于所述第一开口的侧壁和底部表面、所述第二开口的侧壁和底部表面以及所述封料层403的部分顶部表面的电互连层500;所述第一导电结构包括位于第一开口内的电互连层500;所述第二导电结构包括位于第二开口内的电互连层500。 虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

Disclosed are a packaging method and a packaging structure. The packaging method comprises: providing a first substrate and a second substrate, the second substrate having a first surface and a second surface opposite to the first surface, and a side surface of the first substrate being adhered to the first surface of the second substrate via an adhesive layer; forming a groove structure on the second surface of the second substrate; providing a base, the base having a first surface and a second surface opposite to the first surface, and the first surface of the base having a sensing area and a plurality of welding pads located around the sensing area; and laminating the second surface of the second substrate with the first surface of the base to form a cavity between the groove structure and the base, such that the sensing area is located inside the cavity. 一种芯片封装方法,其特征在于,包括: 提供第一芯片,所述第一芯片包括相对的第一表面和第二表面,所述第一芯片的第一表面具有若干第一焊盘; 提供第二芯片,所述第二芯片包括相对的第三表面和第四表面,所述第二芯片的第三表面具有若干第二焊盘,且所述第二芯片的面积大于第一芯片的面积; 提供载板; 将所述第二芯片的第四表面与载板表面相结合; 将所述第一芯片的第二表面与所述第二芯片的第三表面相结合,所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外; 在所述载板表面形成封料层,所述封料层包覆所述第一芯片和第二芯片; 在所述封料层内形成第一导电结构和第二导电结构,所述第一导电结构与第一焊盘电连接,所述第二导电结构与第二焊盘电连接。 如权利要求1所述的芯片封装方法,其特征在于,将所述第二芯片的第四表面与载板表面相结合的步骤包括:在所述载板表面形成胶合层;将所述第二芯片的第四表面固定于所述胶合层表面。 如权利要求1所述的芯片封装方法,其特征在于,所述第一芯片的第二表面通过绝缘胶层与所述第二芯片的第三表面相结合。 如权利要求1所述的芯片封装方法,其特征在于,所述封料层为感光干膜、非感光干膜或者塑封材料膜。 如权利要求1所述的芯片封装方法,其特征在于,还包括:在所述封料层内形成若干分别暴露出若干第一焊盘的第一开口;在所述封料层内形成若干分别暴露出若干第二焊盘的第二开口。

如权利要求5所述的芯片封装方法,其特征在于,所述第一导电结构和第二导电结构包括:位于所述第一开口的侧壁和底部表面、所述第二开口的侧壁和底部表面以及所述封料层的部分顶部表面的电互连层,所述电互连层填充满或不填充满所述第一开口或第二开口。 如权利要求5所述的芯片封装方法,其特征在于,所述第一导电结构和第二导电结构包括:填充满所述第一开口的第一导电插塞和填充满所述第二开口的第二导电插塞。 如权利要求7所述的芯片封装方法,其特征在于,还包括: 在所述封料层的部分表面、第一导电插塞的顶部表面和第二导电插塞的顶部表面形成电互连层。 如权利要求6或者8所述的芯片封装方法,其特征在于,还包括:在所述封料层和电互连层表面形成阻焊层,所述阻焊层内具有若干第三开口,所述第三开口暴露出部分电互连层表面;在所述第三开口内形成凸块。 如权利要求1所述的芯片封装方法,其特征在于,还包括:在形成所述封料层之后,去除所述载板,形成待处理衬底;对所述待处理衬底进行切割,形成若干独立的封装结构。 如权利要求1所述的芯片封装方法,其特征在于,所述第一芯片的数量为一个或多个;所述第二芯片的数量为一个或多个。 如权利要求11所述的芯片封装方法,其特征在于,当所述第一芯片的数量为多个时,若干第一芯片位于同一层或者多层重叠,且若干第一芯片分布于一个或多个第二芯片上;当所述第一芯片或第二芯片的数量为多个时,若干第一芯片或第二芯片的功能相同或不同。 一种芯片封装结构,其特征在于,包括: 第一芯片,所述第一芯片包括相对的第一表面和第二表面,所述第一芯片的第一表面具有若干第一焊盘; 第二芯片,所述第二芯片包括相对的第三表面和第四表面,所述第二芯

片的第三表面具有若干第二焊盘,且所述第二芯片的面积大于第一芯片的面积; 载板,所述第二芯片的第四表面与载板表面相结合; 所述第一芯片的第二表面与所述第二芯片的第三表面相结合,所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外; 位于所述载板表面的封料层,所述封料层包覆所述第一芯片和第二芯片; 位于所述封料层内的第一导电结构和第二导电结构,所述第一导电结构与第一焊盘电连接,所述第二导电结构与第二焊盘电连接。 如权利要求13所述的芯片封装结构,其特征在于,所述第一导电结构和所述第二导电结构分别位于所述封料层的第一开口和第二开口中,所述第一导电结构和第二导电结构包括:位于所述第一开口的侧壁和底部表面、所述第二开口的侧壁和底部表面以及所述封料层的部分顶部表面的电互连层,所述电互连层填充满或不填充满所述第一开口或第二开口。 如权利要求13所述的芯片封装结构,其特征在于,所述第一导电结构和所述第二导电结构分别位于所述封料层的第一开口和第二开口中,所述第一导电结构和第二导电结构包括:填充满所述第一开口的第一导电插塞和填充满所述第二开口的第二导电插塞。 如权利要求15所述的芯片封装结构,其特征在于,还包括: 电互连层,分布于所述封料层的部分表面、第一导电插塞的顶部表面和第二导电插塞的顶部表面。 如权利要求14或者16所述的芯片封装结构,其特征在于,还包括:分布于所述封料层和电互连层表面的阻焊层,所述阻焊层内具有若干第三开口,所述第三开口暴露出部分电互连层表面; 凸块,位于于所述第三开口内。 一种芯片封装结构,其特征在于,包括: 第一芯片,所述第一芯片包括相对的第一表面和第二表面,所述第一芯

片的第一表面具有若干第一焊盘; 第二芯片,所述第二芯片包括相对的第三表面和第四表面,所述第二芯片的第三表面具有若干第二焊盘,且所述第二芯片的面积大于第一芯片的面积; 所述第一芯片的第二表面与所述第二芯片的第三表面相结合,所述若干第二焊盘位于所述第一芯片和第二芯片的结合区域之外; 位于所述载板表面的封料层,所述封料层包覆所述第一芯片和第二芯片; 位于所述封料层内的第一导电结构和第二导电结构,所述第一导电结构与第一焊盘电连接,所述第二导电结构与第二焊盘电连接。 如权利要求18所述的芯片封装结构,其特征在于,所述第一导电结构和所述第二导电结构分别位于所述封料层的第一开口和第二开口中,所述第一导电结构和第二导电结构包括:位于所述第一开口的侧壁和底部表面、所述第二开口的侧壁和底部表面以及所述封料层的部分顶部表面的电互连层,所述电互连层填充满或不填充满所述第一开口或第二开口。 如权利要求18所述的芯片封装结构,其特征在于,所述第一导电结构和所述第二导电结构分别位于所述封料层的第一开口和第二开口中,所述第一导电结构和第二导电结构包括:填充满所述第一开口的第一导电插塞和填充满所述第二开口的第二导电插塞。 如权利要求20所述的芯片封装结构,其特征在于,还包括: 电互连层,分布于所述封料层的部分表面、第一导电插塞的顶部表面和第二导电插塞的顶部表面。 如权利要求19或者21所述的芯片封装结构,其特征在于,还包括:分布于所述封料层和电互连层表面的阻焊层,所述阻焊层内具有若干第三开口,所述第三开口暴露出部分电互连层表面; 凸块,分布于所述第三开口内。

技术领域

背景技术

附图说明

具体实施方式