Multichip-Montageeinheit mit einem Substrat mit mehreren vertikal eingebetteten Plättchen und Verfahren zur Herstellung derselben

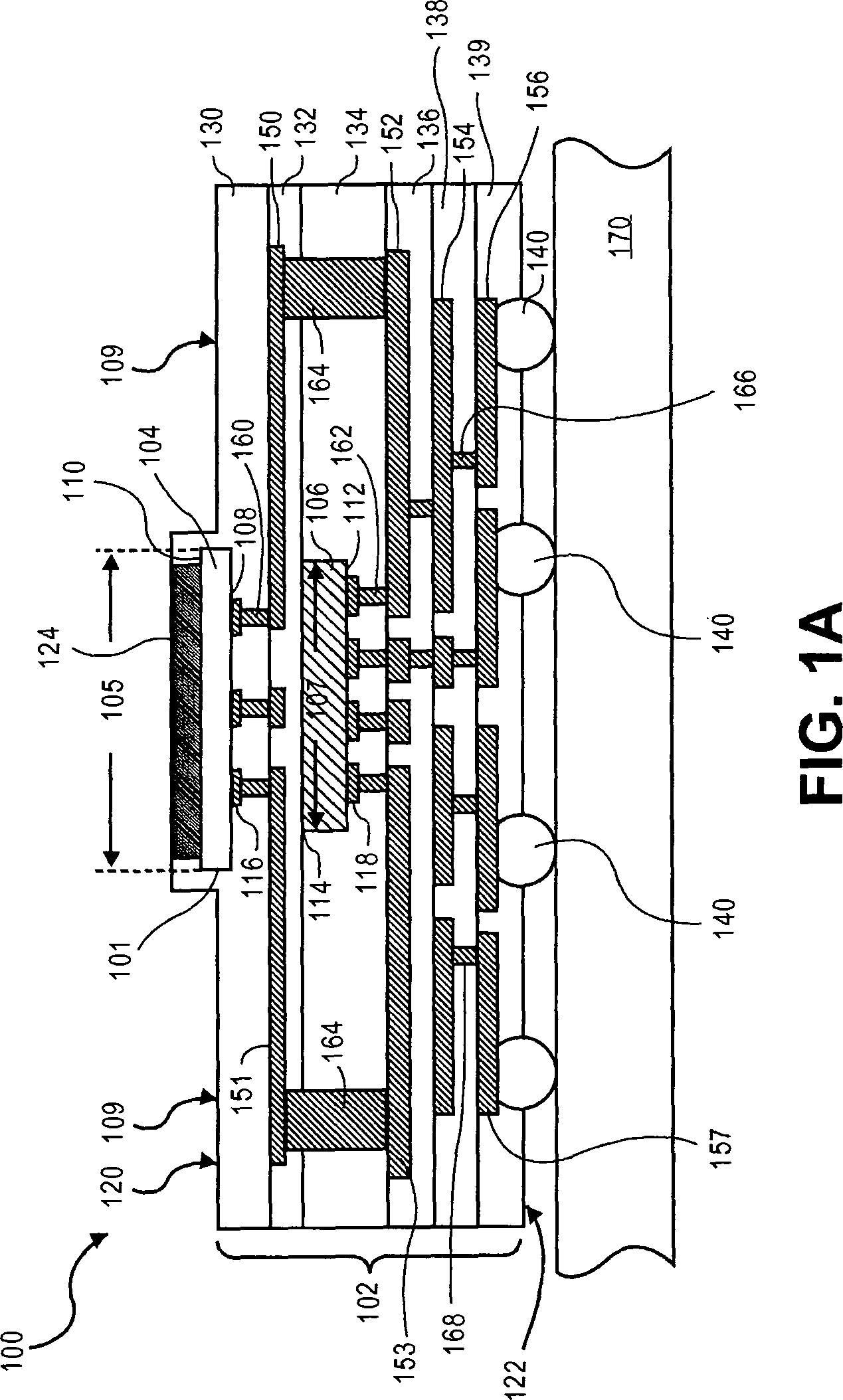

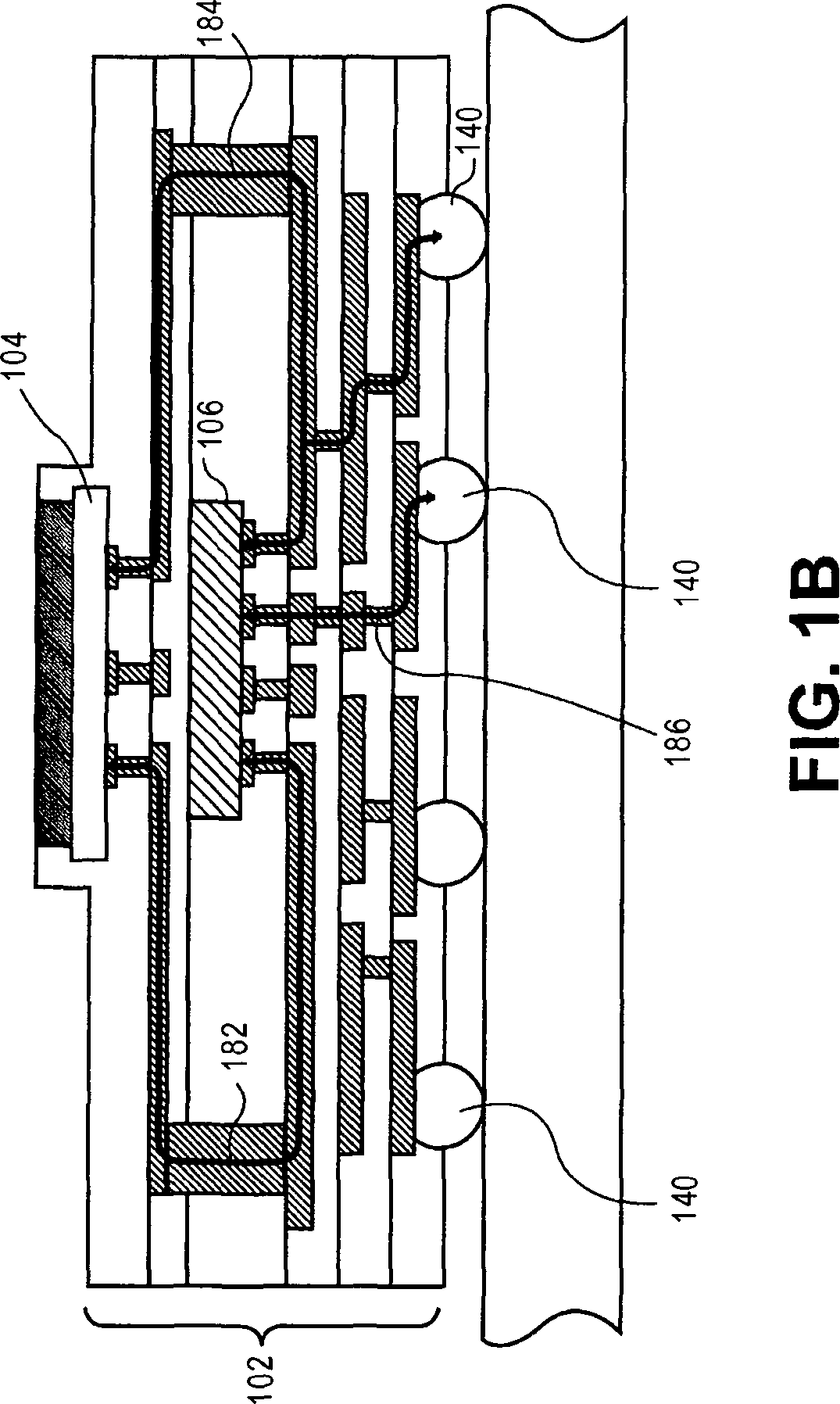

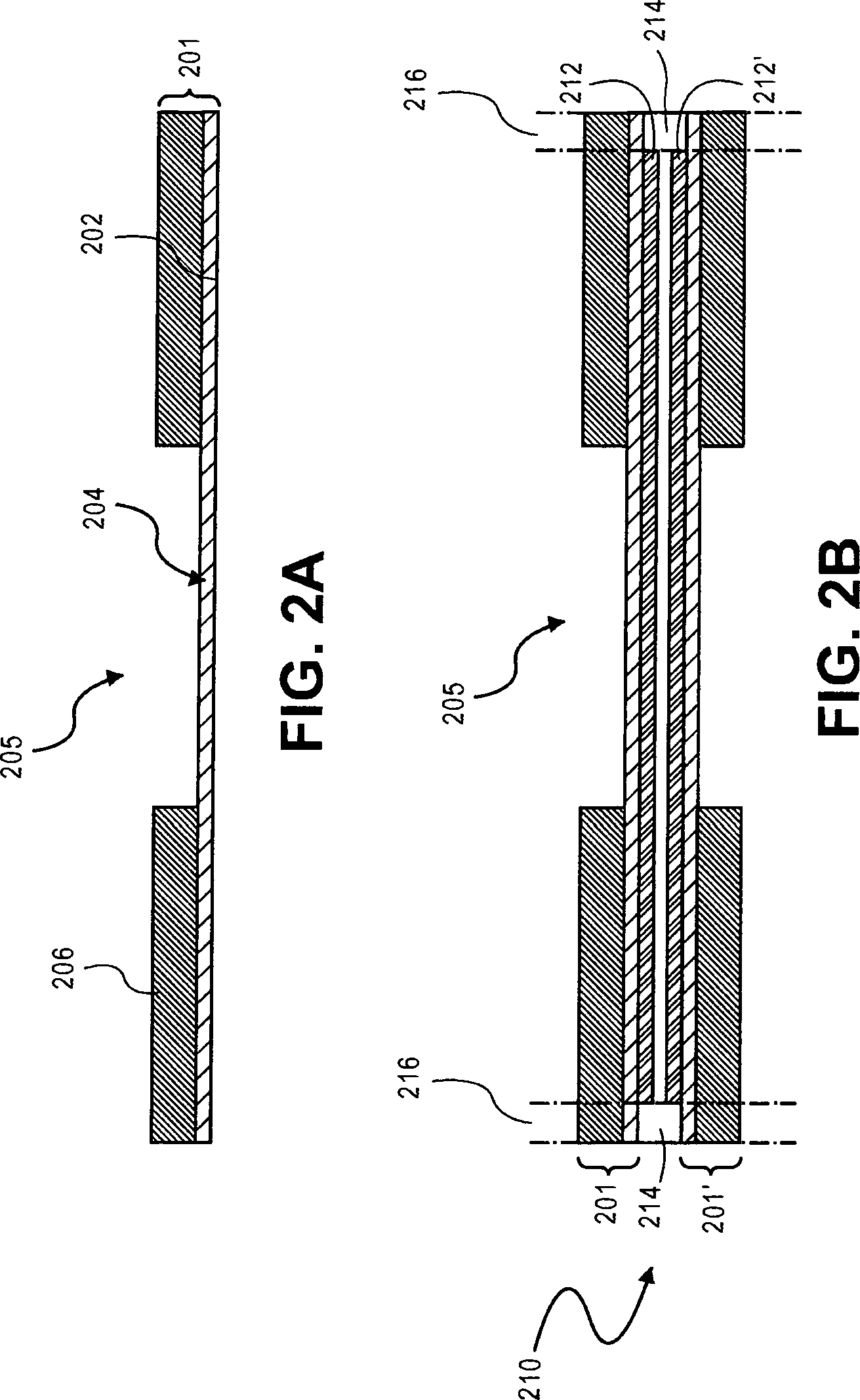

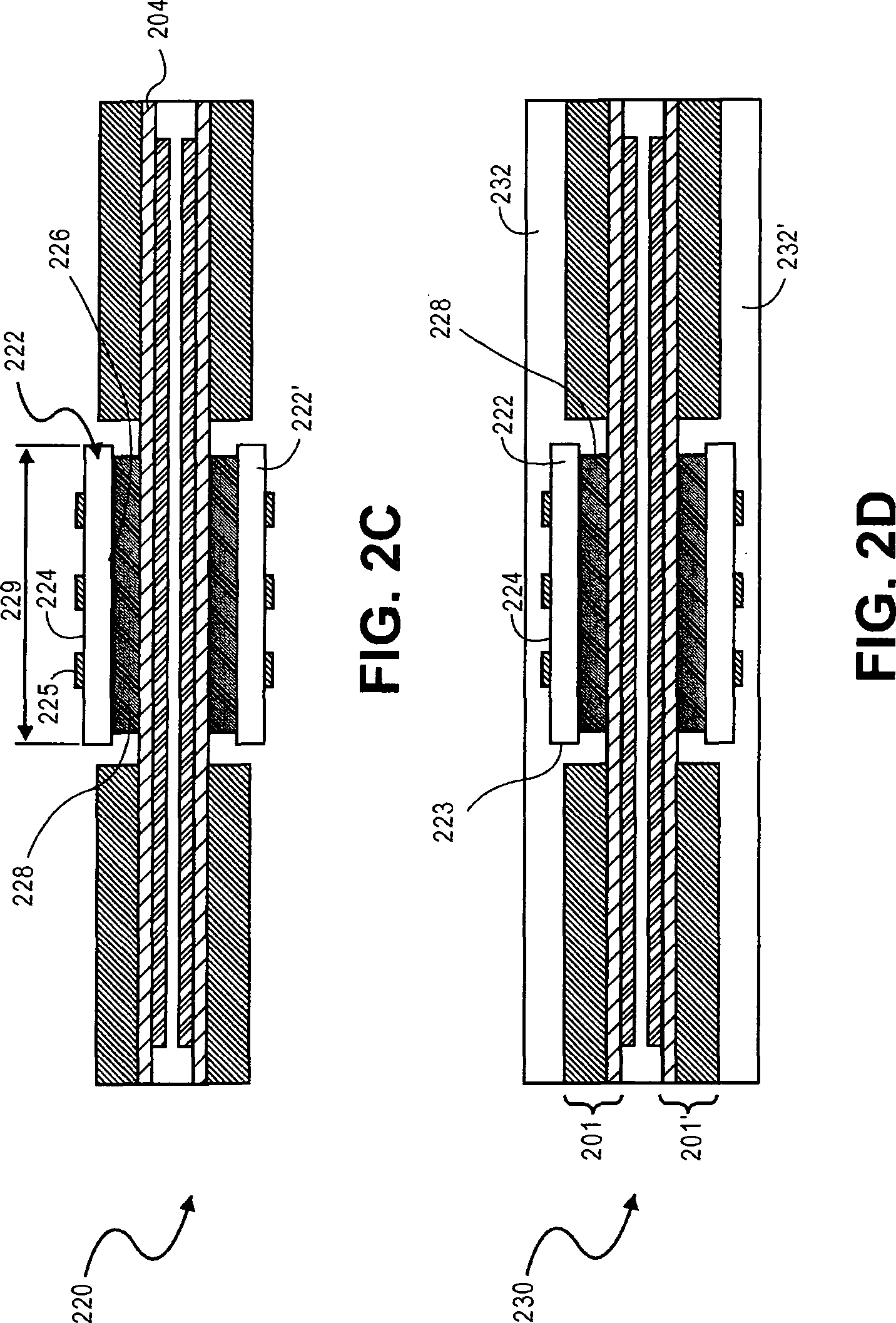

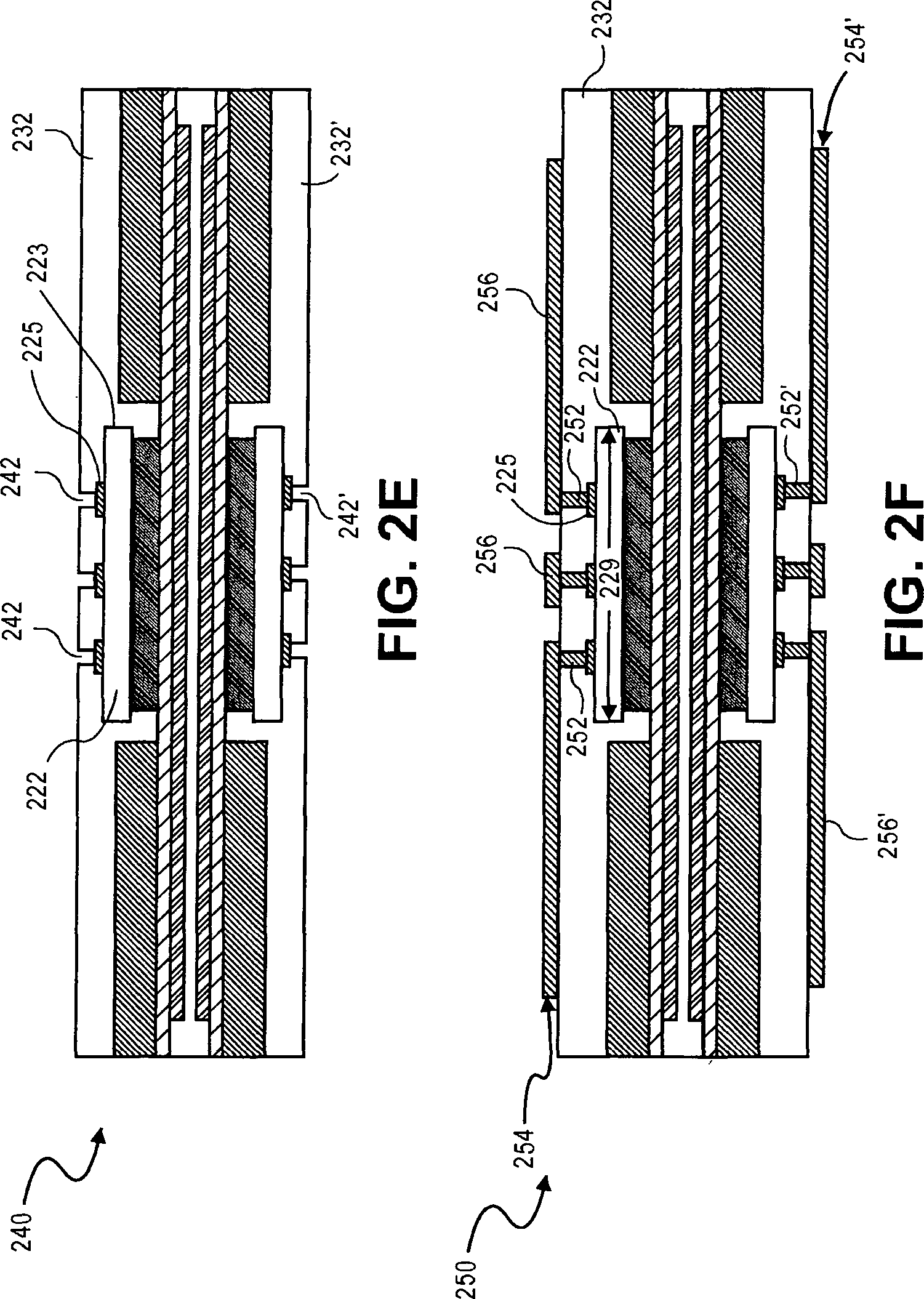

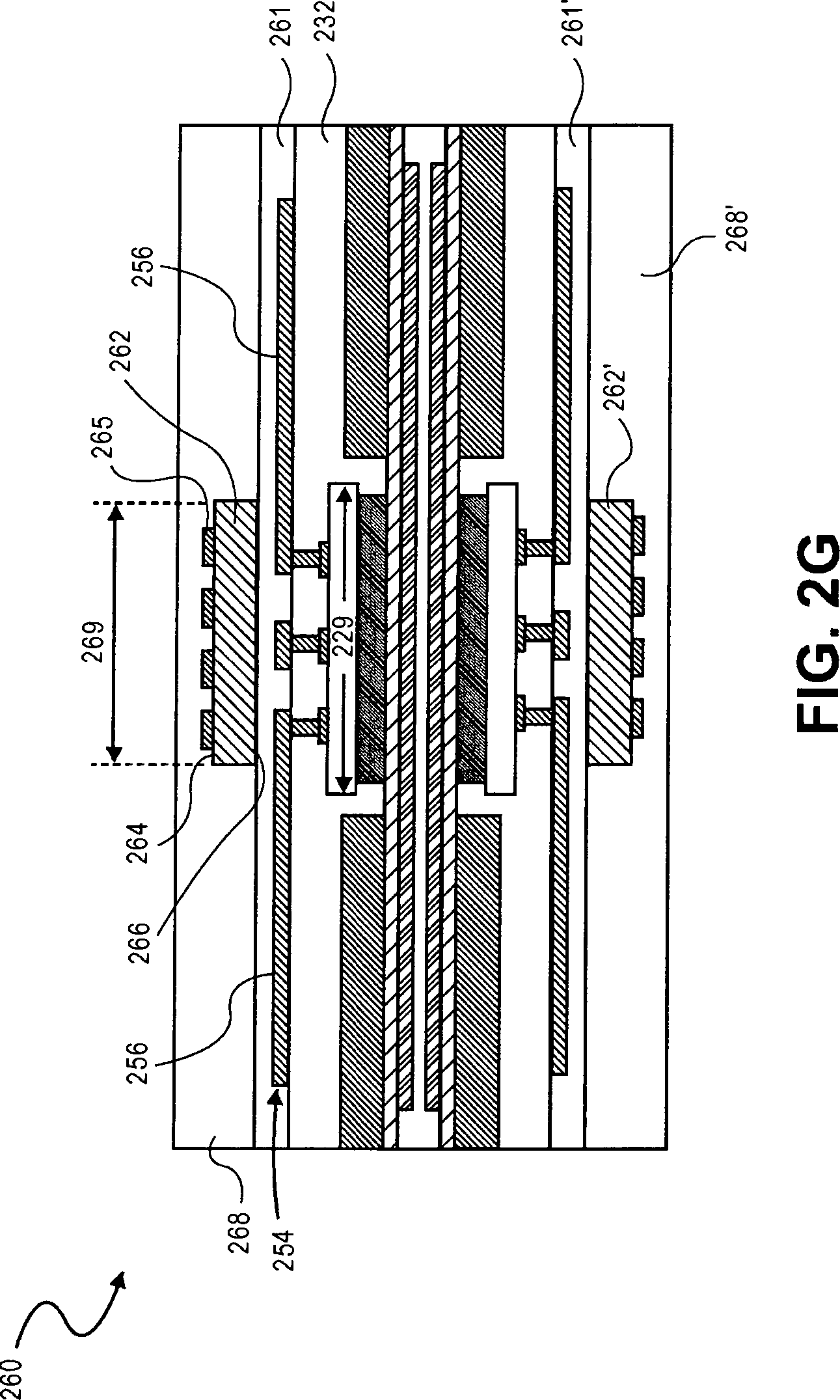

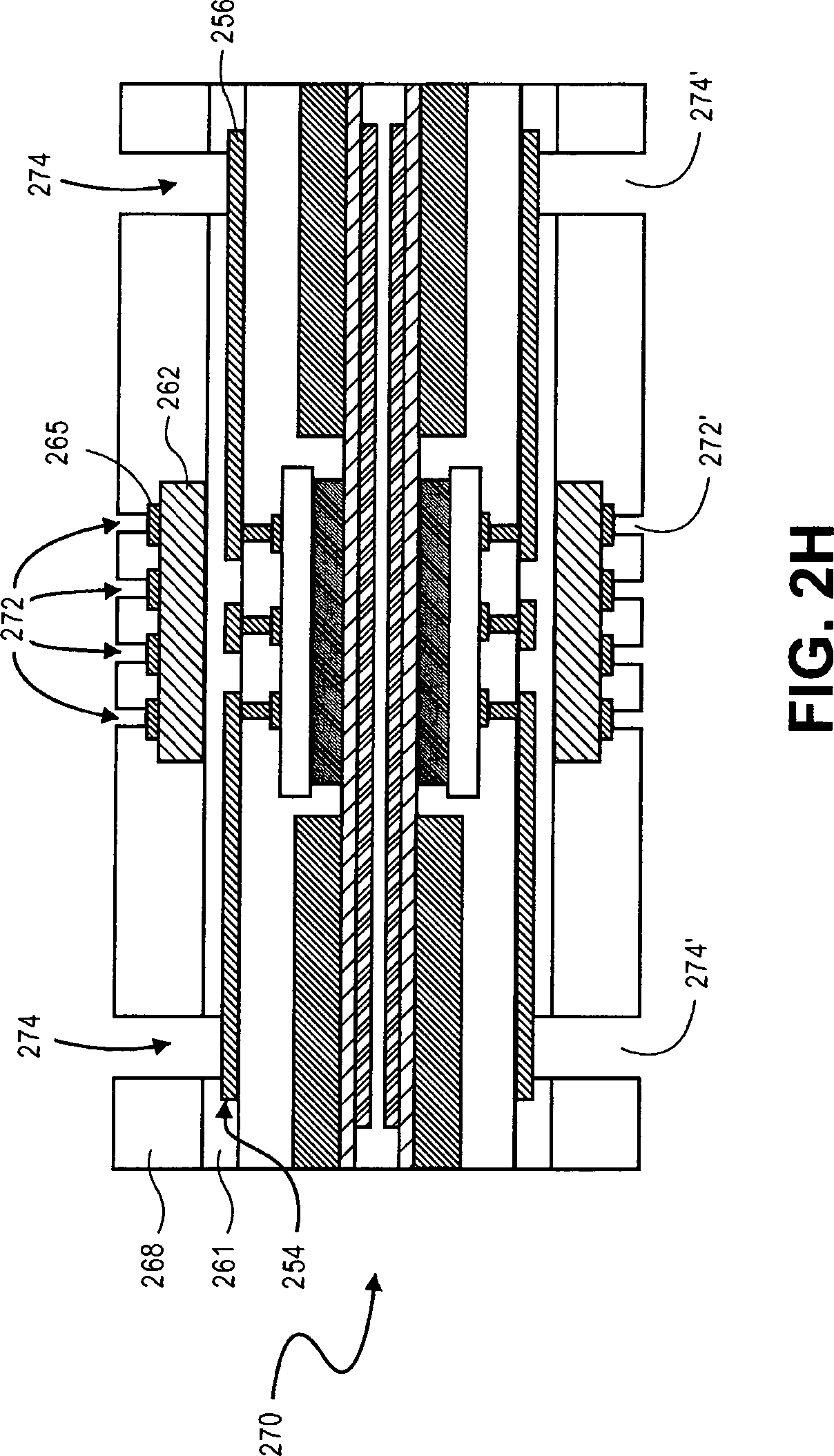

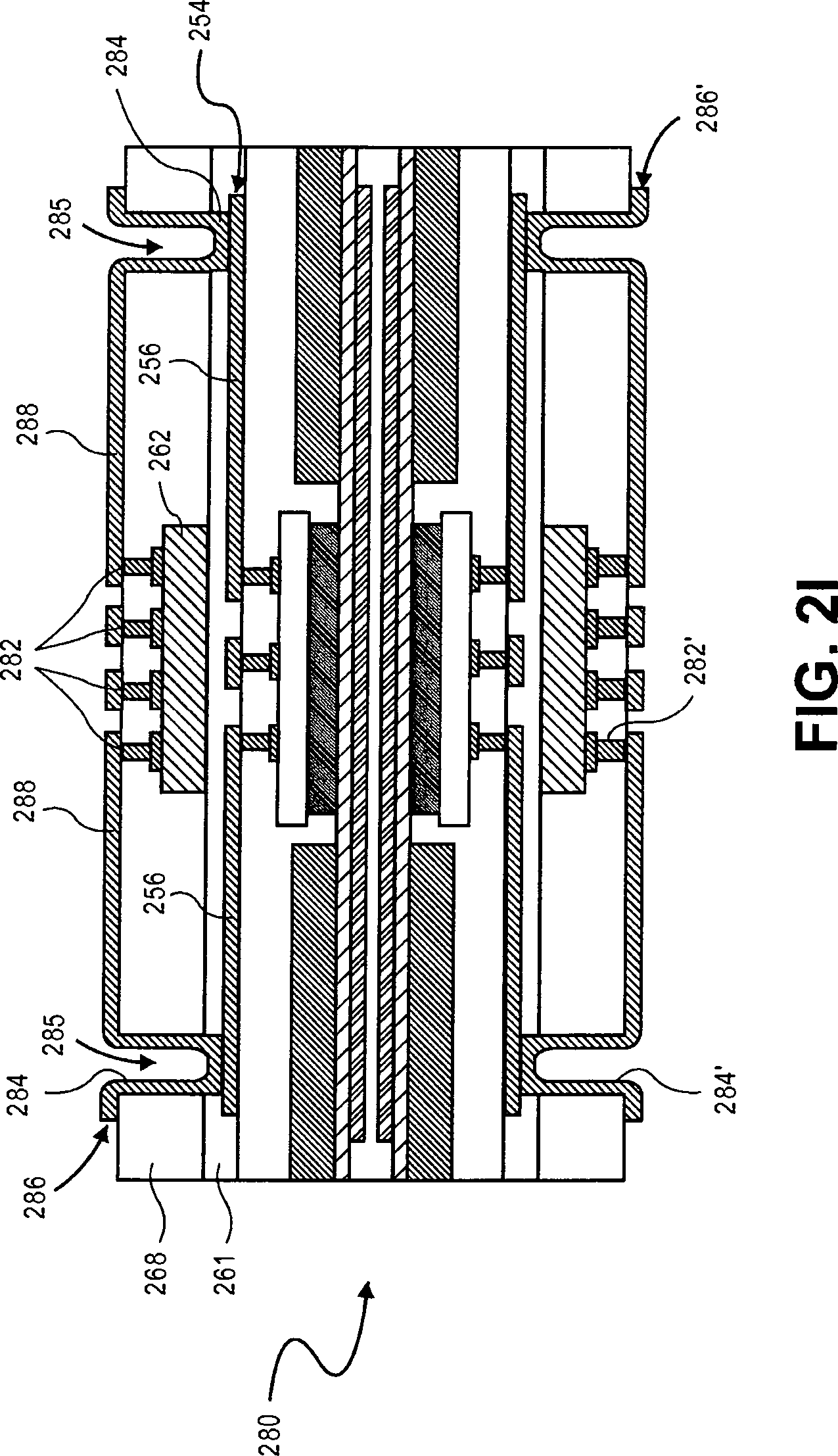

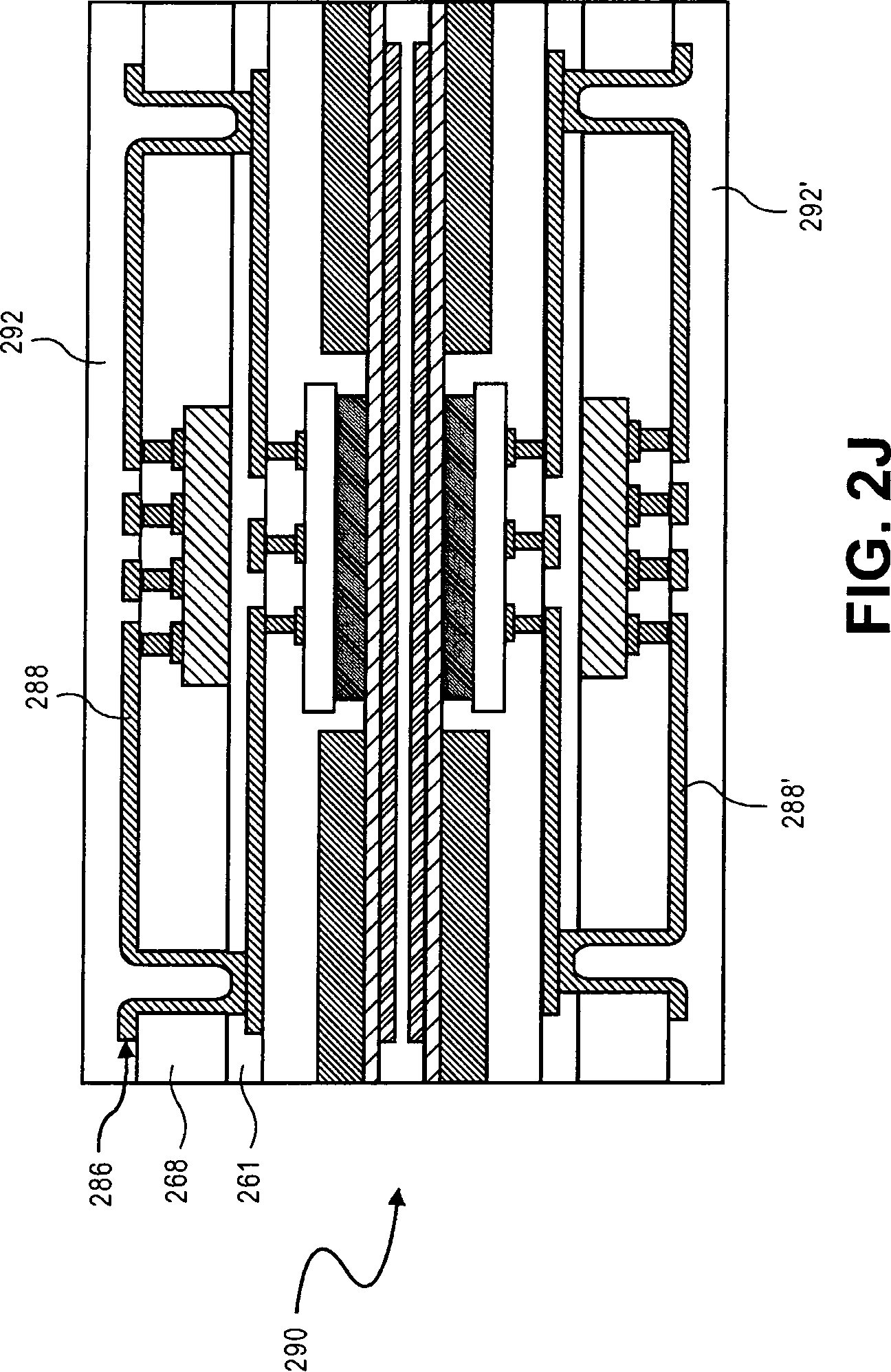

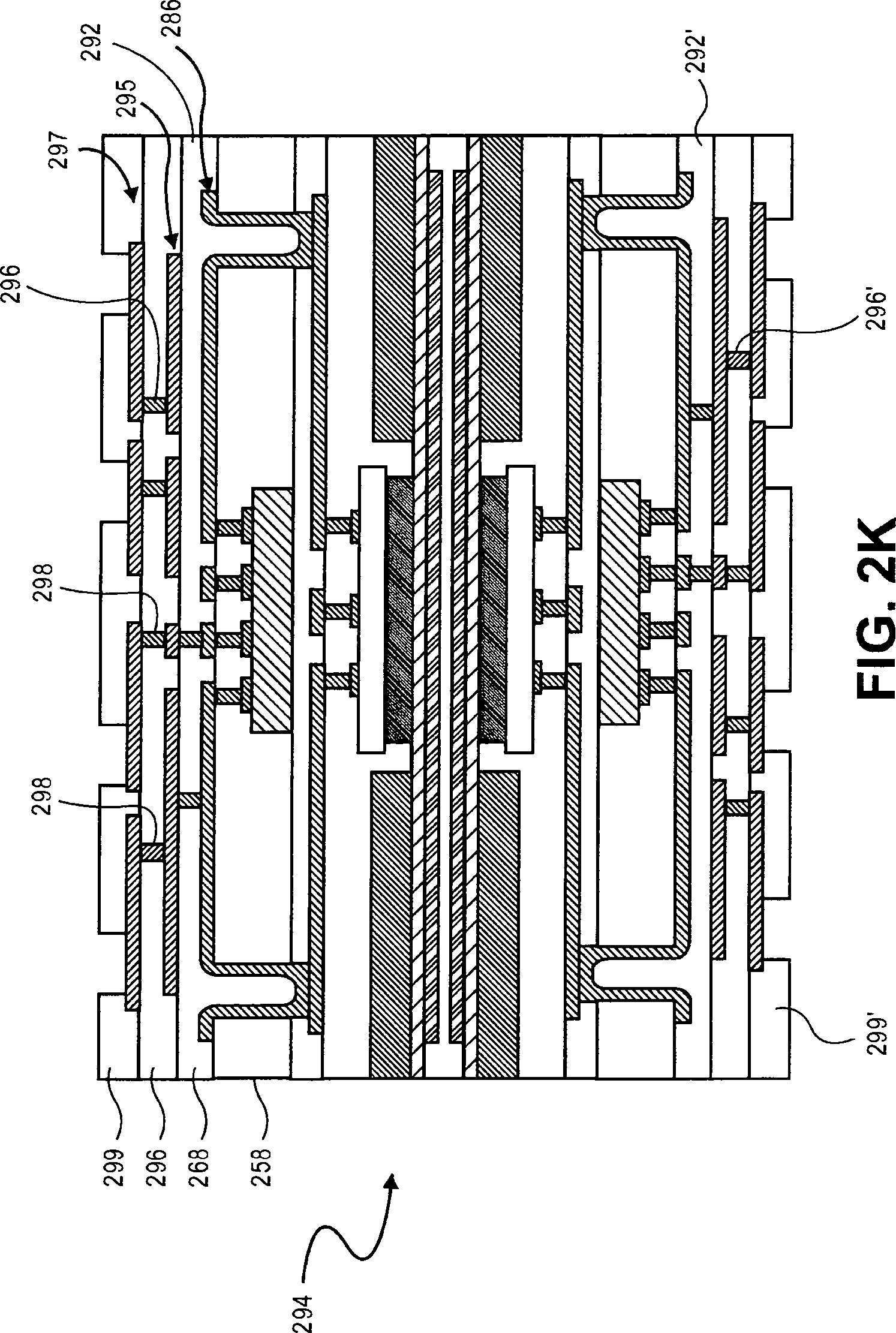

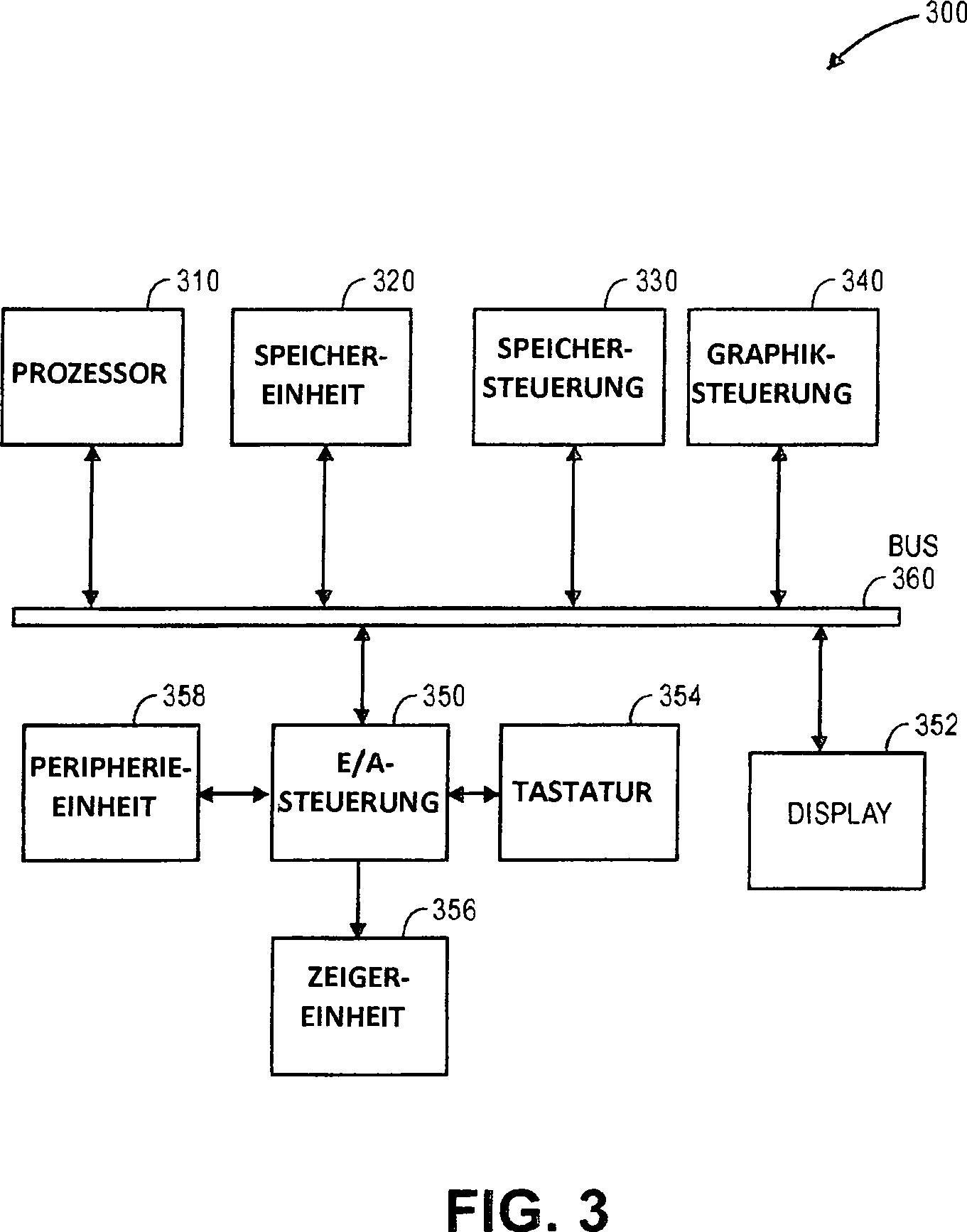

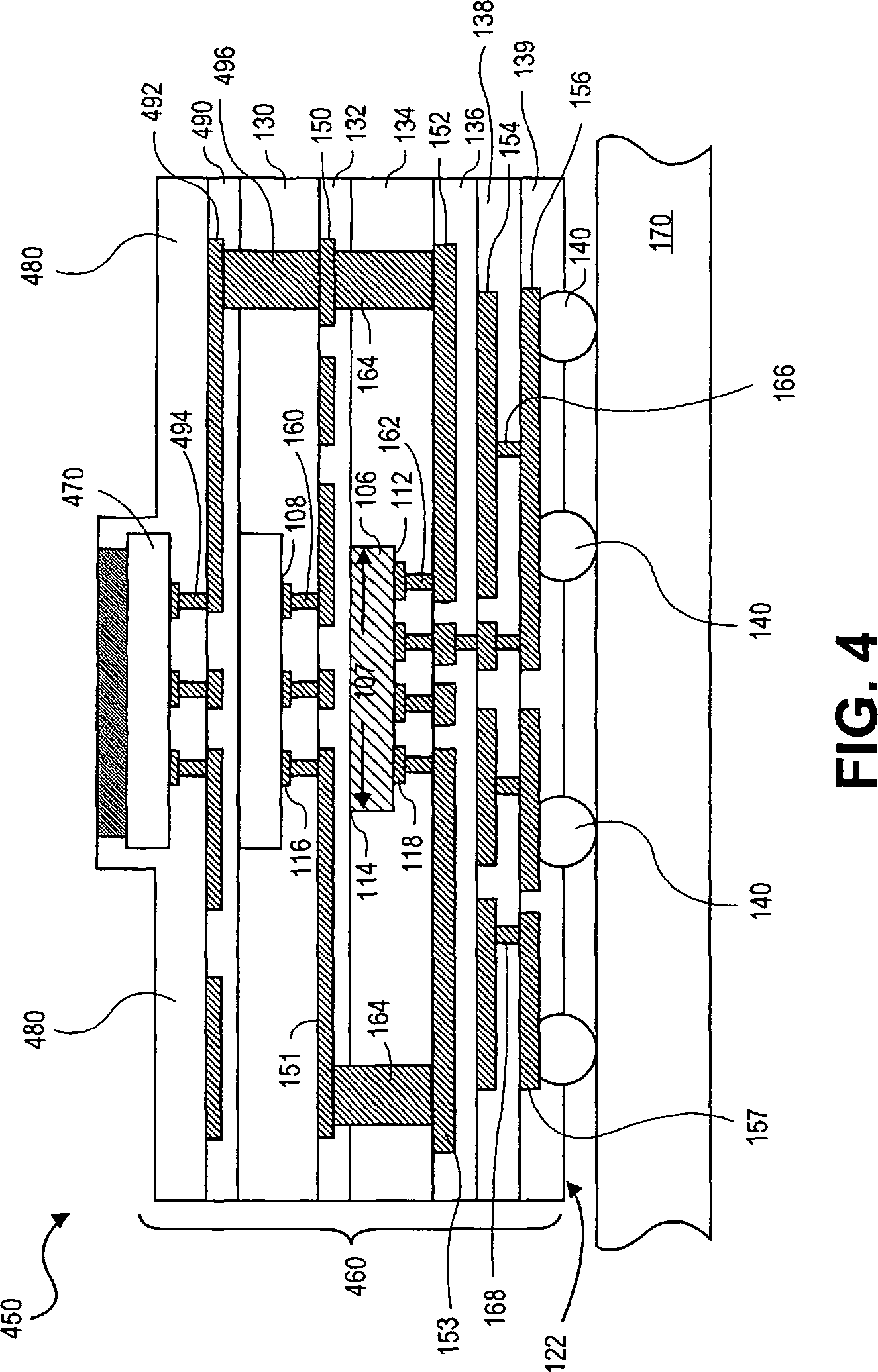

Offenbarte Ausführungsformen betreffen Halbleiter-Mikroelektronik-Montageeinheiten und Herstellungsverfahren. Der heutige Markt der Verbraucherelektronik verlangt oft nach komplexen Funktionen, welche sehr komplizierte Schaltungen erforderlich machen. Die Maßstabsverkleinerung zu immer kleineren Grundbaublöcken, z. B. Transistoren, hat mit jeder weiteren Generation den Einbau von noch komplizierteren Schaltungen auf einem Einzelplättchen ermöglicht. Andererseits werden, obwohl die Maßstabsverkleinerung typischerweise als Verringerung der Größe betrachtet wird, für eine fortgeschrittene Funktionalität und Leistung in einem Computersystem zunehmend mehrere montierte Plättchen miteinander verbunden. Auch kann die Größe einer speziellen Halbleiter-Montageeinheit in der Tat heraufgesetzt werden, um mehrere Plättchen in eine einzige Halbleiter-Montageeinheit einzubauen. Es können jedoch strukturelle Probleme entstehen, wenn versucht wird, mehrere montierte Plättchen zu verbinden. Zum Beispiel kann die Auswirkung von Unterschieden der Wärmeausdehnungskoeffizienten (Coefficients of Thermal Expansion, CTE) zwischen Komponenten, die in den Halbleiter-Montageeinheiten verwendet werden, zu schädlichen Defekten führen, wenn montierte Plättchen zusammengefügt werden. In ähnlicher Weise kann die Auswirkung von Unterschieden der Wärmeausdehnungskoeffizienten (CTE) zwischen Komponenten, die in einer einzelnen Halbleiter-Montageeinheit verwendet werden, als Ergebnis der Durchführung eines Halbleiterplättchen-Montageverfahrens für mehr als ein Plättchen in der einzelnen Montageeinheit zu schädlichen Defekten führen. Halbleiter-Montageeinheiten werden verwendet, um einen Chip oder ein Plättchen einer integrierten Schaltung (Integrated Circuit, IC) zu schützen, und auch, um das Plättchen mit einer elektrischen Schnittstelle zu externen Schaltungen versehen. Mit steigendem Bedarf für kleinere elektronische Einheiten werden Halbleiter-Montageeinheiten so ausgestaltet, dass sie noch kompakter sind und eine größere Schaltungsdichte unterstützen müssen. Zum Beispiel wird bei einigen Halbleiter-Montageeinheiten nun ein kernloses Substrat verwendet, welches nicht die dicke Harzkernschicht umfasst, die man üblicherweise in herkömmlichen Substraten findet. Ferner führt der Bedarf für Einheiten höherer Leistung dazu, dass eine verbesserte Halbleiter-Montageeinheit benötigt wird, welche eine Mischtechnologie-Plättchenstapelung ermöglicht oder eine Plättchenstapelungsmöglichkeit bereitstellt, wobei ein dünnes Montageprofil und eine niedrige Gesamtverformung bewahrt werden, um mit einem anschließenden Verfahren des Zusammenbauens kompatibel zu sein. Um die Art und Weise zu verstehen, wie Ausführungsformen erhalten werden, wird eine speziellere Beschreibung verschiedener Ausführungsformen, die nachstehend kurz beschrieben sind, unter Bezugnahme auf die angehängten Zeichnungen gegeben. Diese Zeichnungen zeigen Ausführungsformen, welche nicht notwendigerweise maßstabsgetreu sind und nicht als im Umfang beschränkt anzusehen sind. Einige Ausführungsformen werden durch die Verwendung der begleitenden Zeichnungen mit zusätzlicher Ausführlichkeit und in zusätzlichen Einzelheiten beschrieben und erläutert, in welchen: Es wird eine Multichip-Montageeinheit (MCP), welche mehrere vertikal eingebettete Plättchen aufweist, und ihr Herstellungsverfahren beschrieben. Es wird nun auf Zeichnungen Bezug genommen, wobei gleiche Strukturen mit gleichen Suffix-Bezugszeichen versehen sein können. Um die Struktur verschiedener Ausführungsformen deutlicher zu zeigen, sind die hierin enthaltenen Zeichnungen diagrammartige Darstellungen der IC-Strukturen. Daher kann das tatsächliche Aussehen der hergestellten IC-Strukturen, zum Beispiel in einer Mikroaufnahme, anders sein, wobei es immer noch die beanspruchte Struktur der veranschaulichten Ausführungsformen beinhaltet. Überdies zeigen die Zeichnungen möglicherweise nur Strukturen, die geeignet sind, um die veranschaulichten Ausführungsformen zu verstehen. Weitere Strukturen, die auf dem Fachgebiet bekannt sind, sind möglicherweise nicht enthalten, um die Klarheit der Zeichnungen zu bewahren. Außerdem sind in der vorliegenden Beschreibung zahlreiche spezielle Einzelheiten ausgeführt, um für ein gründliches Verständnis der Ausführungsformen der vorliegenden Erfindung zu sorgen. In anderen Fällen sind wohlbekannte Halbleiterverarbeitungs- und Montagetechniken nicht in speziellen Einzelheiten ausgeführt worden, um Ausführungsformen der vorliegenden Erfindung nicht unnötig zu verschleiern. Ausführungsformen der vorliegenden Erfindung umfassen eine Multichip-Montageeinheit, welche ein Substrat mit mehreren vertikal angeordneten darin eingebetteten Plättchen aufweist. Das Substrat umfasst eine Anschlussfleckseite und eine Plättchenseite. Ein erstes Plättchen und ein zweites Plättchen sind derart in das Substrat eingebettet, dass sich das zweite Plättchen zwischen dem ersten Plättchen und der Anschlussfleckseite des Substrats befindet. Das Substrat der Montageeinheit umfasst mehrere Leitungsschichten, isolierende Schichten und Durchkontaktierungen zum Erzeugen einer Zwischenverbindungsstruktur in dem Substrat, welche für eine elektrische Verbindung zwischen dem ersten Plättchen und dem zweiten Plättchen sorgt. In einer Ausführungsform der vorliegenden Erfindung befindet sich zwischen dem ersten Plättchen und dem zweiten Plättchen mindestens eine Leitungsschicht. Die Multichip-Montageeinheit, welche ein Substrat mit einem vertikal angeordneten und darin eingebetteten Plättchen aufweist, kann gemäß Ausführungsformen der vorliegenden Erfindung über ein Bumpless-Build-up-Layer(BBUL)-Verfahren gebildet werden. In einer Ausführungsform der vorliegenden Erfindung wird das erste Plättchen an einem temporären Träger befestigt, und eine isolierende Schicht und eine Leitungsschicht werden über dem ersten Plättchen und um dieses herum gebildet und betten das erste Plättchen darin ein. Anschließend wird ein zweites Plättchen an einer der isolierenden Schichten befestigt, und weitere isolierende Schichten und Leitungsschichten werden auf dem zweiten Plättchen und um dieses herum gebildet, wodurch sie das zweite Plättchen ebenso in dem Substrat einbetten. Auf diese Weise werden sowohl das erste als auch das zweite Plättchen in das Substrat. eingebettet, und elektrische Zwischenverbindungen werden in dem Substrat gebildet (Substratleitung), welche das erste und das zweite Plättchen elektrisch verbinden. Der Träger kann anschließend entfernt werden, um ein kernloses Substrat zu erzeugen. Ausführungsformen der vorliegenden Erfindung ermöglichen die Bildung der Multichip-Montageeinheit mit einer dünnen Konfiguration der Montageeinheit und einer kleinen Standfläche, wodurch wertvoller Raum auf Hauptplatinen von Einheiten eingespart wird. Außerdem ermöglichen Ausführungsformen der vorliegenden Erfindung die elektrische Verbindung von zwei Plättchen ohne die Anwendung der Montageeinheit-auf-Montageeinheit(Package-on-Package, POP)-Technologie, welche die Oberflächenmontagetechnologie (Surface Mount Technology, SMT) erforderlich macht, welche aufgrund von Substratverformung für Zuverlässigkeitsprobleme anfällig sein kann. Außerdem wird in Ausführungsformen der vorliegenden Erfindung ein Niedertemperatur-Bumpless-Build-up-Layer(BBUL)-Verfahren angewendet, um das Substrat zu bilden, um die Auswirkungen nicht zueinander passender Wärmeausdehnungskoeffizienten (CTE) zwischen den eingebetteten Plättchen und dem Substrat zu verringern oder zu eliminieren, wodurch die Herstellung einer sehr ebenen Multichip-Montageeinheit ermöglicht wird. Das erste Plättchen 104 weist eine erste Standfläche oder einen ersten Flächenbereich 105 auf, und das zweite Plättchen 106 weist eine zweite Standfläche oder einen zweiten Flächenbereich 107 auf. In einer Ausführungsform der vorliegenden Erfindung weist das erste Plättchen 104 eine größere Standfläche als das zweite Plättchen 106 auf. Das zweite Plättchen 106 ist in das Substrat 102 eingebettet und ist zwischen dem ersten Plättchen 104 und der Anschlussfleckseite 122 des Substrats 102 angeordnet. Auf diese Weise sind das erste Plättchen 104 und das zweite Plättchen 106 vertikal in dem Substrat 102 angeordnet. In einer Ausführungsform der vorliegenden Erfindung liegt mindestens ein Abschnitt der Standfläche 107 des zweiten Plättchens 106 innerhalb der Standfläche 105 des ersten Plättchens 104. In einer Ausführungsform, wie sie in Die Anschlussfleckseite 122 umfasst mehrere leitfähige Kontaktflecken und/oder Leitungsspuren, mit welchen mehrere externe leitfähige Kontakte 140 verbunden sind. Externe leitfähige Kontakte 140 sorgen für eine elektrische Verbindung der Montageeinheit 100 mit anderen Einheiten. Das Substrat 102 umfasst mehrere Leitungsschichten, eine Isolierungsschicht und Durchkontaktierungen, welche zusammen eine Substrat-Zwischenverbindungsstruktur erzeugen. Die Substrat-Zwischenverbindungsstruktur stellt eine elektrische Verbindung zwischen dem ersten Plättchen 104 und dem zweiten Plättchen 106 sowie eine elektrische Verbindung des ersten und zweiten Plättchens mit externen elektrischen Kontakten 140 bereit, die auf der Anschlussfleckseite 122 ausgebildet sind. Die Substrat-Zwischenverbindungsstruktur stellt direkte elektrische Verbindungen des ersten Plättchens 104 mit dem zweiten Plättchen 106 bereit, so dass Signale direkt zwischen dem ersten Plättchen und dem zweiten Plättchen ausgetauscht werden können. Die Substrat-Zwischenverbindungsstruktur kann auch elektrische Verbindungen zwischen dem zweiten Plättchen 106 und externen leitfähigen Kontakten 140 umfassen. In einigen Ausführungsformen der vorliegenden Erfindung stellt die Substrat-Zwischenverbindungsstruktur auch eine elektrische Verbindung zwischen dem ersten Plättchen 104 und externen leitfähigen Kontakten 140 bereit. In anderen Ausführungsformen gibt es keine elektrischen Verbindungen zwischen den externen leitfähigen Kontakten 140 und dem ersten Plättchen 104. Das heißt, in einer Ausführungsform der vorliegenden Erfindung führen alle externen Verbindungen zu dem ersten Plättchen 104 durch das zweite Plättchen 106. In einer speziellen Ausführungsform werden alle anderen elektrischen Signale zu dem ersten Plättchen 104 außer Spannungsversorgungssignalen durch das zweite Plättchen 106 bereitgestellt. In einer Ausführungsform der vorliegenden Erfindung umfasst das Substrat 102 eine erste isolierende Schicht 130, wie in Eine zweite Leitungsschicht 152, welche mehrere leitfähige Spuren umfasst, ist auf der dritten isolierenden Schicht 134 angeordnet. In einer Ausführungsform der vorliegenden Erfindung leiten eine oder mehrere leitfähige Spuren 153 der zweiten Leitungsschicht 152 Signale vom Rand des Substrats 102 in die Standfläche 107 des zweiten Plättchens 106 hinein, um eine elektrische Verbindung zu dem zweiten Plättchen 106 bereitzustellen. Mehrere leitfähige Durchkontaktierungen 162 sind in der dritten isolierenden Schicht 134 zwischen leitfähigen Spuren der zweiten Leitungsschicht 152 und elektrischen Kontakten 118 des zweiten Plättchens 106 ausgebildet, um Spuren der zweiten Leitungsschicht 152 elektrisch mit elektrischen Kontakten 118 auf dem zweiten Plättchen zu verbinden. Außerdem sind mehrere leitfähige Durchkontaktierungen 164 durch die zweite isolierende Schicht 132 und die dritte isolierende Schicht 134 hindurch ausgebildet, um elektrisch Spuren der zweiten Leitungsschicht 152 mit Spuren der ersten Leitungsschicht 150 zu verbinden, wie in In einer Ausführungsform der vorliegenden Erfindung weisen die leitfähigen Durchkontaktierungen 164 einen größeren Durchmesser als die leitfähigen Durchkontaktierungen 162 auf. Es sei angemerkt, dass sich die leitfähigen Durchkontaktierungen 164 tiefer in das Substrat hinein erstrecken als die leitfähigen Durchkontaktierungen 162. In einer Ausführungsform der vorliegenden Erfindung weisen die Durchkontaktierungen 164 einen Durchmesser von 100 μm bis 150 μm auf, während die Durchkontaktierungen 162 einen Durchmesser von 30 μm bis 50 μm aufweisen. Dementsprechend wird durch Erhöhen des Durchmessers der leitfähigen Durchkontaktierungen 164 das Seitenverhältnis (Höhe:Breite) der leitfähigen Durchkontaktierungen 164 verringert, wodurch die zuverlässige Füllung der leitfähigen Durchkontaktierungen ermöglicht wird. Es versteht sich, dass, obwohl die Durchkontaktierung 164 als vollständig mit einem leitfähigen Film gefüllt dargestellt ist, die Durchkontaktierung 164 so gebildet werden kann, dass nur die Seitenwände der Durchkontaktierung 164 einen darin ausgebildeten leitfähigen Film aufweisen und die Mitte ungefüllt bleibt. Die nachfolgende Bildung einer isolierenden Schicht kann genutzt werden, um das ungefüllte Volumen der Durchkontaktierung zu füllen, vgl. zum Beispiel Eine vierte isolierende Schicht 136 ist auf der dritten isolierenden Schicht 134 und auf Spuren der zweiten Leitungsschicht 152 und um diese herum angeordnet. In einer Ausführungsform der vorliegenden Erfindung werden nur zwei Leitungsschichten 150 und 152 bereitgestellt, eine Leitungsschicht (150) zum Bereitstellen leitfähiger Spuren zum Leiten von Signalen aus der Standfläche 105 des ersten Plättchens 104 heraus und eine Leitungsschicht 152 zum Bereitstellen leitfähiger Spuren zum Leiten von Signalen in die Standfläche 107 des zweiten Plättchens 106 hinein. Wenn die Leitungsschicht 152 die letzte Leitungsschicht des Substrats ist, können in der vierten isolierenden Schicht 136 mehrere Kontaktflecköffnungen ausgebildet sein, um Kontaktflecken auf Spuren 153 der zweiten Leitungsschicht zu definieren, zu welchen anschließend externe elektrische Kontakte 140 gebildet werden. Falls erwünscht, können jedoch in Abhängigkeit von speziellen Leitungserfordernissen zusätzliche Leitungsschichten, isolierende Schichten und Durchkontaktierungen eingebaut werden. Zum Beispiel kann auf der vierten isolierenden Schicht 136 eine dritte Leitungsschicht 154 angeordnet sein, welche mehrere leitfähige Spuren umfasst. Mehrere leitfähige Durchkontaktierungen 166 können durch die vierte isolierende Schicht hindurch ausgebildet sein, um eine elektrische Verbindung zwischen leitfähigen Spuren der zweiten Leitungsschicht 152 und leitfähigen Spuren der dritten Leitungsschicht 154 bereitzustellen. Auf der vierten isolierenden Schicht 136 und auf leitfähigen Spuren der dritten Leitungsschicht 154 und um diese herum kann eine fünfte isolierende Schicht 138 ausgebildet sein. Ferner kann auf der fünften isolierenden Schicht 138 eine vierte Leitungsschicht 156 angeordnet sein. Wenn die vierte Leitungsschicht 156 die letzte Leitungsschicht ist, kann sie mehrere Leitungsschichten/leitfähige Kontaktflecken 157 umfassen, mit welchen elektrische Kontakte 140 verbunden sind. Die vierte Leitungsschicht 156 kann auch Leitungsspuren 157 umfassen, um den Ort der Kontaktflecken umzuverteilen. Mehrere Durchkontaktierungen 168 sind durch die fünfte isolierende Schicht 138 hindurch ausgebildet, um Spuren/Kontaktflecken der vierten Leitungsschicht 156 elektrisch mit Spuren der dritten Leitungsschicht 154 zu verbinden. Eine letzte, sechste isolierende Schicht 139, z. B. eine Lötmaskenschicht, kann auf der fünften isolierenden Schicht 138 und auf der vierten Leitungsschicht 156 und um diese herum ausgebildet sein. In der Lötmaskenschicht 139 sind Öffnungen ausgebildet, um zu ermöglichen, dass externe elektrische Kontakte 140 an den Kontaktflecken der Leitungsschicht 156 befestigt werden. In Ausführungsformen der vorliegenden Erfindung kann die Montageeinheit 100 einen Plättchenbefestigungsfilm (Die Attach Film, DAF) 124 umfassen, z. B. einen Die-Bonding-Film (DBF) auf Epoxidbasis, der an der Rückfläche 110 des ersten Plättchens 104 befestigt ist. In anderen Ausführungsformen wird der Plättchenbefestigungsfilm (DAF) 124 entfernt, um einen Zugang zu der Rückfläche 110 des ersten Plättchens 104 ermöglichen. Der DAF 124 wird nicht als Teil des Substrats 102 angesehen. Außerdem kann das Substrat 102 in Ausführungsformen der vorliegenden Erfindung ein kernloses Substrat sein, weil es durch ein Aufbauschichtverfahren auf einem Träger gebildet wird, wobei der Träger schließlich von dem Substrat 102 entfernt wird. Ferner kann das Substrat 102 als kernloses Substrat angesehen werden, weil es keinen dicken Kern wie z. B. ein Epoxidharz mit faserverstärktem Glas umfasst. Wie in In einer Ausführungsform der vorliegenden Erfindung handelt es sich bei den externen leitfähigen Kontakten 140 um Lötkugeln, welche in einer Matrixform angeordnet sind, um ein Ball Grid Array bereitzustellen. Die externen leitfähigen Kontakte 140 müssen jedoch nicht notwendigerweise die Form von Kugeln annehmen und können andere Formen oder Strukturen aufweisen, z. B., ohne darauf beschränkt zu sein, Säulen, Bumps, Anschlussflecken und Stifte. Externe Kontakte 140 ermöglichen die elektrische Verbindung und Kommunikation der Halbleiter-Montageeinheit 100 mit einem Verankerungssubstrat 170. Wenn zum Beispiel die Halbleiter-Montageeinheit 100 ein Teil eines Computers oder eines Handgeräts, z. B. eines Smartphones oder eines Handlesegeräts ist, ist das Verankerungssubstrat 170 eine Hauptplatine. In anderen Ausführungsformen kann das Verankerungssubstrat 170 eine andere Halbleiter-Montageeinheit sein, um eine Montageeinheit-auf-Montageeinheit(POP)-Einheit herzustellen. Die Halbleiter-Montageeinheit 100, welche ein Substrat mit mehreren vertikal eingebetteten Plättchen aufweist, umfasst ein vollständig eingebettetes und umgebenes zweites Plättchen 106. Wie in dieser Beschreibung verwendet, bedeutet „vollständig eingebettet und umgeben”, dass alle Flächen des zweiten Plättchens 106 mit einem isolierenden Film des Substrats 102 in Kontakt stehen. Die Halbleiter-Montageeinheit 100 umfasst auch ein vollständig eingebettetes erstes Plättchen 104. Wie in dieser Beschreibung verwendet, bedeutet „vollständig eingebettet”, dass die aktive Fläche 108 und die gesamten Seitenwände des ersten Plättchens 104 mit einem isolierenden Film des Substrats 102 in Kontakt stehen. Das erste Plättchen 104 ist jedoch nicht „umgeben”, da die Rückfläche 110 des ersten Plättchens 104 nicht mit einem isolierenden Film des Substrats 102 in Kontakt steht. Zwei Ausführungsformen eines „vollständig eingebetteten” ersten Plättchens 104 werden hierin beschrieben. In einer ersten Ausführungsform, wie in Im Gegensatz zu den obigen Definitionen eines „vollständig eingebetteten und umgebenen” und „vollständig eingebetteten” Plättchens ist ein „teilweise eingebettetes” Plättchen ein Plättchen, bei welchem eine vollständige Fläche, jedoch nur ein Teil der Seitenwände mit einem isolierenden Film eines Substrats 102 in Kontakt steht. Im weiteren Gegensatz ist ein „nicht eingebettetes” Plättchen ein Plättchen, bei welchem höchstens eine Fläche und kein Teil der Seitenwände mit einem verkapselnden Film eines Substrats in Kontakt steht. In einer Ausführungsform der vorliegenden Erfindung werden die Durchkontaktierungen 242 unter Anwendung eines semiadditiven Verfahrens (Semi-Additive Process, SAP) gleichzeitig mit der Bildung der leitfähigen Spuren 256 der ersten Leitungsschicht 254 gefüllt, um die leitfähigen Durchkontaktierungen 252 zu bilden. Bei einem semiadditiven Verfahren wird über der Fläche des isolierenden Films 232 sowie in den Durchkontaktierungsöffnungen 242 und den Seitenwänden der Durchkontaktierungsöffnungen 242 eine stromlose Keimschicht, z. B. eine stromlose Kupferkeimschicht, gebildet, welche zum Beispiel eine Dicke von weniger als 1 Mikrometer aufweist. Anschließend wird auf der stromlosen Keimschicht eine Photoresistschicht gebildet und belichtet und entwickelt, wodurch eine Resiststruktur gebildet wird, welche entsprechend der Struktur unmaskierte Bereiche frei lässt, wo leitfähige Spuren 256 erwünscht sind. Die leitfähigen Spuren 256 und leitfähigen Durchkontaktierungen 252 werden dann durch elektrolytisches Plattieren z. B. einer Kupferschicht unter Verwendung des stromlosen Kupferplattierungsfilms als Keimschicht gebildet. Die Elektroplattierung wird fortgesetzt, bis die Durchkontaktierungen 252 vollständig gefüllt sind und die ersten leitfähigen Spuren 256 in einer gewünschten Dicke gebildet sind, z. B. 2 bis 20 Mikrometer. Die Photoresistmaske wird anschließend entfernt, und es wird ein Kurzkontakt-Ätzverfahren angewendet, um die verbleibende Keimschicht zu entfernen. Die oben beschriebene SAP-Technik kann angewendet werden, um Durchkontaktierungen zu füllen und leitfähige Spuren bei einer Temperatur von weniger als 100°C und typischerweise von 50°C bis 80°C zu bilden. Die Anwendung eines semiadditiven Ansatzes ermöglicht, dass dünne leitfähige Spuren mit feinen Leitungs- und Zwischenraumelementen gebildet werden, z. B. Leitungs- und Zwischenraumelementen von weniger als 30 Mikrometern. Die Anwendung eines semiadditiven Verfahrens (SAP) zum Füllen der Durchkontaktierungen 252 und zum Bilden der ersten Leitungsschicht 254 ermöglicht, dass das erste Plättchen 222 elektrisch mit dem Substrat der Montageeinheit verbunden wird, ohne ein Hochtemperaturverfahren anzuwenden, z. B. Wärmekompressions-Bonding oder eine Oberflächenbefestigungstechnologie unter Verwendung bleifreier Lötmetalle, welche bei anderen Montagetechnologien, z. B. Flip-Chip-Bonding und Wire-Bonding, typischerweise angewendet werden, um ein Plättchen elektrisch mit Substrat der Montageeinheit zu verbinden. Durch Anwendung eines Niedertemperaturverfahrens, z. B. eines Verfahrens bei weniger als 100°C, um das erste Plättchen 222 elektrisch mit dem Substrat zu verbinden, werden das Substrat und das Plättchen keinen hohen Temperaturen ausgesetzt, welche aufgrund der CTE-Fehlanpassung zwischen dem ersten Plättchen 222 und schichten der Vorrichtung 240 zu einer Verformung der Montageeinheit führen können. Es kann eine ähnliche Verarbeitung angewendet werden, um die leitfähigen Durchkontaktierungen 252' und die Leitungsschicht 254' zu bilden, um die Vorrichtung 250 bereitzustellen, welche in In einer Ausführungsform der vorliegenden Erfindung wird die Rückfläche 266 des zweiten Plättchens 262 unter Nutzung der Klebrigkeit der zweiten isolierenden Schicht 261 an der zweiten isolierenden Schicht 261 befestigt. Zum Beispiel wird in einer Ausführungsform der vorliegenden Erfindung ein isolierender Film wie z. B. ABF über die Leitungsschicht 254 und die erste isolierende Schicht laminiert, der isolierende Film wird dann nur teilweise gehärtet, zum Beispiel bei einer Temperatur von 70°C, um die Klebrigkeit des isolierenden Films zu bewahren. As zweite Plättchen 262 wird dann auf dem teilweise gehärteten isolierenden Film angeordnet, wobei das zweite Plättchen 262 durch die Klebrigkeit des teilweise gehärteten isolierenden Films befestigt wird. Nach dem Befestigen des zweiten Plättchens 262 kann die teilweise gehärtete isolierende Schicht vollständig gehärtet werden, zum Beispiel durch Erwärmen auf eine Temperatur von etwa 180°C, um die zweite isolierende Schicht 261 zu bilden. Auf diese Weise ist kein Klebstoff oder Plättchenbefestigungsfilm notwendig, um das zweite Plättchen 262 an der zweiten isolierenden Schicht 261 zu befestigen. Durch das Weglassen eines Plättchenbefestigungsfilms wird die Stufenhöhe des befestigten zweiten Plättchens verringert, was dazu beiträgt, die Topographie des zweiten Plättchens 262 zu reduzieren, und ermöglicht, dass nachfolgende Aufbauschichten planarer gebildet werden. In einer Ausführungsform ist das zweite Plättchen 262 so angeordnet, dass wenigstens ein Abschnitt der Standfläche 269 des zweiten Plättchens 262 innerhalb der Standfläche 229 des ersten Plättchens 222 liegt. In einer Ausführungsform der vorliegenden Erfindung weist das zweite Plättchen 262 eine Standfläche 269 auf, welche kleiner als die Standfläche 229 des ersten Plättchens 222 ist, und das zweite Plättchen 262 ist auf der isolierenden Schicht 261 angeordnet, so dass die gesamte Standfläche 269 des zweiten Plättchens 262 innerhalb der Standfläche 229 des ersten Plättchens 222 liegt, wie in Als Nächstes wird auf der zweiten isolierenden Schicht 261 und der aktiven Fläche des zweiten Plättchens 262 eine dritte isolierende Schicht 268 gebildet, wie in Außerdem ist die Vorrichtung 270 weiter verarbeitet worden, so dass sie eine zweite Leitungsschicht 286 umfasst, welche mehrere leitfähige Spuren 288 aufweist. Die zweite Leitungsschicht 286 ist auf der dritten isolierenden Schicht 268 angeordnet, wie in In einer Ausführungsform der vorliegenden Erfindung ist das semiadditive Verfahren so ausgestaltet, dass eine leitfähige Schicht gebildet wird, welche dick genug ist, um kleine Durchkontaktierungen 272 vollständig zu füllen, um vollständig gefüllte leitfähige Durchkontaktierungen 282 zu bilden, welche aber nicht dick genug ist, um große Durchkontaktierungsöffnungen 274 vollständig zu füllen. In einem solchen Fall bildet sich der plattierte Film formangepasst auf den Seitenwänden der Durchkontaktierung 274, wodurch eine „becherförmige” leitfähige Durchkontaktierung 284 mit einem ungefüllten Mittelteil 285 gebildet wird. Durch die Anwendung eines semiadditiven Verfahrens wird ermöglicht, dass das zweite Plättchen 262 elektrisch mit Leitungsschichten des Substrats verbunden wird, ohne Hochtemperatur-Lötverbindungsverfahren anzuwenden, die normalerweise angewendet werden, um ein Plättchen elektrisch mit einem Substrat einer Montageeinheit zu verbinden. Die leitfähigen Durchkontaktierungen 282' und 284' und zweite Leitungsschichten 286 können in ähnlicher Weise gebildet werden, um die Vorrichtung 280 herzustellen, die in Wenn jedoch weitere Leitungsfunktionalitäten benötigt werden, können eine oder mehrere weitere Leitungsschichten und isolierende Schichten zusammen mit Zwischenverbindungs-Durchkontaktierungen gebildet werden, wie oben beschrieben. Zum Beispiel kann die Vorrichtung 290 der Obwohl die vorliegende Erfindung in Bezug auf eine Multichip-Montageeinheit beschrieben worden ist, welche ein Substrat 102 mit zwei eingebetteten Plättchen aufweist, kann das Substrat auch drei oder mehr eingebettete Plättchen umfassen, falls erwünscht. Zum Beispiel kann in einer Ausführungsform der vorliegenden Erfindung eine Multichip-Montageeinheit 450 gebildet werden, welche ein Substrat 460 mit drei eingebetteten Plättchen aufweist, indem ein drittes Plättchen 470 in einer weiteren einbettenden isolierenden Schicht 480 eingebettet wird, welche über der ersten isolierenden Schicht 130 gebildet wird, wie in Außerdem kann in einer anderen Ausführungsform der vorliegenden Erfindung eine Multichip-Montageeinheit 500 gebildet werden, welche ein Substrat 502 mit einem dritten eingebetteten Plättchen aufweist, indem ein drittes Plättchen 560 benachbart zu dem ersten Plättchen 104 im Substrat 102 angeordnet wird, wie in Die Multichip-Montageeinheiten 450 und 500 können auf eine Weise hergestellt werden, wie sie in Bezug auf Eine oder mehrere der im System 300 dargestellten Komponenten können in einer oder mehreren IC-Montageeinheiten, wie zum Beispiel der Montageeinheitsstruktur 100 der Diese Elemente erfüllen ihre herkömmlichen Funktionen, die auf dem Fachgebiet wohlbekannt sind. Insbesondere kann die Speichereinheit 320 in einigen Fällen verwendet werden, um eine Langzeitspeicherung für die ausführbaren Befehle für ein Verfahren zum Bilden montierter Strukturen gemäß Ausführungsformen der vorliegenden Erfindung bereitzustellen, und kann in anderen Ausführungsformen verwendet werden, um die ausführbaren Befehle eines Verfahrens zum Bilden von Montageeinheitsstrukturen gemäß Ausführungsformen der vorliegenden Erfindung während der Ausführung durch den Prozessor 310 auf einer kürzeren Zeitbasis zu speichern. Außerdem können die Befehle mit maschinenzugänglichen Medien, die mit dem System kommunikativ verbunden sind, zum Beispiel Compact-Disc-Nur-Lese-Speichern (Compact Disc Read Only Memories, CD-ROMs), Digital Versatile Discs (DVDs) und Floppy-Discs, Trägerwellen und/oder sich ausbreitenden Signalen, gespeichert oder auf andere Weise verbunden werden. In einer Ausführungsform kann die Speichereinheit 320 dem Prozessor 310 die ausführbaren Befehle zur Ausführung zuführen. Das System 300 kann Computer (z. B. Tischcomputer, Laptops, Handcomputer, Server, Web-Geräte, Router usw.), drahtlose Kommunikationseinheiten (z. B. Mobiltelefone, schnurlose Telefone, Pager, persönliche digitale Assistenten usw.), computerbezogene Peripheriegeräte (z. B. Drucker, Scanner, Monitore), Unterhaltungseinheiten (z. B. Fernsehgeräte, Radios, Stereoanlagen, Cassetten- und Compact-Disc-Abspielgeräte, Videorecorder, Camcorder, Digitalkameras, MP3(Motion Picture Experts Group, Audio Layer 3)-Player, Videospiele, Armbanduhren usw.) und Ähnliches umfassen. Somit sind eine Multichip-Montageeinheit, welche ein Substrat mit mehreren vertikal angeordneten darin eingebetteten Plättchen aufweist, und ihr Herstellungsverfahren beschrieben worden. Eine Vorrichtung umfasst ein Substrat, welches eine Anschlussfleckseite mit mehreren Kontaktflecken und eine Plättchenseite gegenüber der Anschlussfleckseite aufweist. Die Vorrichtung umfasst ein erstes Plättchen und ein zweites Plättchen, wobei das erste Plättchen und das zweite Plättchen derart in das Substrat eingebettet sind, dass das zweite Plättchen zwischen dem ersten Plättchen und der Anschlussfleckseite des Substrats angeordnet ist. Vorrichtung, welche das Folgende aufweist: Vorrichtung nach Anspruch 1, wobei das erste Plättchen eine erste Standfläche aufweist und wobei das zweite Plättchen eine zweite Standfläche aufweist und wobei zumindest ein Teil der ersten Standfläche des ersten Plättchens innerhalb der zweiten Standfläche des zweiten Plättchens angeordnet ist. Vorrichtung nach Anspruch 1, wobei die erste Standfläche größer als die zweite Standfläche ist. Vorrichtung nach Anspruch 3, wobei die Standfläche des zweiten Plättchens vollständig innerhalb der ersten Standfläche des ersten Plättchens angeordnet ist. Vorrichtung nach Anspruch 1, wobei die aktive Fläche des ersten Plättchens und die aktive Fläche des zweiten Plättchens der Anschlussfleckseite des Substrats zugewandt sind. Vorrichtung nach Anspruch 1, wobei das erste Plättchen durch eine elektrische Verbindung mit dem zweiten Plättchen verbunden ist, welche vollständig in das Substrat eingebettet ist. Vorrichtung nach Anspruch 6, wobei die elektrische Verbindung zwischen dem ersten Plättchen und dem zweiten Plättchen keine vertikale Verbindung umfasst, welche einen Durchmesser von mehr als 150 Mikrometern aufweist. Vorrichtung nach Anspruch 2, wobei das erste Plättchen durch eine elektrische Verbindung, die in das Substrat eingebettet ist, mit einem der Anschlussflecken verbunden ist. Vorrichtung nach Anspruch 2, welche eine Leitungsschicht umfasst, die zwischen dem ersten Plättchen und dem zweiten Plättchen in das Substrat eingebettet ist. Vorrichtung nach Anspruch 1, wobei das erste Plättchen in eine erste isolierende Schicht des Substrats eingebettet ist und das zweite Plättchen in eine zweite isolierende Schicht des Substrats eingebettet ist. Vorrichtung nach Anspruch 10, welche ferner das Folgende umfasst: Vorrichtung nach Anspruch 11, welche ferner eine vierte isolierende Schicht zwischen dem zweiten Plättchen und den mehreren Kontaktflecken umfasst, wobei die vierte isolierende Schicht eine zweite Leitungsschicht aufweist, welche mehrere darin eingebettete zweite Spuren umfasst. Vorrichtung nach Anspruch 12, welche ferner mehrere erste Durchkontaktierungen mit einem ersten Durchmesser in dem vierten Dielektrikum zwischen der zweiten Leitungsschicht und dem zweiten Plättchen umfasst; und mehrere zweite Durchkontaktierungen mit einem zweiten Durchmesser in der dritten Dielektrikumsschicht und der zweiten Dielektrikumsschicht und zwischen der ersten Leitungsschicht und der zweiten Leitungsschicht umfasst, wobei der zweite Durchmesser größer als der erste Durchmesser ist. Verfahren zum Bilden einer Multichip-Montageeinheit, welches das Folgende umfasst: Verfahren nach Anspruch 14, welches ferner das Bilden einer Leitungsschicht zwischen dem ersten Plättchen und dem zweiten Plättchen umfasst. Verfahren nach Anspruch 14, welches ferner das Bilden einer dritten isolierenden Schicht zwischen der ersten isolierenden Schicht und der zweiten isolierenden Schicht und das Befestigen des zweiten Plättchens an der dritten isolierenden Schicht umfasst. Verfahren nach Anspruch 16, welches ferner das Folgende umfasst: Verfahren nach Anspruch 17, welches ferner das Bilden einer ersten Leitungsschicht zwischen der ersten isolierenden Schicht und der dritten isolierenden Schicht umfasst, wobei die dritte Leitungsschicht eine erste Spur aufweist, die mit dem ersten Plättchen in elektrischem Kontakt steht. Verfahren nach Anspruch 18, welches ferner das Bilden einer zweiten Leitungsschicht auf der zweiten isolierenden Schicht umfasst, wobei die zweite isolierende Schicht eine zweite Spur aufweist, welche mit dem zweiten Plättchen und der ersten Spur in elektrischem Kontakt steht. Multichip-Montageeinheit, welche das Folgende umfasst: ALLGEMEINER STAND DER TECHNIK

1. GEBIET DER ERFINDUNG

2. BESCHREIBUNG DES STANDES DER TECHNIK

KURZBESCHREIBUNG DER ZEICHNUNGEN

DETAILLIERTE BESCHREIBUNG

ein Substrat, welches eine Plättchenseite und eine Anschlussfleckseite gegenüber der Plättchenseite aufweist, wobei die Anschlussfleckseite mehrere Kontaktflecken aufweist;

ein erstes Plättchen, welches eine erste aktive Fläche und eine Rückfläche gegenüber der aktiven Fläche aufweist;

ein zweites Plättchen, welches eine aktive Fläche und eine Rückfläche gegenüber der aktiven Fläche aufweist; und

wobei das erste Plättchen und das zweite Plättchen derart in das Substrat eingebettet sind, dass das zweite Plättchen zwischen dem ersten Plättchen und der Anschlussfleckseite des Substrats angeordnet ist.

eine dritte isolierende Schicht, welche zwischen der ersten isolierenden Schicht und der zweiten isolierenden Schicht angeordnet ist; und

eine erste Leitungsschicht, welche mehrere erste Spuren umfasst, welche in die dritte isolierende Schicht eingebettet sind, und wobei eine der ersten Spuren der ersten Zwischenverbindungsschicht zwischen dem ersten Plättchen und dem zweiten Plättchen ausgebildet ist.

Befestigen eines ersten Plättchens an einem Träger;

Bilden einer ersten isolierenden Schicht über dem ersten Plättchen und dem Träger, so dass das erste Plättchen in die erste isolierende Schicht eingebettet ist;

Anordnen eines zweiten Plättchens über der ersten isolierenden Schicht; und

Bilden einer zweiten isolierenden Schicht über dem zweiten Plättchen, so dass das zweite Plättchen in die zweite isolierende Schicht eingebettet ist.

Teilhärten der dritten isolierenden Schicht nach dem Bilden der dritten isolierenden Schicht und vor dem Befestigen des ersten Plättchens, um eine teilweise gehärtete dritte isolierende Schicht zu bilden;

Befestigen des zweiten Plättchens an der teilweise gehärteten dritten isolierenden Schicht; und

vollständiges Härten der teilweise gehärteten dritten isolierenden Schicht nach dem Befestigen des zweiten Plättchens.

ein erstes Plättchen, welches eine aktive Fläche gegenüber einer Rückfläche aufweist;

eine erste isolierende Schicht, wobei das erste Plättchen in die erste isolierende Schicht eingebettet ist;

eine erste Durchkontaktierung in der ersten isolierenden Schicht und in elektrischem Kontakt mit der aktiven Fläche des ersten Plättchens;

eine erste Leitungsschicht, welche eine erste leitfähige Spur aufweist, auf der ersten isolierenden Schicht, wobei die erste leitfähige Spur mit der ersten Durchkontaktierung in Kontakt steht;

eine zweite isolierende Schicht auf der ersten Leitungsschicht und der ersten isolierenden Schicht;

ein zweites Plättchen, welches eine aktive Fläche gegenüber einer Rückfläche aufweist, wobei sich die Rückfläche des zweiten Plättchens auf der zweiten isolierenden Schicht befindet;

eine dritte isolierende Schicht auf der aktiven Fläche des zweiten Plättchens und der zweiten isolierenden Schicht;

eine dritte leitfähige Durchkontaktierung in der isolierenden Schicht und in Kontakt mit der aktiven Fläche des zweiten Plättchens;

eine vierte leitfähige Durchkontaktierung in der dritten isolierenden Schicht und der zweiten isolierenden Schicht und in Kontakt mit der ersten leitfähigen Spur der ersten Leitungsschicht;

eine zweite Leitungsschicht, welche eine zweite leitfähige Spur aufweist, auf der dritten isolierenden Schicht, wobei die zweite leitfähige Spur mit der zweiten leitfähigen Durchkontaktierung und der dritten leitfähigen Durchkontaktierung in Kontakt steht; und

eine vierte isolierende Schicht auf der dritten isolierenden Schicht und der zweiten Leitungsschicht.