Semiconductor package for e.g. integrated circuit card in e.g. mobile phone, has external contact terminal provided within through-hole, which electrically connects conductive pattern to semiconductor chip

Die

Erfindung bezieht sich auf eine Halbleiterpackung, auf ein elektronisches

System, wie eine integrierte Schaltkreis(IC)-Karte, in die eine

derartige Halbleiterpackung eingebaut ist, sowie auf ein Verfahren

zur Herstellung einer derartigen Halbleiterpackung und auf ein Verfahren

zur Herstellung eines derartigen elektronischen Systems. Typischerweise

wird eine Halbleiterpackung vom Chip-auf-Board(COB)-Typ zur Herstellung

von IC-Karten verwendet, z. B. Smardcards. Die IC-Karten werden heutzutage üblicherweise

in verschiedenen Anwendungen verwendet, die Magnetkarten ersetzen.

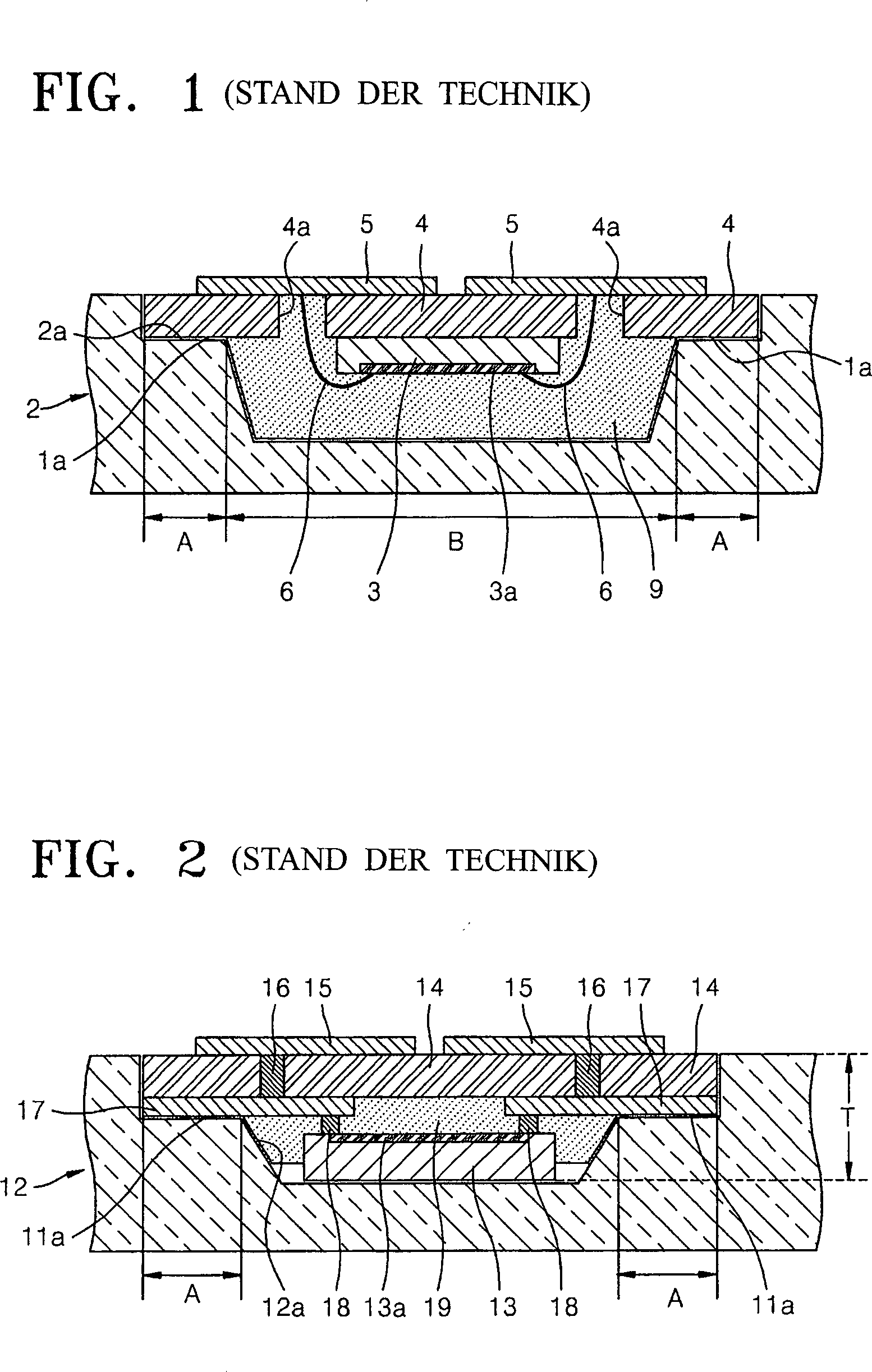

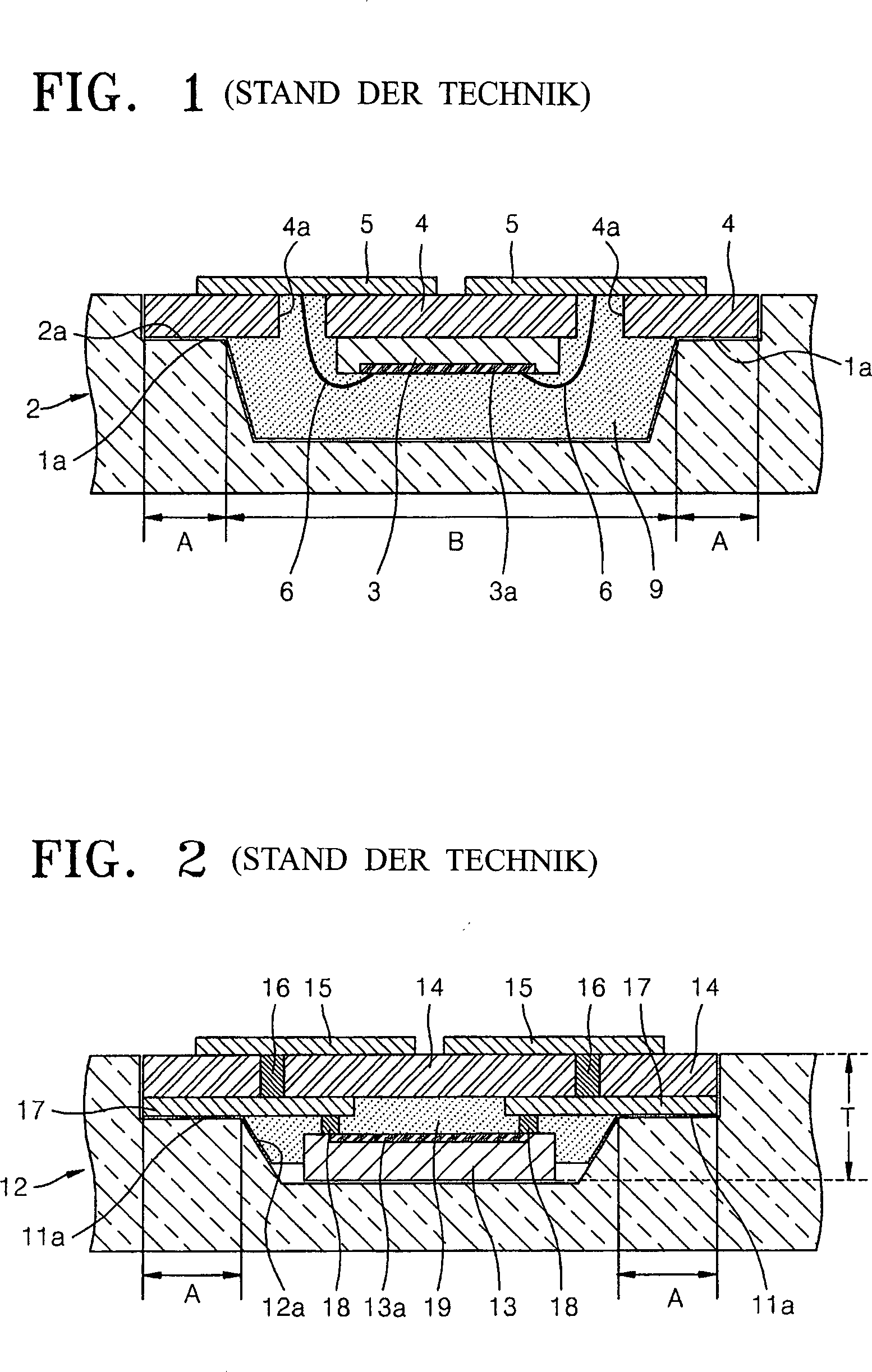

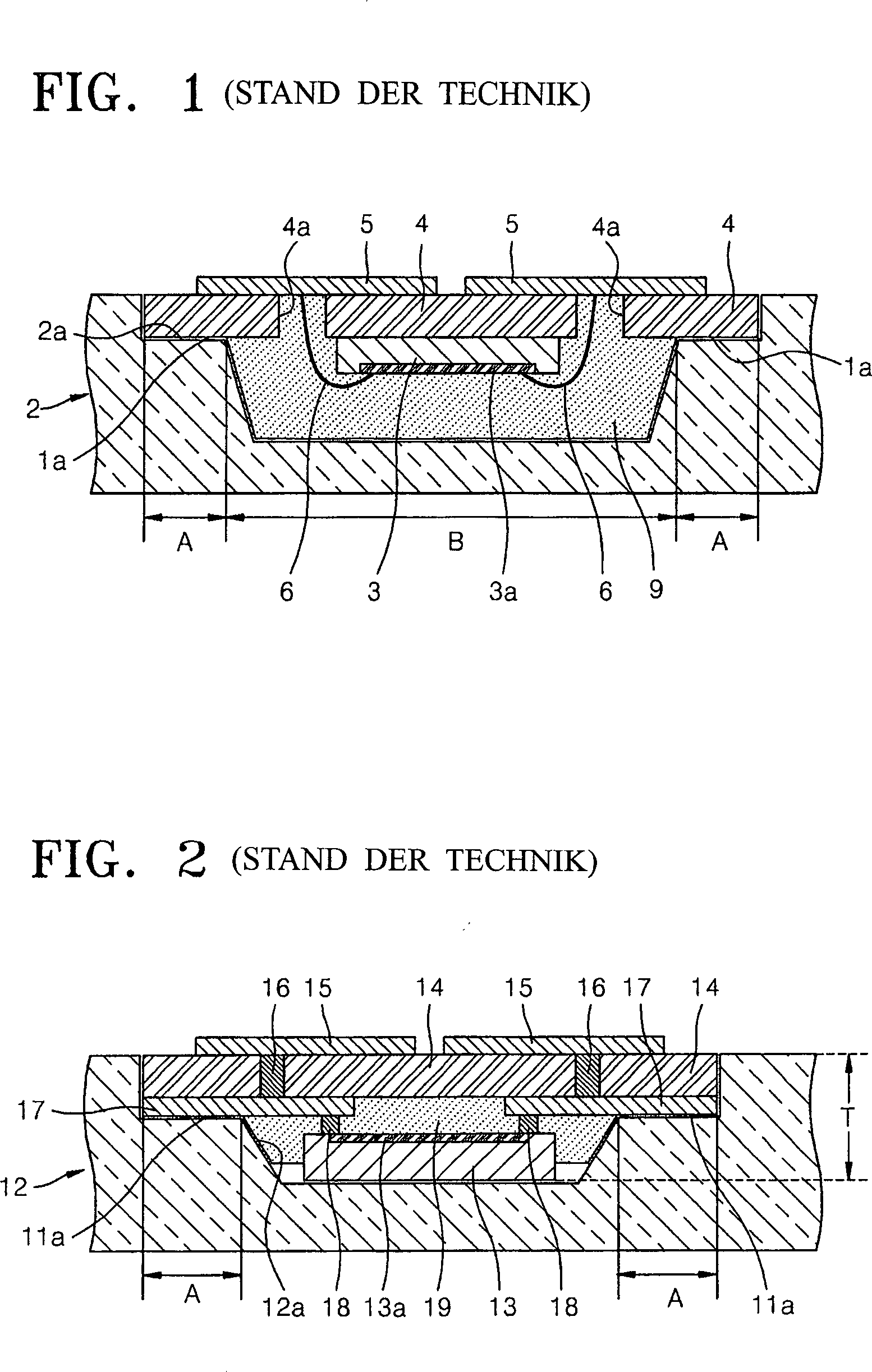

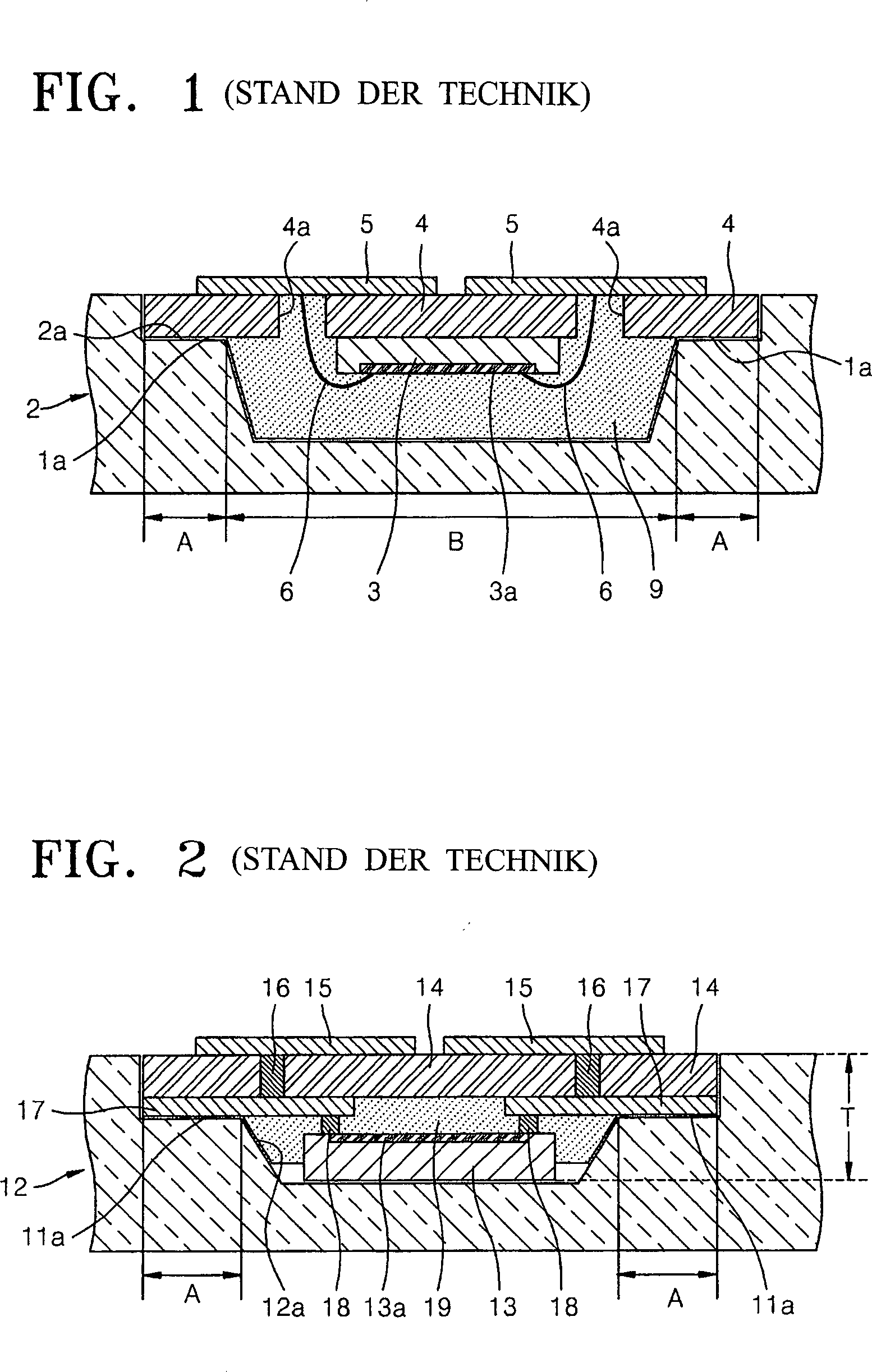

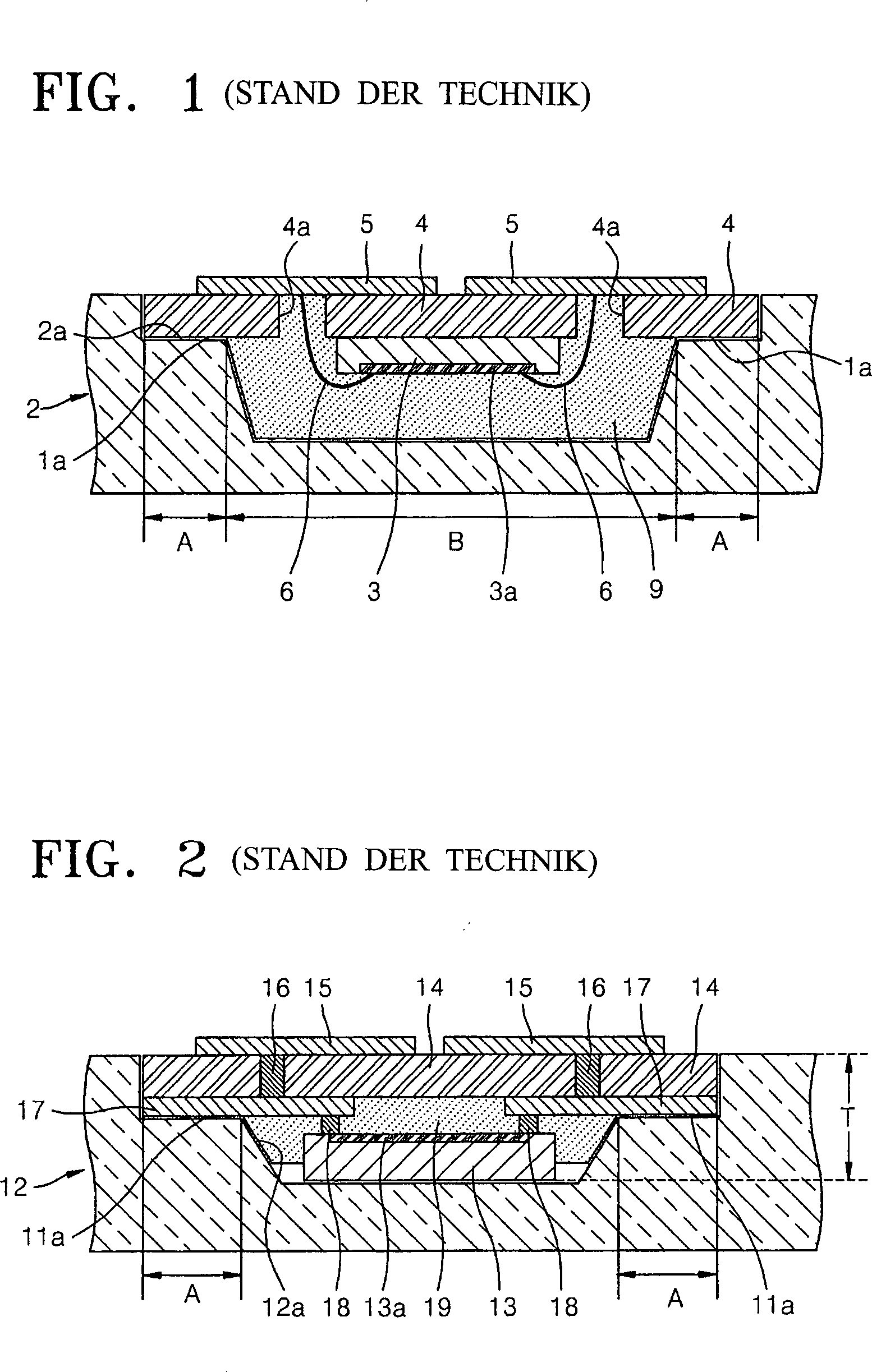

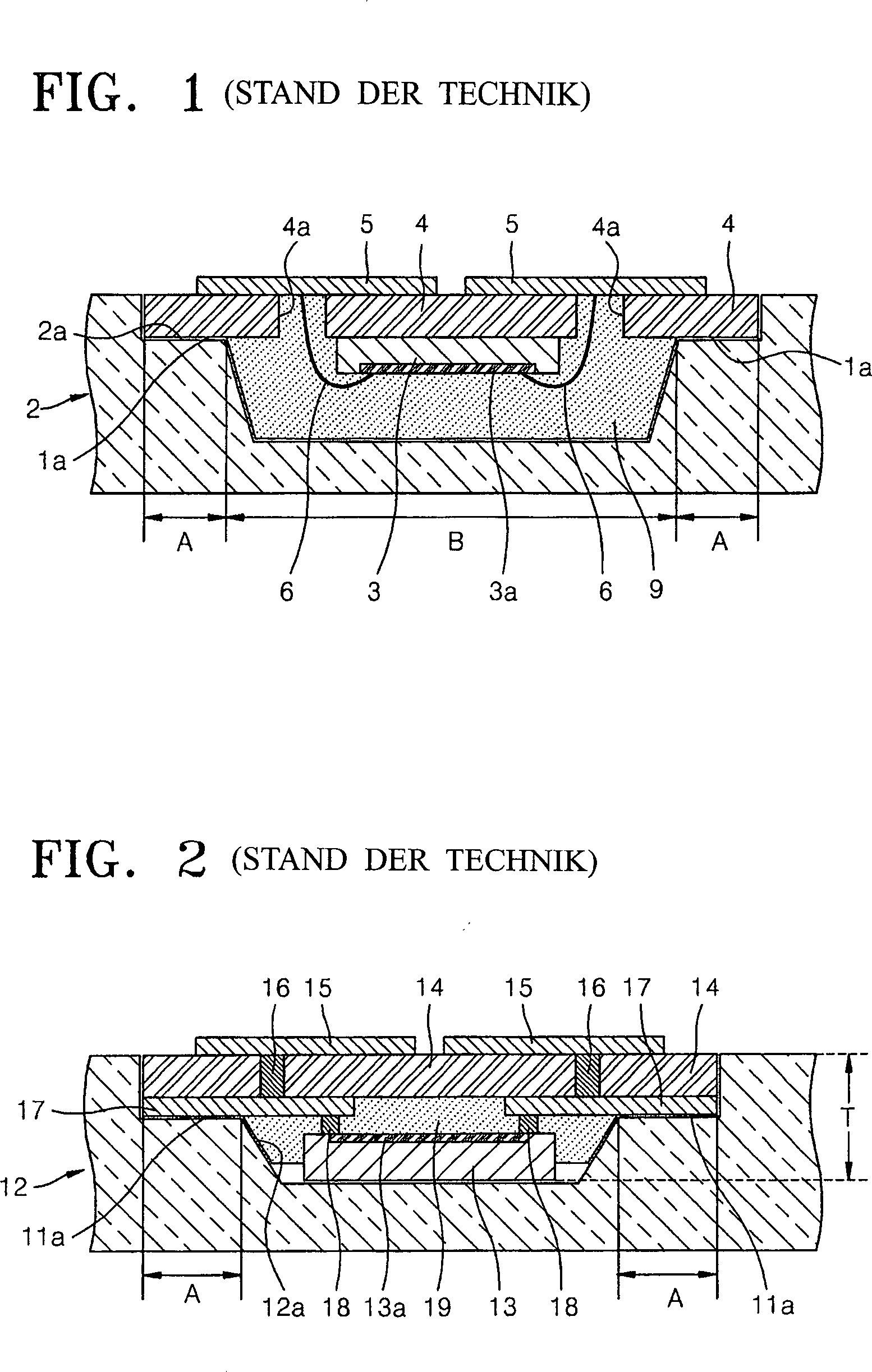

Bezugnehmend auf Die

Bonddrähte 6 ragen

unvermeidbar von der aktiven Oberfläche 3a des Halbleiterchips 3 bis zu

einer gewissen Höhe

vor, wodurch eine Schleife gebildet wird, in der sich die Drähte 6 von

der aktiven Oberfläche 3a weg

erstrecken und sich dann zu der Metallschicht 5 hin biegen.

Außerdem

ist ein Verkapselungsmittel 9 bereitgestellt, um die Drähte 6 einzukapseln.

Es muss daher eine ausreichende Menge an Einkapselungsmittel 9 bereitgestellt

sein, um die Drähte 6 vor

der äußeren Umgebung

zu schützen. Demgemäß erzeugt

das Verkapselungsmittel 9 einen relativ großen Gießbereich "B", wobei ein relativ kleiner Bondbereich "A" verbleibt, in dem die Oberfläche 1a der

Halbleiterpackung und eine gegenüberliegende

Oberfläche

des Kartenkörpers 2 aneinander

gebondet werden können.

Da des Weiteren die Bonddrähte 6 auf

beiden Seiten des Halbleiterchips 3 ausgebildet sein müssen, ist

die Länge

des Gießbereichs "B" zusätzlich

vergrößert, und

die Länge

des Bondbereichs A ist weiter reduziert, während die Gesamtlänge des

zur Verfügung

stehenden Packungssystems begrenzt ist. Es

wurde außerdem

festgestellt, dass Kanten des Substrats 4 dazu tendieren,

während

der Herstellung der Halbleiterpackung vom COB-Typ zu deformieren.

Da der Bondbereich "A" bei dem herkömmlichen

System relativ klein ist, tendiert somit das Substrat 4 dazu,

sich von dem Kartenkörper 2 zu separieren,

und die resultierende IC-Karte kann leicht geschädigt werden oder brechen. Diese

Probleme können

ernsthafter werden, wenn die Abmessung des Halbleiterchips 3 zunimmt

und das Packungssystem oder die IC-Karte einer raueren Umgebung

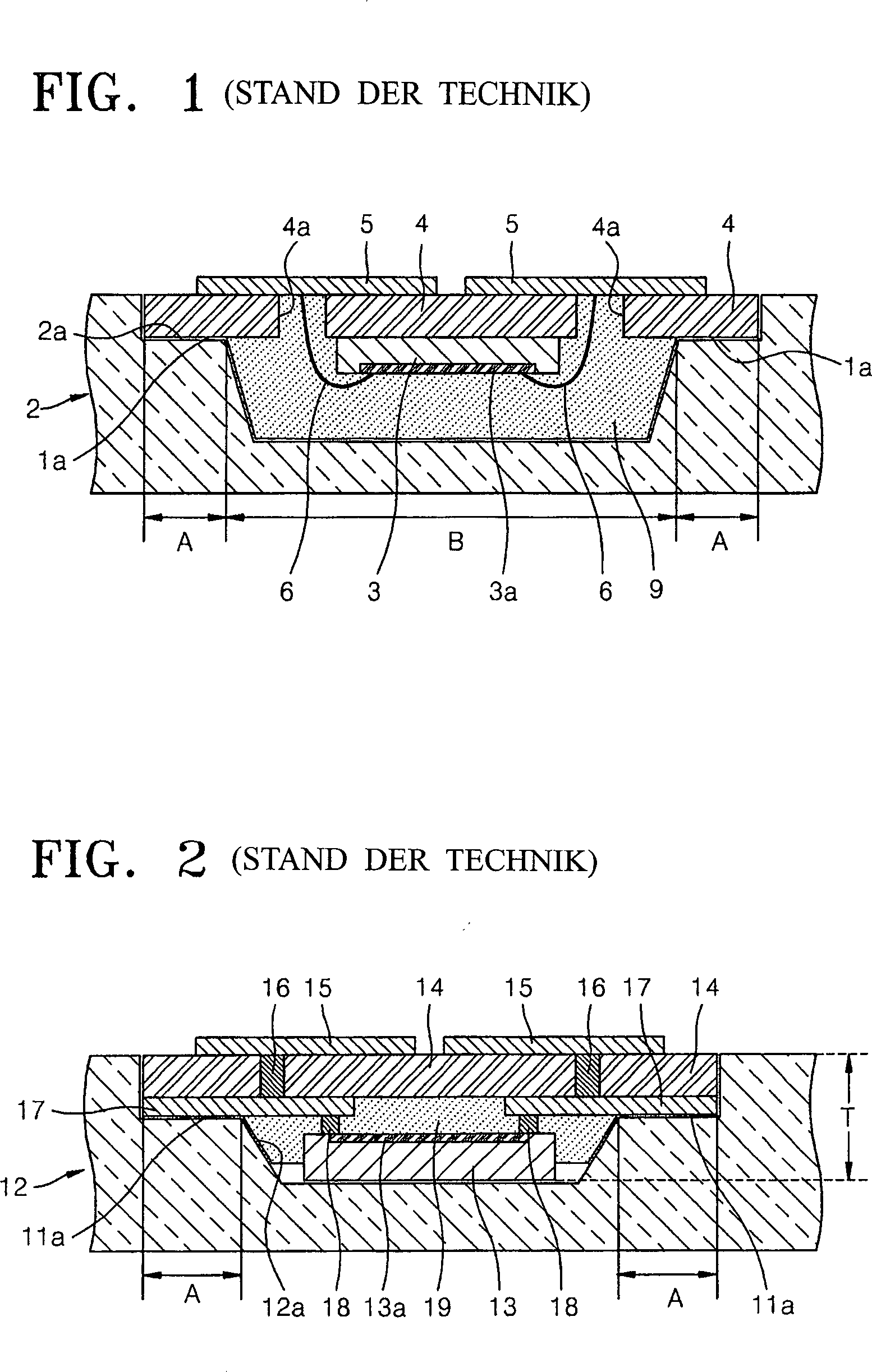

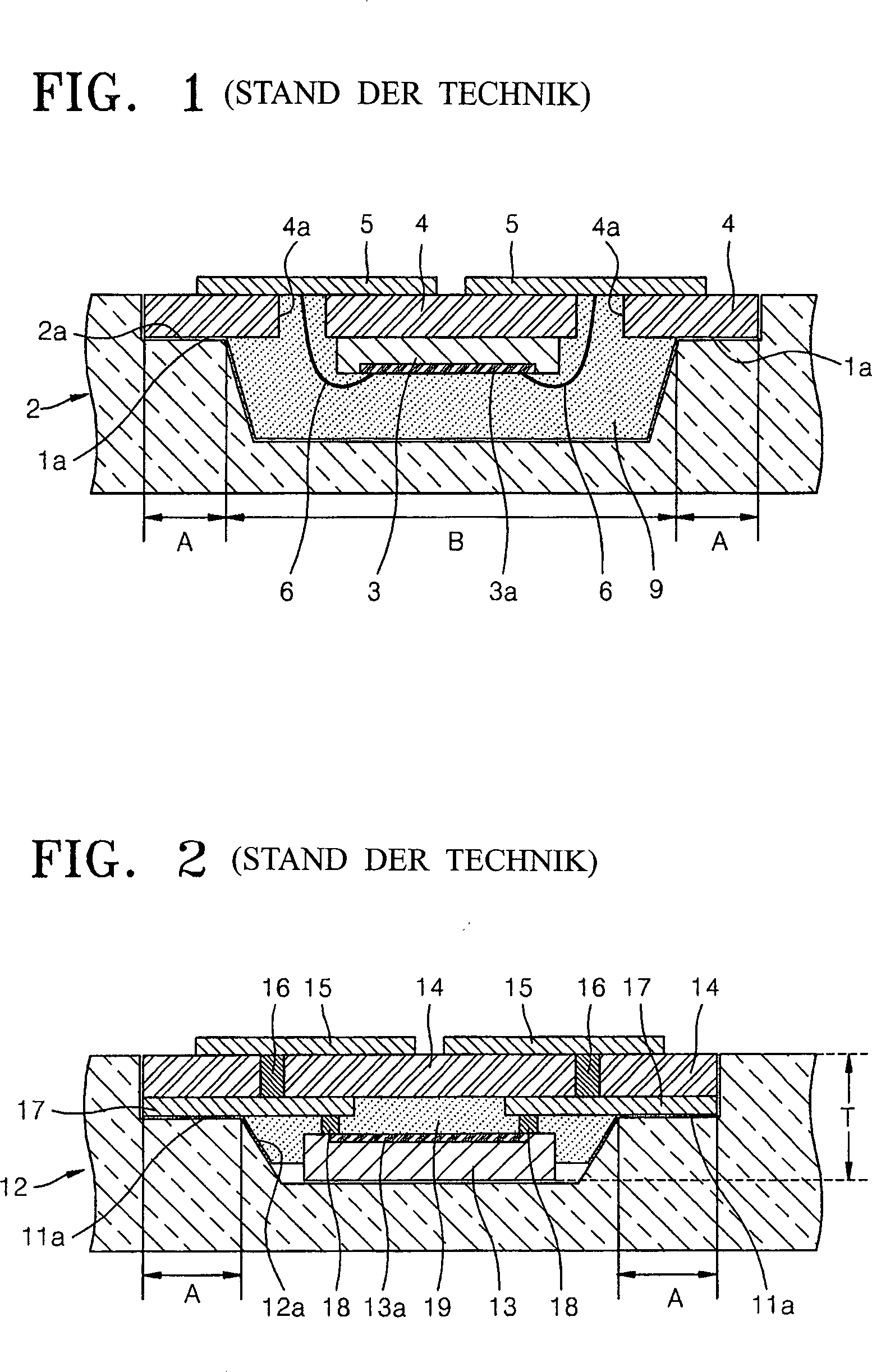

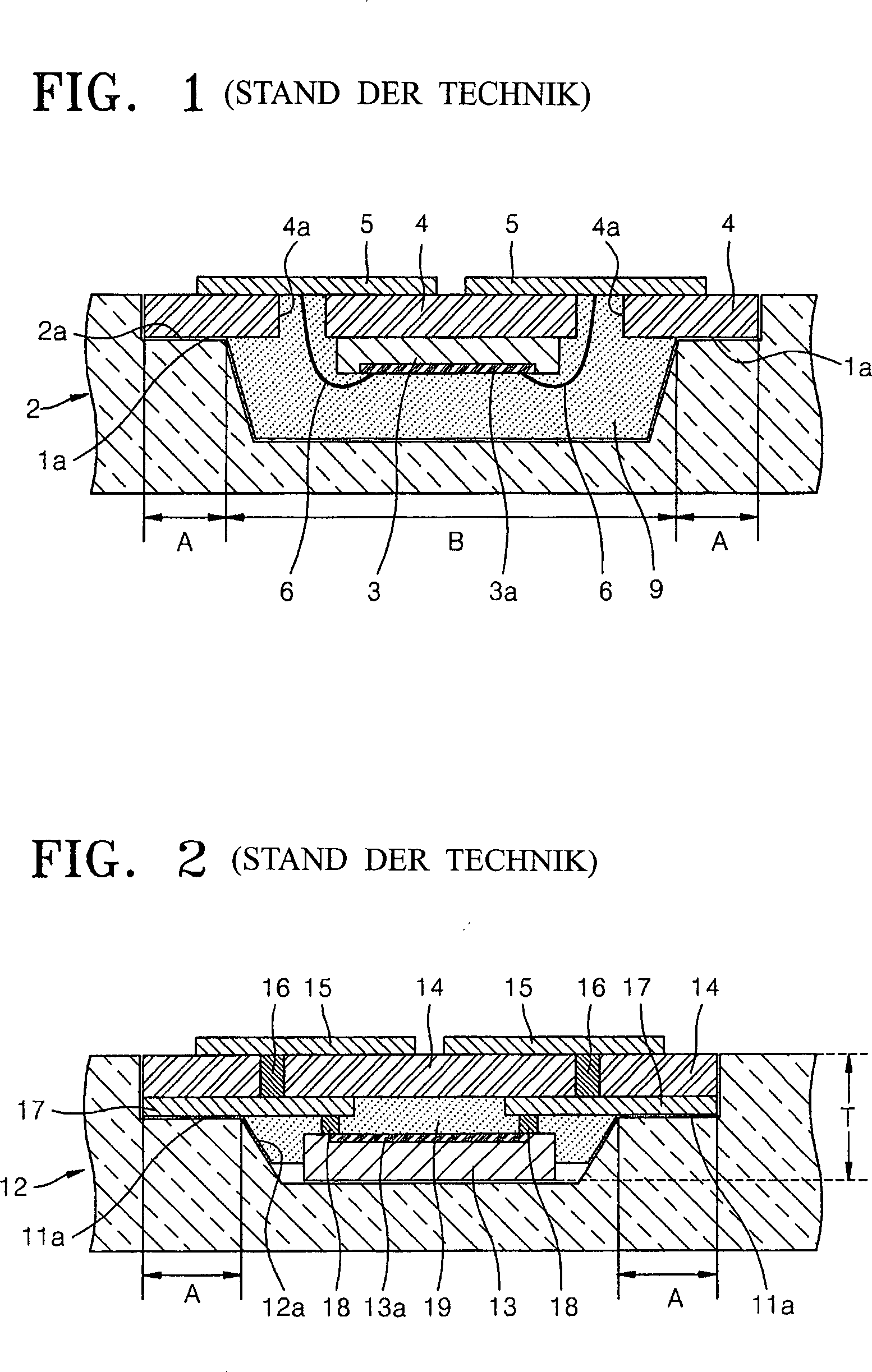

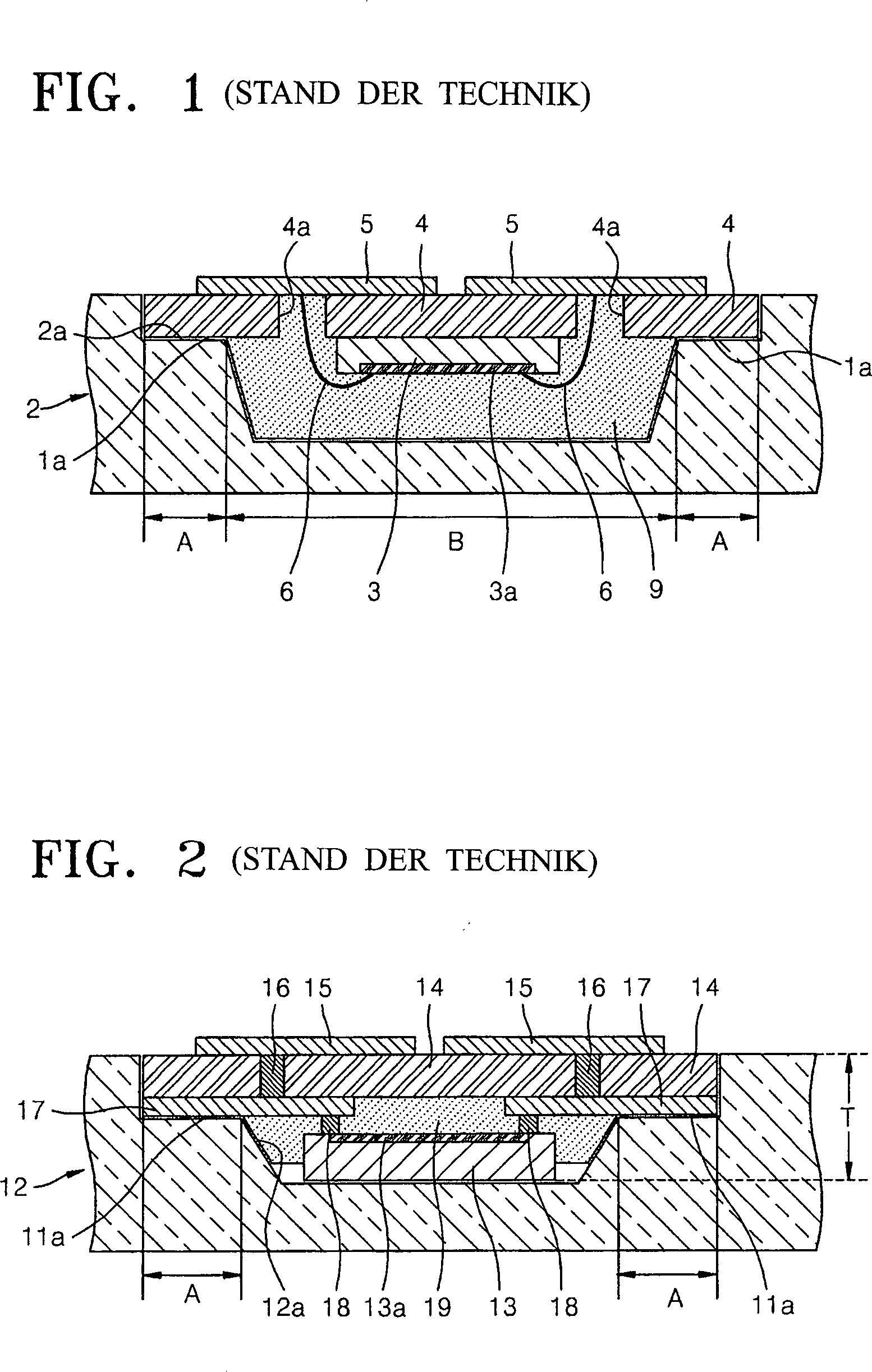

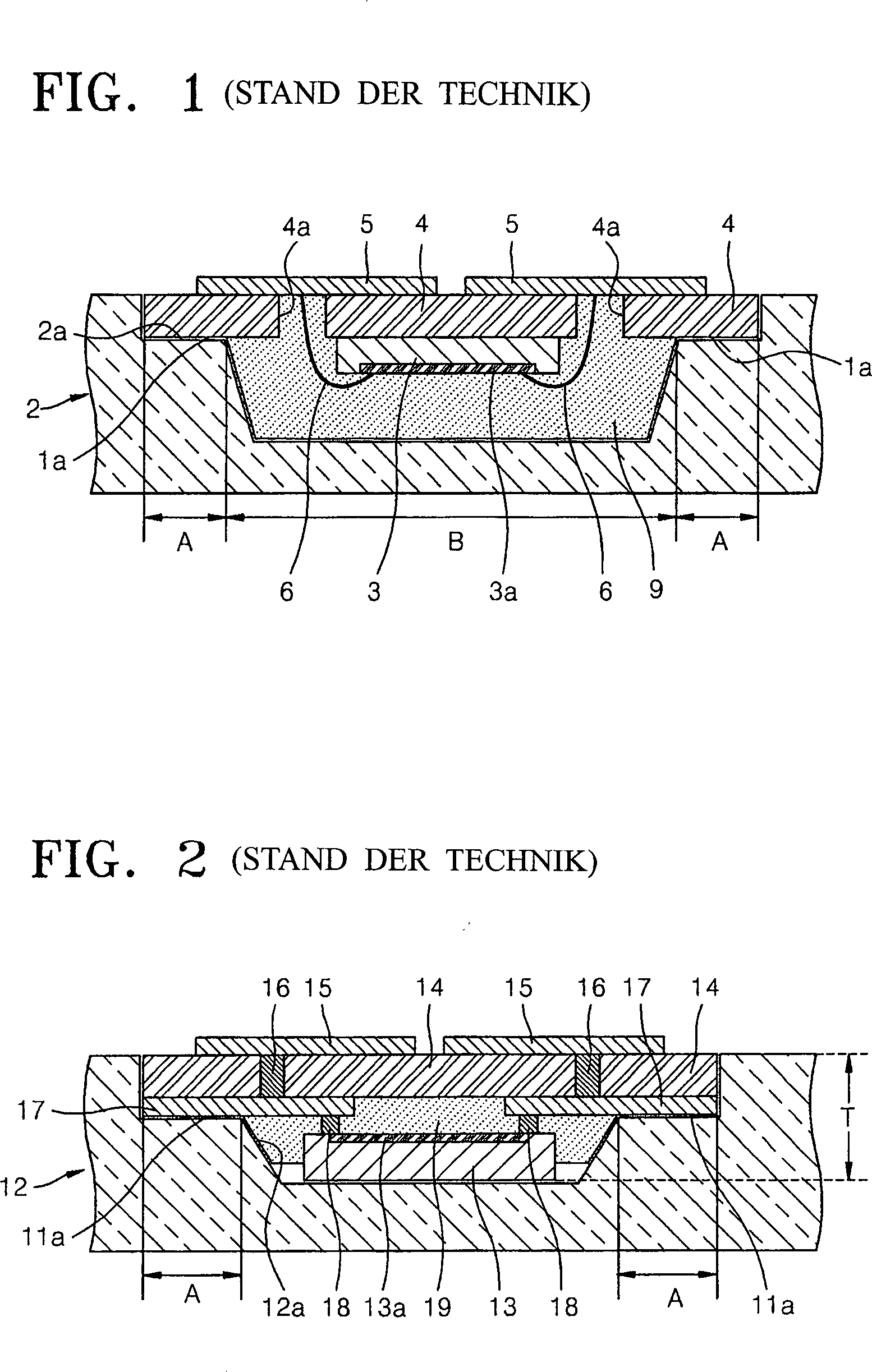

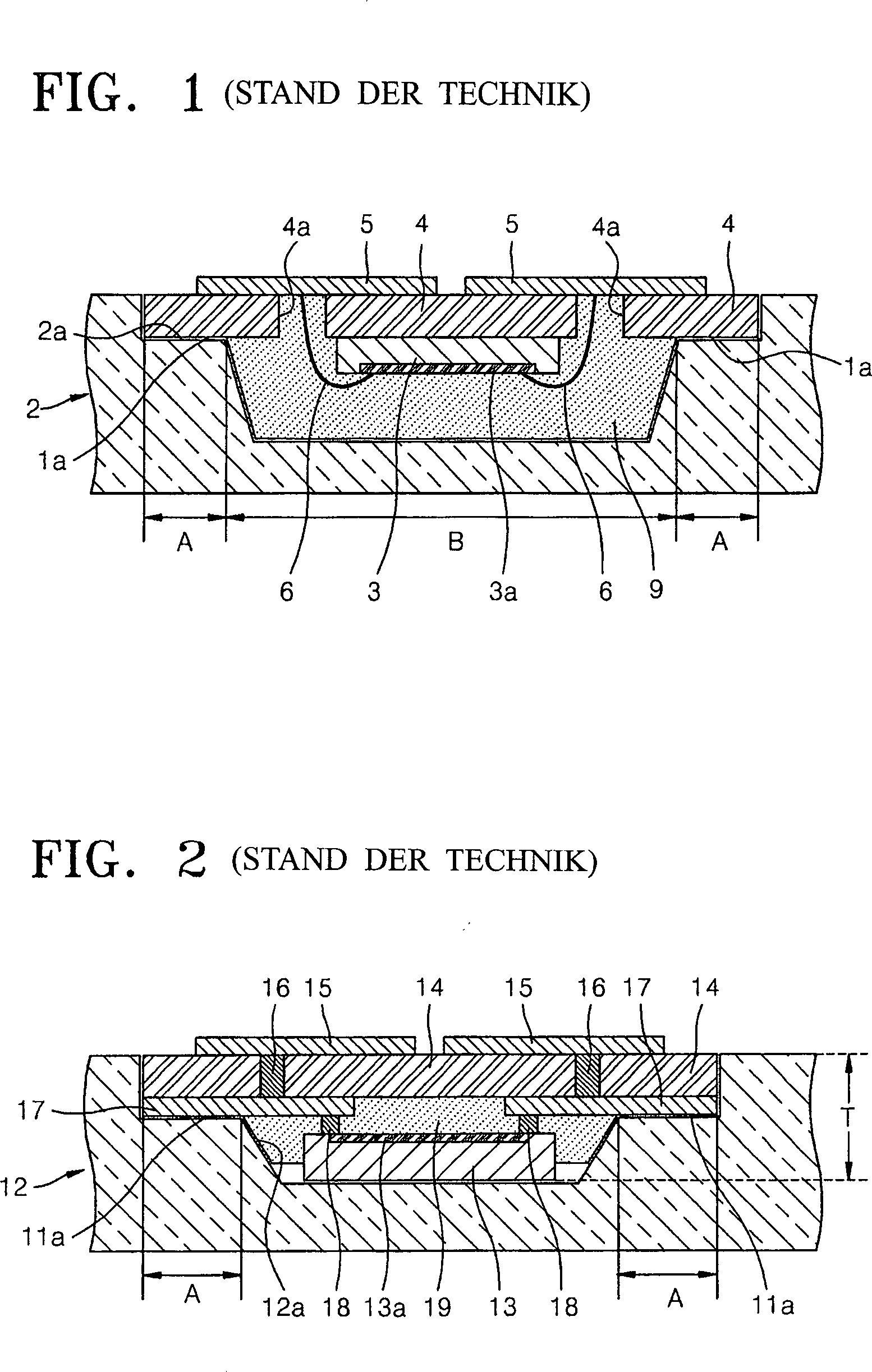

unterworfen ist. Die

leitfähigen

Kontakthügel 18 stehen

von der Oberfläche

des Halbleiterchips 13 von einer Unterseite des Hohlraums 12a vor,

und ein Verkapselungsmittel 19 ist bereitgestellt, um die

leitfähigen Kontakthügel 18 zu

verkapseln. Es muss jedoch auch eine ausreichende Menge des Verkapselungsmittels 19 bereitgestellt

werden, um den Halbleiterchip 13 adäquat an den Zwischenmetallschichten 17 und dem

Substrat 14 festzulegen. Demgemäß nimmt

das Verkapselungsmittel 19 einen relativ großen Gießbereich "B" ein, wobei ein relativ kleiner Bondbereich "A" verbleibt, an dem ein Klebstoff zwischen

der Oberfläche 11a der

Halbleiterpackung und einer gegenüberliegenden Oberfläche des

Kartenkörpers 12 angebracht

werden kann. Das Substrat 14 oder die Halbleiterpackung tendieren

auch dazu, sich von dem Kartenkörper 12

zu

separieren, wie bei der in Der

Erfindung liegt als technisches Problem die Bereitstellung einer

Halbleiterpackung, eines damit ausgerüsteten elektronischen Systems

sowie von Verfahren zur Herstellung derselben zugrunde, die in der

Lage sind, die oben erwähnten

Schwierigkeiten des Standes der Technik zu reduzieren oder zu vermeiden,

und die insbesondere erlauben, eine hohe Haltbarkeit und Zuverlässigkeit

und/oder eine reduzierte Gesamtdicke der Halbleiterpackung und des elektronischen

Systems zu erzielen. Die

Erfindung löst

dieses Problem durch die Bereitstellung einer Halbleiterpackung

mit den Merkmalen des Anspruchs 1, eines Verfahrens zur Herstellung

einer Halbleiterpackung mit den Merkmalen des Anspruchs 23,

eines Verfahrens zur Herstellung eines elektronischen Systems mit

den Merkmalen des Anspruchs 30 und eines elektronischen Systems mit

den Merkmalen des Anspruchs 32. Vorteilhafte Weiterbildungen der

Erfindung sind in den Unteransprüchen

angegeben. Vorteilhafte

Ausführungsformen

der Erfindung werden im Folgenden beschrieben und sind in den Zeichnungen

gezeigt, die außerdem

die vorstehend zum leichteren Verständnis der Erfindung erläuterten

herkömmlichen

Ausführungsformen

zeigen. In den Zeichnungen sind: Nunmehr

werden exemplarische Ausführungsformen

der vorliegenden Erfindung im Folgenden unter Bezugnahme auf die

entsprechenden Die Der

Kartenkörper 26 beinhaltet

eine darin definierte Vertiefung 26a. Die Vertiefung 26a ist

im Allgemeinen zum Aufnehmen der Halbleiterpackung 20

konfiguriert.

In einer Ausführungsform

kann die Vertiefung 26a zum Beispiel einen Chip-Aufnahmeteil 223,

der zum Aufnehmen eines ersten Halbleiterchips 22 konfiguriert

ist, und einen Substrataufnahmeteil 222 beinhalten, der

zum Aufnehmen eines Substrats 23 konfiguriert ist. Die

Halbleiterpackung 20 beinhaltet zum Beispiel den ersten

Halbleiterchip 22, eine Mehrzahl von ersten externen Kontaktanschlüssen 21 auf

dem ersten Halbleiterchip 22, das Packungssubstrat 23 und

eine Mehrzahl von auf dem Packungssubstrat 23 angeordneten

leitfähigen

Strukturen 24. Die Halbleiterpackung 20 weist

eine Haftoberfläche 20a auf,

um an eine gegenüberliegende

Oberfläche

des Kartenkörpers 26 gebondet

zu werden, wobei bekannte Techniken verwendet werden, wie die Verwendung eines

Klebstoffs. Die leitfähigen

Strukturen 24 können

unter Verwendung einer herkömmlichen

Technik gebildet werden, z. B. Bilden einer leitfähigen Schicht auf

dem Substrat 23 und Durchführen einer Photolithographie

zur Bildung einer leitfähigen

Struktur. Das

Packungssubstrat 23 beinhaltet eine Oberseite 23b,

eine Unterseite 24c und eine erste Durchgangsöffnung 23a,

die sich von der Oberseite 24b zu der Unterseite 24c erstreckt.

Die Mehrzahl von leitfähigen

Strukturen 24 kann zum Beispiel auf der Oberseite 23b des

Substrats 23 bereitgestellt sein und kann sich über die

erste Durchgangsöffnung 23a erstrecken.

Außerdem

kann der erste Halbleiterchip 22 der Mehrzahl von leitfähigen Strukturen 24 zugewandt

sein, und wenigstens ein Teil des ersten Halbleiterchips 22 kann

in der ersten Durchgangsöffnung 23a angeordnet

sein (z. B. wie exemplarisch in Des

Weiteren verbindet die Mehrzahl von ersten externen Kontaktanschlüssen 21 die

Mehrzahl von leitfähigen

Strukturen 24 elektrisch mit dem ersten Halbleiterchip 22.

Die ersten externen Kontaktanschlüsse 21 kontaktieren

die Mehrzahl von leitfähigen

Strukturen 24 innerhalb der ersten Durchgangsöffnung 23a.

Da die ersten externen Kontaktanschlüsse 21 direkt die

Mehrzahl von leitfähigen

Strukturen kontaktieren können,

ist die in Da

wenigstens ein Teil des ersten Halbleiterchips 22 innerhalb

der ersten Durchgangsöffnung 23a angeordnet

ist, kann die Gesamtdicke "t" der Halbleiterpackung

im Vergleich mit den vorstehend erläuterten herkömmlichen

Halbleiterpackungen bis zu dem Maß reduziert werden, dass der

erste Halbleiterchip 22 in die erste Durchgangsöffnung 23a eingesetzt

wird oder in dieser enthalten ist. Zum Beispiel kann die Packungsdicke "t" reduziert werden, da sich keine extra

Metallschicht zwischen dem Halbleiterchip und den leitfähigen Strukturen 24 befindet

wie in den herkömmlichen

Halbleiterpackungen. Ein

Verfahren zur Bildung der Halbleiterpackung 20 kann die

Bereitstellung eines Substrats 23, das eine Oberseite und

eine der Oberseite entgegengesetzte Unterseite beinhaltet, das Bilden

einer ersten Durchgangsöffnung 23a innerhalb

des Substrats, die sich von der Oberseite bis zu der Unterseite

erstreckt, das Bilden einer leitfähigen Struktur 24 auf der

Oberseite des Substrats 23 so, dass sie sich über der

ersten Durchgangsöffnung 23a erstreckt,

die Bereitstellung eines ersten Halbleiterchips 22 innerhalb wenigstens

eines Teils der ersten Durchgangsöffnung 23a und das

elektrische Verbinden der leitfähigen

Struktur 24mit dem Halbleiterchip 22 durch eine erste

leitfähige

Zwischenverbindung 21 beinhalten, die sich innerhalb der

ersten Durchgangsöffnung 23a erstreckt.

Wie ebenfalls exemplarisch vorstehend beschrieben, kann ein Verfahren

zur Bildung der Halbleiterpackung 20 das Bilden einer Mehrzahl

von ersten leitfähigen

Zwischenverbindungen 21 und einer Mehrzahl von leitfähigen Strukturen 24 derart

beinhalten, dass die Mehrzahl von ersten leitfähigen Zwischenverbindungen 21 den

ersten Halbleiterchip 22 elektrisch mit der Mehrzahl von

leitfähigen

Strukturen 24 verbindet. Wie

exemplarisch in In

der vorliegenden Ausführungsform

beinhaltet der erste Halbleiterchip 22 eine aktive Oberfläche 22a,

die in Richtung der leitfähigen

Strukturen 24 gewandt ist, wie zum Beispiel in Die

Mehrzahl von ersten externen Kontaktanschlüssen 21 können leitfähige Kontakthügel sein, wie

Lothügel,

leitfähige

Kugeln wie Lotkugeln oder dergleichen, die auf dem ersten Halbleiterchip 22 angeordnet

sind. Zum Beispiel können

leitfähige

Kontakthügel

oder leitfähige

Kugeln durch Bilden einer Mehrzahl von Kontaktstellen auf der aktiven

Oberfläche 22a des

ersten Halbleiterchips 22, Bilden einer Passivierungsschichtstruktur über der

aktiven Oberfläche 22a des

ersten Halbleiterchips 22, um wenigstens einen Teil von

jeder der Mehrzahl von Kontaktstellen freizulegen, und Bereitstellen

eines leitfähigen Materials

(z. B. Blei, Zinn oder dergleichen oder einer Kombination derselben)

auf dem freigelegten Teil von jeder der Mehrzahl von Kontaktstellen

gebildet werden. Leitfähige

Kontakthügel

können

auch durch Bonden eines Drahts an den freigelegten Teil von jeder

der Mehrzahl von Kontaktstellen und Abtrennen des Drahts in einer

bestimmten Höhe über den

Kontaktstellen gebildet werden. Die Mehrzahl von ersten externen

Kontaktanschlüssen 21 kann

exemplarisch durch Bereitstellen einer Kristallkeimschicht über der aktiven

Oberfläche 22a des

ersten Halbleiterchips 22, Bilden einer Photoresiststruktur über der

Kristallkeimschicht, Strukturieren der Kristallkeimschicht, Entfernen

der Photoresiststruktur und Elektroplattieren eines leitfähigen Materials

auf die strukturierte Kristallkeimschicht gebildet werden. In einer

Ausführungsform

kann die Kristallkeimschicht Kupfer beinhalten und eine Dicke von

etwa 0,5 μm

aufweisen, während

das leitfähige

Material Gold beinhalten kann. In

einer weiteren Ausführungsform

können, wenngleich

nicht gezeigt, die Mehrzahl von ersten externen Kontaktanschlüssen 21 und

entsprechende der Mehrzahl von leitfähigen Strukturen 24 als

unitäre Struktur

bereitgestellt werden. In einer derartigen Ausführungsform ragt die Mehrzahl

von externen Kontaktanschlüssen 21 von

entsprechenden der Mehrzahl von leitfähigen Strukturen 24 so

vor, dass sie den ersten Halbleiterchip 22 kontaktieren,

wie exemplarisch in Zwischen

dem ersten Halbleiterchip 22 und der Mehrzahl von leitfähigen Strukturen

ist ein isolierendes Material 25 vorgesehen. Als ein Ergebnis können die

aktive Oberfläche 22a,

auf der integrierte Schaltkreise ausgebildet sind, und die ersten

externen Kontaktanschlüsse 21 mit

dem isolierenden Material 25 bedeckt sein und können somit

vor der äußeren Umgebung

geschützt

sein. Mit dem isolierenden Material 25, das optional auf

dem Substrat 23 gebildet ist, kann der erste Halbleiterchip 22 sicher

an dem Substrat 23 befestigt werden. Das isolierende Material 25 kann

zum Beispiel ein isolierendes Material wie Klebstoff, Epoxid, eine

Epoxidgießverbindung (EMC),

Polyamidharz oder dergleichen oder eine Kombination derselben beinhalten.

Das isolierende Material 25 kann z. B. durch Injizieren

eines isolierenden Materials in den zwischen dem ersten Halbleiterchip 22,

dem Substrat 23 und den leitfähigen Strukturen 24 definierten

Zwischenraum bereitgestellt werden. Mit

Ausführungsformen

der Erfindung, wie vorstehend beschrieben, ist es möglich, die

Menge des Isolatormaterials 25 auf dem Substrat 23 zu

reduzieren, während

die Fläche

der Haftoberfläche 20a vergrößert werden

kann. Speziell kann der Bondbereich "A1" vergrößert werden,

während

der Gießbereich "B1" reduziert werden

kann. Dies gilt insbesondere, da das isolierende Material 25 nicht

ausreichend bereitgestellt werden muss, um Zwischenmetallschichten

zu bedecken, wie in dem in Wie

klarer in Des

Weiteren werden, wie in Wie

außerdem

in Im

Hinblick auf das Vorstehende kann ein Verfahren zur Bildung eines

Packungssystems 200 (hierin auch als ein elektronisches

System oder eine IC-Karte bezeichnet) zusammengefasst exemplarisch

als ein Verfahren charakterisiert werden, welches Bereitstellen

eines Substrats 23 mit einer Oberseite und einer zu der

Oberseite entgegengesetzten Unterseite, Bilden einer ersten Durchgangsöffnung 23a innerhalb

des Substrats 23 derart, dass sich die erste Durchgangsöffnung 23a von

der Oberseite zu der Unterseite erstreckt, Bilden einer leitfähigen Struktur 24 auf

der Oberseite des Substrats 23 derart, dass sich die leitfähige Struktur 24 über der

ersten Durchgangsöffnung 23a erstreckt,

Bereitstellen von wenigstens einem Teil eines ersten Halbleiterchips 22 innerhalb

der ersten Durchgangsöffnung 23a,

elektrisches Verbinden der leitfähigen

Struktur 24 mit dem Halbleiterchip 24 durch eine

erste leitfähige

Zwischenverbindung 21, die sich innerhalb der ersten Durchgangsöffnung 23a befindet,

Bereitstellen eines isolierenden Materials 25 zwischen

der leitfähigen

Struktur 24 und dem ersten Halbleiterchip 22 und

Koppeln des Substrats 23 an den Packungskörper 26 beinhaltet,

um ein elektronisches System 200 zu bilden, wobei wenigstens

ein Teil des Substrats 23 innerhalb einer innerhalb des

Packungskörpers 26 definierten

Vertiefung 26a angeordnet ist. Ebenfalls

im Hinblick auf das Vorstehende kann ein Packungssystem 200 (hierin

auch als ein elektronisches System oder eine IC-Karte bezeichnet)

exemplarisch als eine Halbleiterpackung 20 und einen Packungskörper 26 enthaltend

charakterisiert werden, der die Halbleiterpackung 20 enthält. Die Halbleiterpackung 20 kann

exemplarisch so charakterisiert werden, dass sie ein Substrat 23 mit

einer Oberseite, einer der Oberseite entgegengesetzten Unterseite

und einer Durchgangsöffnung 23a,

die sich von der Oberseite zu der Unterseite erstreckt, eine leitfähige Struktur 24 auf

der Oberseite des Substrats, die sich über der ersten Durchgangsöffnung 23a erstreckt,

einen ersten Halbleiterchip 22, welcher der leitfähigen Struktur 24 derart

zugewandt ist, dass wenigstens ein Teil des ersten Halbleiterchips 22 innerhalb

der ersten Durchgangsöffnung 23a angeordnet

ist, und einen ersten externen Kontaktanschluss 21 innerhalb

der ersten Durchgangsöffnung 23a beinhaltet,

der die leitfähige

Struktur 24 elektrisch mit dem ersten Halbleiterchip 22 verbindet. Wie

exemplarisch vorstehend unter Bezugnahme auf die In

einer Ausführungsform

kann das erste Verfahren 610 zum Bilden einer Halbleiterpackung 20 wie

folgt durchgeführt

werden. In Schritt 611 wird die Mehrzahl von ersten externen

Kontaktanschlüssen 21 auf

dem ersten Halbleiterchip 22 gebildet. In Schritt 613 wird

eine erste Durchgangsöffnung 23a in dem

Substrat 23 gebildet. In Schritt 615 werden leitfähige Strukturen 24 auf

dem Substrat 23 gebildet. In einer Ausführungsform wird ein Teil der

leitfähigen Strukturen 24 durch

die erste Durchgangsöffnung 23 freigelegt.

In Schritt 617 wird der erste Halbleiterchip 22 in

die erste Durchgangsöffnung 23a eingesetzt. Dabei

ist eine aktive Oberfläche

des Halbleiterchips 22 den leitfähigen Strukturen 24 zugewandt

und ist durch die Mehrzahl von ersten externen Kontaktanschlüssen 21 damit

elektrisch verbunden. In Schritt 619 wird ein isolierendes

Material 25 zwischen den leitfähigen Strukturen 24 und

dem ersten Halbleiterchip 22 gebildet oder dort injiziert,

um den ersten Halbleiterchip 22 und die leitfähigen Strukturen 24 einzukapseln.

In einer Ausführungsform

kann das isolierende Material 24 während des Einsetzens der Halbleiterpackung 20 in

eine Vertiefung 26a des Kartenkörpers 26 gebildet

werden. Das heißt,

das isolierende Material 25 kann zur gleichen Zeit bereitgestellt

werden, wie die Halbleiterpackung 20 mit dem Kartenkörper 26 gekoppelt

wird. In

Schritt 620 wird separat von den vorstehend beschriebenen

Prozessen die Vertiefung 26a in dem Kartenkörper 26 gebildet.

In einer Ausführungsform

kann die Vertiefung 26a beim Bilden des Kartenkörpers 26 gebildet

werden (z. B. während

eines Gießprozesses).

In Schritt 630 wird die durch die vorstehenden Prozesse

gebildete Halbleiterpackung 20 in die Vertiefung 26a eingesetzt,

um ein Packungssystem 200 zu bilden. In

entsprechenden Ausführungsformen

können

der Prozess 619 und der Prozess 630 gleichzeitig

durchgeführt

werden, während

ein Unterfüllprozess

durchgeführt

wird. In

einer Ausführungsform

ist der Kontaktbereich 34 von einer der leitfähigen Strukturen 24 benachbart

zu dem Verlängerungsbereich 35 einer

weiteren der leitfähigen

Strukturen 24 entlang der ersten Seite (oder der zweiten

Seite) der ersten Durchgangsöffnung 23a. In

einer weiteren Ausführungsform

weist der Kontaktbereich 34, der an der ersten Seite der

ersten Durchgangsöffnung 23 von

dem Substrat 23 gestützt wird,

die gleiche Form wie der Kontaktbereich 34 auf, der an

der zweiten Seite der ersten Durchgangsöffnung 23a von dem

Substrat 23 gestützt

wird. In ähnlicher

Weise kann der Verlängerungsbereich 35,

der an der zweiten Seite der ersten Durchgangsöffnung 23a von dem

Substrat 23 gestützt

wird, die gleiche Form aufweisen wie der Verlängerungsbereich 35, der

an der ersten Seite der ersten Durchgangsöffnung 23a von dem

Substrat 23 gestützt

wird. In

noch einer weiteren Ausführungsform

sind die Kontaktbereiche 34 der leitfähigen Strukturen 24, die

sich über

Seitenbereichen der ersten Durchgangsöffnung 23a erstrecken,

so charakterisiert, dass sie eine rechteckige Form aufweisen. In ähnlicher

Weise können

Verlängerungsbereiche 35 von leitfähigen Strukturen 24,

die sich über

Seitenbereichen der ersten Durchgangsöffnung 23a erstrecken, so

charakterisiert sein, dass sie eine schmale Streifenform aufweisen. Wenn

die leitfähigen

Strukturen 24, die sich über Seitenbereichen der ersten

Durchgangsöffnung 23a erstrecken,

wie vorstehend unter Bezugnahme auf Eine

Mehrzahl von Isolatorrahmenkörper-Durchgangsöffnungen 254 ist

innerhalb des Isolatorrahmenkörpers 252 definiert

und erstreckt sich von einer Oberseite des Isolatorrahmenkörpers 252 zu

einer Unterseite des Isolatorrahmenkörpers 252. In einer

Ausführungsform

wird die Mehrzahl von ersten externen Kontaktanschlüssen 21 in

die Mehrzahl von Isolatorrahmenkörper-Durchgangsöffnungen 254 eingesetzt.

In einer weiteren Ausführungsform erstreckt

sich die Mehrzahl von ersten externen Kontaktanschlüssen 21 vollständig durch

die Mehrzahl von Isolatorrahmenkörper-Durchgangsöffnungen 254 hindurch,

um mit den leitfähigen

Strukturen 24 gekoppelt zu werden. So

kann, wie vorstehend exemplarisch beschrieben, das isolierende Material 25 gemäß einer Ausführungsform

als ein Isolatorrahmenkörper 252 charakterisiert

werden, der eine durch diesen hindurch definierte Isolatorrahmenkörper-Durchgangsöffnung 254 beinhaltet,

so dass sich ein erster externer Kontaktanschluss 21 durch

die Isolatorrahmenkörper-Durchgangsöffnung 254 hindurch

erstrecken kann. In

einer Ausführungsform

kann ein Verfahren zur Bereitstellung des isolierenden Materials 25 zum Beispiel

das Bilden eines Isolatorrahmenkörpers 252,

wobei der Isolatorrahmenkörper 252 eine

durch diesen hindurch definierte Isolatorrahmenkörper-Durchgangsöffnung 254 beinhaltet,

und das Anordnen des Isolatorrahmenkörpers 252 innerhalb

der ersten Durchgangsöffnung 23a so

beinhaltet, dass er benachbart zu der leitfähigen Struktur 24 ist.

Ein Verfahren zum elektrischen Verbinden einer leitfähigen Struktur 25 mit

dem ersten Halbleiterchip 22 kann zum Beispiel das Einsetzen

eines ersten externen Kontaktanschlusses 21 durch die Isolatorrahmenkörper-Durchgangsöffnung 254 hindurch

beinhalten. Wenn

sich die Mehrzahl von ersten externen Kontaktanschlüssen 21 vollständig durch

die Mehrzahl von Isolatorrahmenkörper-Durchgangsöffnungen 254 hindurch

erstreckt, kontaktiert der erste Halbleiterchip 22 in einer

entsprechenden Ausführungsform

den unteren Teil 252b des Isolatorrahmenkörpers 252.

In einer derartigen Ausführungsform kann

der erste Halbleiterchip 22 mit dem unteren Teil 252b des

Isolatorrahmenkörpers 252 zum

Beispiel durch einen Klebstoff gekoppelt sein. Aufgebaut

wie vorstehend beschrieben, kann der Isolatorrahmenkörper 252 bei

einer Ausrichtung der Mehrzahl von ersten externen Kontaktanschlüssen 21 bezüglich entsprechenden

der Mehrzahl von leitfähigen

Strukturen 24 innerhalb der ersten Durchgangsöffnungen 23a helfen.

Der Isolatorrahmenkörper 252 kann

aus einem isolierenden Material gebildet werden, wie Polyimid, Epoxid,

Harz etc. Die Bezugnehmend

auf Die In

einer entsprechenden Ausführungsform wird

das Barrierenelement vor der Bildung des isolierenden Materials 25 angeordnet.

In entsprechenden Ausführungsformen

wird ein Barrierenelement bereitgestellt, um sich zwischen Paaren

von benachbarten der Mehrzahl von leitfähigen Strukturen 24 über wenigstens

einen Teil des zwischen den benachbarten der Mehrzahl von leitfähigen Strukturen 24 definierten

Zwischenraums hinweg zu erstrecken, wie zum Beispiel in In

weiteren Ausführungsformen

ist ein Barrierenelement innerhalb wenigstens eines Teils des zwischen

den benachbarten der Mehrzahl von leitfähigen Strukturen 24 definierten

Zwischenraums angeordnet, wie zum Beispiel in In

weiteren Ausführungsformen

befindet sich ein Barrierenelement zwischen den benachbarten der

Mehrzahl von leitfähigen

Strukturen 24 und dem ersten Halbleiterchip 22,

wie zum Beispiel in den Bezugnehmend

auf In

entsprechenden Ausführungsformen

beinhalten die Barrierenelemente 40 bis 43 ein

harzartiges Material. In einer weiteren Ausführungsform wird das Barrierenelement 44 aus

einem streifenartigen Material gebildet. Ein Verfahren zur Bildung

einer Halbleiterpackung gemäß der Erfindung

kann zum Beispiel das Entfernen des Barrierenelements 44 nach

dem Bilden des isolierenden Materials 25 beinhalten. In

einer entsprechenden Ausführungsform beinhaltet

das streifenartige Material ein Material, das selektiv an den leitfähigen Strukturen 24 anbringbar/von

diesen abnehmbar ist. In einer Ausführungsform beinhaltet das harzartige

Material ein Material, das versteift werden kann (z. B. nachdem

das isolierende Material injiziert wurde). Demgemäß ist die

Mehrchip-Halbleiterpackung 50a eine heterogene Mehrchip-Halbleiterpackung. Bezugnehmend

auf In

dieser Ausführungsform

sind der erste Chip 22 und der zweite Chip 57 identisch,

sind im Wesentlichen gleich oder ähnlich (z. B. basierend auf der

Funktionalität).

Demgemäß ist die Mehrchip-Halbleiterpackung 50b eine

homogene Mehrchip-Halbleiterpackung. Die Bezugnehmend

auf Bezugnehmend

auf Bezugnehmend

auf Bezugnehmend

auf Gemäß den vorstehend

unter Bezugnahme auf die Außerdem kann

das in den vorstehenden Ausführungsformen

exemplarisch beschriebene Packungssystem wenigstens teilweise aufgrund

der Konfiguration der Halbleiterpackung so gefertigt werden, dass

es relativ dünn,

kostengünstig

und ohne Komplikation ist. Dies gilt insbesondere, da der Halbleiterchip

innerhalb einer Öffnung

des Substrats angeordnet werden kann, wodurch die Gesamtdicke des

elektronischen Systems reduziert wird, da sich die Dicke des Halbleiterchips

nicht zu der Gesamtdicke des elektronischen Systems hinzu addiert.

Als ein Ergebnis können

eine dünnere

Halbleiterpackung und ein dünneres

elektronisches System, wie eine IC-Karte, gemäß Ausführungsformen der vorliegenden

Erfindung erhalten werden. Außerdem können gemäß den vorstehend exemplarisch

beschriebenen Ausführungsformen Prozessschritte

im Vergleich zum Stand der Technik reduziert werden, da die erfinderischen

Verfahren weniger Metall- oder leitfähige Schichten erfordern, wodurch

die Gesamtfertigungskosten wesentlich reduziert werden. Es

versteht sich, dass das Packungssystem und die Halbleiterpackung,

die gemäß den vorstehend

exemplarisch beschriebenen Ausführungsformen

bereitgestellt werden, in Verbindung mit Bauelementen wie IC-Karten, Speicherkarten,

USB-Karten, internen Speicherpackungen von Media-Playern (z. B.

MP3-Playern), mobilen Telephonen, Digitalkameras und der dergleichen

implementiert werden können. The semiconductor package (20) has a conductive pattern (24) provided on the substrate (23) and extended over the through-hole (23a). A semiconductor chip (22) is arranged within the through-hole. An external contact terminal (21) provided within the through-hole, electrically connects the conductive pattern to the semiconductor chip. Independent claims are included for the following: (1) semiconductor package formation method; and (2) electronic system formation method. Halbleiterpackung mit Halbleiterpackung nach Anspruch 1, wobei der externe

Kontaktanschluss einen leitfähigen

Kontakthügel,

eine leitfähige

Kugel oder eine Kombination derselben beinhaltet, der/die auf dem

Halbleiterchip angeordnet ist. Halbleiterpackung nach Anspruch 1, wobei der externe

Kontaktanschluss und die leitfähige

Struktur eine unitäre

Struktur bilden, wobei der externe Kontaktanschluss von der leitfähigen Struktur

vorsteht. Halbleiterpackung nach einem der Ansprüche 1 bis

3, wobei das Substrat eine Oberseite und eine dazu entgegengesetzte

Unterseite beinhaltet und wobei sich eine Unterseite des externen

Kontaktanschlusses zwischen einer Oberseite und einer Unterseite

des Substrats befindet. Halbleiterpackung nach einem der Ansprüche 1 bis

4, die des Weiteren ein isolierendes Material (25) zwischen

dem Halbleiterchip und der leitfähigen Struktur

beinhaltet. Halbleiterpackung nach Anspruch 5, wobei das isolierende

Material einen Isolatorrahmenkörper (252)

bildet, wobei der Isolatorrahmenkörper eine durch diesen hindurch

definierte Isolatorrahmenkörper-Durchgangsöffnung (254)

beinhaltet und wobei sich der externe Kontaktanschluss durch die

Isolatorrahmenkörper-Durchgangsöffnung hindurch

erstreckt. Halbleiterpackung nach Anspruch 5 oder 6, wobei das

isolierende Material einen anisotropen leitfähigen Film (ACF) beinhaltet. Halbleiterpackung nach einem der Ansprüche 1 bis

7, wobei die leitfähige

Struktur in einem ersten Bereich und einem zweiten Bereich, der

von dem ersten Bereich beabstandet ist, von dem Substrat gestützt. Halbleiterpackung nach Anspruch 8, wobei die leitfähige Struktur

einen Kontaktbereich (34), der in dem ersten Bereich von

dem Substrat gestützt

ist, und einen Verlängerungsbereich

(35) beinhaltet, der von dem Substrat gestützt ist,

wobei der erste Bereich und der zweite Bereich entgegengesetzt zueinander

sind. Halbleiterpackung nach Anspruch 9, wobei der Kontaktbereich

eine rechteckige Form aufweist und der Verlängerungsbereich eine schmale

Streifenform aufweist. Halbleiterpackung nach einem der Ansprüche 1 bis

10, wobei eine Mehrzahl von leitfähigen Strukturen (24)

und eine Mehrzahl von externen Kontaktanschlüssen (21) bereitgestellt

sind, wobei jeder der Mehrzahl von externen Kontaktanschlüssen den Halbleiterchip

mit einer entsprechenden der Mehrzahl von leitfähigen Strukturen elektrisch

verbindet. Halbleiterpackung nach Anspruch 11, wobei ein Zwischenraum

zwischen der Mehrzahl von leitfähigen

Strukturen definiert ist und ein Barrierenelement (40 bis 44)

bereitgestellt ist, das sich zwischen wenigstens einem Paar von

benachbarten der Mehrzahl von leitfähigen Strukturen über den

Zwischenraum hinweg erstreckt. Halbleiterpackung nach Anspruch 12, wobei das Barrierenelement

auf einer Unterseite des Paares von benachbarten der Mehrzahl von

leitfähigen Strukturen

angeordnet ist. Halbleiterpackung nach Anspruch 12, wobei das Barrierenelement

auf Oberseiten des Paares von benachbarten der Mehrzahl von leitfähigen Strukturen

angeordnet ist. Halbleiterpackung nach Anspruch 12, wobei das Barrierenelement

wenigstens innerhalb eines Teils des Zwischenraums angeordnet ist. Halbleiterpackung nach Anspruch 12, wobei wenigstens

ein Teil des Barrierenelements zwischen der Mehrzahl von leitfähigen Strukturen

und dem Halbleiterchip angeordnet ist. Halbleiterpackung nach einem der Ansprüche 12 bis

16, wobei das Barrierenelement entfernbar ist. Halbleiterpackung nach einem der Ansprüche 1 bis

17, wobei die erste Durchgangsöffnung

in der Draufsicht eine im Wesentlichen rechteckige Form aufweist. Halbleiterpackung nach einem der Ansprüche 1 bis

18, wobei eine Zwischenverbindung die leitfähige Struktur direkt kontaktiert. Halbleiterpackung nach einem der Ansprüche 1 bis

19, die des Weiteren einen zweiten Halbleiterchip (571)

beinhaltet, der mit dem ersten Halbleiterchip elektrisch gekoppelt

ist. Halbleiterpackung nach Anspruch 20, die des Weiteren

einen leitfähigen

Durchkontakt (59) beinhaltet, der sich durch den ersten

Halbleiterchip (22) hindurch erstreckt, wobei der leitfähige Durchkontakt den

ersten und den zweiten Halbleiterchip (22, 57) elektrisch

verbindet. Halbleiterpackung nach Anspruch 20, wobei der zweite

Chip unter Verwendung eines Bonddrahts (561) mit der leitfähigen Struktur

elektrisch gekoppelt ist. Verfahren zur Herstellung einer Halbleiterpackung,

das die folgenden Schritte umfasst: Verfahren nach Anspruch 23, wobei der externe Kontaktanschluss

und die leitfähige

Struktur durch eine unitäre

Struktur gebildet werden, wobei der externe Kontaktanschluss von

der leitfähigen Struktur

vorsteht und wobei das elektrische Verbinden der leitfähigen Struktur

mit dem Halbleiterchip das Kontaktieren des Halbleiterchips mit

dem externen Kontaktanschluss beinhaltet. Verfahren nach Anspruch 23 oder 24, das des Weiteren

das Bereitstellen eines isolierenden Materials (25) zwischen

dem Halbleiterchip und der leitfähigen

Struktur beinhaltet. Verfahren nach Anspruch 25, wobei das Bereitstellen

des isolierenden Materials umfasst: Verfahren nach einem der Ansprüche 23 bis 26, das des Weiteren

umfasst: Verfahren nach Anspruch 27, das des Weiteren das

Anordnen eines Barrierenelements (40 bis 44) beinhaltet,

das sich zwischen wenigstens einem Paar von benachbarten der Mehrzahl

von leitfähigen Strukturen über einen

zwischen der Mehrzahl von leitfähigen

Strukturen definierten Zwischenraum hinweg erstreckt. Verfahren nach Anspruch 28, das des Weiteren umfasst: Verfahren zur Herstellung eines elektronischen Systems,

das die folgenden Schritte umfasst: Verfahren nach Anspruch 30, das des Weiteren das

gleichzeitige Bereitstellen des isolierenden Materials und Koppeln

des Substrats an dem Packungskörper

beinhaltet. Elektronisches System mit Elektronisches System nach Anspruch 32, wobei der

Packungskörper

eine darin definierte Vertiefung beinhaltet und wobei die Halbleiterpackung innerhalb

der Vertiefung angeordnet ist. Elektronisches System nach Anspruch 32 oder 33,

wobei der Packungskörper

eine IC-Karte beinhaltet.

– einem Substrat (23),

das eine sich durch dieses hindurch erstreckende Durchgangsöffnung (23a)

beinhaltet,

– einer

leitfähigen

Struktur (24), die über

dem Substrat liegt und sich über

der Durchgangsöffnung

erstreckt,

– einem

Halbleiterchip (22), welcher der leitfähigen Struktur zugewandt ist,

wobei wenigstens ein Teil des Halbleiterchips innerhalb der Durchgangsöffnung angeordnet

ist, und

– einem

externen Kontaktanschluss (21) innerhalb der Durchgangsöffnung,

der die leitfähige

Struktur mit dem Halbleiterchip elektrisch verbindet.

– Bereitstellen eines Substrats

(23), das eine Oberseite und eine zur Oberseite entgegengesetzte

Unterseite beinhaltet,

– Bilden

einer Durchgangsöffnung

(23a) innerhalb des Substrats, wobei sich die Durchgangsöffnung von

der Oberseite zu der Unterseite erstreckt,

– Bilden einer leitfähigen Struktur

(24) auf der Oberseite des Substrats, wobei sich die leitfähige Struktur über der

Durchgangsöffnung

erstreckt,

– Anordnen

wenigstens eines Teils eines Halbleiterchips (22) innerhalb

der Durchgangsöffnung

und

– elektrisches

Verbinden der leitfähigen

Struktur mit dem Halbleiterchip, wobei sich ein externer Kontaktanschluss

(21) innerhalb der Durchgangsöffnung befindet.

– Bilden eines Isolatorrahmenkörpers (252),

wobei der Isolatorrahmenkörper

eine durch diesen hindurch definierte Isolatorrahmenkörper-Durchgangsöffnung (254)

beinhaltet, und

– Anordnen

des Isolatorrahmenkörpers

innerhalb der Substrat-Durchgangsöffnung (23a),

um benachbart zu der leitfähigen

Struktur zu sein,

– wobei

das elektrische Verbinden der leitfähigen Struktur mit dem Halbleiterchip

das Einsetzen des externen Kontaktanschlusses durch die Isolatorrahmenkörper-Durchgangsöffnung hindurch

beinhaltet.

– Bilden

einer Mehrzahl von leitfähigen

Strukturen (24) und

– Bilden einer Mehrzahl von

externen Kontaktanschlüssen

(21), wobei jeder der Mehrzahl von externen Kontaktanschlüssen den

Halbleiterchip mit einer entsprechenden der Mehrzahl von leitfähigen Strukturen

elektrisch verbindet.

– Bereitstellen

eines isolierenden Materials zwischen dem Halbleiterchip und der

leitfähigen

Struktur nach dem Anordnen des Barrierenelements und

– Entfernen

des Barrierenelements nach dem Bereitstellen des isolierenden Materials.

– Bereitstellen einer Halbleiterpackung

gemäß dem Verfahren

nach einem der Ansprüche

23 bis 29 und

– Koppeln

des Substrats mit einem Packungskörper, um das elektronische

System zu bilden, wobei wenigstens ein Teil des Substrats innerhalb

einer innerhalb des Packungskörpers

definierten Vertiefung angeordnet ist.

– einer Halbleiterpackung nach

einem der Ansprüche 1

bis 22 und

– einem

Packungskörper,

der die Halbleiterpackung enthält.