Verfahren zur Herstellung von Halbleitervorrichtungen und entsprechende Vorrichtung

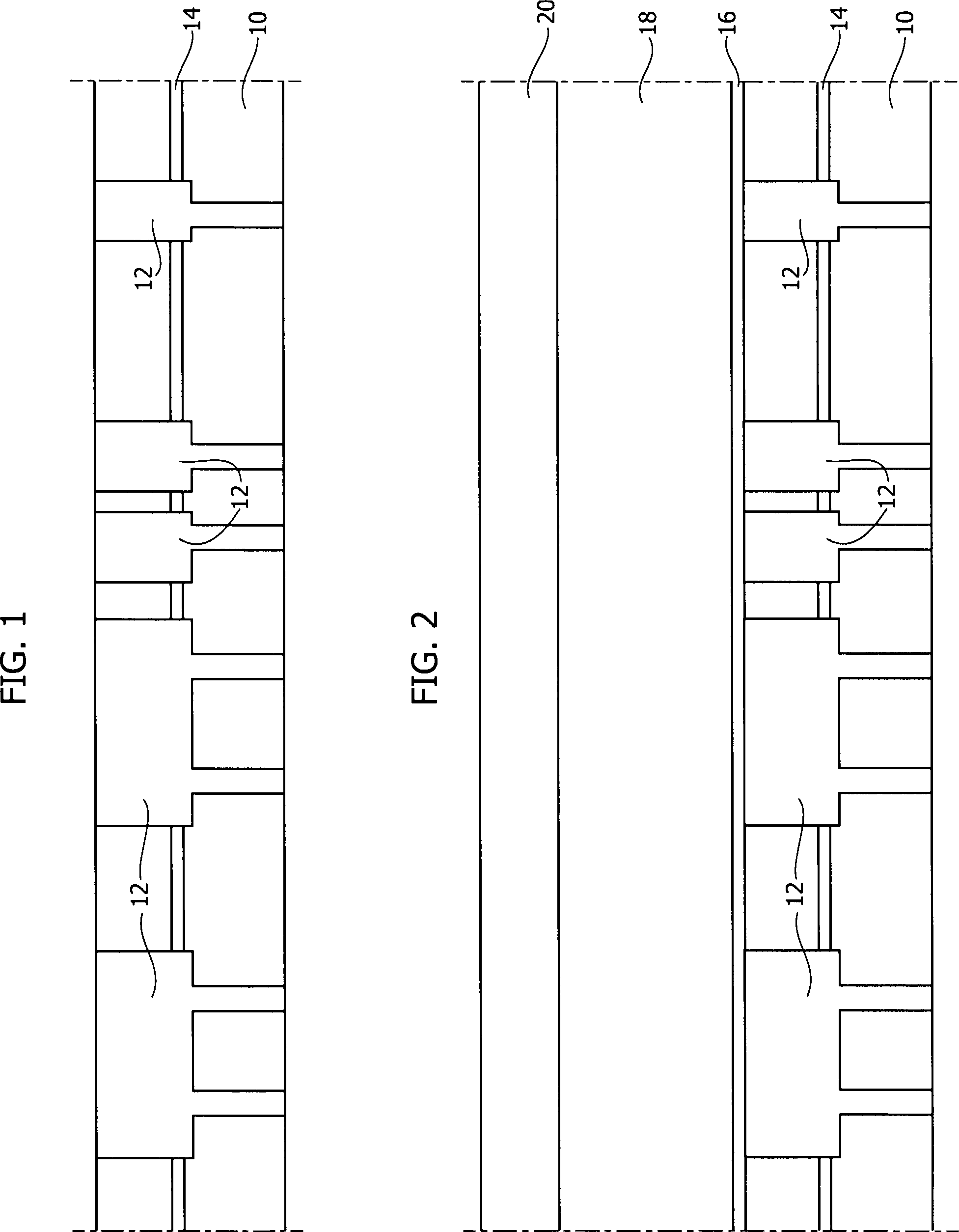

Die Beschreibung bezieht sich auf die Herstellung von Halbleitervorrichtungen. Eine oder mehrere Ausführungsformen können beispielsweise für die Reduzierung von thermomechanischer Belastung in integrierten Schaltungen, beispielsweise für Automobil- und Verbraucherprodukte, angewendet werden. Verschiedene Typen von integrierten Schaltungen (IC) können Technologien wie beispielsweise BCD (Bipolare CMOS-DMOS) Technologie verwenden. BCD-Technologie kann beispielsweise vorteilhaft zur Herstellung von integrierten Schaltungen verwendet werden, die sowohl Leistungselektronik als auch Logikelektronik aufweisen. BCD-Technologie schafft eine Familie von Siliziumprozessen, von denen jeder die Stärken der drei unterschiedlichen Prozesstechnologien auf einem einzelnen Chip kombiniert: Bipolar für präzise analoge Funktionen, CMOS (Complementary Metal Oxide Semiconductor) für digitale Konstruktion und DMOS (Double Diffused Metal Oxide Semiconductor) für Leistungs- und Hochspannungselemente. Die Implementierung von BCD-Technologie kann Deckschicht-Kupfermetall-Verbindungen, bezeichnet als RDL (Re-Distribution Layer), umfassen. Die Resistenz von Passivierungs- und Zwischenisolierschichten gegenüber Problemen mit der Zuverlässigkeit, wie beispielsweise durch thermoelastische Kopplung und Belastungen während Drahtbonding- und Einhausungsprozessen verursacht, kann einen Faktor darstellen, auf den geachtet werden muss. Bei der Herstellung von integrierten Schaltungen kann Siliziumnitrid (SiN) oder Siliziumkarbid (SiC) verwendet werden, um eine Passivierungsschicht für Mikrochips bereitzustellen, beispielsweise um eine Barriere gegen Wassermoleküle und andere Quellen von Korrosion und Instabilität in der Mikroelektronik zu schaffen. In strukturellen Ecken von Metallisierungen, wie beispielsweise Cu(Kupfer)-RDL-Deckschichtmetallisierungen, können Belastungen aufgrund von thermomechanischer Nicht-Übereinstimmung zwischen unterschiedlichen Materialien, beispielsweise Barriereschicht (TiW, Ta, TaNta), Metallisierungskappenschicht (Ni-Pd, Ni-Pd-Au, Ni-Au), Passivierungsschicht (SiN, SiC) Tripelpunkt auftreten. Eine Aufgabe einer oder mehrerer Ausführungsformen ist der Beitrag zur Überwindung der vorstehend erwähnten kritischen Punkte, beispielsweise Passivierungsbelastung in der oberen Oberfläche der Passivierungsschicht am Rand (beispielsweise an einer Ecke) einer Cu-RDL-Struktur. Gemäß einer oder mehreren Ausführungsformen kann diese Aufgabe mittels eines Verfahrens mit den in den anliegenden Ansprüchen dargelegten Merkmalen gelöst werden. Eine oder mehrere Ausführungsformen können sich auch auf eine entsprechende Vorrichtung beziehen. Die Ansprüche sind ein fester Bestandteil der technischen Offenbarung einer oder mehrerer Ausführungsformen, wie hierin dargelegt. Eine oder mehrere Ausführungsformen können zur Reduzierung von SiN-Passivierungsbelastung durch Vermeiden eines „Tripelpunkts” führen, beispielsweise durch Entkoppeln einer Kappenbarriere(beispielsweise Nickel TiW)-Grenzfläche von der oberen Passivierungsoberfläche (beispielsweise SiN, SiC). Eine oder mehrere Ausführungsformen können eine Modifizierung beispielsweise eines Cu RDL-Prozessablaufes beinhalten, der das Hinzufügen einer Opferisolierschicht zum Bilden einer Lücke zwischen Passivierung und beispielsweise Nickel beinhaltet. In einer oder mehreren Ausführungsformen kann eine verbesserte Robustheit der Passivierung mittels eines Prozessablaufes erlangt werden, der das vollständige Bedecken von Kupfer (Cu) durch Nickel (Ni) beinhalten kann, um eine Kupfermigration ohne Veränderungen von Materialien und in Beziehung stehenden Grenzflächen zu verhindern. Eine oder mehrere Ausführungsformen können eine Doppelbarriereschicht (beispielsweise TiW) aufweisen, die dazu ausgebildet ist, Nickel und Passivierung zu entkoppeln, indem die Anwesenheit eines „Tripelpunktes” vermieden wird, der für kritische Belastung der Passivierung verantwortlich ist. Eine oder mehrere Ausführungsformen können eine Doppelkupferbarriereabscheidung, einen Spalt zwischen Nickel und Passivierung, ohne Aufwachsen von Nickel auf einer Kupferbarriere in Kontakt mit der Passivierung beinhalten. Eine oder mehrere Ausführungsformen können auf eine TiW-Ni-SiN-Passivierungsgrenzfläche verzichten, mit einem vollständig eingekapselten Kupfer, beispielsweise in TiW und Ni (zur Vermeidung von Kupfermigration und Korrosion), und ohne Unterschnitte unter der letzten Barriereätzung. Eine oder mehrere Ausführungsformen werden jetzt rein beispielhaft mit Bezugnahme auf die beiliegenden Zeichnungen beschrieben. In denen zeigen: Es wird zu verstehen sein, dass die Zeichnungen der Klarheit der Darstellung bestimmter Merkmale (z. B. Schichtdicken) halber möglicherweise nicht im gleichen Maßstab gezeichnet sind. In der folgenden Beschreibung werden eine oder mehrere spezielle Einzelheiten mit dem Ziel dargestellt, ein tieferes Verständnis der beispielhaften Ausführungsformen zu schaffen. Die Ausführungsformen können ohne eine oder mehrere der speziellen Einzelheiten oder mit anderen Verfahren, Komponenten, Materialien usw. erlangt werden. In anderen Fällen sind bekannte Strukturen, Materialien oder Vorgänge nicht im Detail dargestellt oder beschrieben, um bestimmte Aspekte von Ausführungsformen nicht zu überdeckenen. Die Bezugnahme auf „eine Ausführungsform” im Rahmen der vorliegenden Beschreibung soll darauf hinweisen, dass eine bestimmte im Bezug zu der Ausführungsform beschriebene Konfiguration, Struktur oder Eigenschaft in mindestens einer Ausführungsform enthalten ist. Somit beziehen sich Ausdrücke wie z. B. „in einer Ausführungsform”, die in einem oder mehreren Punkten der vorliegenden Beschreibung vorkommen können, nicht notwendigerweise auf ein und dieselbe Ausführungsform. Außerdem können bestimmte Konfigurationen, Strukturen oder Eigenschaften auf jegliche adäquate Weise in einer oder mehreren Ausführungsformen kombiniert werden. Die hierin verwendeten Bezugszeichen sind nur zum besseren Verständnis vorgesehen und definieren somit nicht den Schutz- oder Offenbarungsumfang der Ausführungsformen. Die Reduzierung der Belastung in Halbleitervorrichtungen wie beispielsweise integrierten Schaltungen (IC) stellt einen umfangreichen Bereich technischer Forschung dar. Dokument In einer oder mehreren Ausführungsformen können die in Es wird zu verstehen sein, dass aufgrund der Anwesenheit des ungeätzten Nitrids 26, das unter der Maske 28 verbleibt, beide Schichten 30 und 32 bei 300 eine stufenförmige Ausbildung aufweisen. In einer oder mehreren Ausführungsformen kann die Maske 34 seitlich versetzt (zurückgesetzt) platziert werden, beispielsweise circa 1 Mikrometer (1 × 10–6 m) bezüglich der Ausbildung 300. Es wird zu verstehen sein, dass aufgrund der Anwesenheit der stufenförmigen Ausbildung bei 300 die TiW-Schicht 30 am Rand der Metallisierung 36 durch das (bis dahin) ungeätzte Dielektrikum 26 in einem Abstand von der TiW-Barriere 24 gehalten wird. In einer oder mehreren Ausführungsformen kann die Kappenschicht 38, 40 eine Dicke von beispielsweise etwa 2 Mikrometer (2 × 10–6 m) haben. Es wird wieder zu verstehen sein, dass die Kappenschicht 38, 40 auf der äußeren Oberfläche der Metallisierung 36 durch die Anwesenheit des ungeätzten Nitrids 26 in einem Abstand von der ersten Barriereschicht 24 gehalten wird. In einer oder mehreren Ausführungsformen, wie hierin beschrieben, kann die zweite Barriereschicht 30 mit der Kappenschicht 38 in Kontakt sein, um die Metallisierung 36 einzukapseln. Die anderen in Wieder verhindert dies die mögliche Bildung einer hohen thermomechanischen Belastung mit den entsprechenden Nachteilen, wie im Einleitungsteil dieser Beschreibung erläutert. In einer oder mehreren Ausführungsformen, wie in Ansonsten wird zu verstehen sein, dass die spezielle Materialauswahl, wie vorstehend beispielhaft dargelegt, vor allem in Zusammenhang mit bestimmten Prozessausführungsformen steht, beispielsweise in Verbindung mit dem RDL-Prozess. Eine oder mehrere Ausführungsformen können unterschiedliche Implementierungsoptionen, beispielsweise unterschiedliche Materialwahl und oder Schichtdicken, vorgeben. Eine oder mehrere Ausführungsformen können somit ein Verfahren zum Herstellen von Halbleitervorrichtungen bereitstellen, die Metallisierungen (beispielsweise 36, 38, 40) mit peripheren Abschnitten aufweisen, wobei mindestens eine unterliegende Schicht (beispielsweise 20, 24) Randbereiche aufweist, die sich den peripheren Abschnitten zugewandt erstrecken. In einer oder mehreren Ausführungsformen kann das Verfahren aufweisen: In einer oder mehreren Ausführungsformen können die Metallisierungen aufweisen: Eine oder mehrere Ausführungsformen können das Bereitstellen einer Barriereschicht (beispielsweise 30, 30a) aufweisen, die vorzugsweise TiN und TiW aufweist, unter dem Metallisierungskörper (36) liegt und an der äußeren Oberflächenbeschichtung anliegt, um den Metallisierungskörper vollständig zu bedecken, wobei die Barriereschicht (beispielsweise 30, 30a) vorgesehen wird (siehe beispielsweise Eine oder mehrere Ausführungsformen können das Bereitstellen der mindestens einen unterliegenden Schicht als eine Passivierungsschicht (beispielsweise 20) aufweisen, auf der vorzugsweise eine entsprechende Barriereschicht (beispielsweise 24) vorgesehen ist. Eine oder mehrere Ausführungsformen können das Bereitstellen der entsprechenden Barriereschicht auf der Passivierungsschicht als eine Schicht aufweisen, die sich unter dem Metallisierungskörper erstreckt, wobei die Opferschicht vorgesehen ist, um die entsprechende Barriereschicht an den Randbereichen der mindestens einen unterliegenden Schicht zu bedecken (siehe beispielsweise Eine oder mehrere Ausführungsformen können das Entfernen der entsprechenden Barriereschicht von der Passivierungsschicht an anderen Stellen als den Randbereichen aufweisen (vergleiche beispielsweise In einer oder mehreren Ausführungsformen: In einer oder mehreren Ausführungsformen kann die Opferschicht (beispielsweise 26) Siliziumnitrid aufweisen. In einer oder mehreren Ausführungsformen können die Metallisierungen Cu-RDL-Metallisierungen aufweisen. Eine oder mehrere Ausführungsformen können eine Halbleitervorrichtung mit Metallisierungen mit peripheren Abschnitten bereitstellen, wobei mindestens eine unterliegende Schicht Randbereiche hat, diese sich den peripheren Abschnitten zugewandt erstrecken, wobei sich die Randbereiche der mindestens einen unterliegenden Schicht den peripheren Abschnitten ohne eine Kontaktgrenzfläche dazwischen zugewandt erstrecken. Unbeschadet der zugrundeliegenden Prinzipien können die Einzelheiten und Ausführungsformen bezüglich der Darstellungen hierin, die rein als nicht beschränkende Beispiele dienen, – sogar wesentlich – variieren, ohne dadurch vom Schutzumfang abzuweichen. Der Schutzumfang ist durch die anliegenden Ansprüche bestimmt. Diese Liste der vom Anmelder aufgeführten Dokumente wurde automatisiert erzeugt und ist ausschließlich zur besseren Information des Lesers aufgenommen. Die Liste ist nicht Bestandteil der deutschen Patent- bzw. Gebrauchsmusteranmeldung. Das DPMA übernimmt keinerlei Haftung für etwaige Fehler oder Auslassungen. In einer Ausführungsform weist ein Verfahren zum Herstellen von Halbleitervorrichtungen, die Metallisierungen (36, 38, 40) mit peripheren Abschnitten aufweisen, wobei mindestens eine unterliegende Schicht (20, 24) Randbereiche aufweist, die sich den peripheren Abschnitten zugewandt erstrecken, auf: – Bereitstellen einer Opferschicht (26) zum Bedecken der Randbereiche der unterliegenden Schicht (20, 24), – Bereitstellen der Metallisierungen (36, 38, 40), während die Randbereiche der unterliegenden Schicht (20, 24) von der Opferschicht (26) bedeckt sind, und – Entfernen der Opferschicht (26), so dass die Randbereiche der unterliegenden Schicht (20, 24) sich den peripheren Abschnitten ohne eine Kontaktgrenzfläche dazwischen zugewandt erstrecken, wodurch thermomechanische Belastungen vermieden werden. Verfahren zum Herstellen von Halbleitervorrichtungen, die Metallisierungen (36, 38, 40) mit peripheren Abschnitten aufweisen, wobei mindestens eine unterliegende Schicht (20, 24) Randbereiche aufweist, die sich den peripheren Abschnitten zugewandt erstrecken, wobei das Verfahren aufweist: Verfahren nach Anspruch 1, wobei die Metallisierungen (36, 38, 40) aufweisen: Verfahren nach Anspruch 2, das das Bereitstellen einer Barriereschicht (30, 30a) aufweist, die vorzugsweise TiN und TiW aufweist, unter dem Metallisierungskörper (36) liegt und an der äußeren Oberflächenbeschichtung (38, 40) anliegt, um den Metallisierungskörper (36) vollständig zu bedecken, wobei die Barriereschicht (30, 30a) vorgesehen wird, während die Randbereiche der mindestens einen unterliegenden Schicht (20, 24) von der Opferschicht (26) bedeckt sind. Verfahren nach einem der vorhergehenden Ansprüche, das das Bereitstellen der mindestens einen unterliegenden Schicht als eine Passivierungsschicht (20) aufweist, auf der vorzugsweise eine entsprechende Barriereschicht (24) vorgesehen ist. Verfahren nach Anspruch 4, das das Bereitstellen der entsprechenden Barriereschicht (24) auf der Passivierungsschicht (20) als eine Schicht, die sich unter dem Metallisierungskörper (36) erstreckt, aufweist, wobei die Opferschicht (26) vorgesehen wird, um die entsprechende Barriereschicht (24) an den Randbereichen der mindestens einen unterliegenden Schicht (20, 24) zu bedecken. Verfahren nach Anspruch 4 oder Anspruch 5, das das Entfernen der entsprechenden Barriereschicht (24) von der Passivierungsschicht (20) an anderen Stellen als den Randbereiche aufweist. Verfahren nach einem der Ansprüche 4 bis 6, wobei: Verfahren nach einem der vorhergehenden Ansprüche, wobei die Opferschicht (26) Siliziumnitrid aufweist. Verfahren nach einem der vorhergehenden Ansprüche, wobei die Metallisierungen (36, 38, 40) Cu-RDL-Metallisierungen aufweisen. Halbleitervorrichtung, die Metallisierungen (36, 38, 40) mit peripheren Abschnitten aufweist, wobei mindestens eine unterliegende Schicht (20, 24) Randbereiche aufweist, die sich den peripheren Abschnitten zugewandt erstrecken, wobei sich die Randbereiche der mindestens einen unterliegenden Schicht (20, 24) den peripheren Abschnitten ohne eine Kontaktgrenzfläche dazwischen zugewandt erstrecken.ZITATE ENTHALTEN IN DER BESCHREIBUNG

Zitierte Patentliteratur

– Bereitstellen einer Opferschicht (26) zum Bedecken der Randbereiche der mindestens einen unterliegenden Schicht (20, 24),

– Bereitstellen der Metallisierungen, (36, 38, 40) während die Randbereiche der mindestens einen unterliegenden Schicht (20, 24) von der Opferschicht (26) bedeckt sind, und

– Entfernen der Opferschicht (26), wodurch sich die Randbereiche der mindestens einen unterliegenden Schicht (20, 24) den peripheren Abschnitten ohne eine Kontaktgrenzfläche dazwischen zugewandt erstrecken.

– einen Metallisierungskörper (36), der vorzugsweise Kupfer aufweist, und

– eine äußere Oberflächenbeschichtung (38, 40) des Körpers (36), wobei die Beschichtung vorzugsweise mindestens eine einer Nickelschicht (38) und einer Palladiumschicht (40) aufweist, wobei sich die Randbereiche ohne eine Kontaktgrenzfläche mit sowohl dem Metallisierungskörper (36) als auch der äußeren Oberflächenbeschichtung (38, 40) den peripheren Abschnitten zugewandt erstrecken.

– die Passivierungsschicht eine dielektrische Passivierungsschicht (20) aufweist und/oder

– die entsprechende Barriereschicht (24) eine TiW-Barriere aufweist.