Packaging substrate, method for manufacturing same, and chip packaging structure having same

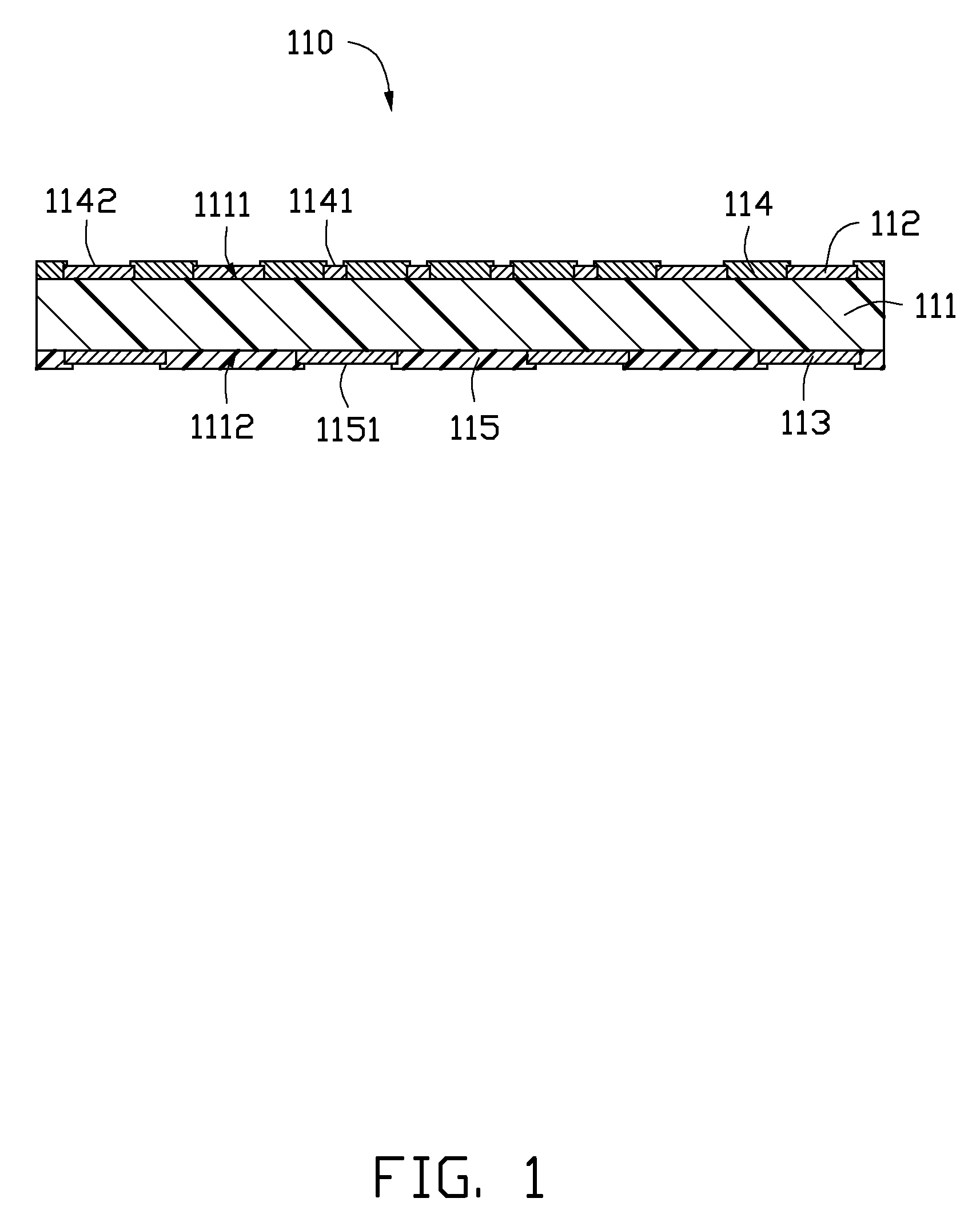

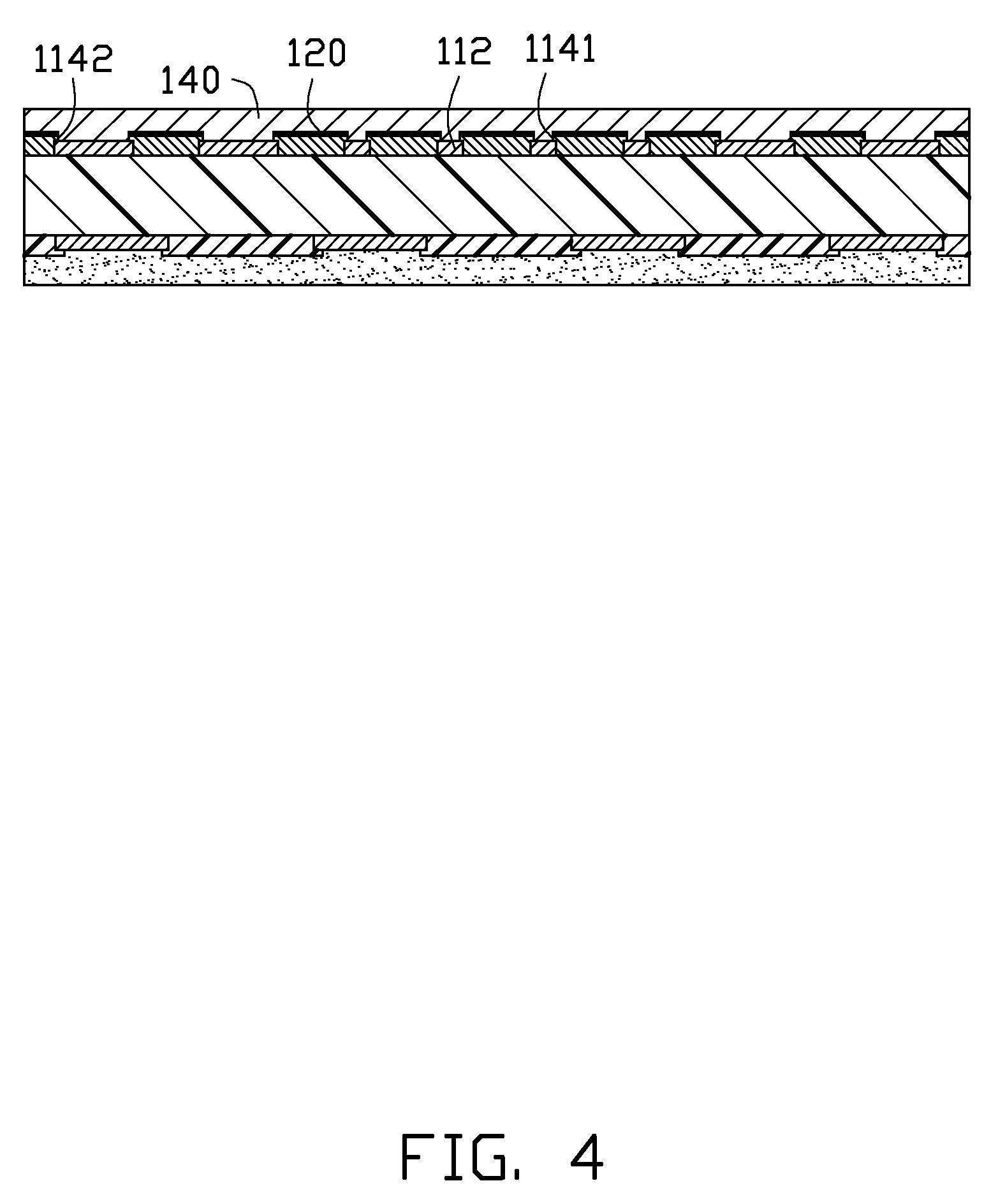

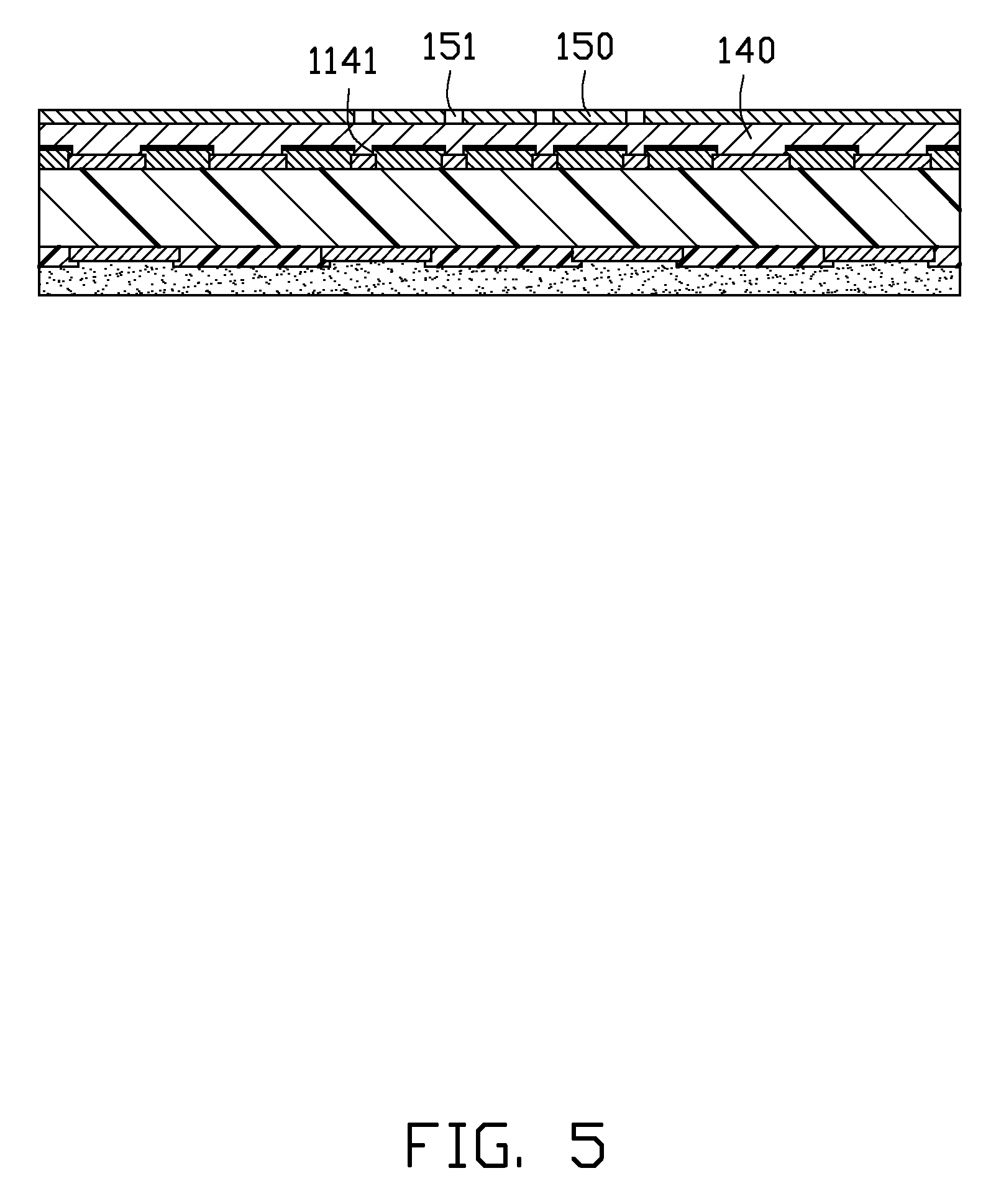

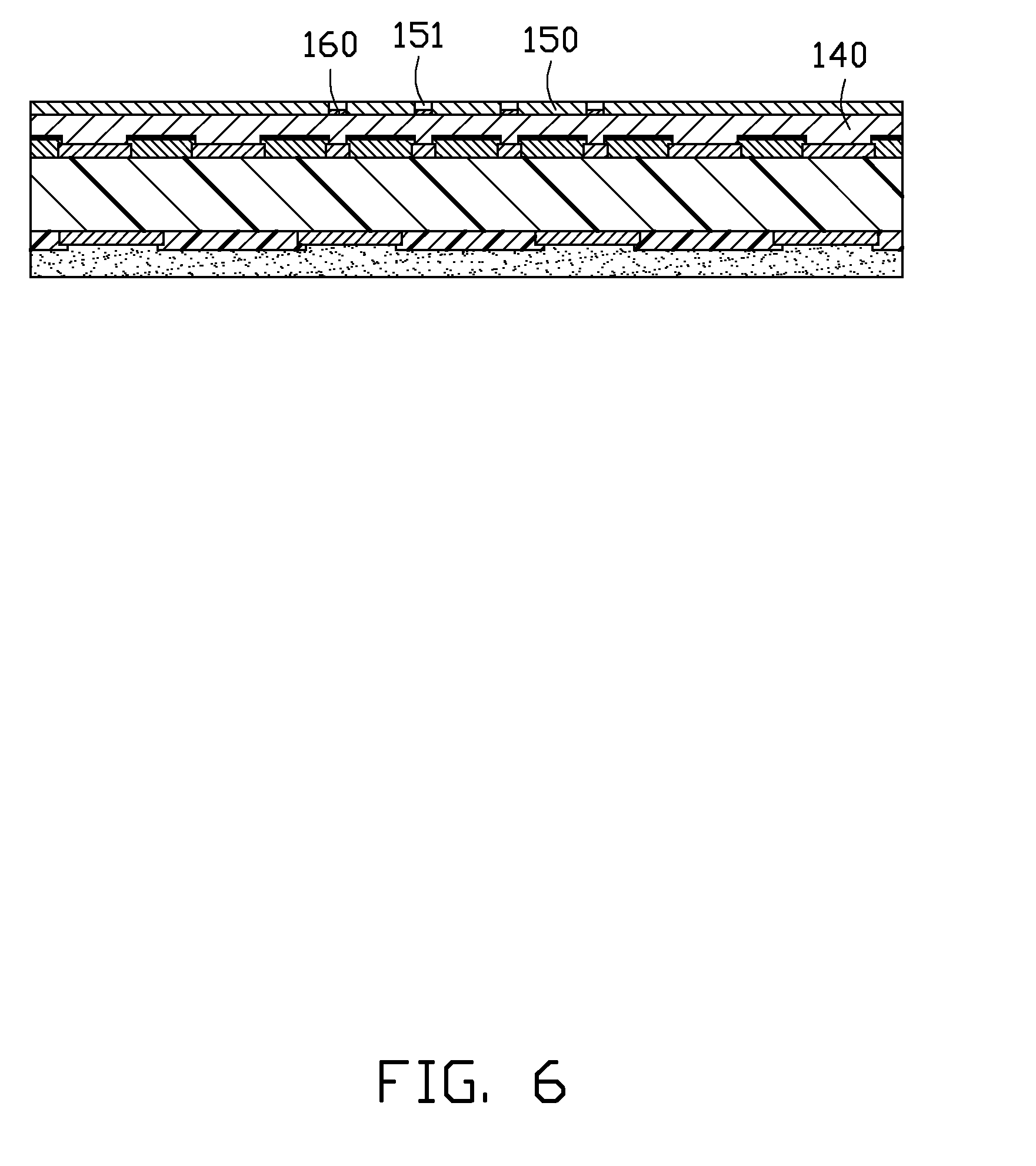

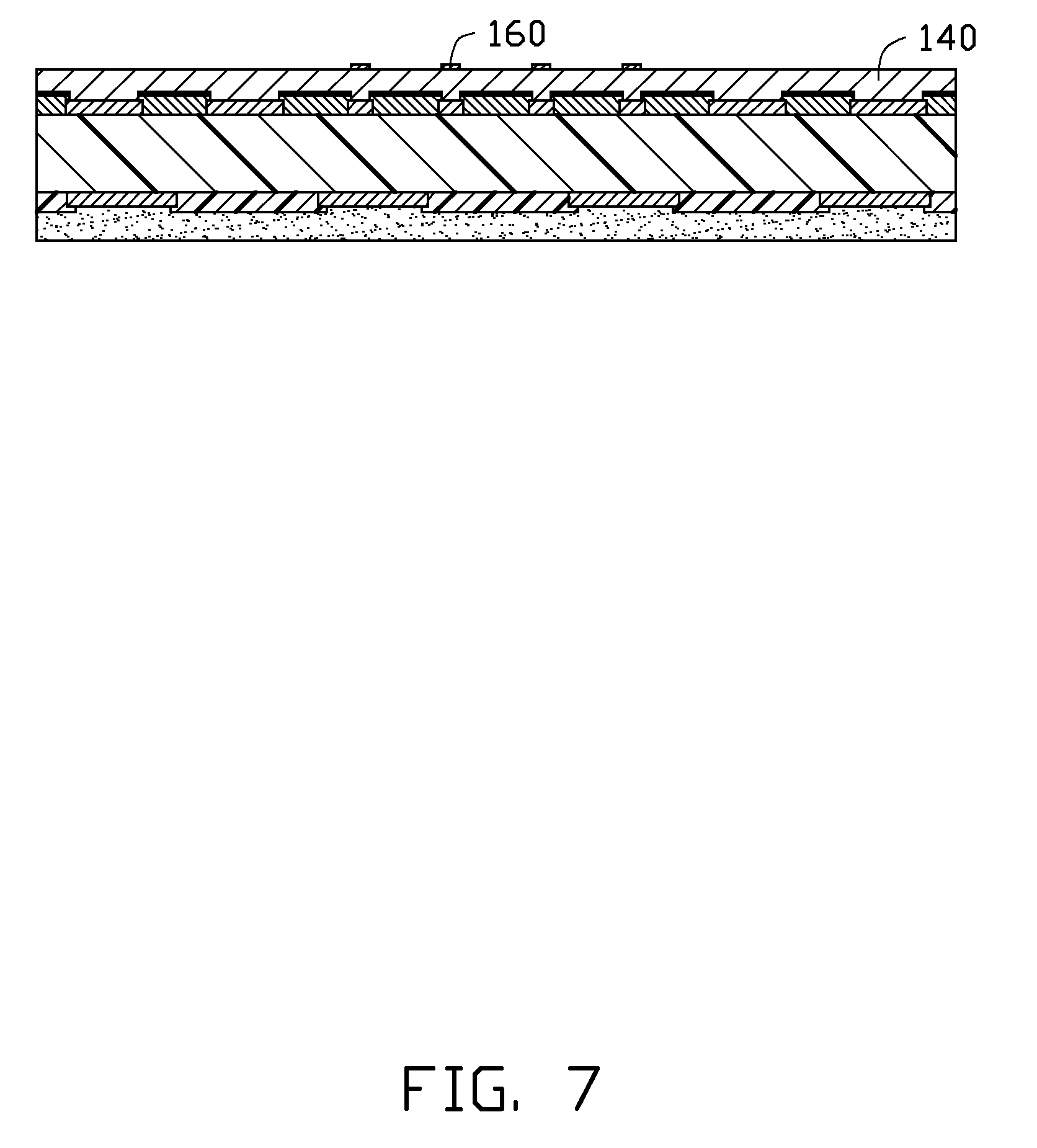

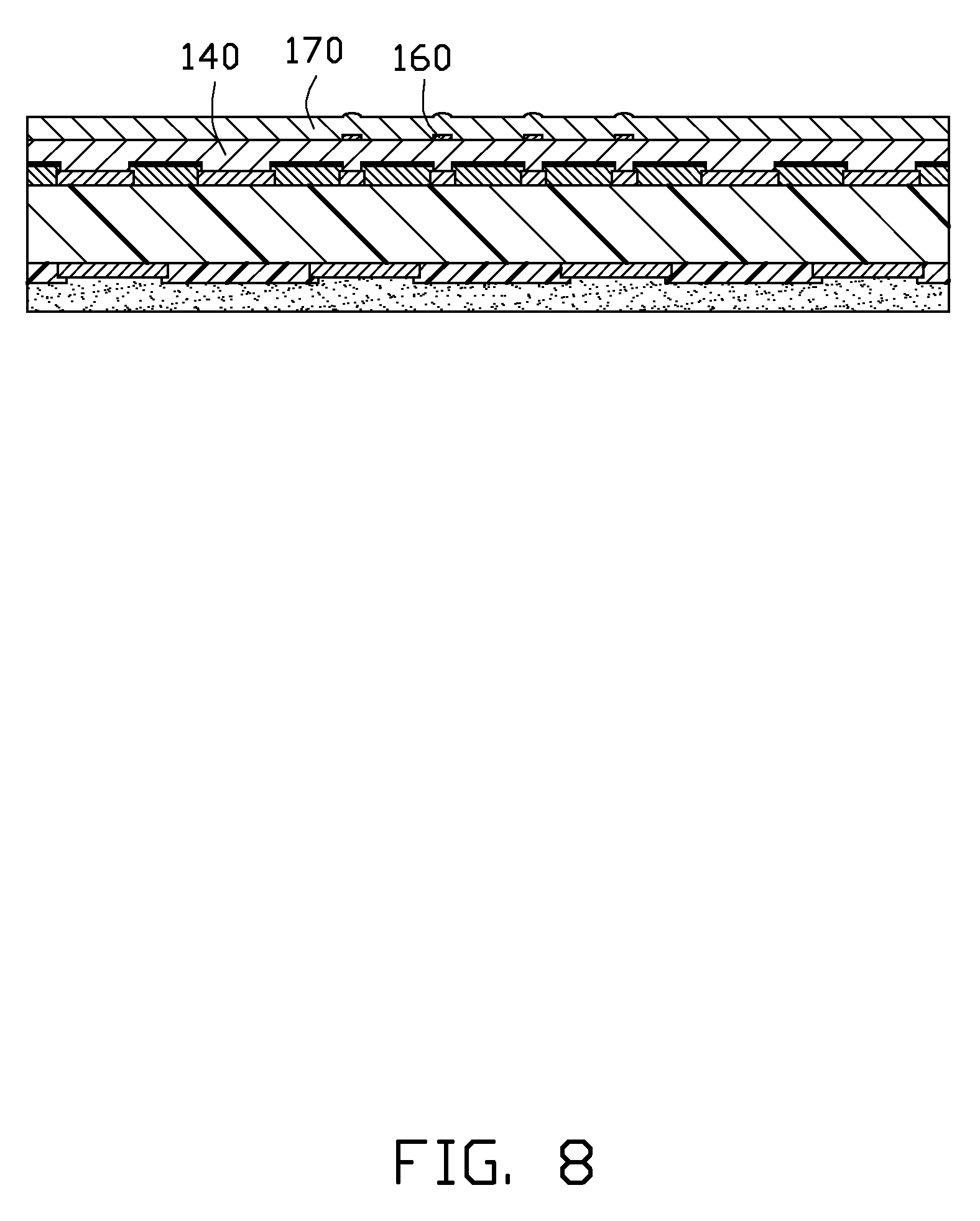

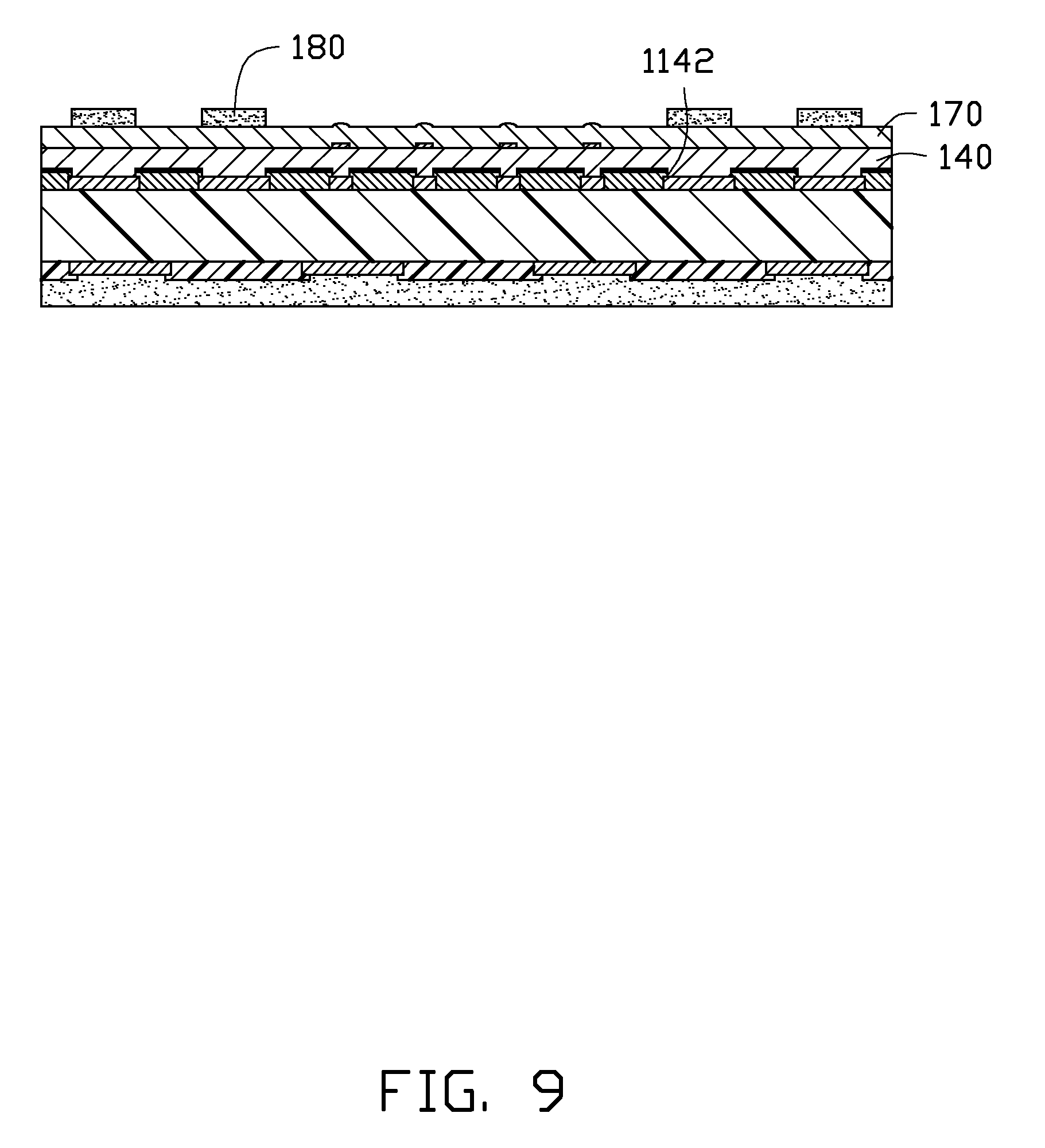

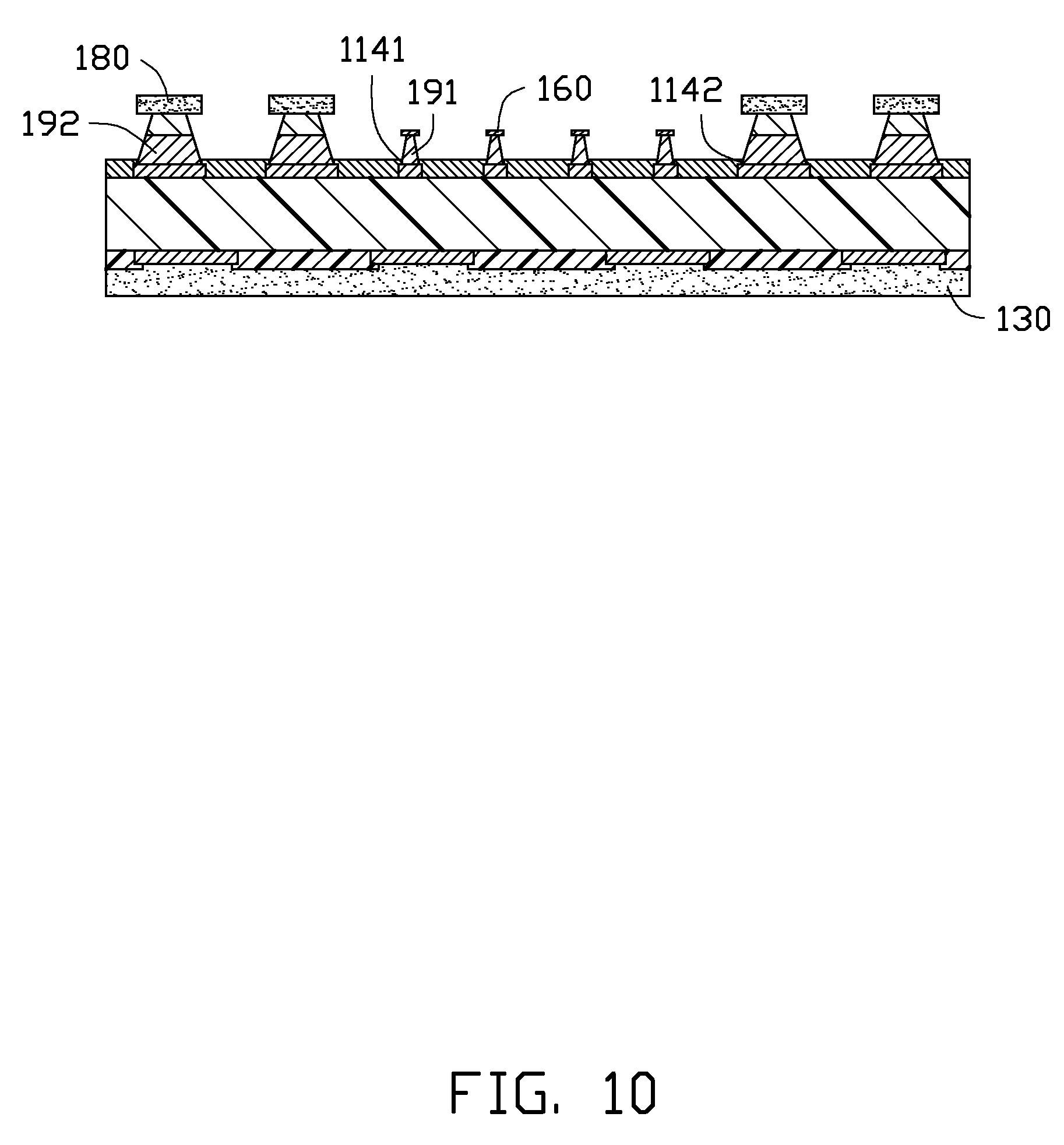

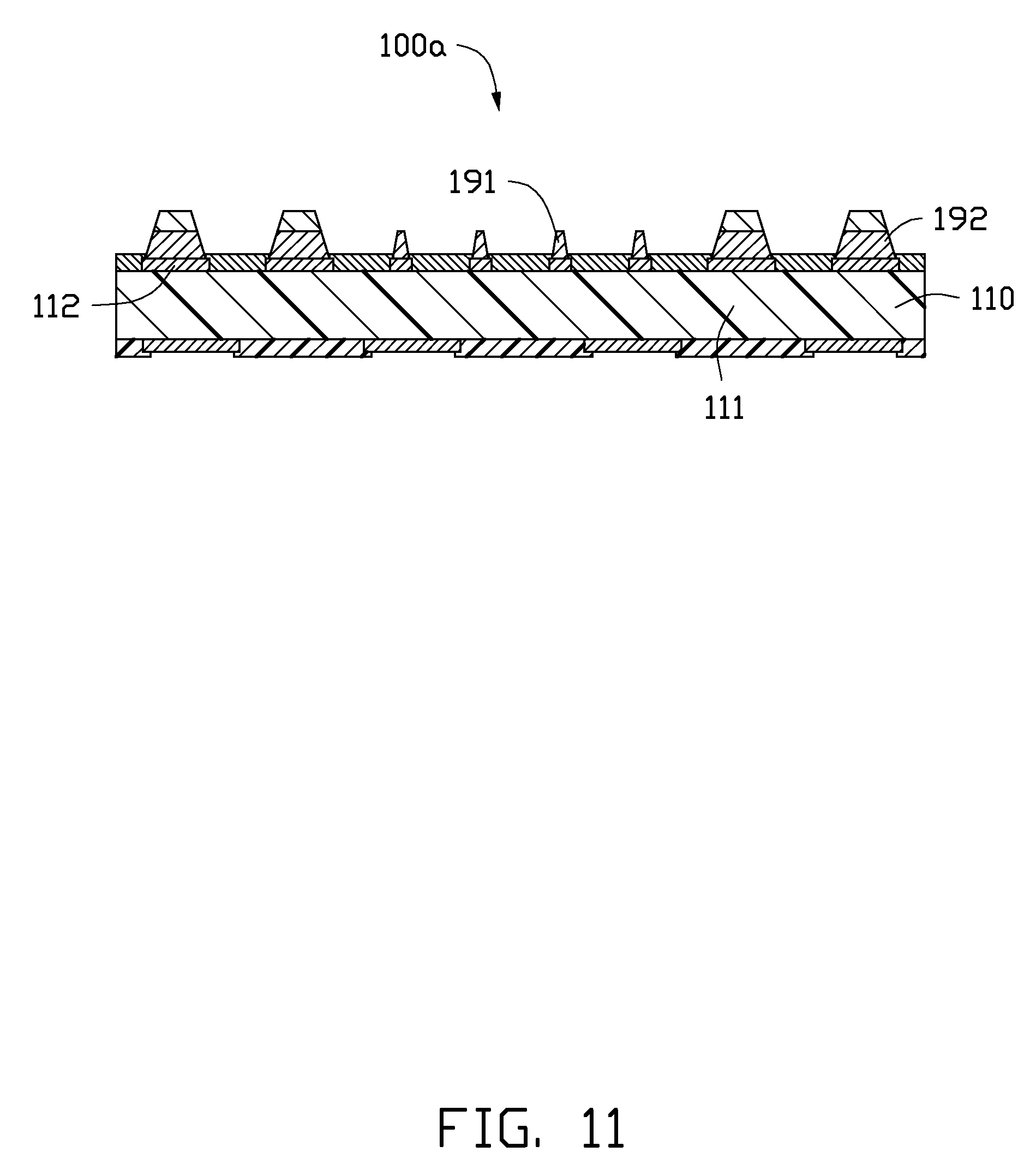

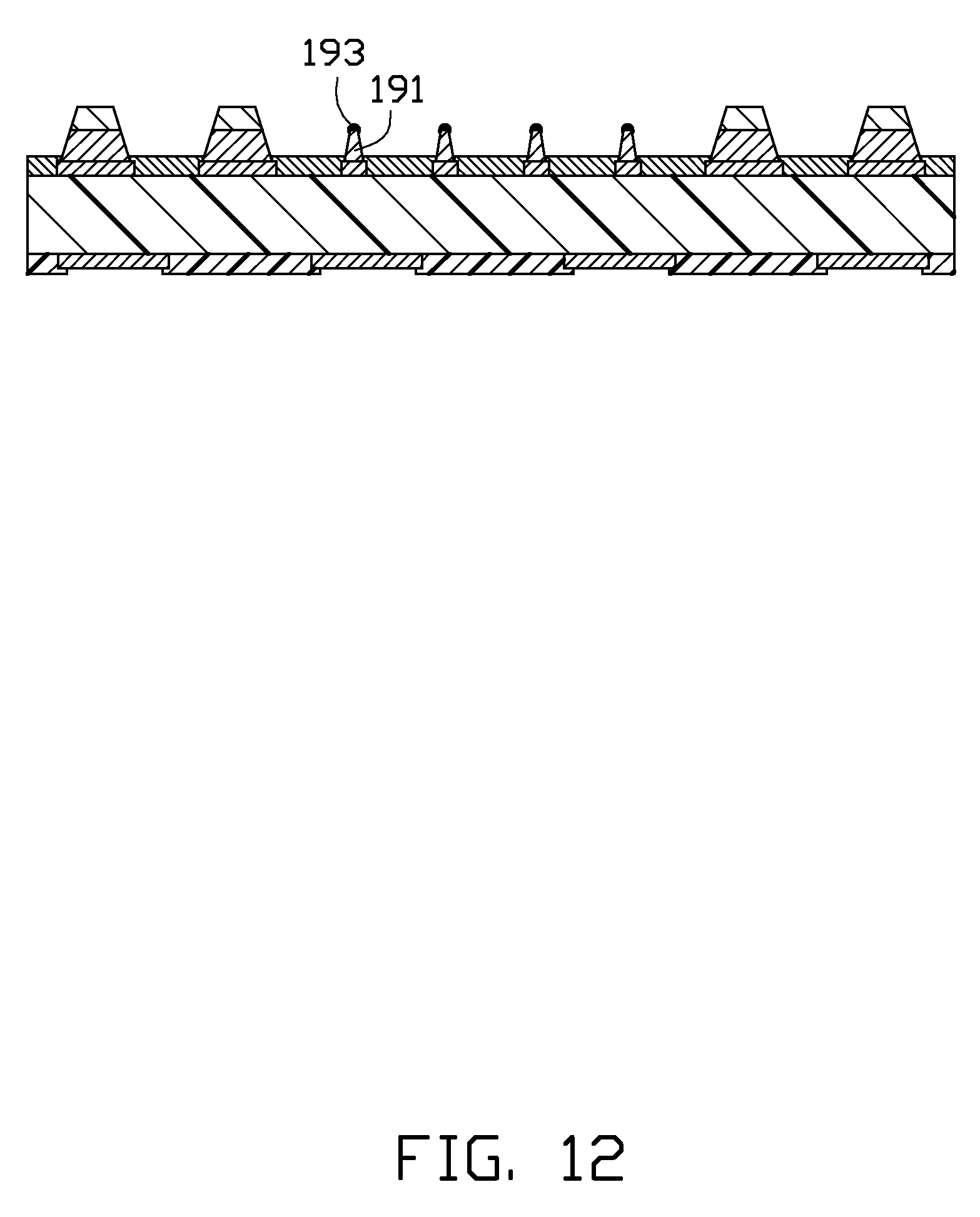

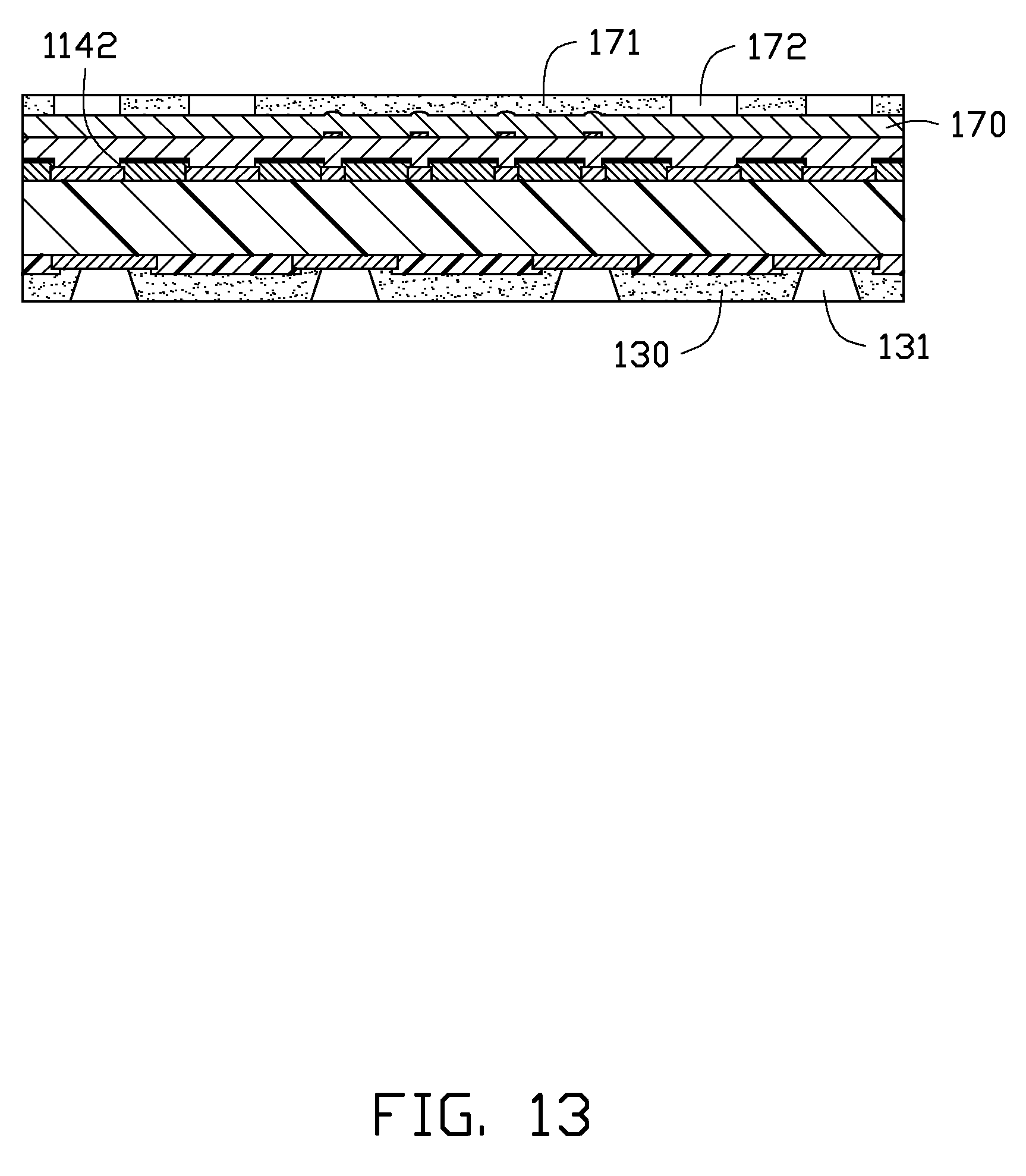

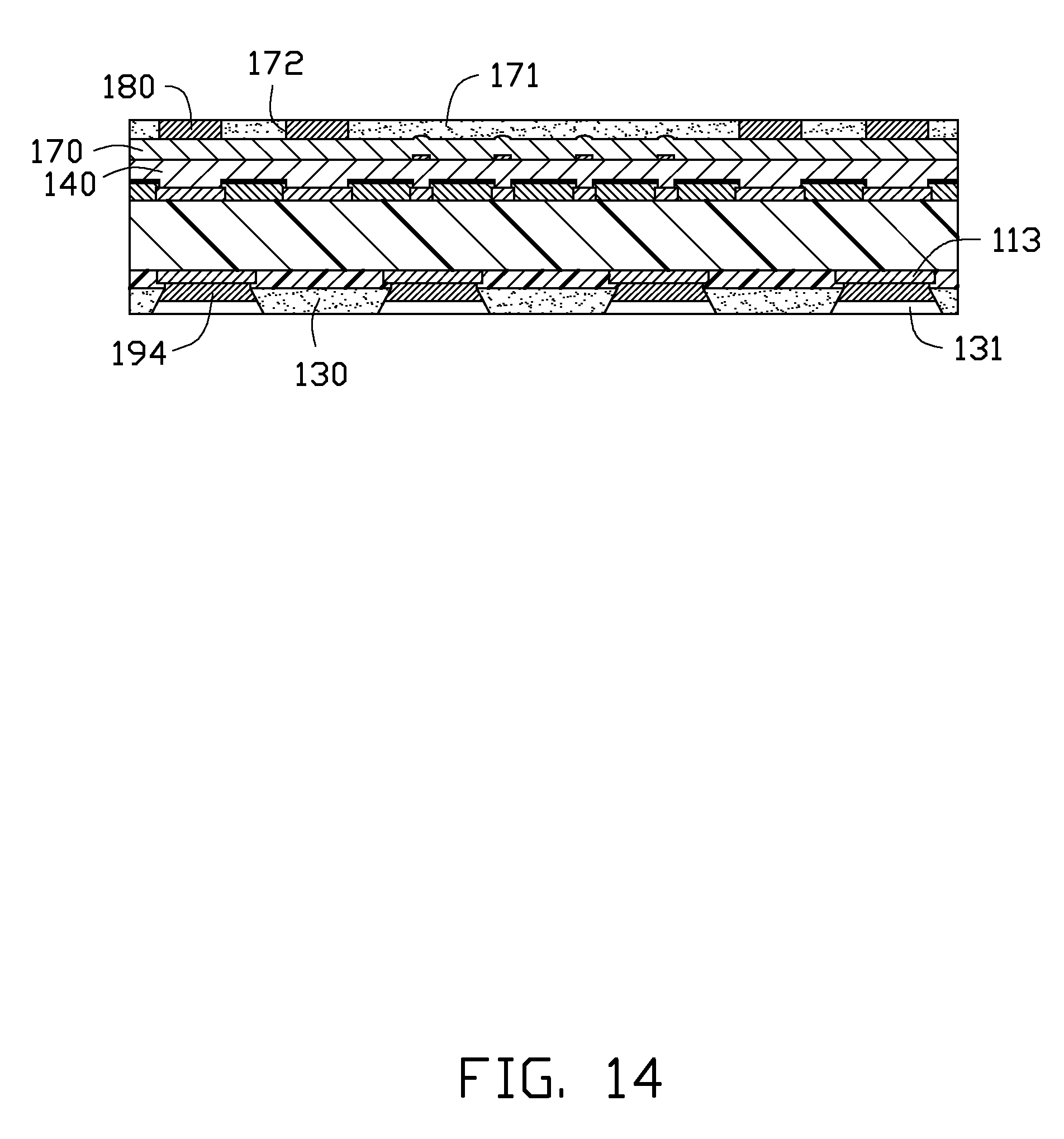

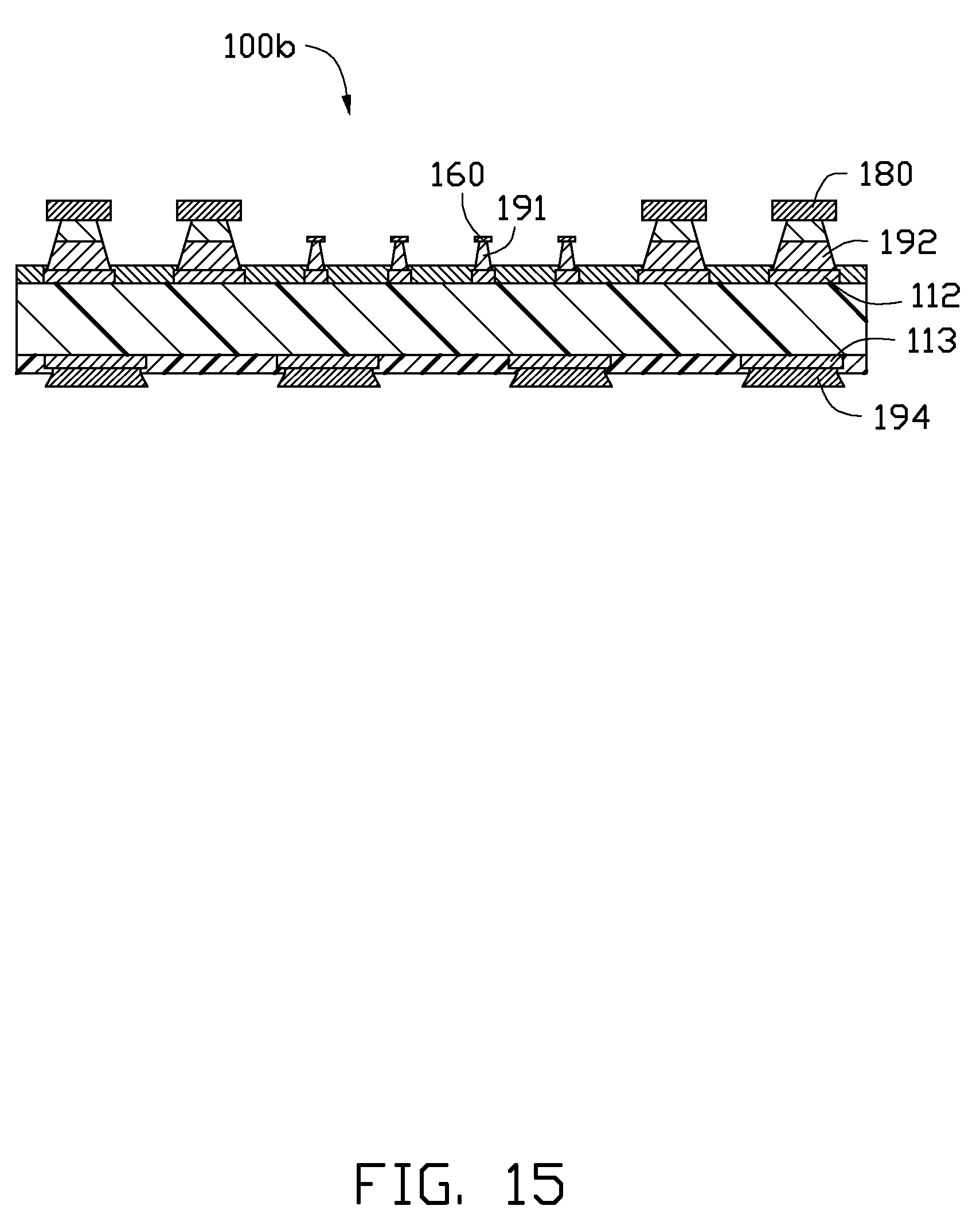

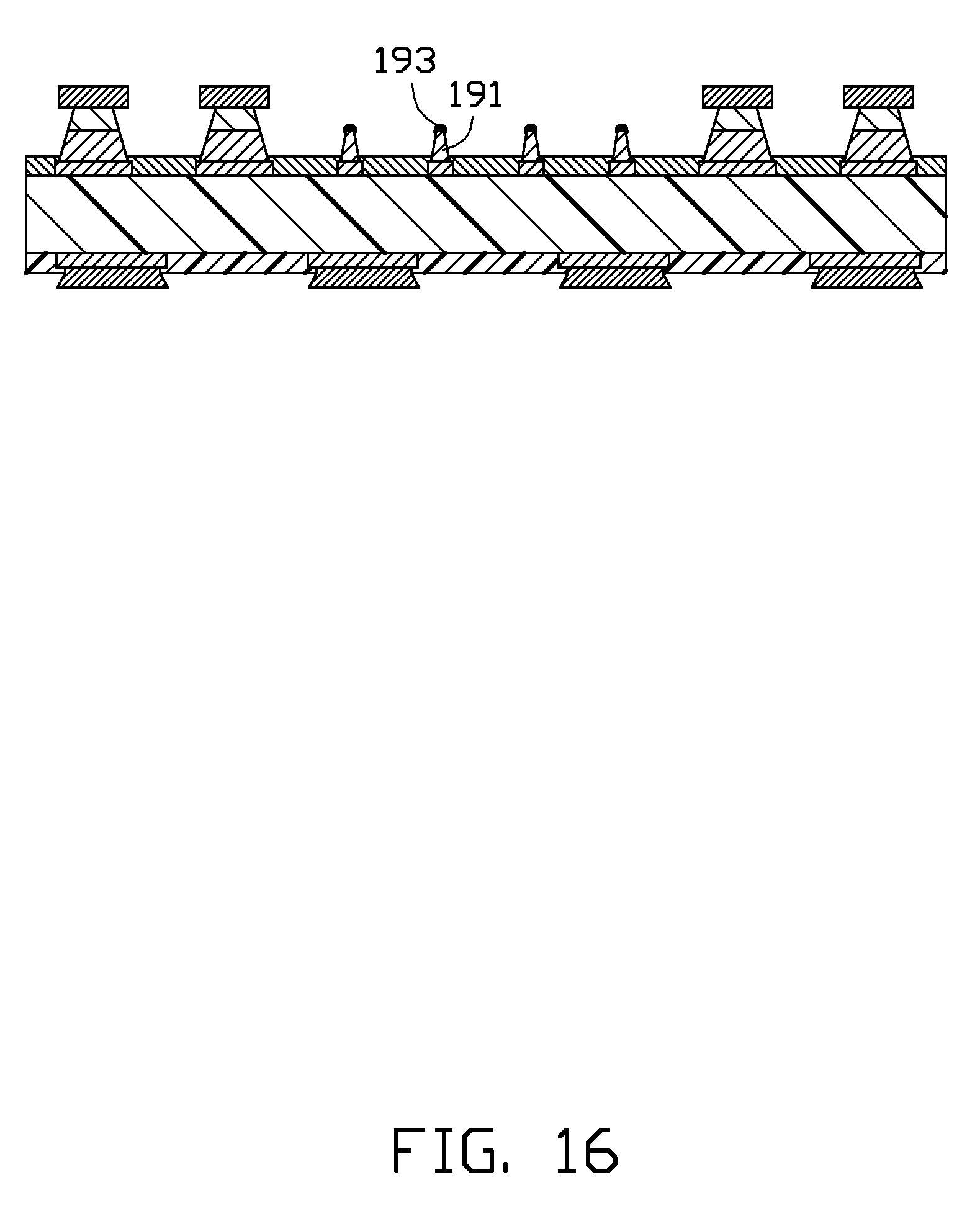

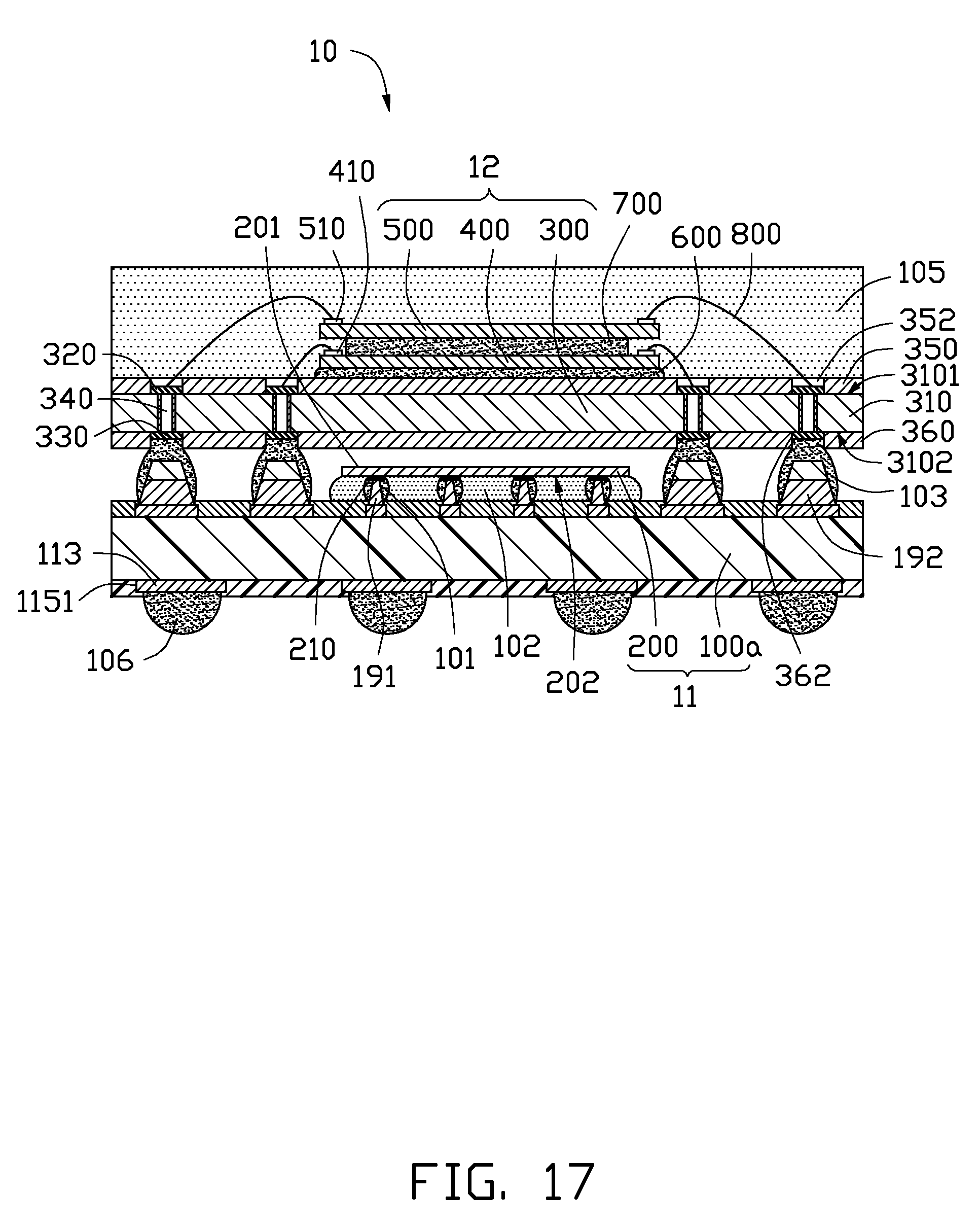

1. Technical Field The present disclosure relates to semiconductor packaging technology and, particularly, to a packaging substrate, a method for manufacturing the packaging substrate, and a chip packaging structure having the packaging substrate. 2. Description of Related Art A chip packaging structure includes a packaging substrate, a connecting substrate, and a number of chips. Some of the chips are arranged on and are electrically connected to the packaging substrate, and the other chips are arranged on and are electrically connected to the connecting substrate. The packaging substrate is mechanically and electrically connected to the connecting substrate through a number of solder balls, which are formed between one surface of the packaging substrate and an opposing surface of the connecting surface. However, the binding force between the packaging substrate and the connecting surface is limited because the contact areas between the solder balls and the surfaces are limited. Thus, the solder balls are easily damaged if the chip packaging structure is touched when in transport or in use. This will make the chip packaging structure not work normally and safe. Therefore, it is desirable to provide a packaging substrate, a method for manufacturing the packaging substrate, and a chip packaging structure having the packaging substrate, to overcome or at least alleviate the above-mentioned problems. Referring to First, referring to The circuit board 110 may be a single-sided circuit board, a double-sided circuit board, or a multilayer circuit board. The circuit board 110 includes a first base 111, a first conductive pattern layer 112, a second conductive pattern layer 113, a first solder mask 114, and a second solder mask 115. In this embodiment, the circuit board 110 is a multilayer circuit board, and includes a number of resin layers (not shown) and a number of conductive pattern layers (not shown) alternatively stacked on one another. The first base 111 includes a first surface 1111 and a second surface 1112. The first surface 1111 and the second surface 1112 are positioned at opposite sides of the first base 111, and the first surface 1111 is substantially parallel to the second surface 1112. The first conductive pattern layer 112 is located on the first surface 1111. The second conductive pattern layer 113 is located on the second surface 1112. The first conductive pattern layer 112 is electrically connected to the second conductive pattern layer 113 through via holes (not shown) defined in the first base 111. The first solder mask 114 covers part of the first surface 1111 which is exposed to the first conductive pattern layer 112 and part of the first conductive pattern layer 112. The first solder mask 114 defines a number of first openings 1141 and a number of second openings 1142. The first openings 1141 are positioned at a central portion of the first solder mask 114 and are arranged in an array. The second openings 1142 surround the first openings 1141. The cross-sectional area of each of the first openings 1141 is less than that of each of the second openings 1142. The first conductive pattern layer 112 is exposed to the first openings 1141 and the second openings 1142. The second solder mask 115 covers part of the second surface 1112 which is exposed to the second conductive pattern layer 113 and part of the second conductive pattern layer 113. The second solder mask 115 defines a number of third openings 1151. The second conductive pattern layer 113 is exposed to the third openings 1151. Second, referring to Third, referring to Fourth, referring to Fifth, referring to Sixth, referring to Seventh, referring to Eighth, referring to Ninth, referring to Tenth, referring to Eleventh, referring to Referring to Ninth, referring to Tenth, referring to Eleventh, referring to Referring to The circuit board 110 may be a single-sided circuit board, a double-sided circuit board, or a multilayer circuit board. The circuit board 110 includes a first base 111, a first conductive pattern layer 112, a second conductive pattern layer 113, a first solder mask 114, and a second solder mask 115. In this embodiment, the circuit board 110 is a multilayer circuit board, and includes a number of resin layers (not shown) and a number of conductive pattern layers (not shown) alternatively stacked on one another. The first base 111 includes a first surface 1111 and a second surface 1112. The first surface 1111 and the second surface 1112 are positioned at opposite sides of the first base 111, and the first surface 1111 is substantially parallel to the second surface 1112. The first conductive pattern layer 112 is located on the first surface 1111. The second conductive pattern layer 113 is located on the second surface 1112. The first conductive pattern layer 112 is electrically connected to the second conductive pattern layer 113 through via holes (not shown) defined in the first base 111. The first solder mask 114 covers part of the first surface 1111 which is exposed to the first conductive pattern layer 112 and part of the first conductive pattern layer 112. The first solder mask 114 defines a number of first openings 1141 and a number of second openings 1142. The first openings 1141 are positioned at a central portion of the first solder mask 114 and are arranged in an array. The second openings 1142 surround the first openings 1141. The cross-sectional area of each of the first openings 1141 is less than that of each of the second openings 1142. The first conductive pattern layer 112 is exposed to the first openings 1141 and the second openings 1142. The second solder mask 115 covers part of the second surface 1112 which is exposed to the second conductive pattern layer 113 and part of the second conductive pattern layer 113. The second solder mask 115 defines a number of third openings 1151. The second conductive pattern layer 113 is exposed to the third openings 1151. The first conductive posts 191 correspond to the first openings 1141. The second conductive posts 192 correspond to the second openings 1142. The first conductive posts 191 extend from the first conductive pattern layer 112 in the respective first openings 1141. The second conductive posts 192 extend from the first conductive patter layer 112 in the respective second openings 1142. The height of each of the second conductive posts 192 is larger than that of each of the first conductive posts 191. A solder cap 193 is formed on a top end of each of the first conductive posts 191. The solder cap 193 is made of tin or nickel. In other embodiments, a protective layer (not shown) can be formed on a top end of each of the second conductive posts 192, and the protective layer is gold plating over nickel. Referring to The first chip packaging body 11 includes the packaging substrate 100 The second chip packaging body 12 includes a connecting substrate 300, a second chip 400, and a third chip 500. The connecting substrate 300 includes a second base 310, a number of first contact pads 320, a number of second contact pads 330, a third solder mask 340, and a fourth solder mask 350. The second base 310 includes a second top surface 3101 and a second bottom surface 3102. The second top surface 3101 and the second bottom surface 3102 are positioned at opposite sides of the second base 310, and the second top surface 3101 is substantially parallel to the second bottom surface 3102. The second base 310 defines a number of conductive holes 340 corresponding to the second conductive posts 192, the first contact pads 320, and the second contact pads 330. Each of the conductive holes 340 passes through the second top surface 3101 and the second bottom surface 3102. The first contact pads 320 are formed on the second top surface 3101 and are aligned with the respective conductive holes 340. The second contact pads 330 are formed on the second bottom surface 3102 and are aligned with the respective conductive holes 340. That is, the first contact pads 320 are electrically connected to the respective second contact pads 330 through the respective conductive holes 340. The third solder mask 350 is formed on the second top surface 3101 and defines a number of fourth opening 352 corresponding to the first contact pads 320. Each of the first contact pads 320 is exposed to the corresponding fourth opening 352. The fourth solder mask 360 is formed on the second bottom surface 3102 and defines a number of fifth openings 362 corresponding to the second contact pads 330. Each of the second contact pads 330 is exposed to the corresponding fifth opening 362. The second chip 400 is located on the third solder mask 350 through a second packaging glue 600. The third chip 500 is located on the second chip 400 through a dielectric film 700 and is spaced apart from the second chip 400. A number of second electrode pads 410 are formed on the second chip 400 surrounding the second packaging glue 600. A number of third electrode pads 510 are formed on the third chip 500 surrounding the dielectric film 700. The second electrode pads 410 and the third electrode pads 510 are electrically connected to the first contact pads 320 through wires 800. A third packaging glue 105 is formed on the connecting substrate 300 and seals the entire second chip 400, the entire third chip 500, the entire second solder mask 350, and the entire wires 800, therefore the connection between the second chip 400, the third chip 500 and the connecting substrate 300 is more reliable. When the second chip packaging body 12 is packaged on the first chip packaging body 11, the second conductive posts 192 are mechanically and electrically connected to the respective second contact pads 330 through second solder balls 103. In detail, each of the second solder balls 103 surrounds the entire circumferential surface of the corresponding second conductive post 192 and covers the entire corresponding second contact pad 330. In this embodiment, a number of third solder balls 106 are formed on the second conductive pattern layer 113 exposed to the respective third openings 1151. The third solder balls 106 are configured for connecting the other electronic elements (not shown). In this embodiment, sum of the height of each of the first conductive posts 191 and the thickness of the first chip 200 is equal to the height of each of the second conductive posts 192. In the chip packaging structure 10, the contact area between the first chip 200 and the first packaging substrate 100 In other embodiments, the packaging substrate 100 Even though numerous characteristics and advantages of the present embodiments have been set forth in the foregoing description, together with details of the structures and functions of the embodiments, the disclosure is illustrative only, and changes may be made in detail, especially in the matters of shape, size, and arrangement of parts within the principles of the disclosure to the full extent indicated by the broad general meaning of the terms in which the appended claims are expressed. A packaging substrate includes a circuit board, a number of first conductive posts, and a number of second conductive posts. The circuit board includes a first base and a first conductive pattern layer formed on a first surface of the first base. The first conductive posts extend from and are electrically connected to the first conductive pattern layer. The second conductive posts extend from and are electrically connected to the first conductive pattern layer. The height of each of the second conductive posts are larger than that of each of the first conductive posts. 1. A method for manufacturing a packaging substrate comprising:

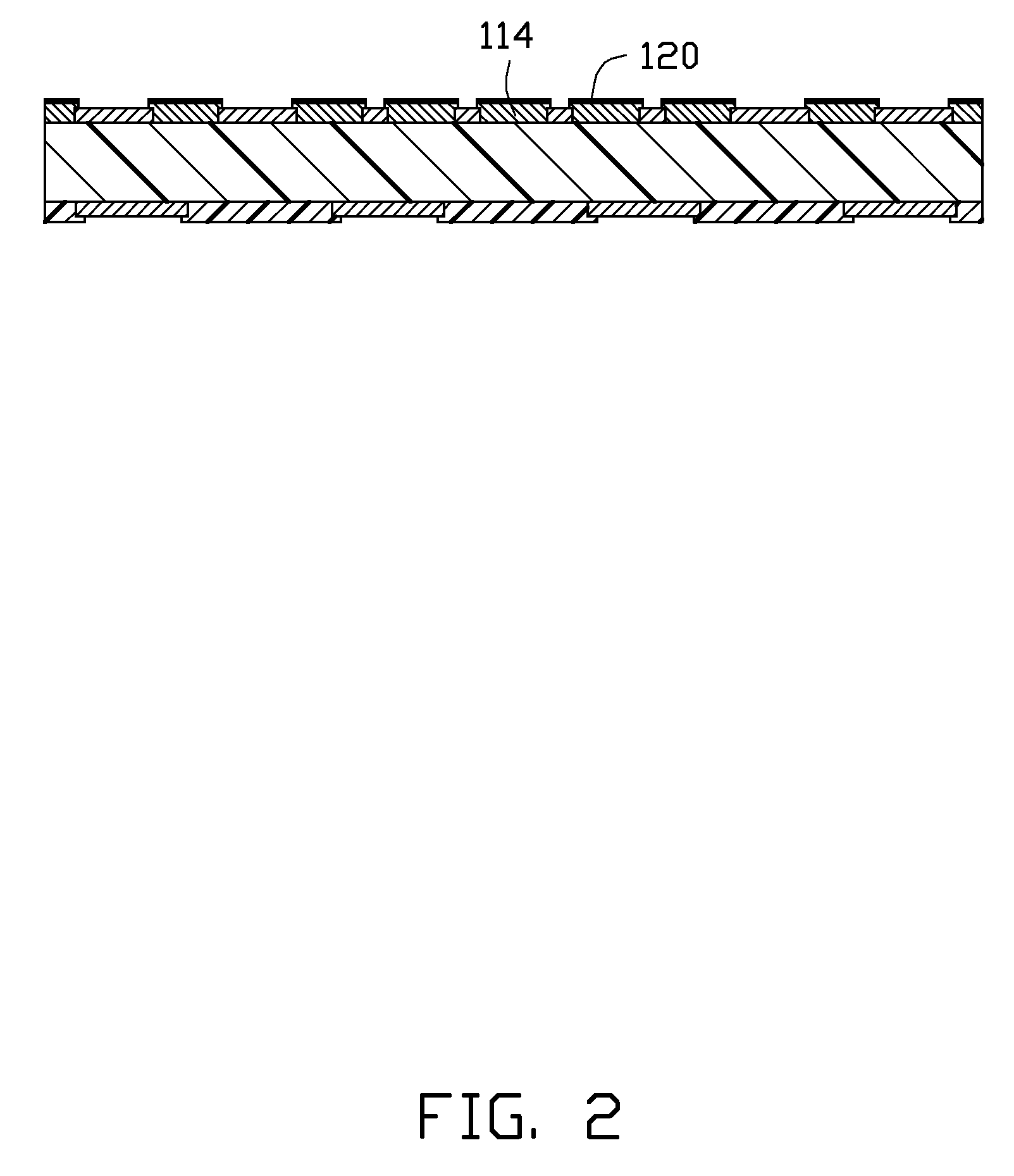

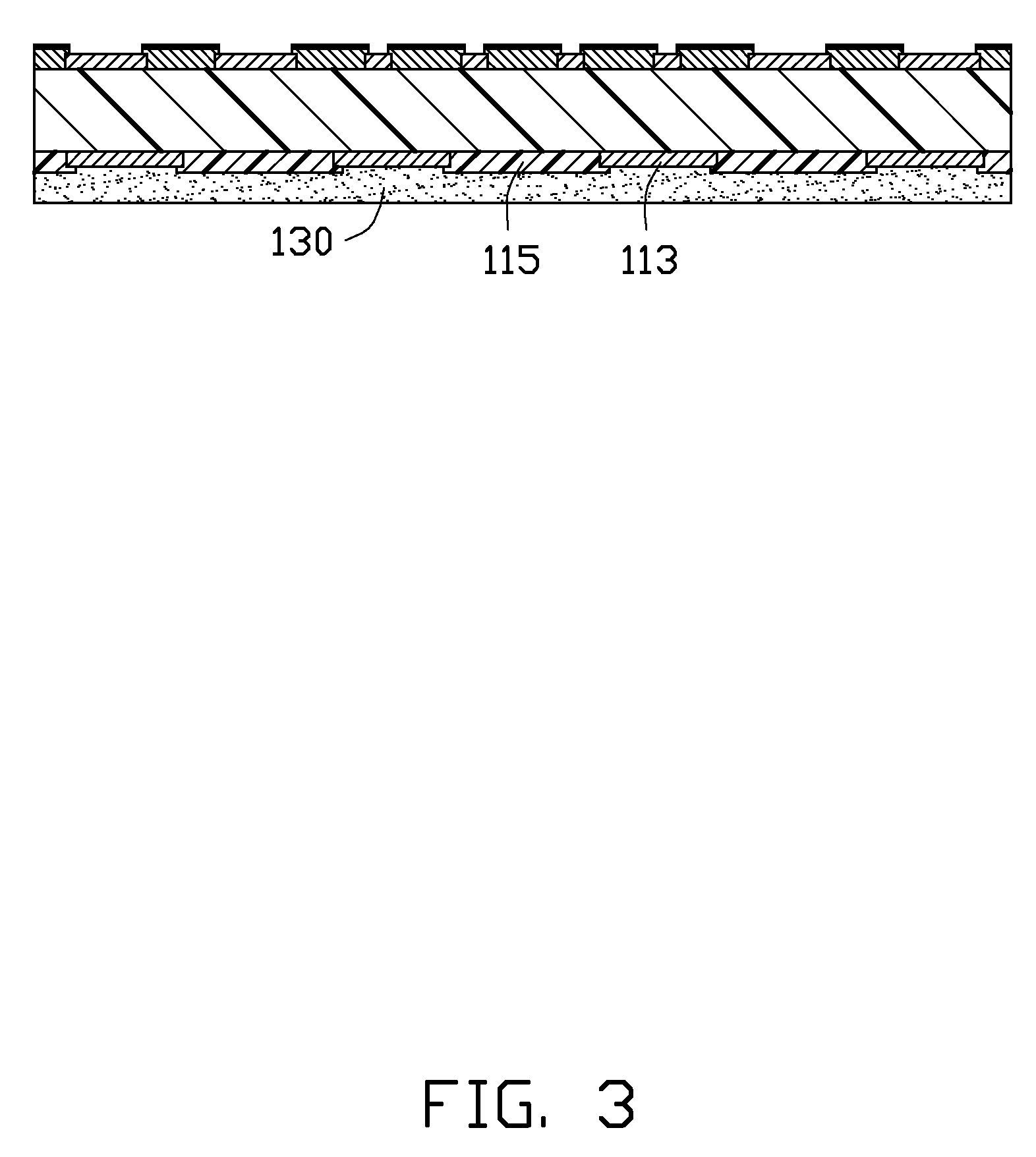

providing a circuit board, the circuit board comprising a first base having a first surface and a second surface at opposite sides thereof, a first conductive pattern layer formed on the first surface, a second conductive pattern layer formed on the second surface, a first solder mask formed on part of the first surface which is exposed to the first conductive pattern layer and part of the first conductive pattern layer, a second solder mask formed on part of the second surface which is exposed to the second conductive pattern layer and part of the second conductive pattern layer, the first solder mask defining a plurality of first openings and a plurality of second openings, part of the first conductive pattern layer exposed to the first openings and the second openings, the second solder mask defining a plurality of third openings, and part of the second conductive pattern layer exposed to the third openings; forming a metal layer on the first solder mask; forming a first plating barrier pattern on the second solder mask and part of the second conductive pattern exposed to the second solder mask; forming a first plating layer on the metal layer and the first conductive pattern layer; forming a second plating barrier pattern on the first plating layer, the second plating barrier pattern defining a plurality of first through holes corresponding to the first openings; forming a first etching barrier pattern on part of the first plating layer which is exposed to the first through holes; removing the second plating barrier pattern; forming a second plating layer on the first plating layer and the first etching barrier pattern; forming a second etching barrier pattern corresponding to the second openings on the second plating layer; etching the first plating layer and the second plating layer to form a plurality of first conductive posts in the first openings and a plurality of second conductive posts in the second openings. 2. The method of 3. The method of 4. The method of 5. The method of BACKGROUND

BRIEF DESCRIPTION OF THE DRAWINGS

DETAILED DESCRIPTION

CPC - классификация

HH0H01H01LH01L2H01L21H01L21/H01L21/4H01L21/48H01L21/485H01L21/4853H01L22H01L222H01L2224H01L2224/H01L2224/0H01L2224/08H01L2224/082H01L2224/0823H01L2224/08238H01L2224/1H01L2224/16H01L2224/162H01L2224/1622H01L2224/16225H01L2224/3H01L2224/32H01L2224/321H01L2224/3214H01L2224/32145H01L2224/322H01L2224/3222H01L2224/32225H01L2224/4H01L2224/48H01L2224/480H01L2224/4809H01L2224/48091H01L2224/7H01L2224/73H01L2224/732H01L2224/7320H01L2224/73204H01L2224/7326H01L2224/73265H01L2225H01L2225/H01L2225/1H01L2225/10H01L2225/102H01L2225/1023H01L2225/105H01L2225/1058H01L2225/107H01L23H01L23/H01L23/4H01L23/49H01L23/498H01L23/4981H01L23/49811H01L23/49816H01L23/4982H01L23/49827H01L23/4986H01L23/49866H01L24H01L24/H01L24/0H01L24/09H01L25H01L25/H01L25/1H01L25/10H01L25/105H01L29H01L292H01L2924H01L2924/H01L2924/0H01L2924/00H01L2924/000H01L2924/0001H01L2924/00014H01L2924/01H01L2924/010H01L2924/0102H01L2924/01028H01L2924/0107H01L2924/01079H01L2924/1H01L2924/15H01L2924/153H01L2924/1531H01L2924/15311H01L2924/1532H01L2924/15321H01L2924/1533H01L2924/15331H01L2924/157H01L2924/1573H01L2924/15738H01L2924/18H01L2924/181H05H05KH05K1H05K1/H05K1/0H05K1/09H05K1/1H05K1/11H05K1/115H05K2H05K22H05K220H05K2201H05K2201/H05K2201/0H05K2201/03H05K2201/034H05K2201/0347H05K2201/037H05K2201/0379H05K2201/09H05K2201/098H05K2201/0983H05K2201/09836H05K2201/1H05K2201/10H05K2201/106H05K2201/1067H05K2201/10674H05K2203H05K2203/H05K2203/0H05K2203/03H05K2203/038H05K2203/0384H05K3H05K3/H05K3/0H05K3/00H05K3/001H05K3/0017H05K3/3H05K3/34H05K3/343H05K3/3436H05K3/4H05K3/40H05K3/400H05K3/4007IPC - классификация

HH0H01H01LH01L2H01L21H01L21/H01L21/4H01L21/44H01L21/48H01L23H01L23/H01L23/4H01L23/49H01L23/498H01L25H01L25/H01L25/1H01L25/10H05H05KH05K3H05K3/H05K3/0H05K3/00H05K3/3H05K3/34H05K3/4H05K3/40Цитирование НПИ

438/108438/108